# Beckman® Series 7521M CMOS, 12-BIT MULTIPLYING D/A CONVERTERS

Effective date: October, 1977

Series 7521M are 12-bit multiplying D/A converters designed for military, aerospace and other applications demanding high performance over environmental extremes of temperature, shock, vibration and humidity. They are hermetically sealed in a standard 18-pin metal dual in-line package and provide true 12-bit accuracy over the full  $-55^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$  temperature range.

Series 7521M are compatible with TTL and CMOS logic, and with the addition of external amplifiers enable unipolar or bipolar operation. The converters operate from  $\pm 5$  to  $\pm 15$  volt power supplies, and consume only 20 mW of power.

#### Series 7521M features:

- 12-bit accuracy and resolution for uncompromised −55°C to +125°C operation.

- Guaranteed  $\pm \frac{1}{2}$  LSB linearity over the full temperature range.

- 1 LSB gain and offset error over the -55°C to +125°C range.

- 20mW dissipation to enable operation in low-power, portable or airborne system.

- Direct interface with TTL and CMOS logic families.

- Material, construction and workmanship to MIL-STD-883 Method 2017 level B.

- Pin-for-pin compatibility with AD7521.

The 7521M can directly replace competitive models thereby improving system performance by a factor of four, 0.012% FSR non-linearity instead of 0.05%. No other system changes are required.

#### Operation

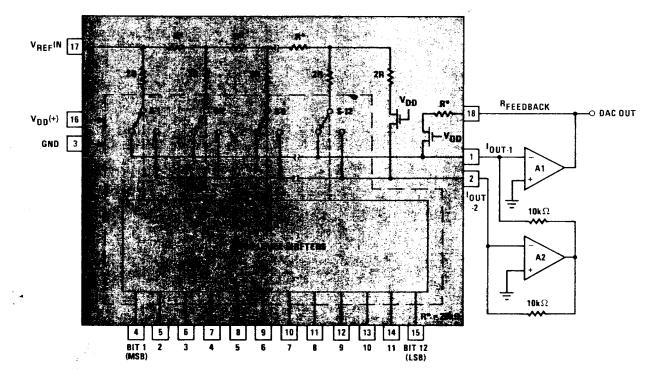

Series 7521M consists of a CMOS integrated circuit, a thin film resistor network and a zener diode. The CMOS IC provides 12 parallel inputs with level shifters, two compensation transistors and 12 current steering switches. As shown in Figure 1, each 2R leg of an inverted R-2R ladder is connected to a pair of N-channels transistors. These transistors switch the binary weighted currents that flow in each 2R leg to either the IOUT 1 bus (logic high input) or to the IOUT 2 bus (logic low input). Normal operation maintains IOUT 1 and IOUT 2 at ground or virtual ground.

Figure 1—7521M D/A Converter Block Diagram. Bipolar operation is provided by external amplifiers A1 and A2.

BECKMAN Like X Like

## **Internal Compensation**

The "on" resistance of the MOS transistor switches are binary weighted with the MSB set at 25 ohms. The linearity of the DAC is dependent upon the ratio accuracies of the switch resistances and not upon their absolute values. Excellent switch ratio tolerances account for small linearity errors even over the operating temperature range of the DAC. Also, the low power density in the switching transistors eliminates transient thermal gradients normally encountered with bipolar current switches.

Feedback gain compensation for switch resistance is provided by an "on" switch in series with the internal "R" feedback resistor. This compensation transistor reduces gain drift errors to less than  $2 \, p/10^{\circ}/^{\circ}C$  and provides outstanding power supply rejection.

A second compensation transistor (unique to Series 7521M) compensates the R-2R ladder terminating resistor, thereby eliminating the requirement for the external 10M $\Omega$  compensating resistor required by competitive models in the bipolar configuration. When replacing competitive units with the 7521M, the 10M $\Omega$  resistor can simply be removed from the board without changing the board layout.

## **Unipolar Operation**

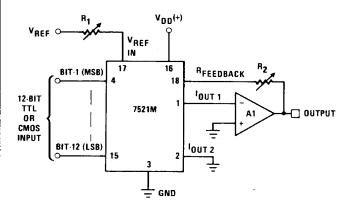

Figure 2 shows the circuit connection required for unipolar operation. Table I gives the input code/output relationship. Series 7521M is internally preset to an initial full scale gain accuracy of  $\pm 0.1\%$ . The resistor R1 and R2 shown in Figure 2 are required only when system gain adjustment is required or when a more precise initial setting is required. If external gain adjustment is used, it is normally set after adjustment of the external amplifier's zero offset.

**Zero Offset Adjustment**—With all bits set to "0," adjust the external amplifier (A1) offset to zero. (A zero offset appearing at the summing function will produce a linearity error, therefore, the output should be adjusted to zero by a method that will set the summing junction to zero.)

Gain Adjustment—Set R1 and R2 to zero (Figure 2) and turn all bits to "1." If the output is greater than required full scale value, increase R1. If the output is less than required full scale value, increase R2.

## **Bipolar Operation**

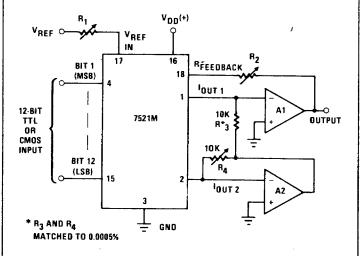

Figure 3 shows the circuit connections required for bipolar operation. Table II gives the input code/output relationship.

**Zero Offset Adjustment**—Adjust the amplifier offsets of A1 and A2 to zero.

**Gain Adjustment**—Set all inputs to "0." Set R1 and R2 to zero. If the output is greater than  $V_{REF}$ , increase R1 until the output equals  $V_{REF}$ . If the output is less than  $V_{REF}$ , increase R2 until it equals  $V_{REF}$ .

## **Absolute Maximum Ratings**

| VDD+17 Volts                                                                    |

|---------------------------------------------------------------------------------|

| V <sub>RFF</sub> ±25 Volts                                                      |

| IOUT 1/ IOUT 2100mV to VDD                                                      |

| Digital Input Voltage Range VDD to GND                                          |

| Operating Temperature Range55°C to +125°C                                       |

| Storage Temperature Range $\dots -65^{\circ}\text{C}$ to $+150^{\circ}\text{C}$ |

### **Operation Cautions**

Do not apply voltages higher than VDD or less than GRD potential to any other input or output terminal except VREF or RFEEDBACK.

#### Construction

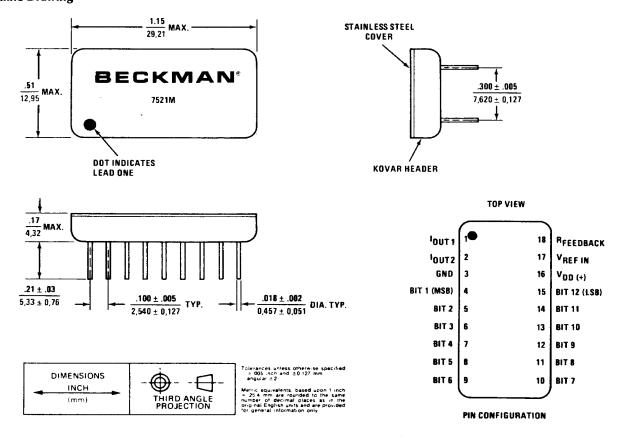

Series 7521M D-to-A Converters utilize cermet thick film conductors fired to an alumina substrate. Interconnections between these conductors, the thin film resistor network, and the CMOS IC are made by thermal compression gold wire bonding. The completed hybrid substrate is mounted on a gold plated Kovar\* header, and the circuit I/O leads are wire bonded to the terminal pins.

Table I—Unipolar Code Table

10

| M<br>S<br>B | L<br>Digital Input S<br>B | Analog Output       |

|-------------|---------------------------|---------------------|

| 111         | 1 1 1                     | -V REF (1 2-12)     |

| 100         | 0 0 1                     | V REF (12 + 2-12)   |

| 100         | 0 0 0                     | −V <sub>REF/2</sub> |

| 0 1 1       | 1 1 1                     | -V REF (1/2 - 2-12) |

| 000         | 0 0 1                     | -V REF (2-12)       |

| 000         | 0 0 0                     | 0                   |

Table II—Bipolar Code Table

| M<br>S<br>B | Digital Input | L<br>S<br>B | Analog Output                |

|-------------|---------------|-------------|------------------------------|

| 1 1 1       |               | 111         | -V <sub>REF</sub> (1 - 2-11) |

| 100         |               | 0 0 1       | -V REF (2-11)                |

| 0 0         |               | 000         | 0                            |

| 1 1         |               | 111         | V <sub>REF (2-11)</sub>      |

| 0 0         |               | 0 0 1       | V REF (1 - 2-11)             |

| 0 0         |               | 000         | V <sub>REF</sub>             |

Figure 2—Unipolar Operation

Figure 3—Bipolar Operation

<sup>\*</sup>Kovar is a registered trademark of Westinghouse Electric Corp.

**Table III—Performance Specifications**

|                             | Parameters                  |                                                               | Conditions                                                             | Mini-<br>mum | Typical | Maxi-<br>mum | Units       |

|-----------------------------|-----------------------------|---------------------------------------------------------------|------------------------------------------------------------------------|--------------|---------|--------------|-------------|

|                             | Resolution                  |                                                               |                                                                        |              |         | 12           | bits        |

|                             | Nonlinearity                |                                                               | $-55^{\circ}C \le T_{C} \le +125^{\circ}C$                             |              |         | ±0.012       | % FSR       |

| Transfer                    | Differential Nonlinearity   |                                                               | $-55^{\circ}C \le T_{C} \le +125^{\circ}C$                             |              | ±0.012  |              | % FSR       |

| Characteristics<br>(Note 1) | Gain Error (Note 2)         |                                                               | $-55^{\circ}C \le T_{C} \le +125^{\circ}C$                             |              |         | ±0.2         | % FSR       |

| (Note 1)                    | Gain Error Tempco (Note 2)  |                                                               | $-55^{\circ}\text{C} \le \text{T}_{\text{C}} \le +125^{\circ}\text{C}$ |              | ±1      | ±2           | p/106/°C    |

|                             | Reference Feedthrough       |                                                               | VREF = 20V p-p; 10KHz                                                  |              | 1       | 10           | mV p-p      |

|                             | Settling Time               |                                                               | To 0.01% of FSR for<br>a FSR Step                                      |              | 2       |              | μS          |

| Reference Input             | Reference Inp               | out Range                                                     |                                                                        |              |         | ±10          | V           |

| Reference input             | Input Resistar              | nce                                                           |                                                                        |              | 20      |              | kΩ          |

|                             | Output<br>Capacitance       | CO1                                                           | All Data Bits High                                                     |              | 200     |              | рF          |

| _                           |                             | CO2                                                           | All Data Bits High                                                     |              | 150     |              | pF          |

| Analog<br>Output            |                             | CO1                                                           | All Data Bits Low                                                      |              | 125     |              | pF          |

| Output                      |                             | CO2                                                           | All Data Bits Low                                                      |              | 70      |              | pF          |

|                             | Output Leaka                | ge Current (101, 102)                                         | -55°C≤T <sub>C</sub> ≤+125°C                                           |              |         | 100          | nA          |

|                             | TTL<br>Logic<br>tics Levels | Logic "1" Voltage                                             |                                                                        | 3            |         |              | ν           |

| Digital                     |                             | Logic "0" Voltage                                             |                                                                        |              |         | 0.8          | V           |

| Input<br>Characteristics    |                             | Input Leakage<br>Current<br>I <sub>IL</sub> , I <sub>IH</sub> | Any Input                                                              |              | +10-5   | +1           | μΑ          |

| Power                       | IDD                         |                                                               |                                                                        |              | 1       | 2            | mA          |

| Supply                      | VDD Rejection (DC)          |                                                               |                                                                        |              | 10      | ŗ            | 0/10º/FSR/% |

|                             | Total Dissipati             | on (Including ladder)                                         |                                                                        |              | 20      |              | mW          |

Unless otherwise specified, specifications apply to VDD=  $\pm$  15V, VREF =  $\pm$  10V. Specifications apply over a temperature range of  $-55^{\circ}\text{C} \leq \text{T}_{c} \leq \pm$  125°C. Typical values shown are for

Notes: 1. Full scale range (FSR) is 10V for unipolar mode and  $\pm$  10V for bipolar mode. 2. Using the internal RFEEDBACK resistor.

## **Outline Drawing**

\_This Page Intentionally Left Blank

## **BECKMAN®**

Beckman Instruments, Inc. • Helipot Division • 2500 Harbor Boulevard • Fullerton, California 92634 (714) 871-4848 • TWX: 910-592-1260 • Telex: 06-78413

4

© 1977 BECKMAN INSTRUMENTS, INC.

H78713-76A10720