# AK27CX641/642

# 64Kbit CMOS High-Speed UV-Erasable PROM

# **Features** $\square$ 8,192word $\times$ 8bit ☐ Advanced CMOS EPROM Technology ☐ High Performance - AK27CX641/642-40 $\cdot \cdot t_{AA} = 40$ nS max. - AK27CX641/642-45 $\cdot \cdot t_{AA} = 45$ nS max. - AK27CX641/642-55 $\cdot \cdot t_{AA} = 55$ nS max. ☐ Low Power Consumption $-1_{CC} = 80$ mA max. ☐ TTL-Compatible I/0 ☐ Reprogrammability Adds convenience, reduces costs - Windowed package for UV erasure - Allows 100% factory testing ☐ Bipolar PROM replacement - Pin-compatible with Bipolar PROMs - Higher speed - Lower power consumption - 300-mil(AK27CX642) and 600-mil(AK27CX641) packages

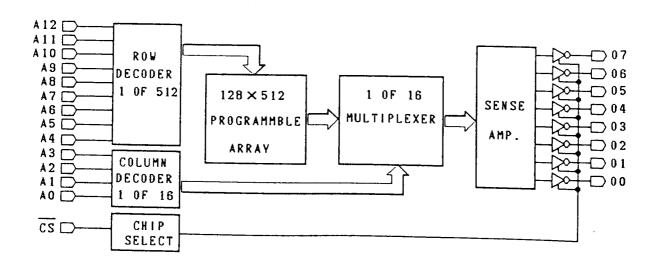

**Block Diagrams**

#### General Description

The AKM AK27CX641 and AK27CX642 are  $8,192 \times 8$ -bit, CMOS, high-speed, UV-erasable PROMs that provide a low-power, reprogrammable alternative to bipolar fuse-link PROMs. Available in both 600mil (AK27CX641) and 300mil (AK27CX642) packages, these devices are pin/socket-compatible with many popular bipolar PROMs. The AK27CX641/642 is designed in an advanced CMOS EPROM technology and utilize differential memory cell techniques to provide access times comparable to high-speed bipolar PROMs (as fast as 40nS), with a significant improvement in power consumption.

The reprogrammability of the AK27CX641/642 not only adds convenience and reduces development and field retrofit costs, but enhances factory testability, allowing for 100% field programmability and function.

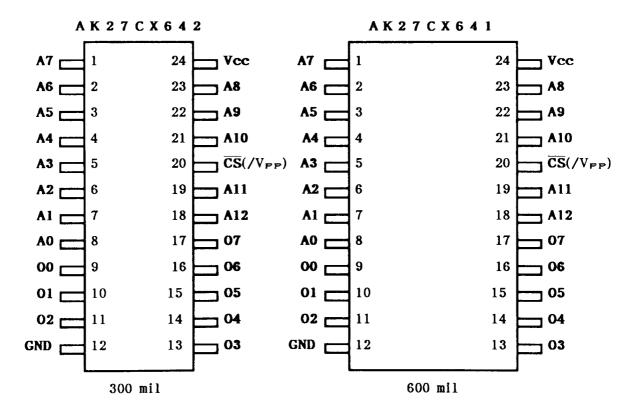

### ■ Pin Diagrams

A0-A12 = Address Input

00-07 = Data Output

= Chip Select (/VPP Programming Voltage)

GND = Ground

Vcc = Power Supply(+5V)

#### **Erasure Characteristics**

The AK27CX641/642 is erased by exposure to ultraviolet light. For complete erasure, the recommended minimum integrated dose (UV intensity × exposure time) is 15 Watt-second/cm² of ultraviolet light with a wavelength of 2537. For an ultraviolet lamp with a 12mW/cm² power rating, the exposure time would be approximately 20 minutes. The AK27CX641/642 should be placed within one inch of the lamp during erasure. Exposing the CMOS EPROM to high-intensity UV light for extended periods may affect device reliability.

### Programming the AK27CX641/642

The AK27CX641/642 employs a dual-transistor differential memory cell design. Initially, and after erasure, all bits of the AK27CX641/642 are in an undefined state. Verifying a blank device will yield erroneous results. The desired state of each bit must be programmed into the device to ensure proper operation. Programming support is available from AKM and third-party vendors.

# Absolute Maximum Ratings

Exposure to absolute maximum ratings over extended periods of time may affect device reliability. Exceeding absolute maximum ratings may cause permanent damage

| Symbol          | Parameter                       | Conditions           | Rating         | Unit       |

|-----------------|---------------------------------|----------------------|----------------|------------|

| VGC             | Supply Voltage                  | Relative to GND      | -0.6 ~ +7.0    | V          |

| V <sub>IO</sub> | Voltage Applied to<br>Any Pin   | Relative to GND      | -0.6 ~ Vcc+0.6 | V          |

| TA              | Ambient Temp.,<br>Power Applied |                      | -10 ~ +85      | °C         |

| T <sub>st</sub> | Storage<br>Temperature          |                      | -65 ∼ +125     | င          |

| $T_{LT}$        | Lead Temperature                | Soldering 10 seconds | +260           | $^{\circ}$ |

# Read Operation

### **Operation Ranges**

| Symbol | Parameter              | Conditions | min. | max. | Unit |

|--------|------------------------|------------|------|------|------|

| Vcc    | Supply Voltage         |            | 4.75 | 5.25 | V    |

| TA     | Ambient<br>Temperature |            | 0    | 70   | °C   |

## D.C. Electrical Characteristics

### Over the operating range

| Symbol          | Parameter                       | Conditions                                                                            | min. | max. | Unit |

|-----------------|---------------------------------|---------------------------------------------------------------------------------------|------|------|------|

| VIH             | Input HIGH Level                |                                                                                       | 2.0  |      | v    |

| VIL             | Input LOW Level                 |                                                                                       |      | 0.8  | v    |

| V <sub>он</sub> | Output HIGH<br>Voltage*1        | V <sub>CC</sub> =min., I <sub>OH</sub> =-4.0mA                                        | 2.4  |      | v    |

| Vol             | Output LOW<br>Voltage           | Voc=min., IoL=12mA                                                                    |      | 0.45 | v    |

| IL              | Input Leakage<br>Current        | $V_{\text{GC}}=\text{Max},$ $\text{GND} \leq V_{1} \leq V_{\text{GC}}$                |      | 10   | μΑ   |

| Ios             | Output Short<br>Circuit Current | V <sub>⊙</sub> c=max., <del>CS</del> =GND,<br>V <sub>⊙</sub> =GND                     | -15  | -90  | mA   |

| Ioz             | Output Leakage<br>Current       | V <sub>GC</sub> =max., CS=V <sub>IH</sub> ,<br>V <sub>O</sub> =V <sub>GC</sub> or GND |      | 10   | μΑ   |

| Icc             | Power Supply Current*2          | All inputs=(GND or $V_{CC}$ ) $\pm$ 0.3V                                              |      | 80   | mA   |

| VIG             | Input Clamp<br>Voltage          | V <sub>CC</sub> =min., I <sub>IN</sub> =-18mA                                         |      | -1.2 | v    |

#### Notes:

- 1. The AK27CX641/642 provide true CMOS output interface levels. The specifications shown are for TTL interface.

- 2. Maximum value for  $I_{\text{CC}}$  when all cells are programmed.

# Capacitance

# These measurements are periodically sample tested

| Symbol | Parameter          | Conditions                      | min. | max. | Unit |

|--------|--------------------|---------------------------------|------|------|------|

| Сти    | Input Capacitance  | V <sub>IN</sub> =0.0V<br>f=1MHz |      | 6    | pF   |

| Соот   | Output Capacitance |                                 |      | 12   | pF   |

| ССВ    | CS Pin Capacitance |                                 |      | 15   | pF   |

# A.C. Electrical Characteristics

# Over the Operating Range $^{\! \mathbf{a}}$

| Symbol | Parameter                                      | 27CX641-40<br>27CX642-40 |      | 27CX641-45<br>27CX642-45 |      | 27CX641-55<br>27CX642-55 |      |      |

|--------|------------------------------------------------|--------------------------|------|--------------------------|------|--------------------------|------|------|

|        |                                                | min.                     | max. | min.                     | max. | min.                     | max. | Unit |

| t      | Access Time From<br>Address To Output          |                          | 40   |                          | 45   |                          | 55   | nS   |

| tcs    | Access Time From<br>Chip Select to<br>Output*4 |                          | 20   |                          | 25   |                          | 35   | nS   |

| top    | Chip Disable to<br>High-Z*4.*5                 |                          | 20   |                          | 25   |                          | 35   | nS   |

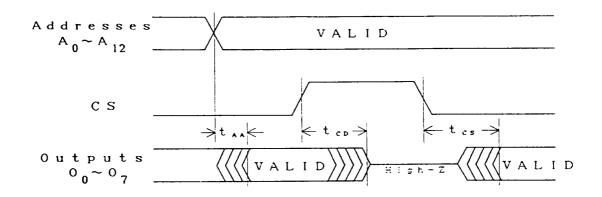

# Switching Waveforms (READ)

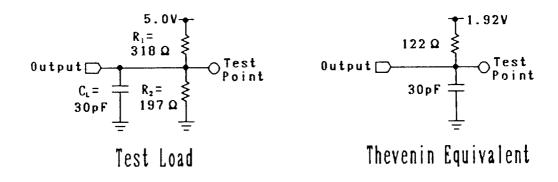

### **Test Loads**

#### Note:

- 3. Test conditions assume: signal transition times of 5 nS or less from the 10% and 90% points; timing reference levels of 1.5V(unless otherwise specified); and test loads shown above.

- 4.  $t_{CS}$ ,  $t_{CD}$ , are measured at the midpoint between output  $(0_{D-7})$  steady-state high-Z level and  $V_{OH}$  or  $V_{OL}$ .

- 5.  $C_L$  includes scope and jig capacitance.  $t_{CD}$  is tested with  $C_L$ =5pF.

## Program operation

#### **Operation Ranges**

| Symbol | Parameter           | Conditions | min. | max. | Unit |

|--------|---------------------|------------|------|------|------|

| TA     | Ambient Temperature |            | 20   | 30   | °C   |

#### D.C. Electrical Characteristics

Ta = 25℃

| Symbol           | Parameter                           | min.  | typ. | max.  | Unit |

|------------------|-------------------------------------|-------|------|-------|------|

| Vccp             | Vcc during programming              | 5.75  | 6    | 6.25  | v    |

| V <sub>IHP</sub> | Input HIGH Level during programming | 3.0   |      | 6.25  | v    |

| $V_{ILP}$        | Input LOW Level during programming  | 0     |      | 0.45  | v    |

| Vpp              | Programming Voltage                 | 11.75 | 12   | 12.25 | v    |

| Ipp              | Vpp Supply Current                  |       | 25   | 50    | mA   |

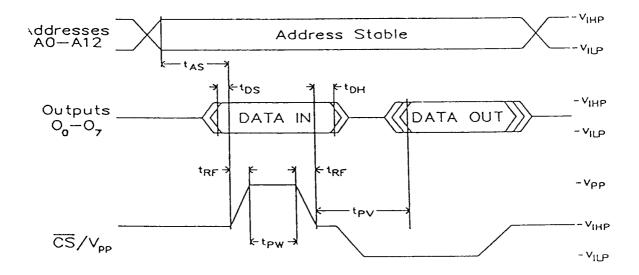

#### A.C. Electrical Characteristics

Ta = 25℃

| Symbol          | Parameter                      | min. | typ. | max. | Unit |

|-----------------|--------------------------------|------|------|------|------|

| tas             | Address set-up to Vpp pulse    | 0    |      |      | ns   |

| tos             | Data set-up to Vpp pulse       | 0    |      |      | ns   |

| tpw             | Vpp program pulse width *6     |      |      | 50   | μs   |

| t <sub>RF</sub> | Vpp rise and fall ramp time *7 | 1    |      |      | ns/V |

| t <sub>□H</sub> | Data hold time                 | 10   |      |      | ns   |

| t <sub>PV</sub> | Vpp pulse to verify delay **   |      | 2    | 5    | μs   |

#### Note:

- \*6: It is recommended to use  $50\,\mu$  s for the Vpp Program pilse width in the interetive section to ensure maximum device performance.

- \*7: In using the recommended rise and fall ramp times, any overshoot due to system and/or tester noise must not exceed the maximum Vccp voltage.

- \*8: This timing parameter is the device internal delay, After the  $\overline{CS}/Vpp$  pin has been ramped down from the Vpp to the  $V_{ILP}$  voltage (to do a data read for data verification), the outputs will have a  $t_{PV}$  delay before they are valid.

# Switching Waveforms (PROGRAMMING) <Vccp=6V>

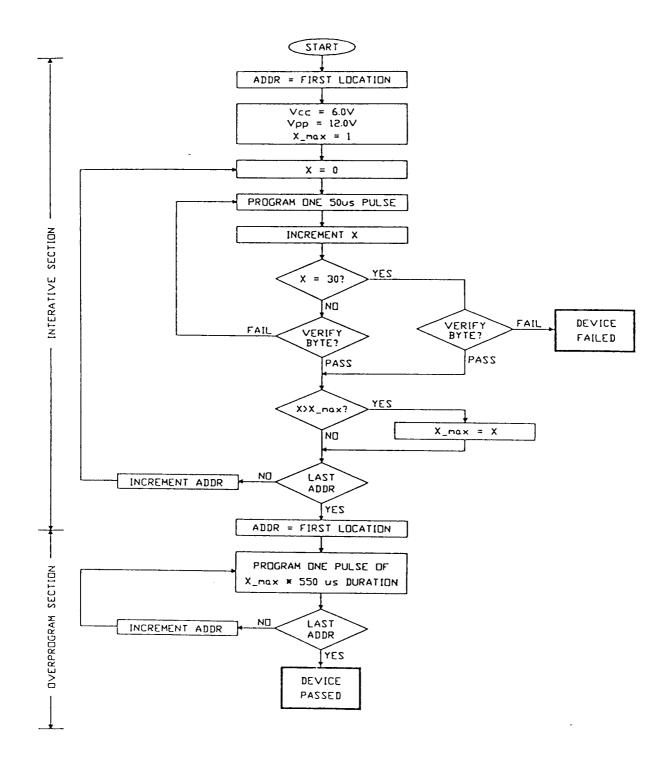

### Programming Flow