### **FEATURES**

- ☐ Four-Wide 2901 ALUs Plus Carry Look-Ahead Logic and Full 16-bit Data Paths

- High Speed, Low Power CMOS Technology

- ☐ Fast Clock Period: 35 ns Commercial, 45 ns Military

- ☐ DESC SMD No. 5962-89517

- Available 100% Screened to MIL-STD-883, Class B

- ☐ Pin and Functionally Equivalent to AMD Am29C101 and Cypress CY7C9101

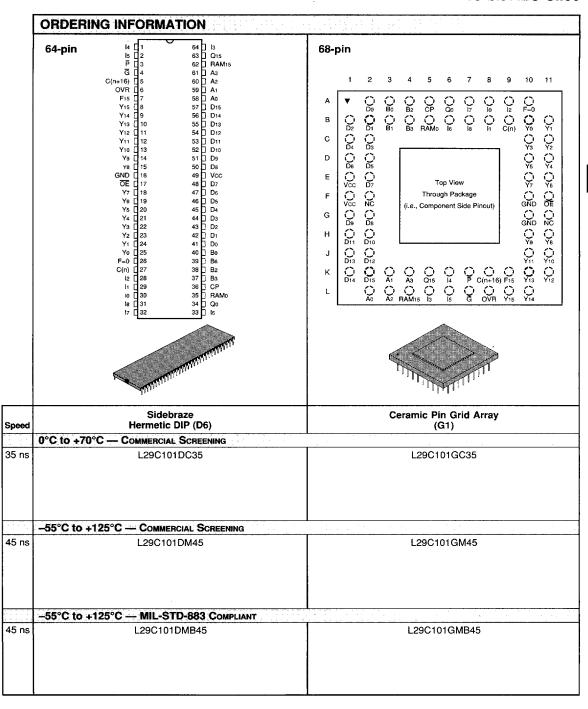

- □ Package Styles Available:

- 64-pin Sidebraze, Hermetic DIP

- 68-pin Ceramic Pin Grid Array

### DESCRIPTION

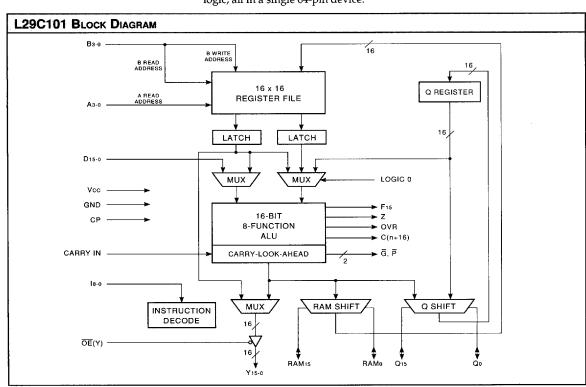

The **L29C101** is a high-performance, expandable, 16-bit Arithmetic Logic Unit slice manufactured using CMOS technology. Completely code compatible with its 4-bit predecessors, the part can be used to implement the arithmetic section of central processors or many types of programmable controllers.

The microinstruction set of the L29C101 is straightforward, yet versatile enough so that the part can be used to emulate the ALU operations of most digital computers.

The L29C101 is comprised of functions equivalent to four 2901 bit-slice ALUs plus the 2902 carry look-ahead logic, all in a single 64-pin device.

Included are a 16-word by 16-bit dualport register file, a 16-bit 8-function ALU, 16-bit shifters, and all the necessary decoding and control logic.

All status, shift linkage, and carry functions are cascadable to allow construction of architectures wider than 16-bits if desired. Expanded

### Arithmetic Logic Units

### 16-bit ALU Slice

designs can take advantage of full carry-look-ahead for improved performance.

The L29C101 is fully pin and function compatible with the Am29C101. The L29C101 is available in High-Rel versions that are fully compliant with MIL-STD-883, Class B.

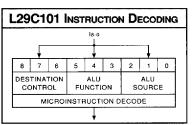

#### **L29C101 ARCHITECTURE**

A typical execution cycle for the L29C101 consists of reading two operands simultaneously from the two-port register file, performing an ALU operation on these operands, and returning the result to the register file. This entire operation can be completed in a single clock cycle, providing high performance and simple microcode. Optionally, the ALU operands may be sourced by the external data port, an

auxiliary register denoted the Quotient or "Q" register, or forced to zero under instruction control. Also, the data returned to the register file and the Q register may be shifted one bit in either direction to aid multiplication and division operations.

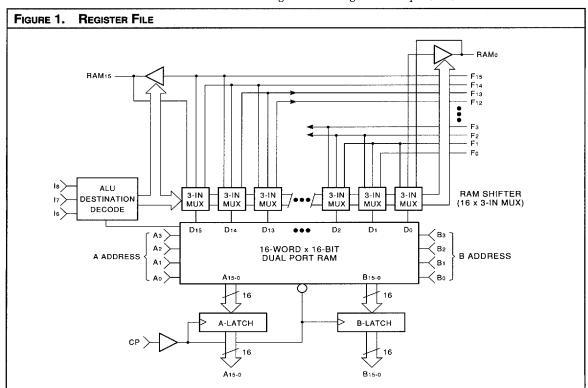

#### REGISTER FILE

The two-port register file has a capacity of 16 words of 16 bits each. The A-port address, A3-0, specifies the register to be read from the A-port, and the B-port address, B3-0, specifies the register to the read from the B-port. Both A and B addresses may be the same, in which case identical data will appear at both A and B ports. In addition, the B-port address can specify a register location for writing. Data from the locations indicated by the A and B addresses are read from the register file during the

low period of the clock. The data is applied to two latches which are transparent during the clock low period, and hold their state during the clock high period. The purpose of these latches is to hold the A and B ALU operands constant while a computation result is written back to the register file at the B address. This allows for a readmodify-write cycle, which is useful in applications such as accumulation. Under control of the Result Destination Field (I8-6), data to be written to the register file is stored into the register addressed by the B field on the rising edge of the clock.

#### **ALU CONTROL**

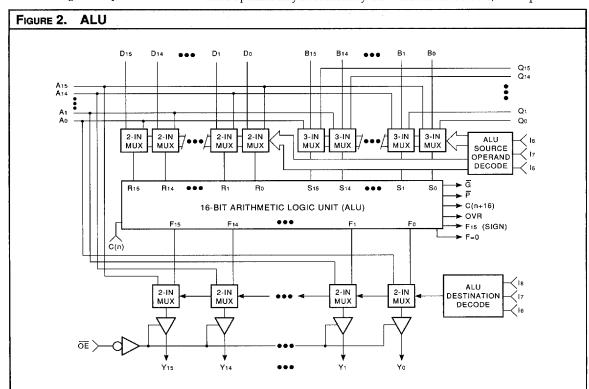

The ALU is capable of performing eight operations. These functions are described in Table 2. The control inputs, I5-3, select one of three arith-

3-16

# = Arithmetic Logic Units

03/11/94-LDS.101-G

5565905 0002436 567 1

### 16-bit ALU Slice

metic or five logical operations to be performed on the input operands. The integral carry-look-ahead circuitry across all 16 ALU bits is functionally equivalent to the 2902 carry-look-ahead unit and provides significant speed advantages.

In the arithmetic mode, the ALU result is also a function of the Carry-In input. When executing ALU Add or Subtract instructions, setting the C(n) input to '1' causes the addition of '1' to the result. Thus for two's complement operations, C(n) of the least significant slice would be set to zero for addition, and to '1' for subtraction. This is because the L29C101 ALU naturally implements one's complement subtraction, that is, a bitwise complement of one of the operands. In order to achieve a two's complement result, a '1' must be added in the least significant position. This is

accomplished by using C(n). PASS and Negate operations are also available by combining arithmetic instructions (Add, Subtract) with any of the operand source options which set one operand to zero. Tables 5 and 6 show the detailed ALU logic and arithmetic functions and the operands selected. Table 5 includes ALU function selection.

#### OPERAND SOURCE CONTROL

As shown in the figure below, each of the ALU operands is supplied by a multiplexer, which allows significant flexibility in the selection of the operand source. The two 16-bit ALU inputs are denoted R and S. The R operand may be sourced by the A read port of the register file, from the D input pins, or may be forced to zero. The S operand may be sourced by the

B read port of the register file, the A read port (when the R operand is D or zero), the Q register, or forced to zero. Control of the operand selection multiplexers is encoded into control field I2-0, as described in Table 1.

### RESULT DESTINATION CONTROL

The instruction field, I8-6, is encoded to control the routing of the ALU result field, denoted F, and the Q register contents. The encoding is defined in Table 3. Under instruction control, the ALU result can be stored in the register file, the Q register, or both. A No Operation capability is also provided during which the result is not stored in either location. This field also controls the value presented at the Y15-0 outputs. These outputs generally reflect the ALU result F, but for one of the instruction decodes, the outputs are

3-17

# **Arithmetic Logic Units**

03/11/94-LDS.101-G

5565905 0002437 4T3 📟

### 16-bit ALU Slice

driven by the A port value read from the register file. This provides the capability to read data from the register file while simultaneously performing an ALU operation. This is useful in applications such as postincrement address generation.

In addition to destination control, up or down shifting of both the register file and Q register load values are controlled by the I8-6 field. Each can be up or down shifted one position prior to storing in the destination register. The RAM0 or Q0 pins output the least significant bit of the value being stored for downshifts, and accept the bit to be stored in the least significant position for upshifts. Similarly, the RAM15 or Q15 pins output the most significant bit for upshifts, and accept the bit to be

stored in the most significant position for downshifts. Table 3 gives the various shift actions and data destinations controlled by the I8-6 inputs.

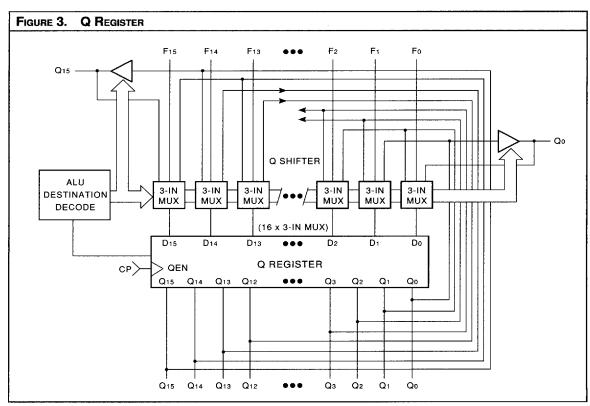

#### **O REGISTER**

The Q register is intended primarily for use as a separate working register for multiplication and division routines but it also serves as an accumulator or for temporary storage. The Q register is loaded via a multiplexer, which allows either up or downshift of the Q register contents, or an unshifted load of the Q register with the ALU result.

### STATUS OUTPUTS

The  $\overline{G}$  and  $\overline{P}$  outputs are low-true Carry-Generate and Carry-Propagate

signals. They are used in conjunction with an external carry-look-ahead generator when cascading L29C101 slices beyond 32 bits. The C(n+16) is the Carry-Out signal, which can be directly connected to the C(n) input of another L29C101 to implement a 32-bit system. The OVR output indicates two's complement overflow for addition and subtraction. The logical definitions of the  $\overline{G}$ ,  $\overline{P}$ , C(n+16), and OVR signals are given in Table 7.

The MSB of the ALU result (F15) is provided so that the sign bit may be examined easily. The Z output is used for zero detection and is high when all of the F output bits are low. It is an open drain output which may be wire OR'ed across multiple slices.

= Arithmetic Logic Units

# 16-bit ALU Slice

| TABLE 1. ALU SOURCE OPERAND CONTROL |                |                |        |       |       |        |  |

|-------------------------------------|----------------|----------------|--------|-------|-------|--------|--|

|                                     |                | Micr           | o Code |       | ALU S | Source |  |

|                                     |                |                |        | Octal | Ope   | rands  |  |

| Mnemonic                            | l <sub>2</sub> | l <sub>1</sub> | lo     | Code  | R     | s      |  |

| AQ                                  | L              | L              | L      | 0     | Α     | Q      |  |

| AB                                  | L              | L              | н      | 1     | Α     | В      |  |

| ZQ                                  | L              | н              | L      | 2     | 0     | Q      |  |

| ZB                                  | L              | н              | н      | 3     | 0     | В      |  |

| ZA                                  | Н              | L              | L      | 4     | 0     | A      |  |

| DA                                  | Н              | Ł              | Н      | 5     | D     | Α      |  |

| DQ                                  | Н              | Н              | L      | 6     | D     | Q      |  |

| DZ                                  | н              | Н              | Н      | 7     | D     | 0      |  |

| TABLE 2. ALU FUNCTION CONTROL |    |       |       |       |            |        |  |  |

|-------------------------------|----|-------|-------|-------|------------|--------|--|--|

|                               |    | Micro | o Coc | le    |            |        |  |  |

|                               |    |       |       | Octal | ALU        |        |  |  |

| Mnemonic                      | l5 | 14    | 13    | Code  | Function   | Symbol |  |  |

| ADD                           | L  | L     | L     | 0     | R Plus S   | R+S    |  |  |

| SUBR                          | L  | L     | Н     | 1     | S Minus R  | S-R    |  |  |

| SUBS                          | L  | н     | L     | 2     | R Minus S  | R-S    |  |  |

| OR                            | L  | н     | н     | 3     | RORS       |        |  |  |

| AND                           | Н  | L     | L     | 4     | R AND S    |        |  |  |

| NOTRS                         | н  | L     | Н     | 5     | FI AND S   |        |  |  |

| EXOR                          | Н  | н     | L     | 6     | R EX-OR S  |        |  |  |

| EXNOR                         | Н  | Н     | Н     | 7     | R EX-NOR S |        |  |  |

| TABLE 3. | AL | U D | EST  | NATION        | Contro | L             |                 |         |             |                  |                   |                |                  |

|----------|----|-----|------|---------------|--------|---------------|-----------------|---------|-------------|------------------|-------------------|----------------|------------------|

|          |    | Mic | ro C | ode           | RAM F  | unction       | Q-Reg. Function |         |             | RAM Shifter      |                   | Q Shifter      |                  |

| Mnemonic | 18 | 17  | 16   | Octal<br>Code | Shift  | Load          | Shift           | Load    | Y<br>Output | RAM <sub>0</sub> | RAM <sub>15</sub> | Qo             | <b>Q</b> 15      |

| QREG     | L  | L   | L    | 0             | ×      | None          | None            | F→Q     | F           | Х                | ×                 | ×              | Х                |

| NOP      | L  | L   | Н    | 1             | х      | None          | X               | None    | F           | Х                | X                 | ×              | ×                |

| RAMA     | L  | Н   | L    | 2             | None   | F→B           | Х               | None    | Α           | Х                | х                 | х              | х                |

| RAMF     | L  | Н   | Н    | 3             | None   | F→B           | х               | None    | F           | Х                | х                 | Х              | Х                |

| RAMQD    | н  | L   | L    | 4             | DOWN   | F/2 → B       | DOWN            | Q/2 → Q | F           | Fo               | IN <sub>15</sub>  | Q <sub>0</sub> | IN <sub>15</sub> |

| RAMD     | Н  | L   | Н    | 5             | DOWN   | F/2 → B       | х               | None    | F           | Fo               | IN15              | Qo             | х                |

| RAMQU    | Н  | Н   | L    | 6             | UP     | 2F → B        | UP              | 2Q → Q  | F           | INo              | F15               | ∤No            | Q15              |

| RAMU     | Н  | Н   | н    | 7             | UP     | 2F <b>→</b> B | х               | None    | F           | INo              | F15               | ×              | Q15              |

|       | I2-0 →                | 0         | 1         | 2      | 3          | 4       | 5                       | 6        | 7       |

|-------|-----------------------|-----------|-----------|--------|------------|---------|-------------------------|----------|---------|

| Octal | ALU                   |           | •         | ,      | ALU Source |         |                         |          |         |

| l5-3  | Function              | A, Q      | A, B      | O, Q   | О, В       | O, A    | D, A                    | D, Q     | D, O    |

| 0     | C(n) = L<br>R plus S  | A + Q     | A + B     | Q      | В          | Α       | D + A                   | D+Q      | D       |

|       | C(n) = H              | A + Q +1  | A + B + 1 | Q + 1  | B + 1      | A + 1   | D + A + 1               | D+Q+1    | D + 1   |

| 1     | C(n) = L<br>S minus R | Q – A – 1 | B A 1     | Q – 1  | B – 1      | A – 1   | A D 1                   | Q – D –1 | - D - 1 |

|       | C(n) = H              | Q – A     | B-A       | Q      | • в        | Α       | A – D                   | Q – D    | - D     |

| 2     | C(n) = L<br>R minus S | A-Q-1     | A – B – 1 | − Q −1 | -B-1       | - A - 1 | D-A-1                   | D-Q-1    | D – 1   |

|       | C(n) = H              | A-Q       | A – B     | - Q    | - B        | - A     | D – A                   | D-Q      | D       |

| 3     | RORS                  | A v Q     | A∨B       | Q      | В          | Α       | D v A                   | D∨Q      | D       |

| 4     | R AND S               | A ^ Q     | Ā A Q     | 0      | 0          | 0       | $\overline{D} \wedge A$ | Ū∧Q      | 0       |

| 5     | R AND S               | Ā∧Q       | A∧B       | Q      | В          | Α       | D ^ A                   | D∧Q      | 0       |

| 6     | R EX-OR S             | A∀Q       | A∀B       | Q      | В          | Α       | D∀A                     | DAO      | D       |

| 7     | R EX-NOR S            | Α∀Q       | Ā∀B       | ā      | Ē          | Ā       | D∀A                     | D∀Q      | D       |

3-19

= Arithmetic Logic Units

**5565905 0002439 276**

# 16-bit ALU Slice

| TABLE 5. ALU LOGIC MODE FUNCTIONS |          |              |  |  |  |  |

|-----------------------------------|----------|--------------|--|--|--|--|

| Octal 15-3, 12-0                  | Group    | Function     |  |  |  |  |

| 40                                |          | A ^ Q        |  |  |  |  |

| 41                                |          | A∧B          |  |  |  |  |

| 45                                | AND      | D∧A          |  |  |  |  |

| 46                                | 1        | D∧Q          |  |  |  |  |

| 30                                |          | A v Q        |  |  |  |  |

| 31                                |          | A∨B          |  |  |  |  |

| 35                                | OR       | D∨A          |  |  |  |  |

| 36                                |          | D∨A          |  |  |  |  |

| 60                                |          | A∀Q          |  |  |  |  |

| 61                                |          | A∀B          |  |  |  |  |

| 65                                | EX – OR  | D∀A          |  |  |  |  |

| 66                                |          | D∀Q          |  |  |  |  |

| 70                                |          | <u>A ∀ Q</u> |  |  |  |  |

| 71                                |          | Ā∀B          |  |  |  |  |

| 75                                | EX – NOR | D∀A          |  |  |  |  |

| 76                                |          | D∀Q          |  |  |  |  |

| 72                                |          | Q            |  |  |  |  |

| 73                                |          | Ã            |  |  |  |  |

| 74                                | INVERT   | Ā            |  |  |  |  |

| 77                                |          | D            |  |  |  |  |

| 62                                |          | Q            |  |  |  |  |

| 63                                |          | В            |  |  |  |  |

| 64                                | PASS     | Α            |  |  |  |  |

| 67                                |          | D            |  |  |  |  |

| 32                                |          | Q            |  |  |  |  |

| 33                                |          | В            |  |  |  |  |

| 34                                | PASS     | A            |  |  |  |  |

| 37                                |          | D            |  |  |  |  |

| 42                                |          | 0            |  |  |  |  |

| 43                                |          | 0            |  |  |  |  |

| 44                                | ZERO     | 0            |  |  |  |  |

| <b>4</b> 7                        |          | 0            |  |  |  |  |

| 50                                |          | Ā∧Q          |  |  |  |  |

| 51                                |          | Ā∧B          |  |  |  |  |

| 55                                | MASK     | Ō∧A          |  |  |  |  |

| 56                                |          | Ū∧Q          |  |  |  |  |

| TABLE 6. ALU ARITHMETIC MODE FUNCTIONS |             |           |             |           |  |  |  |

|----------------------------------------|-------------|-----------|-------------|-----------|--|--|--|

| Octal                                  | C(n) = 0    | (Low)     | C(n) =      | 1 (High)  |  |  |  |

| 12-0                                   | Group       | Function  | Group       | Function  |  |  |  |

| 00                                     |             | A + Q     |             | A + Q + 1 |  |  |  |

| 01                                     |             | A + B     | ADD Plus    | A + B + 1 |  |  |  |

| 05                                     | ADD         | D + A     | One         | D + A + 1 |  |  |  |

| 06                                     |             | D + Q     |             | D+Q+1     |  |  |  |

| 02                                     |             | Q         |             | Q + 1     |  |  |  |

| 03                                     |             | В         |             | B + 1     |  |  |  |

| 04                                     | PASS        | Α         | Increment   | A + 1     |  |  |  |

| 07                                     |             | D         |             | D + 1     |  |  |  |

| 12                                     |             | Q – 1     |             | α         |  |  |  |

| 13                                     |             | B – 1     |             | В         |  |  |  |

| 14                                     | Decrement   | A – 1     | PASS        | Α         |  |  |  |

| 27                                     |             | D – 1     |             | D         |  |  |  |

| 22                                     |             | - Q -1    |             | – Q       |  |  |  |

| 23                                     |             | - B - 1   | 2's Comp.   | – B       |  |  |  |

| 24                                     | 1's Comp.   | - A - 1   | (Negate)    | - A       |  |  |  |

| 17                                     |             | – D − 1   |             | – Đ       |  |  |  |

| 10                                     |             | Q – A –1  |             | Q – A     |  |  |  |

| 11                                     |             | B – A – 1 |             | B A       |  |  |  |

| 15                                     |             | A – D – 1 |             | A – D     |  |  |  |

| 16                                     | Subtract    | Q-D-1     | Subtract    | Q-D       |  |  |  |

| 20                                     | (1's Comp.) | A – Q –1  | (2's Comp.) | A-Q       |  |  |  |

| 21                                     |             | A-B-1     |             | A – B     |  |  |  |

| 25                                     |             | D – A – 1 |             | D A       |  |  |  |

| 26                                     |             | D-Q-1     |             | D – Q     |  |  |  |

| TABLE 7. | Logic Fun | ICTIONS FOR CARR | Y AND OVERFLOW CONDITIONS                            |               |           |

|----------|-----------|------------------|------------------------------------------------------|---------------|-----------|

| l5-3     | Function  | P                | G                                                    | C (n+16)      | OVR       |

| 0        | R + S     | Po • P1 ··· P15  | G15 + P15 G14 + P15 P14 G13 + ···                    | C16           | C16 ∀ C15 |

| 1        | S – R     |                  | Same as R + S equations, but substitute Ri for Ri in | n definitions |           |

| 2        | R-S       |                  | Same as R + S equations, but substitute Si for Si in | n definitions |           |

| 3        | RVS       |                  |                                                      |               |           |

| 4        | R∧S       |                  |                                                      |               |           |

| 5        | R ^ S     | HIGH             | HIGH                                                 | LOW           | LOW       |

| 6        | Ā∀S       |                  |                                                      |               |           |

| 7        | R∀S       |                  |                                                      |               |           |

= Arithmetic Logic Units

03/11/94-LDS.101-G

5565905 0002440 T98 📟

# 16-bit ALU Slice

| Aximum Ratings Above which useful life may be impaired (Notes 1, 2, 3, 8) |                  |  |  |  |  |  |

|---------------------------------------------------------------------------|------------------|--|--|--|--|--|

| Storage temperature                                                       | 65°C to +150°C   |  |  |  |  |  |

| Operating ambient temperature                                             | 55°C to +125°C   |  |  |  |  |  |

| Vcc supply voltage with respect to ground                                 | 0.5 V to +7.0 V  |  |  |  |  |  |

| Input signal with respect to ground                                       | 3.0 V to +7.0 V  |  |  |  |  |  |

| Signal applied to high impedance output                                   | –3.0 V to +7.0 V |  |  |  |  |  |

| Output current into low outputs                                           | 25 mA            |  |  |  |  |  |

| Latchup current                                                           | > 400 mA         |  |  |  |  |  |

| OPERATING CONDITIONS To meet specified electrical and switching characteristics |                             |                                                            |  |  |  |  |  |  |  |

|---------------------------------------------------------------------------------|-----------------------------|------------------------------------------------------------|--|--|--|--|--|--|--|

| Mode                                                                            | Temperature Range (Ambient) | Supply Voltage                                             |  |  |  |  |  |  |  |

| Active Operation, Commercial                                                    | 0°C to +70°C                | $4.75 \text{ V} \le \text{V} \text{cc} \le 5.25 \text{ V}$ |  |  |  |  |  |  |  |

| Active Operation, Military                                                      | –55°C to +125°C             | $4.50 \text{ V} \le \text{V}_{CC} \le 5.50 \text{ V}$      |  |  |  |  |  |  |  |

| ELECTRICAL CHARACTERISTICS Over Operating Conditions (Note 4) |                        |                                               |     |     |             |      |  |  |

|---------------------------------------------------------------|------------------------|-----------------------------------------------|-----|-----|-------------|------|--|--|

| Symbol                                                        | Parameter              | Test Condition                                | Min | Тур | Max         | Unit |  |  |

| <b>V</b> OH                                                   | Output High Voltage    | Vcc = Min., IoH = -2.0 mA                     | 2.4 |     |             | ٧    |  |  |

| <b>V</b> OL                                                   | Output Low Voltage     | VCC = Min., IOL = 8.0 mA                      |     |     | 0.4         | V    |  |  |

| <b>V</b> 1H                                                   | Input High Voltage     |                                               | 2.0 |     | <b>V</b> cc | ٧    |  |  |

| <b>V</b> IL                                                   | Input Low Voltage      | (Note 3)                                      | 0.0 |     | 0.8         | V    |  |  |

| lix                                                           | Input Current          | Ground ≤ ViN ≤ VCC (Note 12)                  |     |     | ±20         | μA   |  |  |

| loz                                                           | Output Leakage Current | Ground ≤ <b>V</b> OUT ≤ <b>V</b> CC (Note 12) |     |     | ±20         | μΑ   |  |  |

| lcc1                                                          | Vcc Current, Dynamic   | (Notes 5, 6)                                  |     | 15  | 30          | mA   |  |  |

| ICC2                                                          | Vcc Current, Quiescent | (Note 7)                                      |     |     | 5.0         | mA   |  |  |

= Arithmetic Logic Units

5565905 0002441 924 🖿

# 16-bit ALU Slice

# SWITCHING CHARACTERISTICS — COMMERCIAL OPERATING RANGE (0°C to +70°C) Note 9 (ns)

| OUTPUT ENABLE/DISABLE TIMES (Note 11) |       |        |      |      |  |  |

|---------------------------------------|-------|--------|------|------|--|--|

| Device                                | Input | Output | tENA | tois |  |  |

| L29C101-35                            | ŌĒ    | Y      | 20   | 17   |  |  |

| CYCLE TIME AND CLOCK CHARACTERISTICS                                           |        |

|--------------------------------------------------------------------------------|--------|

| Read – Modify – Write Cycle (from selection of A, B registers to end of cycle) | 35 ns  |

| Maximum Clock Frequency to shift Q (50% duty cycle, I = 432 or 632)            | 30 MHz |

| Minimum Clock LOW Time                                                         | 15 ns  |

| Minimum Clock HIGH Time                                                        | 20 ns  |

| COMBINATIONAL PROPAGATION DELAYS (Note 13) |    |     |         |      |              |     |               |           |

|--------------------------------------------|----|-----|---------|------|--------------|-----|---------------|-----------|

| To Output From Input                       | Υ  | F15 | C (n16) | G, P | F = 0        | OVR | RAM0<br>RAM15 | Q0<br>Q15 |

| A,B Address                                | 46 | 43  | 35      | 37   | 49           | 41  | 40            | _         |

| D                                          | 34 | 34  | 27      | 27   | 40           | 29  | 33            | _         |

| C(n)                                       | 27 | 24  | 20      | _    | 28           | 23  | 28            |           |

| 10, 11, 12                                 | 40 | 40  | 33      | 30   | 42           | 32  | 35            | _         |

| 13, 14, 15                                 | 41 | 38  | 32      | 28   | 40           | 36  | 38            | _         |

| l6, I7, I8                                 | 20 | _   | _       | _    | <del>-</del> | _   | 26            | 26        |

| A bypass ALU<br>(I = 2XX)                  | 26 | _   | _       | _    | _            |     |               |           |

| Clock                                      | 38 | 34  | 30      | 30   | 36           | 32  | 34            | 25        |

| SETUP AND HOLD TIMES RELATIVE TO CLOCK INPUT (Note 13) |                            |                          |                            |                          |  |  |  |

|--------------------------------------------------------|----------------------------|--------------------------|----------------------------|--------------------------|--|--|--|

| Input                                                  | Setup Time<br>Before H → L | Hold Time<br>After H → L | Setup Time<br>Before L → H | Hold Time<br>After L → H |  |  |  |

| A,B Source Address (Notes 15, 16)                      | 24                         | 3                        | 35                         | _                        |  |  |  |

| B Destination Address (Note 14)                        | 24                         | Do Not Change            |                            | 0                        |  |  |  |

| D                                                      | <u> </u>                   | _                        | 26                         | 0                        |  |  |  |

| C(n)                                                   | <u>—</u>                   | <u>—</u>                 | 16                         | 0                        |  |  |  |

| ło, l1, l2                                             |                            | _                        | 30                         | 0                        |  |  |  |

| 13, 14, 15                                             | _                          | _                        | 31                         | 0                        |  |  |  |

| I6, I7, I8 (Note 14)                                   | 10                         | Do Not Change            |                            | 0                        |  |  |  |

| RAMo, RAM15, Qo, Q15                                   | _                          | <u> </u>                 |                            | 0                        |  |  |  |

= Arithmetic Logic Units

### 16-bit ALU Slice

### SWITCHING CHARACTERISTICS — MILITARY OPERATING RANGE (-55°C to +125°C) Note 9 (ns)

| OUTPUT ENABLE/DISABLE TIMES (Note 11) |       |        |      |      |  |  |

|---------------------------------------|-------|--------|------|------|--|--|

| Device                                | Input | Output | tENA | tDIS |  |  |

| L29C101-45                            | ŌĒ    | Y      | 23   | 20   |  |  |

| CYCLE TIME AND CLOCK CHARACTERISTICS                                           |        |  |  |  |  |  |

|--------------------------------------------------------------------------------|--------|--|--|--|--|--|

| Read – Modify – Write Cycle (from selection of A, B registers to end of cycle) | 45ns   |  |  |  |  |  |

| Maximum Clock Frequency to shift Q (50% duty cycle, I = 432 or 632)            | 25 MHz |  |  |  |  |  |

| Minimum Clock LOW Time                                                         | 20 ns  |  |  |  |  |  |

| Minimum Clock HIGH Time                                                        | 20 ns  |  |  |  |  |  |

| COMBINATIONAL PROPAGA     |    |     | 1       |      | T     |     | DANA          |           |

|---------------------------|----|-----|---------|------|-------|-----|---------------|-----------|

| To Output From Input      | Υ  | F15 | C (n16) | G, P | F = 0 | OVR | RAM0<br>RAM15 | Q0<br>Q15 |

| A,B Address               | 52 | 50  | 40      | 38   | 48    | 46  | 43            | _         |

| D                         | 37 | 36  | 30      | 32   | 40    | 32  | 35            | _         |

| C(n)                      | 30 | 28  | 24      | _    | 29    | 27  | 30            | _         |

| lo, l1, l2                | 44 | 43  | 36      | 34   | 46    | 38  | 41            | _         |

| l3, l4, l5                | 47 | 44  | 35      | 35   | 45    | 44  | 45            | _         |

| l6, l7, <b>l</b> 8        | 22 | _   |         | _    |       |     | 30            | 30        |

| A bypass ALU<br>(I = 2XX) | 27 | _   | _       |      | _     | _   | _             | _         |

| Clock                     | 44 | 39  | 32      | 32   | 40    | 36  | 34            | 28        |

| SETUP AND HOLD TIMES RELATIVE TO CLOCK INPUT (Note 13) |                            |                          |                            |                          |  |  |  |

|--------------------------------------------------------|----------------------------|--------------------------|----------------------------|--------------------------|--|--|--|

| Input                                                  | Setup Time<br>Before H → L | Hold Time<br>After H → L | Setup Time<br>Before L → H | Hold Time<br>After L → H |  |  |  |

| A,B Source Address (Notes 15, 16)                      | 22                         | 3                        | 40                         |                          |  |  |  |

| B Destination Address (Note 14)                        | 22                         | Do Not Change            |                            | 0                        |  |  |  |

| D                                                      | _                          | <del>_</del>             | 30                         | 0                        |  |  |  |

| C(n)                                                   | <del>_</del>               |                          | 20                         | 0                        |  |  |  |

| lo, l1, l2                                             | _                          | _                        | 37                         | 0                        |  |  |  |

| 13, 14, 15                                             |                            | _                        | 36                         | 0                        |  |  |  |

| l6, l7, l8 (Note 14)                                   | 10                         | Do Not Change            |                            | 0                        |  |  |  |

| RAMo, RAM15, Qo, Q15                                   |                            | _                        | 12                         | 0                        |  |  |  |

= Arithmetic Logic Units

### 16-bit ALU Slice

### **NOTES**

- 1. Maximum Ratings indicate stress specifications only. Functional operation of these products at values beyond those indicated in the Operating Conditions table is not implied. Exposure to maximum rating conditions for extended periods may affect reliability.

- 2. The products described by this specification include internal circuitry designed to protect the chip from damaging substrate injection currents and accumulations of static charge. Nevertheless, conventional precautions should be observed during storage, handling, and use of these circuits in order to avoid exposure to excessive electrical stress values.

- 3. This device provides hard clamping of transient undershoot and overshoot. Input levels below ground or above VCC will be clamped beginning at -0.6 V and VCC +0.6 V. The device can withstand indefinite operation with inputs in the range of -0.5 V to +7.0 V. Device operation will not be adversely affected, however, input current levels will be well in excess of 100 mA.

- 4. Actual test conditions may vary from those designated but operation is guaranteed as specified.

- 5. Supply current for a given application can be accurately approximated by:

$\frac{NCV^2F}{4}$

where

N = total number of device outputs

C = capacitive load per output

V = supply voltage

F = clock frequency

- 6. Tested with all outputs changing every cycle and no load, at a 5 MHz clock rate.

- 7. Tested with all inputs within 0.1 V of VCC or Ground, no load.

- 8. These parameters are guaranteed but not 100% tested.

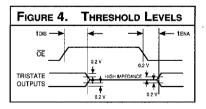

9. AC specifications are tested with input transition times less than 3 ns, output reference levels of 1.5 V (except tENA/tDIS test), and input levels of nominally 0 to 3.0 V. Output loading may be a resistive divider which provides for specified IOH and IOL at an output voltage of VOH min and VOL max respectively. Alternatively, a diode bridge with upper and lower current sources of IOH and IOL respectively, and a balancing voltage of 1.5 V may be used. Parasitic capacitance is 30 pF minimum, and may be distributed. For tENABLE and tDISABLE measurements, the load current is increased to 10 mA to reduce the RC delay component of the measurement.

This device has high-speed outputs capable of large instantaneous current pulses and fast turn-on/turn-off times. As a result, care must be exercised in the testing of this device. The following measures are recommended:

- a. A 0.1  $\mu$ F ceramic capacitor should be installed between **V**CC and Ground leads as close to the Device Under Test (DUT) as possible. Similar capacitors should be installed between device **V**CC and the tester common, and device ground and tester common.

- b. Ground and VCC supply planes must be brought directly to the DUT socket or contactor fingers.

- c. Input voltages should be adjusted to compensate for inductive ground and VCC noise to maintain required DUT input levels relative to the DUT ground pin.

- 10. Each parameter is shown as a minimum or maximum value. Input requirements are specified from the point of view of the external system driving the chip. Setup time, for example, is specified as a minimum since the external system must supply at least that much time to meet the worst-case requirements of all parts. Responses from the internal circuitry are specified from

3-24

the point of view of the device. Output delay, for example, is specified as a maximum since worst-case operation of any device always provides data within that time.

- 11. Transition is measured ±200 mV from steady-state voltage with specified loading.

- 12. These parameters are only tested at the high temperature extreme, which is the worst case for leakage current.

- 13. A dash indicates a propagation delay or setup time constraint that does not exist.

- 14. Certain signals must be stable during the entire clock LOW time to avoid erroneous operation. This is indicated by the phrase "do not change."

- 15. Source addresses must be stable prior to the clock H→L transition to allow time to access the source data before the latches close. The A address may then be changed. The B address could be changed if it is not a destination; i.e., if data is not being written back into the RAM. Normally A and B are not changed during the clock LOW time.

- 16. The setup time prior to the clock  $L\rightarrow H$  transition is to allow time for data to be accessed, passed through the ALU, and returned to the RAM. It includes all the time from stable A and B addresses to the clock  $L\rightarrow H$  transition, regardless of when the clock  $H\rightarrow L$  transition occurs.

# Arithmetic Logic Units

### 16-bit ALU Slice

= Arithmetic Logic Units