# Glass/Ceramic Numeric and Hexadecimal Displays for Industrial Applications

# **Technical Data**

4N51 4N52 4N53 4N54

#### **Features**

- Three Character Options Numeric, Hexadecimal, Over Range

- 4 x 7 Dot Matrix Character

- Performance Guaranteed Over Temperature

- High Temperature Stabilized

- Solder Dipped Leads

- Memory Latch/Decoder/ Driver

TTL Compatible

- Categorized for Luminous Intensity

## **Description**

These standard red solid state displays have a 7.4 mm (0.29 inch) dot matrix character and an on-board IC with data memory latch/decoder and LED drivers in a glass/ceramic package. These devices utilize a solder glass frit seal.

The 4N51 numeric display decodes positive 8421 BCD logic inputs into characters 0-9, a "–" sign, a test pattern, and four blanks in the invalid BCD states. The unit employs a right-hand decimal point.

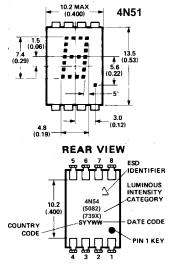

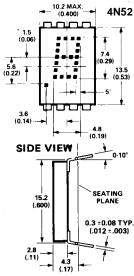

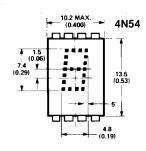

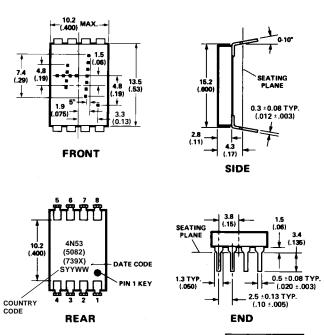

## **Package Dimensions\***

|                    | END VIEW            |   |

|--------------------|---------------------|---|

| _<br>SEATING       | 3.8 (.15) 1.5 (.06) |   |

| PLANE              | 3.4 (.135)          |   |

|                    |                     |   |

| 1.3 TYP.<br>(.050) | 0.5 ±0.08 TYI       | • |

| _                  | → 2.5 ±0.13 TYP.    |   |

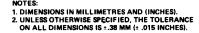

|     | FUNCTION                |                          |  |  |  |

|-----|-------------------------|--------------------------|--|--|--|

| PIN | 4N51<br>4N52<br>NUMERIC | 4N54<br>HEXA-<br>DECIMAL |  |  |  |

| 1   | Input 2                 | Input 2                  |  |  |  |

| 2   | Input 4                 | Input 4                  |  |  |  |

| 3   | Input 8                 | Input 8                  |  |  |  |

| 4   | Decimal point           | Blanking<br>control      |  |  |  |

| 5   | Latch<br>enable         | Latch<br>enable          |  |  |  |

| 6   | Ground                  | Ground                   |  |  |  |

| 7   | V <sub>CC</sub>         | V <sub>CC</sub>          |  |  |  |

| 8   | Input 1                 | Input 1                  |  |  |  |

### NOTES:

- Dimensions in millimetres and (inches).

- 2. Unless otherwise specified, the tolerance

- on all dimensions is ±.38mm (±.015")

3. Digit center line is ±.25mm (±.01")

- from package center line.

4. Solder dipped leads.

- Sée over range package drawing for HP standard marking.

The 4N52 is the same as the 4N51 except that the decimal point is located on the left side of the digit.

In place of the decimal point an input is provided for blanking the display (all LEDs off), without losing the contents of the memory.

The 4N54 hexadecimal display decodes positive 8421 logic inputs into 16 states, 0-9 and A-F.

The 4N53 is a "± 1." overrange display, including a right-hand decimal point.

## **Absolute Maximum Ratings\***

| Description                                        | Symbol                         | Min. | Max.     | Unit                 |

|----------------------------------------------------|--------------------------------|------|----------|----------------------|

| Storage Temperature, Ambient                       | $T_{\mathrm{S}}$               | -65  | +125     | $^{\circ}\mathrm{C}$ |

| Operating Temperature, Ambient <sup>[1,2]</sup>    | $T_{A}$                        | -55  | +100     | $^{\circ}\mathrm{C}$ |

| Supply Voltage <sup>[3]</sup>                      | $V_{\rm CC}$                   | -0.5 | +7.0     | V                    |

| Voltage Applied to Input Logic, dp and Enable Pins | $V_{\rm I},V_{ m DP},V_{ m E}$ | -0.5 | $V_{CC}$ | V                    |

| Voltage Applied to Blanking Input <sup>[7]</sup>   | $V_{\rm B}$                    | -0.5 | $V_{CC}$ | V                    |

| Maximum Solder Temperature at 1.59 mm (0.062 inch) |                                |      | 260      | $^{\circ}\mathrm{C}$ |

| Below Seating Plane; t ≤ 5 Seconds                 |                                |      |          |                      |

# **Recommended Operating Conditions\***

| Description                                                         | Symbol         | Min. | Nom. | Max. | Unit |

|---------------------------------------------------------------------|----------------|------|------|------|------|

| Supply Voltage                                                      | $V_{CC}$       | 4.5  | 5.0  | 5.5  | V    |

| Operating Temperature, Ambient <sup>[1,2]</sup>                     | T <sub>A</sub> | -55  |      | +100 | °C   |

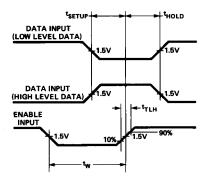

| Enable Pulse Width                                                  | $t_{ m W}$     | 100  |      |      | nsec |

| Time Data Must Be Held Before Positive<br>Transition of Enable Line | $ m t_{SETUP}$ | 50   |      |      | nsec |

| Time Data Must Be Held After Positive<br>Transition of Enable Line  | $t_{ m HOLD}$  | 50   |      |      | nsec |

| Enable Pulse Rise Time                                              | $t_{ m TLH}$   |      |      | 200  | nsec |

$<sup>*{\</sup>tt JEDEC}$  Registered Data.

## **Electrical/Optical Characteristics\***

$T_A = -55$ °C to +100°C, unless otherwise specified

| Description                                                 | Symbol                 | <b>Test Conditions</b>                                   | Min. | Typ.[4] | Max.                 | Unit   |

|-------------------------------------------------------------|------------------------|----------------------------------------------------------|------|---------|----------------------|--------|

| Supply Current                                              | $I_{CC}$               | $V_{CC} = 5.5 \text{ V}$                                 |      | 112     | 170                  | mA     |

| Power Dissipation                                           | $P_{T}$                | (Characters "5." or "B")                                 |      | 560     | 935                  | mW     |

| Luminous Intensity per LED (Digit Average) <sup>[5,6]</sup> | $I_{\rm v}$            | $V_{CC} = 5.0 \text{ V}, T_A = 25^{\circ}\text{C}$       | 40   | 85      |                      | μcd    |

| Logic Low-Level Input Voltage                               | V <sub>IL</sub>        | $V_{CC} = 4.5 \text{ V}$                                 |      |         | 0.8                  | V      |

| Logic High-Level Input Voltage                              | V <sub>IH</sub>        |                                                          | 2.0  |         |                      | V      |

| Enable Low-Voltage;<br>Data Being Entered                   | $V_{\mathrm{EL}}$      |                                                          |      |         | 0.8                  | V      |

| Enable High-Voltage;<br>Data Not Being Entered              | $V_{\rm EH}$           |                                                          | 2.0  |         |                      | V      |

| Blanking Low-Voltage;<br>Display Not Blanked <sup>[7]</sup> | $V_{ m BL}$            |                                                          |      |         | 0.8                  | V      |

| Blanking High-Voltage;<br>Display Blanked <sup>[7]</sup>    | $V_{ m BH}$            |                                                          | 3.5  |         |                      | V      |

| Blanking Low-Level Input<br>Current <sup>[7]</sup>          | $I_{ m BL}$            | $V_{CC} = 5.5 \text{ V}, V_{BL} = 0.8 \text{ V}$         |      |         | 50                   | μА     |

| Blanking High-Level Input<br>Current <sup>[7]</sup>         | $I_{ m BH}$            | $V_{\rm CC} = 5.5 \text{ V}, V_{\rm BH} = 4.5 \text{ V}$ |      |         | 1.0                  | mA     |

| Logic Low-Level Input Current                               | $I_{\mathrm{IL}}$      | $V_{\rm CC} = 5.5 \text{ V}, V_{\rm IL} = 0.4 \text{ V}$ |      |         | -1.6                 | mA     |

| Logic High-Level Input Current                              | $I_{\mathrm{IH}}$      | $V_{CC} = 5.5 \text{ V}, V_{IH} = 2.4 \text{ V}$         |      |         | +100                 | μΑ     |

| Enable Low-Level Input Current                              | $I_{EL}$               | $V_{\rm CC} = 5.5 \text{ V}, V_{\rm EL} = 0.4 \text{ V}$ |      |         | -1.6                 | mA     |

| Enable High-Level Input<br>Current                          | $I_{EH}$               | $V_{CC} = 5.5 \text{ V}, V_{EH} = 2.4 \text{ V}$         |      |         | +130                 | μА     |

| Peak Wavelength                                             | $\lambda_{	ext{PEAK}}$ | $T_A = 25$ °C                                            |      | 655     |                      | nm     |

| Dominant Wavelength <sup>[8]</sup>                          | $\lambda_{ m d}$       | $T_A = 25$ °C                                            |      | 640     |                      | nm     |

| Weight**                                                    |                        |                                                          |      | 1.0     |                      | gm     |

| Leak Rate                                                   |                        |                                                          |      |         | 5 x 10 <sup>-8</sup> | cc/sec |

#### Notes

- 1. Nominal thermal resistance of a display mounted in a socket which is soldered into a printed circuit board:  $\Theta_{JA} = 50^{\circ}\text{C/W}$ ;  $\Theta_{JC} = 15^{\circ}\text{C/W}$ .

- 2.  $\Theta_{CA}$  of a mounted display should not exceed 35°C/W for operation up to  $T_A = +100$ °C.

- 3. Voltage values are with respect to device ground, pin 6.

- 4. All typical values at  $V_{CC}$  = 5.0 Volts,  $T_{A}$  = 25 °C.

- 5. These displays are categorized for luminous intensity with the intensity category designated by a letter located on the back of the display contiguous with the Hewlett-Packard logo marking.

- 6. The luminous intensity at a specific ambient temperature,  $I_v(T_A)$ , may be calculated from this relationship:  $I_v(T_A) = I_{v(25^{\circ}C)}(0.985) \,^{(T_A-25^{\circ}C)}$ .

- 7. Applies only to 4N54.

- 8. The dominant wavelength,  $\lambda_d$ , is derived from the CIE chromaticity diagram and represents the single wavelength which defines the color of the device.

<sup>\*</sup>JEDEC Registered Data.

<sup>\*\*</sup>Non-Registered Data.

Figure 1. Timing Diagram of 4N51-4N54 Series Logic.

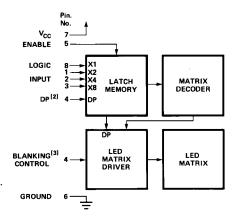

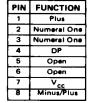

Figure 2. Block Diagram of 4N51-4N54 Series Logic.

|    | TRUTH TABLE    |                    |                |                   |                                            |  |  |  |  |

|----|----------------|--------------------|----------------|-------------------|--------------------------------------------|--|--|--|--|

|    | BCD D          |                    |                | 4N51 AND 4N52     | 4N54                                       |  |  |  |  |

| X8 | X <sub>4</sub> | X <sub>2</sub>     | X <sub>1</sub> |                   |                                            |  |  |  |  |

| L  | L              | L                  | L              | 0                 | Ü                                          |  |  |  |  |

| L  | L              | L                  | н              | -                 |                                            |  |  |  |  |

| L  | L              | н                  | L              |                   |                                            |  |  |  |  |

| L  | L              | н                  | н              | 3                 |                                            |  |  |  |  |

| L  | н              | L                  | L              | 4                 | Lij                                        |  |  |  |  |

| L  | н              | L                  | н              | 5                 | 5                                          |  |  |  |  |

| L  | н              | Н                  | L              | 6                 | 6                                          |  |  |  |  |

| L  | Н              | Н                  | Н              |                   |                                            |  |  |  |  |

| н  | L              | L                  | L              | 8                 | 8                                          |  |  |  |  |

| н  | L              | L                  | Н              | 9                 | 9                                          |  |  |  |  |

| Н  | L              | н                  | L              | . 🗒               | Ĥ                                          |  |  |  |  |

| н  | L              | н                  | н              | (BLANK)           | B                                          |  |  |  |  |

| н  | н              | L                  | L              | (BLANK)           | l <u></u>                                  |  |  |  |  |

| Н  | н              | L                  | н              | .,.,              | D                                          |  |  |  |  |

| н  | н              | Н                  | L              | (BLANK)           | E                                          |  |  |  |  |

| н  | н              | Ξ                  | н              | (BLANK)           | F                                          |  |  |  |  |

| DE | CIMAL          | PT. <sup>[2]</sup> | ON<br>OFF      |                   | V <sub>DP</sub> = L<br>V <sub>DP</sub> = H |  |  |  |  |

| EN | NABLE [1       | 1                  |                | D DATA            | V <sub>E</sub> = L                         |  |  |  |  |

| ВЦ | ANKIN          | 3 [3]              | DISP           | LAY-ON<br>LAY-OFF | V <sub>B</sub> = L                         |  |  |  |  |

### Notes:

- H = Logic High; L = Logic Low. With the enable input at logic high changes in BCD input logic levels or D.P. input have no effect upon display memory, displayed character, or D.P.

- The decimal point input, DP, pertains only to the 4N51 and 4N52 displays.

- The blanking control input, B, pertains only to the 4N54 hexadecimal display. Blanking input has no effect upon display memory.

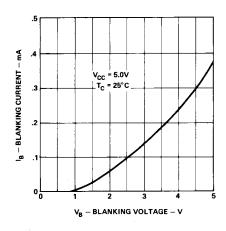

Figure 3. Typical Blanking Control Current vs. Voltage for 4N54.

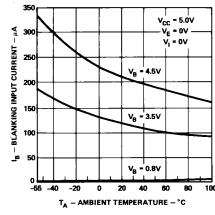

Figure 4. Typical Blanking Control Input Current vs. Ambient Temperature for 4N54.

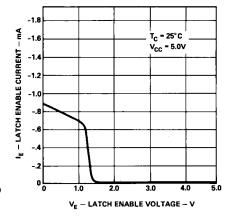

Figure 5. Typical Latch Enable Input Current vs. Voltage.

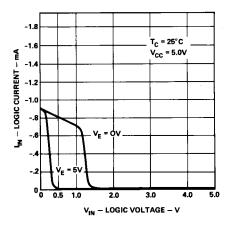

Figure 6. Typical Logic and Decimal Point Input Current vs. Voltage.

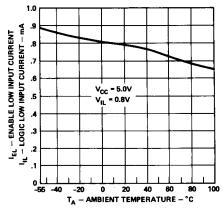

Figure 7. Typical Logic and Enable Low Input Current vs. Ambient Temperature.

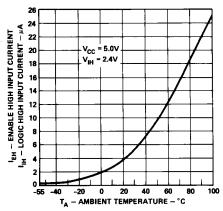

Figure 8. Typical Logic and Enable High Input Current vs. Ambient Temperature.

# Operational Considerations

#### **Electrical**

The 4N51-4N54 series devices use a modified 4 x 7 dot matrix of light emitting diodes (LEDs) to display decimal/hexadecimal numeric information. The LEDs are driven by constant current drivers. BCD information is accepted by the display memory when the enable line is at logic low and the data is latched when the enable is at logic high. To avoid the latching of erroneous information, the enable pulse rise time should not exceed 200 nanoseconds. Using the enable pulse width and data setup and hold times listed in the Recommended Operating Conditions allows data to be clocked into an array of displays at a 6.7 MHz rate.

The blanking control input on the 4N54 display blanks (turns off) the displayed hexadecimal information without disturbing the contents of display memory. The display is blanked at a

minimum threshold level of 3.5 volts. This may be easily achieved by using an open collector TTL gate and a pull-up resistor. For example, (1/6) 7416 hexinverter buffer/driver and a 120 ohm pull-up resistor will provide sufficient drive to blank eight displays. The size of the blanking pull-up resistor may be calculated from the following formula, where N is the number of digits:

$$R_{blank} = (V_{CC} - 3.5 \text{ V})/[\text{N} (1.0 \text{ mA})]$$

The decimal point input is active low true and this data is latched into the display memory in the same fashion as the BCD data. The decimal point LED is driven by the on-board IC.

The ESD susceptibility of the IC devices is Class A of MIL-STD-883 or Class 2 of DOD-STD-1686 and DOD-HDBK-263.

#### Mechanical

4N51-4N54 series displays are hermetically tested for use in environments which require a high reliability device. These displays are designed and tested to meet a helium leak rate of  $5 \times 10^{-8}$  cc/sec and a fluorocarbon gross leak bubble test.

These displays may be mounted by soldering directly to a printed circuit board or inserted into a socket. The lead-to-lead pin spacing is 2.54 mm (0.100 inch) and the lead row spacing is 15.24 mm (0.600 inch). These displays may be end stacked with 2.54 mm (0.100 inch) spacing between outside pins of adjacent displays. Sockets such as Augat 324 AG2D (3 digits) or Augat 508 (one digit, right angle mounting) may be used.

The primary thermal path for power dissipation is through the device leads. Therefore, to insure reliable operation up to an ambient temperature of +100°C, it is important to maintain a case-to-ambient thermal resistance of less than 35°C/watt as measured on top of display pin 3.

#### **Soldering**

For information on soldering and post solder cleaning, see Application Note 1027 Soldering LED Components.

#### **Preconditioning**

4N51-4N54 series displays are 100% preconditioned by 24 hour storage at  $125\,^{\circ}$ C.

#### **Contrast Enhancement**

The 4N51-4N54 displays have been designed to provide the maximum possible ON/OFF contrast when placed behind an appropriate contrast enhancement filter. For further information see Agilent Application Note 1015, Contrast Enhancement for LED Displays.

# **Solid State Over Range Display**

For display applications requiring a  $\pm$  , 1, or decimal point designation, the 4N53 over range display is available. This display module comes in the same package as the 4N51-4N54 series numeric display and is completely compatible with it.

## **Package Dimensions\***

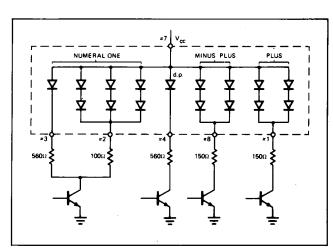

Figure 9. Typical Driving Circuit.

#### TRUTH TABLE

| CHARACTER     | PIN |     |   |   |  |

|---------------|-----|-----|---|---|--|

|               | 1   | 2,3 | 4 | 8 |  |

| +             | Н   | X   | Х | Н |  |

|               | L   | X   | X | Н |  |

| 1             | Х   | Н   | X | Х |  |

| Decimal Point | X   | Х   | Ĥ | X |  |

| Blank         | L   | L   | L | L |  |

NOTES: L: Line switching transistor in Figure 9 cutoff.

H: Line switching transistor in Figure 9 saturated.

X: 'Don't care'

<sup>\*</sup>JEDEC registered data

## **Electrical/Optical Characteristics\***

**4N53** ( $T_A = -55$  °C to +100 °C, Unless Otherwise Specified)

| Description                | Symbol              | Test Conditions               | Min | Тур | Max | Unit |

|----------------------------|---------------------|-------------------------------|-----|-----|-----|------|

| Forward Voltage per LED    | $V_{\mathrm{F}}$    | $I_F = 10 \text{ mA}$         |     | 1.6 | 2.0 | V    |

| Power Dissipation          | $P_{T}$             | $I_F = 10$ mA, all diodes lit |     | 280 | 320 | mW   |

| Luminous Intensity per LED | $I_{\mathrm{F}}$    | $I_F = 6 \text{ mA}$          | 40  | 85  |     |      |

| (Digit Average)            |                     | $T_C = 25$ °C                 |     |     |     | μcd  |

| Peak Wavelength            | $\lambda_{ m peak}$ | $T_C = 25$ °C                 |     | 655 |     | nm   |

| Dominant Wavelength        | $\lambda_{ m d}$    | $T_C = 25$ °C                 |     | 640 |     | nm   |

| Weight**                   |                     |                               |     | 1.0 |     | gm   |

# **Recommended Operating Conditions\***

| Description               | Sym              | Min | Nom | Max | Unit |

|---------------------------|------------------|-----|-----|-----|------|

| LED Supply Voltage        | $V_{\rm CC}$     | 4.5 | 5.0 | 5.5 | V    |

| Forward Current, Each LED | $I_{\mathrm{F}}$ |     | 5.0 | 10  | mA   |

## **Absolute Maximum Ratings\***

| Description                    | Symbol           | Min | Max  | Unit                 |

|--------------------------------|------------------|-----|------|----------------------|

| Storage Temperature, Ambient   | $T_{\mathrm{S}}$ | -65 | +125 | $^{\circ}\mathrm{C}$ |

| Operating Temperature, Ambient | T <sub>A</sub>   | -55 | +100 | $^{\circ}\mathrm{C}$ |

| Forward Current, Each LED      | $I_{\mathrm{F}}$ |     | 10   | mA                   |

| Reverse Voltage, Each LED      | $V_{\mathrm{R}}$ |     | 4    | V                    |

#### Note

LED current must be externally limited. Refer to Figure 9 for recommended resistor values.

<sup>\*</sup>JEDEC Registered Data.

<sup>\*\*</sup>Non-Registered Data.