**User's Manual**

# **μPD77016 Family**

# **Digital Signal Processor**

Instructions

```

μPD77015

μPD77016

μPD77017

μPD77018

μPD77018A

μPD77019

μPD77110

μPD77110

μPD77112

μPD77113

μPD77114

```

Document No. U13116EJ2V0UM00 (2nd edition) Date Published July 2000 N CP(K)

© NEC Corporation 1998 Printed in Japan [MEMO]

## **()**PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

#### Note:

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

### (2) HANDLING OF UNUSED INPUT PINS FOR CMOS

#### Note:

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

### **③STATUS BEFORE INITIALIZATION OF MOS DEVICES**

#### Note:

Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

The export of these products from Japan is regulated by the Japanese government. The export of some or all of these products may be prohibited without governmental license. To export or re-export some or all of these products from a country other than Japan may also be prohibited without a license from that country. Please call an NEC sales representative.

License not needed: The customer must judge the the need for licence: μPD77016, μPD77019-013, μPD77110 μPD77015, μPD77017, μPD77018, μPD77018A, μPD77019, μPD77111, μPD77112, μPD77113, μPD77114

- The information in this document is current as of February, 2000. The information is subject to change without notice. For actual design-in, refer to the latest publications of NEC's data sheets or data books, etc., for the most up-to-date specifications of NEC semiconductor products. Not all products and/or types are available in every country. Please check with an NEC sales representative for availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without prior written consent of NEC. NEC assumes no responsibility for any errors that may appear in this document.

- NEC does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from the use of NEC semiconductor products listed in this document or any other liability arising from the use of such products. No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC or others.

- Descriptions of circuits, software and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software and information in the design of customer's equipment shall be done under the full responsibility of customer. NEC assumes no responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information.

- While NEC endeavours to enhance the quality, reliability and safety of NEC semiconductor products, customers

agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize

risks of damage to property or injury (including death) to persons arising from defects in NEC

semiconductor products, customers must incorporate sufficient safety measures in their design, such as

redundancy, fire-containment, and anti-failure features.

- NEC semiconductor products are classified into the following three quality grades: "Standard", "Special" and "Specific". The "Specific" quality grade applies only to semiconductor products developed based on a customer-designated "quality assurance program" for a specific application. The recommended applications of a semiconductor product depend on its quality grade, as indicated below. Customers must check the quality grade of each semiconductor product before using it in a particular application.

- "Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

- "Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

- "Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems and medical equipment for life support, etc.

The quality grade of NEC semiconductor products is "Standard" unless otherwise expressly specified in NEC's data sheets or data books, etc. If customers wish to use NEC semiconductor products in applications not intended by NEC, they must contact an NEC sales representative in advance to determine NEC's willingness to support a given application.

(Note)

(1) "NEC" as used in this statement means NEC Corporation and also includes its majority-owned subsidiaries.

(2) "NEC semiconductor products" means any semiconductor product developed or manufactured by or for NEC (as defined above).

# **Regional Information**

Some information contained in this document may vary from country to country. Before using any NEC product in your application, please contact the NEC office in your country to obtain a list of authorized representatives and distributors. They will verify:

- Device availability

- Ordering information

- Product release schedule

- · Availability of related technical literature

- Development environment specifications (for example, specifications for third-party tools and components, host computers, power plugs, AC supply voltages, and so forth)

- Network requirements

In addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary from country to country.

### NEC Electronics Inc. (U.S.) Santa Clara, California Tel: 408-588-6000 800-366-9782 Fax: 408-588-6130

Fax: 408-588-6130 800-729-9288

## **NEC Electronics (Germany) GmbH**

Duesseldorf, Germany Tel: 0211-65 03 02 Fax: 0211-65 03 490

### **NEC Electronics (UK) Ltd.** Milton Keynes, UK Tel: 01908-691-133 Fax: 01908-670-290

## NEC Electronics Italiana s.r.l.

Milano, Italy Tel: 02-66 75 41 Fax: 02-66 75 42 99

## NEC Electronics (Germany) GmbH Benelux Office Eindhoven, The Netherlands Tel: 040-2445845 Fax: 040-2444580

NEC Electronics (France) S.A. Velizy-Villacoublay, France Tel: 01-30-67 58 00 Fax: 01-30-67 58 99

# NEC Electronics (France) S.A.

Spain Office Madrid, Spain Tel: 91-504-2787 Fax: 91-504-2860

## **NEC Electronics (Germany) GmbH**

Scandinavia Office Taeby, Sweden Tel: 08-63 80 820 Fax: 08-63 80 388 **NEC Electronics Hong Kong Ltd.** Hong Kong Tel: 2886-9318 Fax: 2886-9022/9044

### NEC Electronics Hong Kong Ltd. Seoul Branch Seoul, Korea Tel: 02-528-0303 Fax: 02-528-4411

NEC Electronics Singapore Pte. Ltd. United Square, Singapore 1130 Tel: 65-253-8311 Fax: 65-250-3583

# NEC Electronics Taiwan Ltd.

Taipei, Taiwan Tel: 02-2719-2377 Fax: 02-2719-5951

## NEC do Brasil S.A.

Electron Devices Division Rodovia Presidente Dutra, Km 214 07210-902-Guarulhos-SP Brasil Tel: 55-11-6465-6810 Fax: 55-11-6465-6829

J99.1

# Major Revisions in This Edition

| Page       | Description                                                                                                   |

|------------|---------------------------------------------------------------------------------------------------------------|

| Throughout | Addition of mPD77110, 77111, 77112, 77113, and 77114 as target devices                                        |

| p. 78      | 3.4 Load/Store Instructions<br>Addition of description to Caution 1 of LSPA (parallel load/store instruction) |

| p. 84      | 3.4 Load/Store Instructions<br>Addition of description to Caution 1 of LSSE (section load/store instruction)  |

| p. 109     | 3.8 Hardware Loop Instructions<br>Addition of Caution 2 of REP (repeat instruction)                           |

| p. 111     | 3.8 Hardware Loop Instructions<br>Addition of Caution 2 and change of Caution 3 of LOOP (loop instruction)    |

| p. 113     | 3.9 Control Instructions<br>Change of description and addition of Caution 3 of STOP (stop instruction)        |

The mark  $\star$  shows major revised points.

# INTRODUCTION

| Target Readers:         | This manual is intended for users who wish to understand the functions of the $\mu$ PD77016 Family devices and to design and develop software/hardware application systems using these micocontrollers.                                                                                                                                  |                                                                                                                                                                             |  |  |  |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Purpose:                | provided in $\mu$ PD77016 Fa                                                                                                                                                                                                                                                                                                             | give users an understanding of the instruction functions<br>mily devices, and is designed to be used as a reference<br>software or hardware application systems using these |  |  |  |

| Organization:           | <ul> <li>This manual consists of the following sections:</li> <li>CHAPTER 1 OUTLINE</li> <li>CHAPTER 2 INSTRUCTION CATEGORIES AND INSTRUCTION FUNCTIONS</li> <li>CHAPTER 3 EXPLANATION OF INSTRUCTIONS</li> <li>APPENDIX A CLASSIFICATION OF INSTRUCTION WORDS</li> <li>APPENDIX B INSTRUCTION SETS</li> <li>APPENDIX C INDEX</li> </ul> |                                                                                                                                                                             |  |  |  |

| How to Use This Manual: | electrical engineering, logi                                                                                                                                                                                                                                                                                                             | der of this manual has general knowledge in the fields of c circuits, and microcomputers.<br>presents $\mu$ PD7701x Family devices ( $\mu$ PD77016, 77015,                  |  |  |  |

|                         | 77017, 77018, 77018A, and 77019) and $\mu$ PD77111 Family ( $\mu$ PD77110, 7711<br>77112, 77113, and 77114). Unless there are differences in function or operatio<br>read the $\mu$ PD77016 Family as the corresponding products. If there are difference<br>among family products, they are described under their respective names.     |                                                                                                                                                                             |  |  |  |

| Legends:                | Data significance:                                                                                                                                                                                                                                                                                                                       | Higher digits on the left and lower on the right                                                                                                                            |  |  |  |

|                         | Note:<br>Caution:                                                                                                                                                                                                                                                                                                                        | Footnote for item marked with <b>Note</b> in the text                                                                                                                       |  |  |  |

|                         | Remarks:                                                                                                                                                                                                                                                                                                                                 | Information requiring particular attention<br>Supplementary information                                                                                                     |  |  |  |

|                         | Bold text:                                                                                                                                                                                                                                                                                                                               | Important items                                                                                                                                                             |  |  |  |

|                         | Numerical representation: Binary 0bXXXX<br>Decimal XXXX                                                                                                                                                                                                                                                                                  |                                                                                                                                                                             |  |  |  |

|                         | { }:                                                                                                                                                                                                                                                                                                                                     | Hexadecimal 0xXXXX<br>Either of the items enclosed within { } can be<br>selected.                                                                                           |  |  |  |

### **Related Documents:**

The related documents listed below may include preliminary versions. However, preliminary versions are not marked as such.

# **Documents Related to Devices**

| Document Name |          |            | User's       | Application Note |                |

|---------------|----------|------------|--------------|------------------|----------------|

| Product name  | Pamphlet | Data Sheet | Architecture | Instructions     | Basic software |

| μPD77016      | U12395E  | U10891E    | U10503E      | This document    | U11958E        |

| μPD77015      |          | U10902E    |              |                  |                |

| μPD77017      |          |            |              |                  |                |

| μPD77018      |          |            |              |                  |                |

| μPD77018A     |          | U11849E    |              |                  |                |

| μPD77019      |          |            |              |                  |                |

| μPD77019-013  |          | U13053E    |              |                  |                |

| μPD77110      |          | U12801E    | U14623E      |                  |                |

| μPD77111      |          |            |              |                  |                |

| μPD77112      |          |            |              |                  |                |

| μPD77113      |          | U14373E    |              |                  |                |

| μPD77114      |          |            |              |                  |                |

## **Documents Related to Development Tools**

| Document Name                          | Document No. |         |

|----------------------------------------|--------------|---------|

| IE-77016-98, IE-77016-PC User's Manual | U13044E      |         |

| IE-11016-CM-LC User's Manual           | U14139E      |         |

| RX77016 User's Manual                  | U14397E      |         |

|                                        | U14404E      |         |

| RX77016 Application Note               | HOST API     | U14371E |

# Caution The documents listed above are subject to change without notice. Be sure to use the latest documents when designing.

# CONTENTS

| СНАРТЕ | ER 1 0  | UTLINE                                                              | 13  |

|--------|---------|---------------------------------------------------------------------|-----|

| 1.1    | Asser   | nbly Description                                                    | 13  |

|        | 1.1.1   | Coding instructions                                                 | 13  |

|        | 1.1.2   | Parallel coding                                                     | 13  |

|        | 1.1.3   | Coding trinomial operations                                         | 14  |

|        | 1.1.4   | Pointer operations                                                  | 14  |

|        | 1.1.5   | Coding conditional instructions                                     | 14  |

|        | 1.1.6   | Coding hardware loop instructions                                   | 14  |

| 1.2    | Conv    | entions Used for Instruction Descriptions                           | 16  |

|        | 1.2.1   | Symbols and corresponding registers                                 | 16  |

|        | 1.2.2   | General-purpose register partition format                           | 17  |

|        | 1.2.3   | Data pointer modification                                           | 18  |

| 1.3    | Descr   | iption Format                                                       | 19  |

| СНАРТЕ | ER 2 IN | ISTRUCTION CATEGORIES AND INSTRUCTION FUNCTIONS                     | 21  |

| 2.1    | Class   | ification by Instruction Word                                       | 21  |

|        | 2.1.1   | Classification by instruction word format (category classification) |     |

|        | 2.1.2   | Classification by instruction function (functional classification)  |     |

| СНАРТЕ | ER3E    | XPLANATION OF INSTRUCTIONS                                          | 23  |

| 3.1    | Trino   | mial Operation Instructions                                         | 23  |

| 3.2    |         | nial Operation Instructions                                         |     |

| 3.3    | Mono    | mial Operation Instructions                                         | 57  |

| 3.4    | Load/   | Store Instructions                                                  |     |

| 3.5    | Inter-  | Register Transfer Instructions                                      | 93  |

| 3.6    | Imme    | diate Value Set Instruction                                         | 96  |

| 3.7    | Branc   | h Instructions                                                      | 99  |

| 3.8    | Hardv   | vare Loop Instructions                                              | 107 |

| 3.9    | Contr   | ol Instructions                                                     | 114 |

| APPEN  | ΟΙΧΑ (  | CLASSIFICATION OF INSTRUCTION WORDS                                 | 120 |

| A.1    | Three   | -Operand Instructions                                               | 121 |

| A.2    | Two-0   | Derand Instructions                                                 | 123 |

| A.3    | Imme    | diate Value Operation Instructions                                  | 125 |

| A.4    | Load/   | Store Instructions                                                  | 126 |

| A.5    | Inter-  | Register Transfer Instruction                                       | 129 |

| A.6    | Imme    | diate Value Set Instruction                                         | 130 |

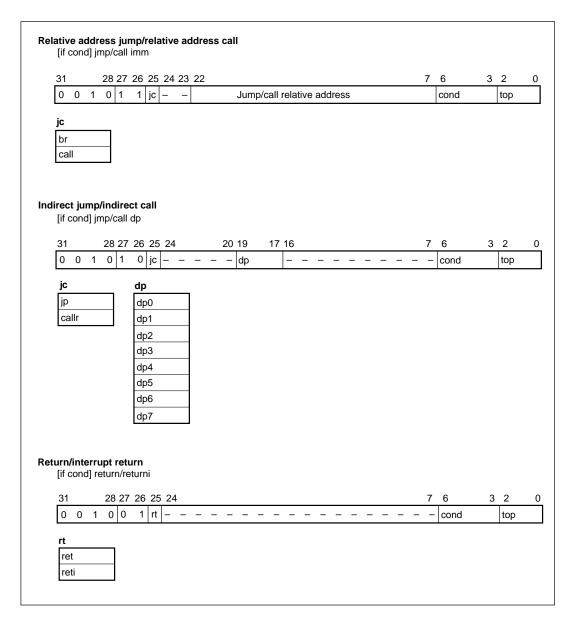

| A.7    | Branc   | h Instructions                                                      | 131 |

| A.8    | Hardv   | vare Loop Instructions                                              | 133 |

| A.9    | CPU (   | Control Instructions                                                | 135 |

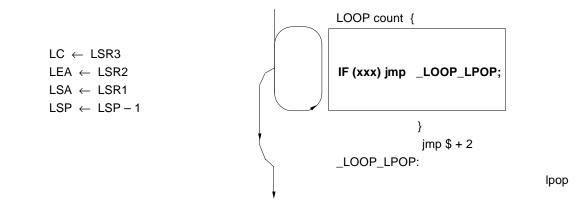

| A.10   | Cond    | itional Instructions                                                | 136 |

| APPENDIX B INSTRUCTION SETS | 138 |

|-----------------------------|-----|

| APPENDIX C INDEX            | 144 |

# LIST OF FIGURES

| Figure No. | Title                                          | Page |

|------------|------------------------------------------------|------|

| 1-1        | Partition Formats of General-Purpose Registers | 17   |

| A-1        | Three-Operand Instruction Format               |      |

| A-2        | Two-Operand Instruction Format                 | 124  |

| A-3        | Immediate Value Operation Instruction Format   |      |

| A-4        | Load/Store Instruction Format                  |      |

| A-5        | Inter-Register Transfer Instruction Format     | 129  |

| A-6        | Immediate Value Set Instruction Format         | 130  |

| A-7        | Branch Instruction Format                      | 132  |

| A-8        | Hardware Loop Instruction Format               | 134  |

| A-9        | CPU Control Instruction Format                 |      |

| A-10       | Conditional Instruction Format                 | 137  |

# LIST OF TABLES

| Table No. | Title                               | Page |

|-----------|-------------------------------------|------|

| 1-1       | Symbols and Corresponding Registers |      |

| 1-2       | Data Pointer Modify                 |      |

| A-1       | Formats of Instruction Words        |      |

# **CHAPTER 1 OUTLINE**

An instruction word in the  $\mu$ PD77016 Family is composed of 32 bits. Each instruction word is partitioned logically, allowing plural functional instructions to be included in a single instruction word. All operation instructions and transfer instructions are executed in one instruction cycle, while loop instructions and branch instructions are executed in two or three instruction cycles. The  $\mu$ PD77016 has the following assembly instruction features.

- 32-bit instruction words

- Nine instruction function groups

- Plural instructions can be described in one instruction word.

- · Flexible description of conditional operations by combining independent conditional instructions

# 1.1 Assembly Description

### 1.1.1 Coding instructions

The assembly language for the  $\mu$ PD77016 Family uses arithmetic symbols such as +, -, \*, /, and =, instead of general mnemonics such as ADD and MOV, for improved program readability.

This assembly language requires a semicolon ";" to indicate the end of each line in the same manner as the C language. Note that this assembler treats all codes as one line until a semicolon, even though one instruction description may fill several lines. A description example is provided below:

### **Description example:**

- R1 = R0; ..... Assigns the R0 register contents to the R1 register.

- R5 = \*DP0; ..... Assigns the X memory contents to the R5 register by using the DP0 register as a pointer.

- R4 = R2 + R3; ..... Adds the R2 and R3 register contents, and assigns the result to the R4 register.

### 1.1.2 Parallel coding

To describe parallel operations of the  $\mu$ PD77016 Family, up to three instructions can be described in parallel: an operation instruction (trinomial, binomial, monomial operation instructions) and two transfer instructions for data movements via X and Y buses.

### **Description example:**

R1 = R0 R2 = \*DP0 \*DP4 = R3H;

...... Assigns the R0 register contents to the R1 register, then assigns the X memory contents to the R2 register using the DP0 register as a pointer, and assigns the R3H register contents to the Y memory using the DP4 register as a pointer.

**Remark** In the example above, the  $\mu$ PD77016 Family first executes the operational instruction, then executes the transfer instructions.

### 1.1.3 Coding trinomial operations

The  $\mu$ PD77016 Family supports trinomial instructions that use three operands to describe the operation of the incorporated multiplier (the result obtained from multiplication by hardware is added to another register).

#### **Description example:**

R0 = R0 + R1L \* R2L;

......... Multiplies the R1L register and the R2L register contents, then adds the result to the R0 register contents, and stores the sum in the R0 register.

#### 1.1.4 Pointer operations

The  $\mu$ PD77016 Family is provided with instructions that add and subtract the pointer value after executing the transfer instructions explained in **1.1.2** and **1.1.3** above.

For details on pointer operations, refer to *µ*PD7701x Family User's Manual Architecture or *µ*PD77111 Family User's Manual Architecture.

### **Description example:**

R1 = \*DP0++ R2 = \*DP4##;

...... Executes transfer instructions using the DP0 and DP4 registers as pointers, adds 1 to the DP0 contents, and adds the DN4 (supplement register) value to the DP4 contents.

#### 1.1.5 Coding conditional instructions

The  $\mu$ PD77016 Family is provided with conditional instructions that can use a register value as the condition. These instructions are executed only when the register value matches the specified condition. By using these instructions, the number of branch (conditional) instructions required in conditional operation can be reduced. For details on the conditional instructions, refer to section **3.9 Conditional instruction of control instruction (COND)**.

#### **Description example:**

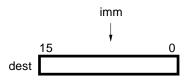

#### 1.1.6 Coding hardware loop instructions

The  $\mu$ PD77016 Family is provided with hardware loop instructions, which enable instructions consisting of 1 to 255 lines to be repeatedly executed 1 to 32767 times. To describe this operation, either the REPEAT or LOOP instruction is used depending on the number of repeated instruction lines. Nesting of loops is allowed (up to four levels).

**Description example:**

• To execute one line of instruction two or more times:

REPEAT 32

R0 = R0 + R1L \* R2L R1 = \*DP0++ R2 = \*DP4++;

• To execute 2 to 255 lines of instructions two or more times:

```

R1L {

R0 = R0 + R1L * R2L;

•

•

R4 = R4 – 1;

```

};

LOOP

LOOP

• To execute a loop within a loop function (nesting of loops):

};

# 1.2 Conventions Used for Instruction Descriptions

# 1.2.1 Symbols and corresponding registers

In the following sections, registers are described in a generalized style using symbols. The relationship between the symbols and the corresponding registers is shown in Table 1-1.

| Symbols      | Corresponding Registers                                                                    |

|--------------|--------------------------------------------------------------------------------------------|

| ro, ro' ro'' | R0 to R7                                                                                   |

| rl, rl'      | R0L to R7L                                                                                 |

| rh, rh'      | R0H to R7H                                                                                 |

| re           | R0E to R7E                                                                                 |

| reh          | R0EH to R7EH                                                                               |

| dp           | DP0 to DP7                                                                                 |

| dn           | DN0 to DN7                                                                                 |

| dm           | DMX and DMY                                                                                |

| dpx          | DP0 to DP3                                                                                 |

| dpy          | DP4 to DP7                                                                                 |

| dpx_mod      | DPn, DPn++, DPn, DPn##, DPn%%, !DPn## (n = 0 to 3)                                         |

| dpy_mod      | DPn, DPn++, DPn, DPn##, DPn%%, !DPn## (n = 4 to 7)                                         |

| dp_imm       | DPn##imm (n = 0 to 7)                                                                      |

| * XXX        | Memory contents with address xxx                                                           |

|              | Example                                                                                    |

|              | * DP0 indicates the contents of address 1000 when the contents of the DP0 register is 1000 |

## Table 1-1. Symbols and Corresponding Registers

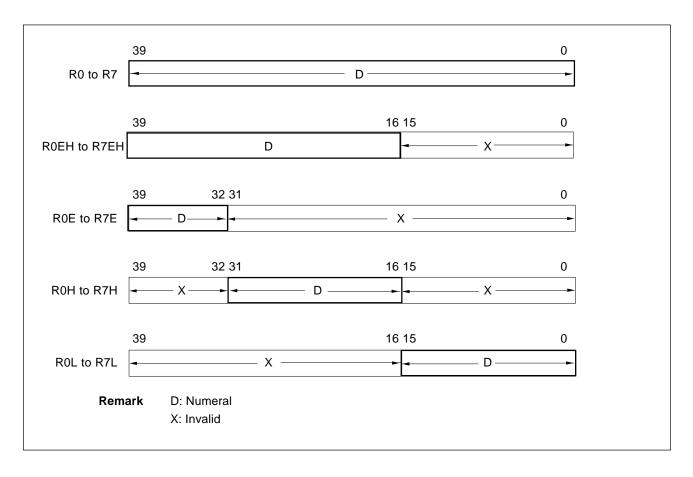

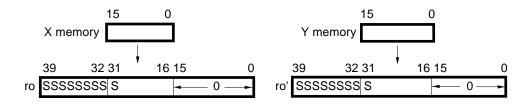

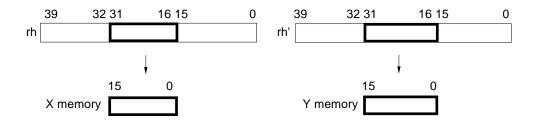

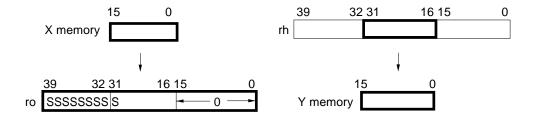

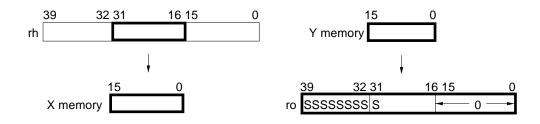

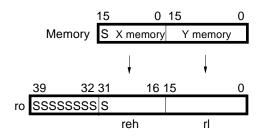

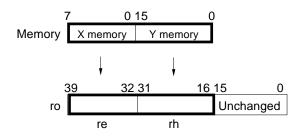

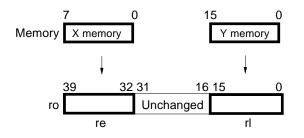

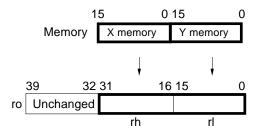

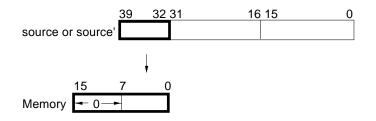

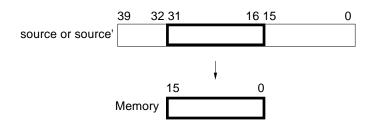

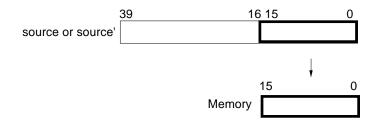

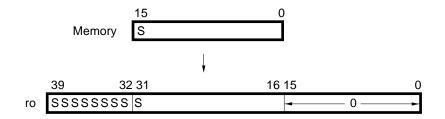

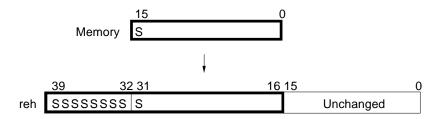

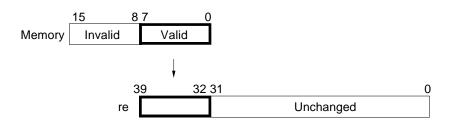

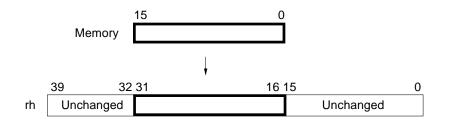

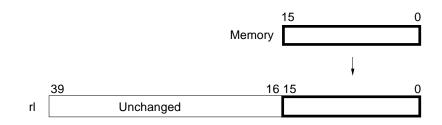

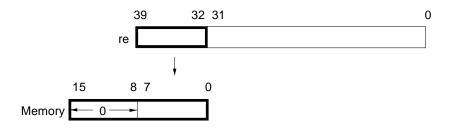

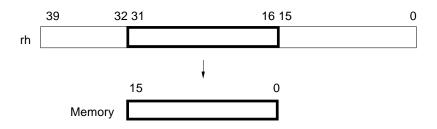

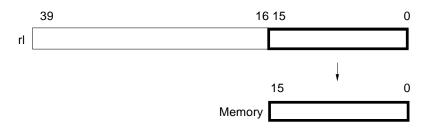

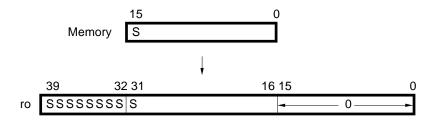

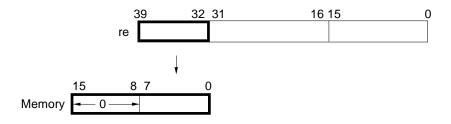

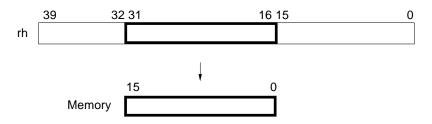

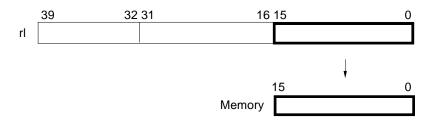

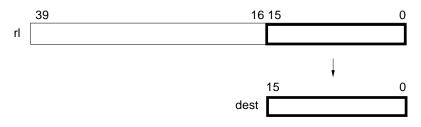

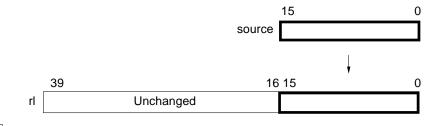

# 1.2.2 General-purpose register partition format

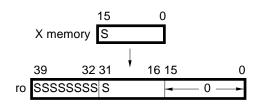

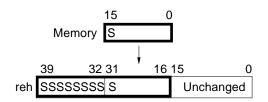

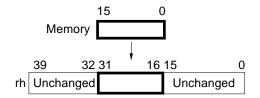

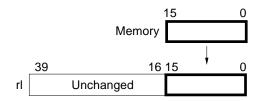

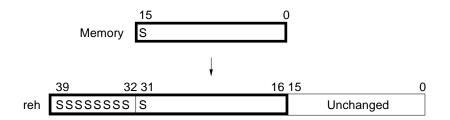

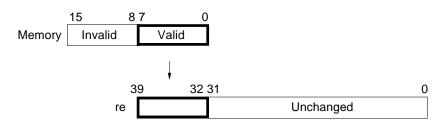

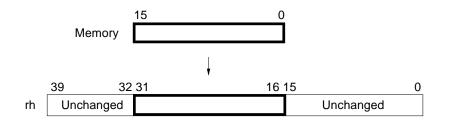

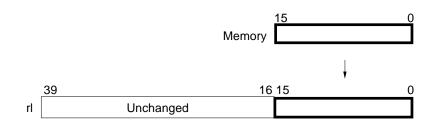

General-purpose registers can be partially accessed when an operation or transfer is executed. The partial access methods are classified into the five formats shown in Figure 1-1.

### Figure 1-1. Partition Formats of General-Purpose Registers

# 1.2.3 Data pointer modification

If indirect addressing using a pointer (DPn) is executed, the data pointer is, in most cases, modified after memory access. Table 1-2 shows the relationship between the descriptions of data pointer modify and the corresponding operations.

| Table 1-2 | . Data | Pointer | Modify |

|-----------|--------|---------|--------|

|-----------|--------|---------|--------|

| Description                                                                                          | Operation                                                                                                                                   |

|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| DPn                                                                                                  | No operation (The value of DPn is not changed.)                                                                                             |

| DPn++                                                                                                | $DPn \leftarrow DPn + 1$                                                                                                                    |

| DPn                                                                                                  | $DPn \leftarrow DPn - 1$                                                                                                                    |

| DPn##                                                                                                | $DPn \leftarrow DPn + DNn$<br>(Adds DP0 through DP7 values to DN0 through DN7 values, respectively.)<br>Example: DP0 $\leftarrow$ DP0 + DN0 |

| DPn%%                                                                                                | (n = 0 to 3) DPn = ((DPL + DNn) mod (DMX + 1)) + DPH                                                                                        |

|                                                                                                      | (n = 4 to 7) DPn = ((DPL + DNn) mod (DMY + 1)) + DPH                                                                                        |

| !DPn##       Accesses memory after bit reverse for DPn.         After memory access, DPn ← DPn + DNn |                                                                                                                                             |

| DPn##imm                                                                                             | $DPn \leftarrow DPn + imm$                                                                                                                  |

# **1.3 Description Format**

| MA                                                                                                                                                                                                              |                     | struction sy      | mbol<br>Instructio | on type                |                                             |        | MADD        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------------|--------------------|------------------------|---------------------------------------------|--------|-------------|

|                                                                                                                                                                                                                 | al operati          | on                |                    |                        |                                             |        |             |

|                                                                                                                                                                                                                 |                     |                   | r                  | o = ro + rh * rl       | h'                                          |        |             |

| Name of                                                                                                                                                                                                         | instruction         | n: Multiply add   |                    |                        |                                             |        |             |

| Mnemon                                                                                                                                                                                                          | nic:                | ro = ro + rh      | * rh'              |                        |                                             |        |             |

| Example                                                                                                                                                                                                         | e R1 =              | R1 + R0H * R4I    | 4                  |                        |                                             |        |             |

| Explanat                                                                                                                                                                                                        | tion $\leftarrow L$ | Details on in     | struction          | operations             | s are descri                                | bed.   |             |

|                                                                                                                                                                                                                 | Instru              | uction to add the | -                  |                        | <b>vith solid lin</b><br>bit data to 40-bit |        |             |

|                                                                                                                                                                                                                 | 39                  | 32 31             | 30                 | 1                      | 6 15                                        |        | 0           |

|                                                                                                                                                                                                                 | ro S                |                   |                    | +                      |                                             |        |             |

|                                                                                                                                                                                                                 | 39                  | 32 31             |                    |                        | 6 15                                        |        | 0           |

|                                                                                                                                                                                                                 | rh                  | S                 |                    | ×                      |                                             |        |             |

|                                                                                                                                                                                                                 | 39<br>rh'           | 32 31<br>S        |                    | 1                      | 6 15                                        |        | 0           |

|                                                                                                                                                                                                                 | 39                  | 32 31             | 30                 | = 1                    | 6 15                                        |        | 0           |

|                                                                                                                                                                                                                 | ro S                |                   |                    |                        |                                             |        |             |

| Execution cycle       1        ← Number of instruction execution cycles          Instruction that can be described concurrently        ← Instructions marked with "Yes" can be described with this instruction. |                     |                   |                    |                        |                                             |        |             |

|                                                                                                                                                                                                                 | Trinomia            | l Binomial        | Monomial           | Parallel<br>load/store | Inter-register<br>transfer                  | Branch | Conditional |

|                                                                                                                                                                                                                 | No                  | No                | No                 | Yes                    | No                                          | No     | No          |

| Caution                                                                                                                                                                                                         | ] ← <b>De</b> s     | scription th      | at should          | be read ca             | arefully.                                   |        |             |

[MEMO]

# **CHAPTER 2 INSTRUCTION CATEGORIES AND INSTRUCTION FUNCTIONS**

An instruction is composed of 32 bits which are partitioned into several fields to concurrently manage various resources in the device. Instructions can be classified into various formats according to the field partition methods. These formats are further classified by function group into several categories to facilitate the use of instructions.

### 2.1 Classification by Instruction Word

This section describes two instruction classifications: category and functional classifications.

### 2.1.1 Classification by instruction word format (category classification)

Instructions can be classified by the format in which the instruction words are partitioned into fields. Such classification is called category classification. Under this classification, categories are mutually exclusive. In other words, an instruction which is described in a particular format cannot be used in any other format. If the entire program is described according to this classification, the programmer can easily trace which functions are concurrently performed by a one-word instruction execution. This also allows users to create bit patterns of instruction words by synthesizing element fields, and to analyze concurrently performed functions based on the bit pattern of an instruction word.

Although this classification is closely related to the architecture of language processors including assemblers, programmers do not necessarily have to be aware of these formats. The details of the category classification are provided in Appendix A.

#### 2.1.2 Classification by instruction function (functional classification)

Classifying instructions according to their functions is called functional classification. This classification helps programmers understand overall instructions and is convenient when creating application programs. In this manual, instructions are classified into the following nine functional groups:

- Trinomial operation

- Binomial operation

- Monomial operation

- Load/store

- Inter-register transfer

- Immediate value set

- Branch

- Hardware loop

- Control

- **Remark**: The classification indicated in 2.1.2 above does not imply that each instruction is exclusive within one word; plural instructions may be concurrently described in the same instruction word. For details, refer to **CHAPTER 3 EXPLANATION OF INSTRUCTIONS**.

[MEMO]

# **CHAPTER 3 EXPLANATION OF INSTRUCTIONS**

This section describes instructions of the  $\mu$ PD77016 Family based on the functional classification. The following nine types of instructions are provided:

- 3.1 Trinomial Operation Instructions

- 3.2 Binomial Operation Instructions

- 3.3 Monomial Operation Instructions

- 3.4 Load/Store Instructions

- 3.5 Inter-Register Transfer Instruction

- 3.6 Immediate Value Set Instruction

- 3.7 Branch Instructions

- 3.8 Hardware Loop Instructions

- 3.9 Control Instructions

# 3.1 Trinomial Operation Instructions

Instruction for specifying operations with the multiply-accumulator. Any three registers can be specified for the operands (inputs) from the general-purpose register file, and any one of the registers specified for the operands can be specified for the output destination.

The following trinomial operation instructions are provided (symbol in parentheses is an abbreviation of each instruction).

| Multiply add               | (MADD)  |

|----------------------------|---------|

| Multiply sub               | (MSUB)  |

| Sign unsign multiply add   | (SUMA)  |

| Unsign unsign multiply add | (UUMA)  |

| 1-bit shift multiply add   | (MAS1)  |

| 16-bit shift multiply add  | (MAS16) |

# **MADD** Trinomial operation

# MADD

ro = ro + rh \* rh'

| Name of inst | ruction:                                         | Multiply add                                                |                                                                               |                                                                         |                                                                                                                                                    |

|--------------|--------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Mnemonic:    |                                                  | ro = ro + rh * rh'                                          |                                                                               |                                                                         |                                                                                                                                                    |

| Example      | R1 = R1                                          | + R0H * R4H                                                 |                                                                               |                                                                         |                                                                                                                                                    |

| Explanation  | The prod<br>by the va<br>of bits 39<br>the gener | lue of bits 31 to 16 of the g<br>to 0 of the general-purpos | to 16 of the gene<br>general-purpose<br>se register speci<br>ied by ro. The 1 | eral-purpose re<br>register speci<br>fied by ro. The<br>6-bit values sp | egister specified by rh multiplied<br>fied by rh' is added to the value<br>e sum is stored in bits 39 to 0 of<br>ecified by rh and rh' and the 40- |

|              | 39                                               | 32 31 30                                                    | 16                                                                            | 15                                                                      | 0                                                                                                                                                  |

| ro           | S                                                |                                                             |                                                                               |                                                                         |                                                                                                                                                    |

| rh           | 39                                               | 32 31 30<br>S .                                             | +<br>16                                                                       | 15                                                                      | 0                                                                                                                                                  |

|              |                                                  |                                                             | ×                                                                             |                                                                         |                                                                                                                                                    |

|              | 39                                               | 32 31 30                                                    | 16                                                                            | 15                                                                      | 0                                                                                                                                                  |

| rh'          |                                                  | S .                                                         |                                                                               |                                                                         |                                                                                                                                                    |

|              |                                                  |                                                             | =                                                                             |                                                                         |                                                                                                                                                    |

|              | 39                                               | 32 31 30                                                    | 16                                                                            | 15                                                                      | 0                                                                                                                                                  |

| ro           | S                                                |                                                             |                                                                               |                                                                         |                                                                                                                                                    |

On the assumption that a decimal point is located between bit 31 and bit 30 of the value of the general-purpose registers specified by rh and rh', the product to be added to the value of the general-purpose register specified by ro is a value with a decimal point located between bit 31 and bit 30, sign-extended to bits 39 to 32 and with bit 0 set to 0.

# MADD

Execution cycle

Instructions that can be described concurrently

1

| Trinomial | Binomial | Monomial | Parallel<br>load/store | Inter-register<br>transfer | Branch | Conditional |

|-----------|----------|----------|------------------------|----------------------------|--------|-------------|

| No        | No       | No       | Yes                    | No                         | No     | No          |

Caution

If the addition results in an overflow, the overflow flag ovf in the error status register ESR is set to 1.

# MSUB

# **MSUB**

# **Trinomial operation**

ro = ro - rh \* rh'

| Name of instr | uction:             | Multiply sub                                               |            |                                                                                               |

|---------------|---------------------|------------------------------------------------------------|------------|-----------------------------------------------------------------------------------------------|

| Mnemonic:     | I                   | ro = ro – rh * rh'                                         |            |                                                                                               |

| Example       | R1 = R1             | – R0H * R4H                                                |            |                                                                                               |

| Explanation   | The produbits 39 to | uct of bits 31 to 16 of regis<br>0 of register ro. The 16- |            | om 40-bit data.<br>6 of register rh' is subtracted from<br>rh' and the 40-bit value specified |

|               | 39                  | 32 31 30                                                   | 16 15      | 0                                                                                             |

| ro            | S                   |                                                            |            |                                                                                               |

| rh            | 39                  | 32 31 30<br>S .                                            |            | 0                                                                                             |

|               |                     |                                                            | ×          |                                                                                               |

|               | 39                  | 32 31 30                                                   | 16 15      | 0                                                                                             |

| rh'           |                     | S .                                                        |            |                                                                                               |

|               | 39                  | 32 31 30                                                   | =<br>16 15 | 0                                                                                             |

|               |                     |                                                            |            |                                                                                               |

On the assumption that a decimal point is located between bit 31 and bit 30 of the value of the general-purpose registers specified by rh and rh', the product to be added to the value of the general-purpose register specified by ro is a value with a decimal point located between bit 31 and bit 30, sign-extended to bits 39 to 32 and with bit 0 set to 0.

# **MSUB**

Execution cycle

Instructions that can be described concurrently

1

| Trinomial | Binomial | Monomial | Parallel<br>load/store | Inter-register<br>transfer | Branch | Conditional |

|-----------|----------|----------|------------------------|----------------------------|--------|-------------|

| No        | No       | No       | Yes                    | No                         | No     | No          |

Caution

If the subtraction results in an overflow, the overflow flag ovf in the error status register ESR is set to 1.

# SUMA Trinomial operation

ro S

# SUMA

ro = ro + rh \* rl

| Name of instruction: Sign unsign multiply add                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |                   |            |   |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------------|------------|---|--|--|--|--|

| Mnemonic:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          | ro = ro + rh * rl |            |   |  |  |  |  |

| Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R1 = R1  | + R0H * R4L       |            |   |  |  |  |  |

| ExplanationInstruction to add the product of 16-bit data x 16-bit data to 40-bit data.The product of the value of bits 31 to 16 of the general-purpose register specified by rh multiplied<br>by the value of bits 15 to 0 of the general-purpose register specified by rl is added to the value of<br>bits 39 to 0 of the general-purpose register specified by ro. The sum is stored in bits 39 to 0 of the<br>general-purpose register specified by ro. The 16-bit value specified by rh and the 40-bit value<br>specified by ro are represented with two's complement, and the 16-bit value specified by rl is a data<br>format of a positive integer value. |          |                   |            |   |  |  |  |  |

| ro                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 39<br>S  | 32 31             | 16 15      | 0 |  |  |  |  |

| 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <u> </u> |                   | +          |   |  |  |  |  |

| rh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 39       | 32 31<br>S.       | 16 15      | 0 |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <u>_</u> |                   | ×          |   |  |  |  |  |

| rl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 39       | 32 31             | 16 15      | 0 |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 39       | 32 31             | =<br>16 15 | 0 |  |  |  |  |

On the assumption that a decimal point is located between bit 31 and bit 30 of the value of the general-purpose register specified by rh and another decimal point is located below bit 0 of the value of the general-purpose register specified by rl, the product to be added to the value of the general-purpose register specified by ro is a value with a decimal point located between bit 16 and bit 15, sign-extended to bits 39 to 32 and with bit 0 set to 0.

# SUMA

Execution cycle

Instructions that can be described concurrently

1

| Trinomial | Binomial | Monomial | Parallel<br>load/store | Inter-register<br>transfer | Branch | Conditional |

|-----------|----------|----------|------------------------|----------------------------|--------|-------------|

| No        | No       | No       | Yes                    | No                         | No     | No          |

Caution

If the addition results in an overflow, the overflow flag ovf in the error status register ESR is set to 1.

ro = ro + rl \* rl'

# **UUMA** Trinomial operation

# UUMA

| Name of instruction: Unsign unsign multiply add |                                                |                                                                                                       |                                                    |                                                                    |                                                                                                                                                          |  |  |  |

|-------------------------------------------------|------------------------------------------------|-------------------------------------------------------------------------------------------------------|----------------------------------------------------|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Mnemonic:                                       |                                                | ro = ro + rl * rl'                                                                                    |                                                    |                                                                    |                                                                                                                                                          |  |  |  |

| Example                                         | R1 = R1                                        | I + R0L * R4L                                                                                         |                                                    |                                                                    |                                                                                                                                                          |  |  |  |

| Explanation                                     | The proo<br>the value<br>39 to 0 o<br>register | duct of the value of bi<br>e of bits 15 to 0 of the<br>of the general-purpose<br>specified by ro. The | general-purpose regis<br>e register specified by r | Il-purpose re<br>iter specified<br>o. The sum i<br>by rl and rl' a | gister specified by rl multiplied by<br>by rl' is added to the value of bits<br>s stored into the general-purpose<br>re positive integer values, and the |  |  |  |

| ro                                              | 39                                             | 32 31                                                                                                 | 16                                                 | 15                                                                 | 1 0                                                                                                                                                      |  |  |  |

| rl                                              | 39                                             | 32 31                                                                                                 | +<br>16<br>                                        | 15                                                                 | 0                                                                                                                                                        |  |  |  |

| rl'                                             | 39                                             | 32 31                                                                                                 | - 16                                               | 15                                                                 | 0                                                                                                                                                        |  |  |  |

| ro                                              | 39                                             | 32 31                                                                                                 | - 16                                               | 15                                                                 | 10                                                                                                                                                       |  |  |  |

On the assumption that a decimal point is located below bit 0 of the values of the general-purpose registers specified by rl and rl', the product to be added to the value of the general-purpose register specified by ro is a value with a decimal point located between bit 1 and bit 0 with bits 39 to 32 and bit 0 set to 0.

# UUMA

Execution cycle

Instructions that can be described concurrently

1

| Trinomial | Binomial | Monomial | Parallel<br>load/store | Inter-register<br>transfer | Branch | Conditional |

|-----------|----------|----------|------------------------|----------------------------|--------|-------------|

| No        | No       | No       | Yes                    | No                         | No     | No          |

Cautions

1. The result is treated as two's complement data.

2. If the addition results in an overflow, the overflow flag ovf in the error status register ESR is set to 1.

# MAS1 Trinomial operation

# MAS1

inomial operation

| ro = ( | (ro >> | 1) +    | rh | * rh |  |

|--------|--------|---------|----|------|--|

|        |        | • • • • |    |      |  |

| Name of inst                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ruction:   | 1-bit shift multiply add  |                           |   |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------------------|---------------------------|---|--|--|--|

| Mnemonic:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            | ro = (ro >> 1) + rh * rh' |                           |   |  |  |  |

| Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ] R1 = (R1 | >> 1) + R0H * R4H         |                           |   |  |  |  |

| ExplanationInstruction to add the product of 16-bit data x 16-bit data to 40-bit data.The product of the value of bits 31 to 16 of the general-purpose register specified by rh multiplied<br>by the value of bit 31 to 16 of the general-purpose register specified by rh' is added to the value of<br>bits 39 to 0 of the general-purpose register specified by ro arithmetically shifted to the right by one<br>bit. The sum is stored in bits 39 to 0 of the general-purpose register specified by ro are data formats represented with |            |                           |                           |   |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | two's con  |                           |                           |   |  |  |  |

| rc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 39<br>S    | 32 31 30                  | 16 15                     | 0 |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Ľ          | 1-b                       | it arithmetic right shift |   |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 39         | 32 31 30                  | 16 15                     | 0 |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | SS         |                           |                           |   |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 39         | 32 31 30                  | +<br>16 15                | 0 |  |  |  |