I C T INC

Preliminary Information

T.46-19-07

## PEEL<sup>™</sup>18CV8L-25

## **CMOS Programmable Electrically Erasable Logic Device**

#### **Features**

Advanced CMOS EEPROM Technology

, INC.

- Low Power Consumption

- 22mA at 25MHz

- High Performance

- tpp = 25ns, fmax=33.3MHz

- EE Instant Reprogrammability

- 100% factory tested

- Cost-effective windowless package

- Erases and programs in seconds

- Adds convenience, reduces field retrofit and development costs

- Fooiproof Design Security

- Prevents unauthorized reading or copying of design

- M Architectural Flexibility

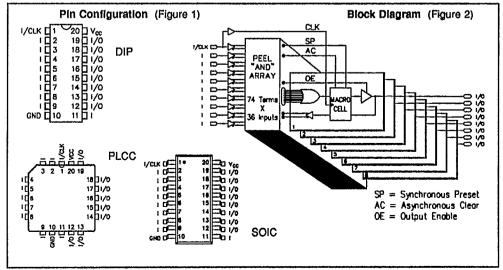

- 74 product term x 36 input array

- Up to 18 inputs and 8 I/O pins Independent configurable I/O macro cells

- Synchronous preset, asynchronous clear

- Independent output enables

- Application Versatility

- Replaces SSI/MSI logic

Emulates bipolar PAL\* devices, GAL\* devices, and EPLDs

- Simplifies inventory control

- Allows new design possibilities

- Development/Programmer Support

- Third party software and programmers

- ICT PEEL Development System and Software

#### **General Description**

The ICT PEEL18CV8L-25 is a CMOS Programmable Electrically Erasable Logic device that provides a high-performance, low-power, reprogrammable, and architecturally flexible alterreprogrammable, and architecturally lexible afternative to early-generation programmable logic devices (PLDs). Designed in advanced CMOS EEPROM technology, the performance of the PEEL18CV8L-25 rivals speed parameters of bipolar PLDs with a dramatic reduction in power consumption. EE reprogrammability simplifies inventory management, reduces development and field retrofit costs, enhances testability to ensure 100% field programmability and function, while al-

lowing for low-cost "windowless" packaging in a 20-pin, 300-mil DIP. The PEEL18CV8L-25's flexible architecture allows the device to replace SSI/MSI logic circuitry. ICT's JEDEC file translator allows the PEEL18CV8L-25 to replace existing 20-pin PLDs without the need to rework the existing design. Development and programming support for the PEEL18CV8L-25 is provided by popular third-party PC-based development tools and programmers from third-party manufacturers. ICT also offers a free design software package and a low-cost development system.

I C T INC

### **Absolute Maximum Ratings**

, INC.

Exposure to absolute maximum ratings over extended periods of time may affect device reliability. Exceeding absolute maximum ratings may cause permanent damage

| ·      |                            |                              |                    | -    |  |

|--------|----------------------------|------------------------------|--------------------|------|--|

| Symbol | Parameter                  | Conditions                   | Rating             | Unit |  |

| Vcc    | Supply Voltage             | Relative to GND              | - 0.5 to + 7.0     | V    |  |

| VI, Vo | Voltage Applied to Any Pin | Relative to GND <sup>1</sup> | - 0.5 to Vcc + 0.6 | ٧    |  |

| lo     | Output Current             | Per pin (IoL, IoH)           | ± 25               | mA   |  |

| Tst    | Storage Temperature        |                              | - 65 to+150        | ,c   |  |

| TLT    | Lead Temperature           | Soldering 10 seconds         | + 300              | .c   |  |

## Operating Ranges<sup>2</sup>

| Symbol | Parameter           | Conditions | Min  | Max  | Unit |

|--------|---------------------|------------|------|------|------|

| Vcc    | Supply Voltage      | Commercial | 4.75 | 5.25 | V    |

|        |                     | Industrial | 4.5  | 5.5  | V    |

| TA     | Ambient Temperature | Commercial | 0    | + 70 | °C   |

|        |                     | Industrial | - 40 | + 85 | .c   |

| TR     | Clock Rise Time     | See note 4 |      | 250  | ns   |

| TF     | Clock Fall Time     | See note 4 |      | 250  | ns   |

| TRVCC  | Vcc Rise Time       | See note 4 |      | 250  | ms   |

#### D.C. Electrical Characteristics Over the operating range

| Symbol           | Parameter                    | Conditions                                                                      | Min       | Max       | Unit |

|------------------|------------------------------|---------------------------------------------------------------------------------|-----------|-----------|------|

| Vон              | Output HIGH Voltage - TTL    | Vcc = Min, IoH = - 4.0mA                                                        | 2.4       |           | ٧    |

| Vонс             | Output HIGH Voltage-CMOS     | Vcc = Min, IoH = -10μA                                                          | Vcc - 0.1 |           | ٧    |

| Vol              | Output LOW Voltage - TTL     | Vcc = Min, IoL = 16mA                                                           |           | 0.45      | V    |

| Volc             | Output LOW Voltage-CMOS      | Vcc = Min, IoL = 10μA                                                           | -         | 0.1       | ٧    |

| ViH              | Input HIGH Level             |                                                                                 | 2.0       | Vcc + 0.3 | ٧    |

| VIL              | Input LOW Level              |                                                                                 | - 0.3     | 0.8       | ٧    |

| [ <sub>[L</sub>  | Input Leakage Current        | Vcc = Max, GND ≤ Vin ≤ Vcc                                                      |           | ±10       | μА   |

| loz              | Output Leakage Current       | I/O = High-Z, GND ≤ Vo≤ Vcc                                                     |           | ±10       | μА   |

| Isc              | Output Short Circuit Current | Vcc=5V,Vo=0.5V <sup>9</sup>                                                     | - 30      | - 100     | mA   |

| lcc <sup>1</sup> | Vcc Current                  | V <sub>IN</sub> = 0V or 3V <sup>5,10</sup><br>f = 25MHz<br>All outputs disabled |           | 22        | mA   |

| CIN 7            | Input Capacitance            | T <sub>A</sub> = 25 °C, V <sub>CC</sub> = 5.0V                                  |           | 6         | pF   |

| Cout 7           | Output Capacitance           | ─ @ f = 1MHz                                                                    | _         | 12        | рF   |

, INC.

#### I C T INC

# PEEL<sup>™</sup>18CV8L-25

T-46-19-07

#### A.C. Electrical Characteristics Over the Operating Range 8.11

| Symbol            | Parameter                                                            | 18CV8L-25 |     | Unit |

|-------------------|----------------------------------------------------------------------|-----------|-----|------|

|                   | i alamoto.                                                           | Min       | Max | 1    |

| tPD               | Input or I/O to non-registered output                                |           | 25  | nS   |

| toe               | Input or I/O to output enable <sup>6</sup>                           |           | 25  | nS   |

| top               | Input or I/O to output disable <sup>6</sup>                          |           | 25  | nS   |

| tcoı              | Clock to output                                                      |           | 12  | nS   |

| tco2              | Clock to combinatorial output delay via internal registered feedback |           | 35  | nS   |

| tcr               | Clock to feedback                                                    |           | 10  | nS   |

| tsc               | Input or feedback setup to clock                                     | 15        |     | nS   |

| tнс               | Input hold after clock                                               | 0         |     | nS   |

| tcl.tch           | Clock width - clk low time, clk high time 4                          | 9         |     | nS   |

| tcp               | Min clock period External (tsc + tco1)                               | 27        | -   | nS   |

| fmax1             | Max clock freq Internal Feedback                                     | 40        |     | MHz  |

| fmax2             | Max Clock freq. External (1/tcp)                                     | 37        |     | nS   |

| f <sub>max3</sub> | Max clock freq. No feedback (1/tcL + tch)                            | 55.5      |     | MHz  |

| taw               | Asynchronous clear pulse width                                       | 25        |     | nS   |

| tap               | Input to asynchronous clear                                          |           | 25  | nS   |

| tar               | Asynchronous Reset Recovery Time                                     |           | 20  | nS   |

| TRESET            | Power-on reset time for registers in clear state <sup>4</sup>        |           | 5   | μS   |

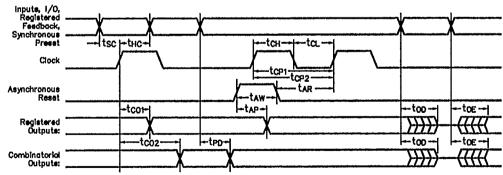

#### **Switching Waveforms**

- Minimum DC input is -0,5V, however inputs may undershoot to -2.0V for periods less than 20ns

- 2. Contact ICT for other operating ranges.

- Vi and Vo are not specified for program/verify operation.

Test points for Clock and Vcc in ta, tc, tcl, tch, and tasset are referenced at 10% and 90% levels.

- I/O pins are 0V or 3V.

- toe is measured from input transition to VREF ± 0.1V, too is measured from input transition to VoH-0.1V or VoL+0.1V; VREF = VL see test loads at the end of this section.

- 7. Capacitance are tested on a sample basis.

- 8. Test conditions assume: signal transition times of 5ns or less from the 10% and 90% points, timing reference levels of 1.5V (unless otherwise specified).

- 9. Test one output at a time for a duration less than 1 second.

- 10. ICC for a typical application. This parameter is tested with the device programmed as an 8-bit counter.

- 11. PEEL Device test loads are specified at the end of this section.