# **GPS Receiver Baseband Processor**

#### **Features**

- Complete GPS correlator and Firefly MF1 microcontroller core

- ARM 7TDMI<sup>™</sup> (Thumb<sup>®</sup>) Microprocessor, with JTAG ICEBreaker<sup>™</sup> Debug Interface

- Fully Configurable External Data Bus

- 12 Fully Independent Correlation Channels

- Low Voltage Operation: 3-3V

- Low Current Power–Down Mode

- 1PPS UTC Aligned Timing Output

- Dual UART

- 3-wire BuILD Serial Input/Output (BSIO) Interface

- 8 General Purpose Input/Output (GPIO) Lines

- · Boot ROM, allowing Software Upload via UART

- 8K Bytes Internal SRAM

- Compatible with GP2015 and GP2010 RF Front Ends

#### **Applications**

- · GPS Navigation Systems

- · GPS Geodetic Receivers

- Time Transfer Receivers

- Automatic Vehicle Location (AVL)

- E911 Emergency Positioning

# **Related Products**

| Part   | Description               | Data sheet |

|--------|---------------------------|------------|

| GP2015 | GPS Receiver RF Front End | DS4374     |

|        | (TQFP 48 package)         |            |

| GP2010 | GPS Receiver RF Front End | DS4056     |

|        | (PQFP 44 package)         |            |

DS5134 ISSUE 4.4 May 2002

#### **Ordering Information**

GP4020/IG/GQ1N (trays)

GP4020/IG/GQ1Q (tape and reel, 1000 units per reel)

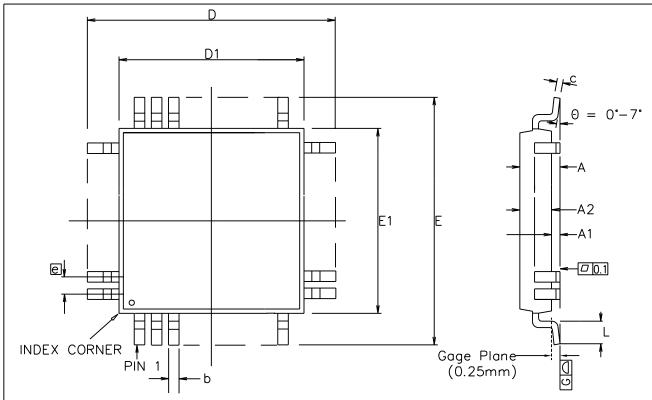

The GP4020 is available in a 100 pin PQFP package in Industrial (-40°C to +85°C) grade. The ordering code is standard for screened devices

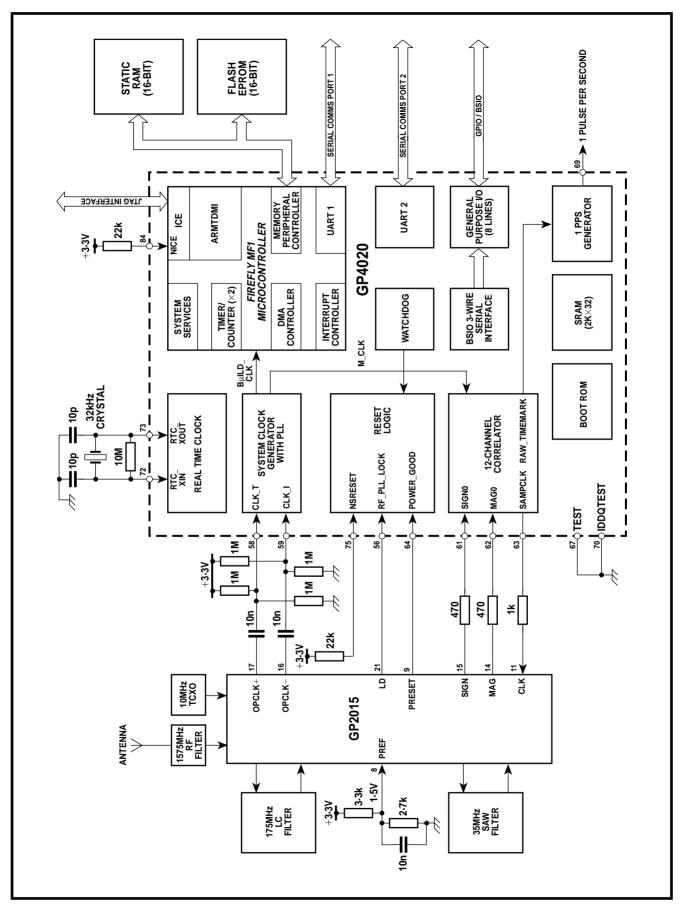

#### **Description**

The GP4020 is a complete digital baseband processor for a Global Positioning System (GPS) receiver. It combines the 12-channel correlator function of the GP2021 with an advanced ARM7TDMI (Thumb) microprocessor to achieve a higher level of integration, reduced system cost, reduced power consumption and added functionality. The GP4020 complements the GP2015 and GP2010 C/A code RF downconverters available from Zarlink Semiconductor.

The correlator section contains 12 identical tracking module blocks, one for each channel. Each channel contains all the components necessary for acquiring and tracking the received signal, and also contains other functional blocks, which are used to produce part of the measurement data set. Individual channels may be deactivated for systems not requiring full 12-channel operation and thus allowing for reduced power consumption and processor loading.

The microprocessor section contains the Firefly MF1 microcontroller core, which includes an ARM7TDMI with a Thumb instruction de-compressor plus the Firefly BµILD module. Also included are a second UART, BµILD Serial I/O, General I/O and Watchdog functions.

#### **Absolute Maximum Ratings**

\*Mil Std 883 Human Body Model = discharge from 100pF through  $1500\Omega$  between any 2 pins

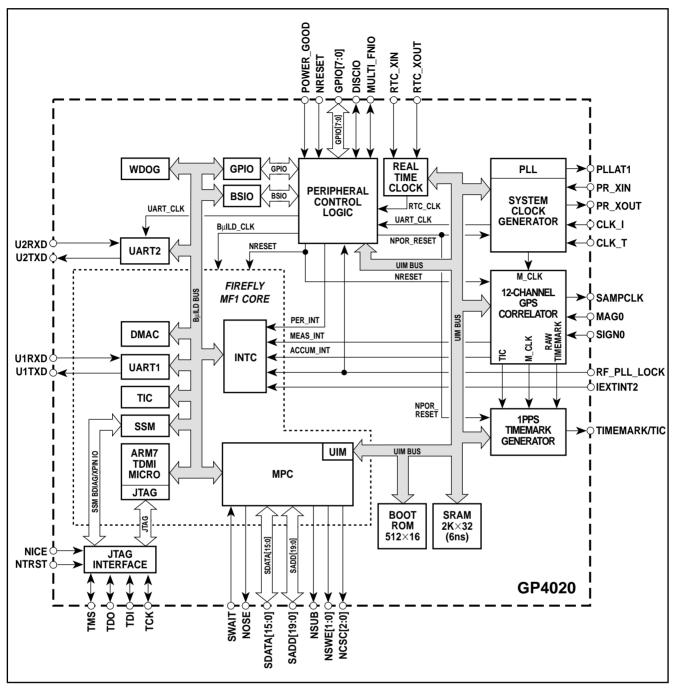

Figure 1 - Block diagram

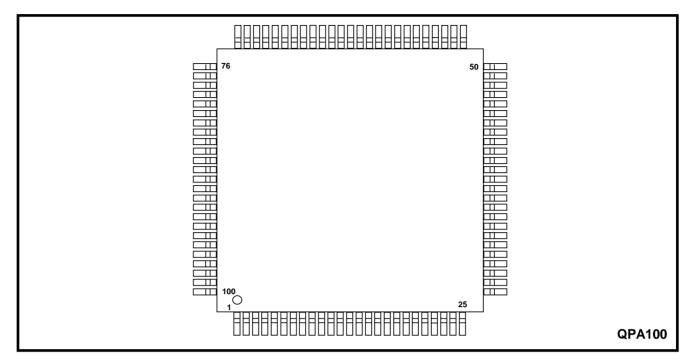

Figure 2 - Pin connections (top view)

| Pin No.  | Signal Name                     | Туре | Associated circuit block | Description                        |   |

|----------|---------------------------------|------|--------------------------|------------------------------------|---|

| 1        | SADD[0]                         | I/O  | MPC                      | System Address bit 0               |   |

| 2        | SADD[1]                         | I/O  | MPC                      | System Address bit 1               |   |

| 3        | SADD[2]                         | I/O  | MPC                      | System Address bit 2               |   |

| 4        | SADD[3]                         | I/O  | MPC                      | System Address bit 3               |   |

| 5        | SADD[4]                         | I/O  | MPC                      | System Address bit 4               |   |

| 6        | SADD[5]                         | I/O  | MPC                      | System Address bit 5               |   |

| 7        | GNDPWR                          |      |                          |                                    |   |

| 8        | SADD[6]                         | I/O  | MPC                      | System Address bit 6               |   |

| 9        | SADD[7]                         | I/O  | MPC                      | System Address bit 7               |   |

| 10       | $V_{DD}$ PWR                    |      |                          |                                    |   |

| 11       | NSCS[0]                         | I/O  | MPC                      | System Chip Select 0 - Active Low  | 1 |

| 12       | NSCS[1]                         | 0    | MPC                      | System Chip Select 1 - Active Low  | 1 |

| 13       | NSCS[2A]                        | 0    | MPC                      | System Chip Select 2A - Active Low | 1 |

| 14       | SADD[19]                        | 0    | MPC                      | System Address bit 19              |   |

| 15       | SDATA[0]                        | I/O  | MPC                      | System Data bit 01                 |   |

| 16       | SDATA[1]                        | I/O  | MPC                      | System Data bit 11                 |   |

| 17       | SDATA[2]                        | I/O  | MPC                      | System Data bit 21                 |   |

| 18       | SDATA[3]                        | I/O  | MPC                      | System Data bit 31                 |   |

| 19       | GNDPWR                          |      |                          |                                    |   |

| 20       | SDATA[4]                        | I/O  | MPC                      | System Data bit 41                 |   |

| 21       | SDATA[5]                        | I/O  | MPC                      | System Data bit 51                 |   |

| 22<br>23 | V <sub>DD</sub> PWR<br>SDATA[6] | I/O  | MPC                      | System Data bit 61                 |   |

Table 1 - Pin descriptions

Cont...

All  $V_{DD}$  and GND pins must be connected to ensure reliable operation. Any unused input pins must be tied either high or low; no inputs should be left unconnected.

| Pin No. | Signal Name            | Туре | Associated circuit block | Description                                    | Notes        |

|---------|------------------------|------|--------------------------|------------------------------------------------|--------------|

| 24      | SDATA[7]               | I/O  | MPC                      | System Data bit 7                              | 1            |

| 25      | NSOE                   | I/O  | MPC                      | System Output Enable, active low               | 1 <b> </b>   |

| 26      | NSWE[1]                | I/O  | MPC                      | System Write Enable bit 1, active low          | 1 1 <b>1</b> |

| 27      | NSWE[0]                | I/O  | MPC                      | System Write Enable bit 0, active low          | 1 <b> </b>   |

| 28      | SDATA[8]               | I/O  | MPC                      | System Data bit 8                              | i            |

| 29      | SDATA[9]               | I/O  | MPC                      | System Data bit 9                              | i            |

| 30      | V <sub>DD</sub>        | PWR  | 0                        | System Bala Sit 5                              | '            |

| 31      | SDATA[10]              | 1/0  | MPC                      | System Data bit 10                             | 1 <b> </b>   |

| 32      | SDATA[11]              | 1/0  | MPC                      | System Data bit 11                             | i            |

| 33      | GND                    | PWR  | IVII O                   | System Bata bit 11                             | '            |

| 34      | SDATA[12]              | 1/0  | MPC                      | System Data bit 12                             | 1 <b> </b>   |

| 35      | SDATA[12]              | 1/0  | MPC                      | System Data bit 12                             | i            |

| 36      | SDATA[15]<br>SDATA[14] | 1/0  | MPC                      | System Data bit 13                             |              |

| 37      | SDATA[14]<br>SDATA[15] | 1/0  | MPC                      | 1 7                                            | ¦            |

|         |                        | 1/0  |                          | System Data bit 15                             | '            |

| 38      | SADD[18]               |      | MPC                      | System Address bit 18                          |              |

| 39      | SADD[17]               | I/O  | MPC                      | System Address bit 17                          |              |

| 40      | SADD[16]               | I/O  | MPC                      | System Address bit 16                          |              |

| 41      | GND                    | PWR  |                          |                                                |              |

| 42      | SADD[15]               | I/O  | MPC                      | System Address bit 15                          |              |

| 43      | I                      | 1/0  | MPC                      |                                                |              |

|         | SADD[14]               | 1    | IVIPC                    | System Address bit 14                          |              |

| 44      | $V_{DD}$               | PWR  |                          |                                                |              |

| 45      | SADD[13]               | I/O  | MPC                      | System Address bit 13                          |              |

| 46      | SADD[12]               | 1/0  | MPC                      | System Address bit 12                          |              |

| 47      | SADD[11]               | I/O  | MPC                      | System Address bit 11                          |              |

| 48      | SADD[10]               | I/O  | MPC                      | System Address bit 10                          |              |

|         | I                      |      |                          |                                                |              |

| 49      | SADD[9]                | I/O  | MPC                      | System Address bit 9                           |              |

| 50      | SADD[8]                | I/O  | MPC                      | System Address bit 8                           |              |

| 51      | SWAIT                  |      | MPC                      | System Wait input - allows                     |              |

|         |                        |      |                          | wait-states to be inserted into the            |              |

|         |                        |      |                          | current Firefly clock cycle.                   |              |

| 52      | NSUB                   | 0    | MPC                      | System Upper Byte, active low.                 | 1,2          |

| 53      | IEXTINT2               | l I  | INTC                     | Interrupt source 2 input                       |              |

|         |                        |      |                          | (for external interrupts).                     |              |

| 54      | MULTI_FNIO             | I/O  | PCL                      | Multi-function Input / Output. Used to set     |              |

|         |                        |      |                          | Boot Up ROM area, and source either            |              |

|         |                        |      |                          | 100kHz square wave or System Clock.            |              |

| 55      | DISCIO                 | I/O  | PCL                      | Discrete Input / Output.                       | 3            |

|         |                        |      |                          | Used either as input or to source              |              |

|         |                        |      |                          | RF_Power_Down control signal or TIC.           |              |

| 56      | RF_PLL_LOCK            |      | INTC /PCL                | PLL Lock Indicator input from RF section.      | <b> </b>     |

|         |                        |      |                          | When high this signal indicates that the       |              |

|         |                        |      |                          | PLL within the RF section is in lock and       |              |

|         |                        |      |                          | the master-clock inputs have stabilised.       | <b> </b>     |

| 57      | A1V <sub>DD</sub>      | PWR  | SCG                      | V <sub>DD</sub> Supply for CLK_T & CLK_I input | <b> </b>     |

|         |                        |      |                          | block in the System Clock Generator. This      |              |

|         |                        |      |                          | pin should be well decoupled to pin 60         |              |

|         |                        |      |                          | (GND) to ensure optimum noise immunity         | ,  <b> </b>  |

| 58      | CLK_T                  | l ,  | SCG                      | Master Clock Input from RF front end           | 4            |

|         | ] ""."                 | '    |                          | 40MHz 100mV rms.                               | ' <b> </b>   |

| 59      | CLK_I                  | 1    | SCG                      | Inverted Master Clock Input from RF            | 4            |

| I       |                        | '    |                          | front end: 40MHz 100mV rms.                    |              |

|         |                        |      |                          | HOHE CHO. 40MINZ TOUTHY ITTIS.                 |              |

Table 1 - Pin descriptions (continued)

Cont...

| Pin No.  | Signal name          | Туре     | Associated circuit block | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Notes |

|----------|----------------------|----------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 60       | GND                  | PWR      |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |

| 61       | SIGN0                | 1        | CORR                     | Sampled Sign (polarity) data from RF front end.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |

| 62       | MAG0                 | I        | CORR                     | Sampled Mag (amplitude) data from RF front end.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |

| 63       | SAMPCLK              | 0        | CORR                     | Sample Clock output to the RF front end. Provides a 5-714MHz clock with a 4:3 mark to space ratio.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       |

| 64       | POWER_GOOD           | I        | PCL                      | Power Monitor input, high for normal operation; low forces the GP4020 into Power Down mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |

| 65       | PR_XOUT              | Ο        | SCG                      | System Clock Oscillator - crystal output for 10 to 16MHz crystal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |

| 66       | PR_XIN               | I        | SCG                      | System Clock Oscillator - crystal inputfor 10 to 16MHz crystal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |

| 67       | TEST                 | I        |                          | TEST select pin, used with TESTMODE (pin 74). Used for test purposes only and should be connected to GND in normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5     |

| 68       | $V_{DD}$             | PWR      |                          | Connected to GND in normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |

| 69       | TIMEMARK / TIC       | 0        | 1PPS                     | Timemark output. This pin can be used to produce                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |

| 70       | IDDQTEST             | ı        |                          | a UTC-aligned 1 PPS output, or TIC output.<br>TEST select pin, used with TESTMODE (pin 74).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |

| 70       | IDDQTEGT             | '        |                          | Used for test purposes only and should be connected to GND in normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |

| 71       | GND                  | PWR      |                          | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |

| 72<br>73 | RTC_XIN<br>RTC_XOUT  | 0        | RTC<br>RTC               | Real-time Clock Oscillator input for 32kHz crystal. Real-time Clock Oscillator output for 32kHz crystal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |

| 74       | TESTMODE             | Ī        | KIO                      | TEST select pin, used with TEST (pin 67). Used                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5     |

|          |                      |          |                          | for test purposes only and should be connected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

| 75       | NSRESET              | ı        | PCL                      | to GND in normal operation.  System Reset input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |

| 76       | U2TXD                | Ö        | UART2                    | UART 2 Transmit data output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |

| 77       | U2RXD                | I        | UART2                    | UART 2 Receive data input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3     |

| 78       | U1TXD                | 0        | UART1                    | UART 1 Transmit data output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |

| 79<br>80 | U1RXD<br>PLLGND      | I<br>PWR | UART1<br>SCGPLL          | UART 1 Receive data input. GND connection for PLL Block.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3     |

| 81       | PLLVDD               | PWR      | SCGPLL                   | V <sub>DD</sub> connection for PLL Block.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

| 82       | GND                  | PWR      | 000. 22                  | V <sub>DD</sub> connection to the Blook.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |

| 83       | PLLAT1               | 0        | SCGPLL                   | System Clock Generator PLL Analog Test I/O. Reserved for TEST purposes only and should                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |

| 84       | NICE                 | ı        | JTAG/SSM                 | NOT be connected in normal operation.  ARM7 operating mode and JTAG / SSM Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6     |

|          |                      |          | MUTIPLEX                 | Multiplex (pins 86, 87, 88, 89).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |

| 85       | V <sub>DD</sub>      | PWR      | IT 4 C /CC 4             | ITAO T A OL LAGONA SI CARA SI |       |

| 86       | TCK/bdiag[0]/XReq    | I/O      | JTAG/SSM                 | JTAG Test Clock/SSM Diagnostic broadcast debug output bdiag[0]/System test control input XReg.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6     |

| 87       | TDI/bdiag[1]/XWrite  | I/O      | JTAG/SSM                 | JTAG Test Data In/SSM Diagnostic broadcast debug output bdiag[1]/System Test control input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6     |