# M8085AH 8-BIT HMOS MICROPROCESSOR

Military

- Single +5V Power Supply with 10% **Voltage Margins**

- **Full Military Temperature Range:**  $-55^{\circ}$ C to  $+125^{\circ}$ C (T<sub>c</sub>)

- 1.3 µs Instruction Cycle (M8085AH)

- 100% Compatible with M8085A

- 100% Software Compatible with M8080A

- On-Chip Clock Generator (with External Crystal, LC or RC Network)

- On-Chip System Controller; Advanced Cycle Status Information Available for **Large System Control**

- **Four Vectored Interrupt Inputs (One is** Non-Maskable) Plus an M8080A-Compatible Interrupt

- Serial In/Serial Out Port

- Decimal, Binary and Double Precision Arithmetic

- Direct Addressing Capablity to 64K Bytes of Memory

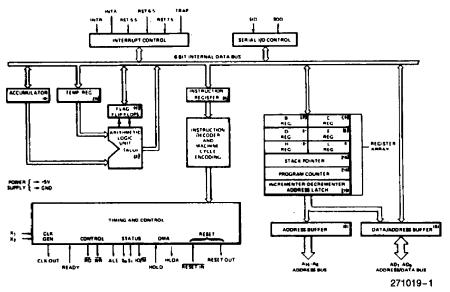

The Intel M8085AH is a complete 8 bit parallel Central Processing Unit (CPU) implemented in N-channel, depletion load, silicon gate technology (HMOS). Its instruction set is 100% software compatible with the M8080A microprocessor, and it is designed to improve the present M8080A's performance by higher system speed. Its high level of system integration allows a minimum system of four IC's [M8085AH (CPU), M8155 (RAM/IO), M2764A (EPROM), and M8282 (Octal Latch)] while maintaining total system expandability.

The M8085AH incorporates all of the features that the M8224 (clock generator) and M8228 (system controller) provided for the M8080A, thereby offering a high level of system integration.

The M8085AH uses a multiplexed data bus. The address is split between the 8 bit address bus and the 8 bit data bus. The on-chip address latches of M8155H/M8755A memory products allow a direct interface with the M8085AH.

17-1

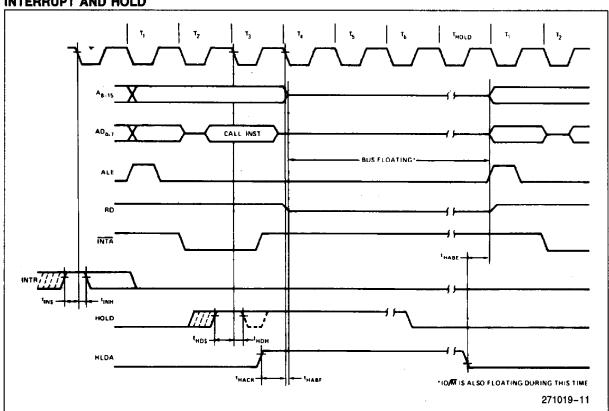

Figure 1. M8085AH CPU Functional Block Diagram

Figure 2. M8085AH Pin Configuration

November 1987 Order Number: 271019-002

Table 1. Pin Description

| Symbol                                     | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|--------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| A <sub>8</sub> -A <sub>15</sub>            | 0    | ADDRESS BUS: The most significant 8 bits of the memory address or the 8 bits of the I/O address, 3-stated during Hold and Halt modes and during RESET.                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

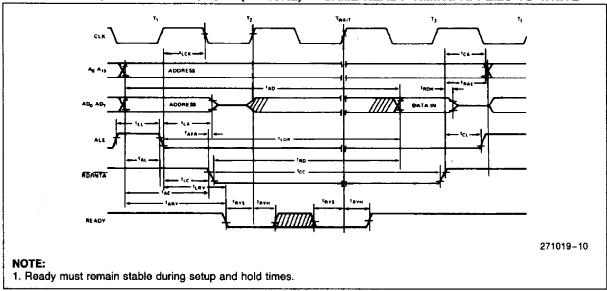

| AD <sub>0-7</sub>                          | 1/0  | MULTIPLEXED ADDRESS/DATA BUS: Lower 8 bits of the memory address (or I/O address) appear on the bus during the first clock cycle (T state) of a machine cycle. It then becomes the data bus during the second and third clock cycles.                                                                                                                                                                                                                                                                              |  |  |  |

| ALE                                        | 0    | ADDRESS LATCH ENABLE: It occurs during the first clock state of a machine cycle and enables the address to get latched into the on-chip latch of peripherals. The falling edge of ALE is set to guarantee setup and hold times for the address information. The falling edge of ALE can also be used to strobe the status information. ALE is never 3-stated.                                                                                                                                                      |  |  |  |

| S <sub>0</sub> , S <sub>1</sub> , and IO/M | 0    | MACHINE CYCLE STATUS:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| •                                          |      | IO/M S <sub>1</sub> S <sub>0</sub> Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|                                            |      | 0 0 1 Memory write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|                                            | l    | 0 1 0 Memory read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|                                            |      | 1 0 1 I/O write 1 1 0 I/O read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|                                            |      | 0 1 1 Opcode fetch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|                                            |      | 1 1 Opcode fetch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|                                            |      | 1 1 1 Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|                                            |      | Acknowledge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|                                            |      | * 0 0 Halt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|                                            |      | * X X Hold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|                                            |      | * X X Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|                                            |      | * = 3-state (high impedance)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|                                            |      | X = unspecified                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|                                            |      | $S_1$ can be used as an advanced R/W status. IO/M, $S_0$ and $S_1$ become valid at the beginning of a machine cycle and remain stable throughout the cycle. The falling edge of ALE may be used to tatch the state of these lines.                                                                                                                                                                                                                                                                                 |  |  |  |

| RD .                                       | 0    | READ CONTROL: A low level on RD indicates the selected memory or I/O device is to be read and that the Data Bus is available for the data transfer, 3-stated during Hold and Halt modes and during RESET.                                                                                                                                                                                                                                                                                                          |  |  |  |

| WR                                         | 0    | WRITE CONTROL: A low level WR indicates the data on the Data Bus is to be written into the selected memory or I/O location. Data is set up at the trailing edge of WR. 3-stated during Hold and Halt modes and during RESET.                                                                                                                                                                                                                                                                                       |  |  |  |

| READY                                      | 1    | READY: If READY is high during a read or write cycle, it indicates that the memory or peripheral is ready to send or receive data. If READY is low, the cpu will wait an integral number of clock cycles for READY to go high before completing the read or write cycle. READY must conform to specified setup and hold times.                                                                                                                                                                                     |  |  |  |

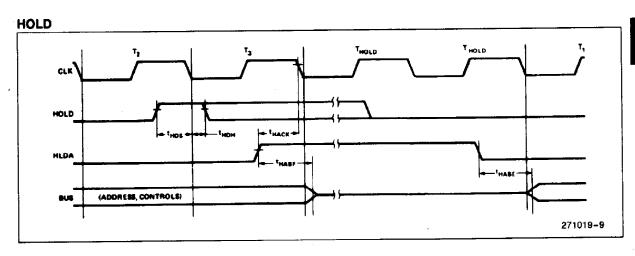

| HOLD                                       | ı    | HOLD: Indicates that another master is requesting the use of the address and data buses. The cpu, upon receiving the hold request, will relinquish the use of the bus as soon as the completion of the current bus transfer. Internal processing can continue. The processor can regain the bus only after the HOLD is removed. When the HOLD is acknowledged, the Address, Data RD, WR, and IO/M lines are 3-stated.                                                                                              |  |  |  |

| HLDA                                       | 0    | HOLD ACKNOWLEDGE: Indicates that the cpu has received the HOLD request and that it will relinquish the bus in the next clock cycle. HLDA goes low after the Hold request is removed. The cpu takes the bus one half clock cycle after HLDA goes low.                                                                                                                                                                                                                                                               |  |  |  |

| INTR                                       | I    | INTERRUPT REQUEST: Is used as a general purpose interrupt. It is sampled only during the next to the last clock cycle of an instruction and during Hold and Halt states. If it is active, the Program Counter (PC) will be inhibited from incrementing and an INTA will be issued. During this cycle a RESTART or CALL instruction can be inserted to jump to the interrupt service routine. The INTR is enabled and disabled by software. It is disabled by Reset and immediately after an interrupt is accepted. |  |  |  |

| INTA                                       | 0    | INTERRUPT ACKNOWLEDGE: Is used instead of (and has the same timing as) RD during the Instruction cycle after an INTR is accepted. It can be used to activate an M8259A Interrupt chip or some other interrupt port.                                                                                                                                                                                                                                                                                                |  |  |  |

| RST 5.5<br>RST 6.5<br>RST 7.5              | I    | RESTART INTERRUPTS: These three inputs have the same timing as INTR except they cause an internal RESTART to be automatically inserted. The priority of these interrupts is ordered as shown in Table 2. These interrupts have a higher priority than INTR. In addition, they may be individually masked out using the SIM instruction.                                                                                                                                                                            |  |  |  |

Table 1. Pin Description (Continued)

| Symbol Type TRAP I              |   | Name and Function  TRAP: Trap interrupt is a nonmaskable RESTART interrupt. It is recognized at the same time as INTR or RST 5.5–7.5. It is unaffected by any mask or interrupt Enable. It has the highest priority of any interrupt. (See Table 2.)                           |  |  |  |

|---------------------------------|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                 |   |                                                                                                                                                                                                                                                                                |  |  |  |

| RESET OUT                       | 0 | RESET OUT: Reset Out indicates CPU is being reset. Can be used as a system reset. The signal is synchronized to the processor clock and lasts an integral number of clock periods.                                                                                             |  |  |  |

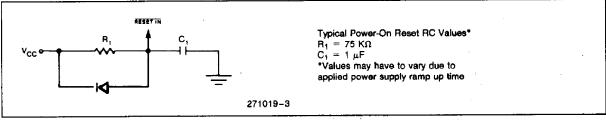

| X <sub>1</sub> , X <sub>2</sub> | l | X <sub>1</sub> and X <sub>2</sub> : Are connected to a crystal LC or RC network to drive the internal clock gene<br>X <sub>1</sub> can also be an external clock input from a logic gate. The input frequency is divided to give the processor's internal operating frequency. |  |  |  |

| CLK                             | 0 | CLOCK: Clock output for use as a system clock. The period of CLK is twice the X <sub>1</sub> , X <sub>2</sub> in period.                                                                                                                                                       |  |  |  |

| SID                             | ļ | SERIAL INPUT DATA LINE: The data on this line is loaded into accumulator bit 7 whenever a RIM instruction is executed.                                                                                                                                                         |  |  |  |

| SOD                             | 0 | SERIAL OUTPUT DATA LINE: The output SOD is set or reset as specified by the SIM instruction.                                                                                                                                                                                   |  |  |  |

| V <sub>CC</sub>                 |   | POWER: +5 volt supply.                                                                                                                                                                                                                                                         |  |  |  |

| V <sub>SS</sub>                 |   | GROUND: Reference.                                                                                                                                                                                                                                                             |  |  |  |

Table 2. Interrupt Priority, Restart Address and Sensitivity

| Name    | Priority | Address Branched To (1) When Interrupt Occurs | Type Trigger                             |  |

|---------|----------|-----------------------------------------------|------------------------------------------|--|

| TRAP    | 1        | 24H                                           | Rising Edge AND High Level Until Sampled |  |

| RST 7.5 | 2        | 3CH                                           | CH Rising Edge Latched                   |  |

| RST 6.5 | 3        | 34H                                           | High Level Until Sampled                 |  |

| RST 5.5 | 4        | 2CH                                           | High Level Until Sampled                 |  |

| INTR    | 5        | (Note 2)                                      | High Level Until Sampled                 |  |

### NOTES:

- 1. The processor pushes the PC on the stack before branching to the indicated address.

- 2. The address branched to depends on the instruction provided to the cpu when the interrupt is acknowledged.

Figure 3. Power-On Reset Circuit

### NOTE:

Additional details on the M8085AH's operation are available by referring to the MCS-80/85 Microprocessor section of the Microsystem Components Handbook. Topics covered include: a functional description; interrupt and serial I/O operation; how to generate wait states; and driving the  $X_1$  and  $X_2$  (clock) inputs. Basic system timing and interface techniques are also described.

### **ABSOLUTE MAXIMUM RATINGS\***

Case Temperature Under Bias(1). -55°C to +125°C

Storage Temperature ..... -65°C to + 150°C

Voltage on Any Pin with

Respect to Ground ..... -0.5V to +7V

Power Dissipation ..... 1.5W

NOTICE: This is a production data sheet. The specifications are subject to change without notice.

\*WARNING: Stressing the device beyond the "Absolute Maximum Ratings" may cause permanent damage. These are stress ratings only. Operation beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.

### D.C. CHARACTERISTICS

$T_C^{(1)} = -55$ °C to +125°C,  $V_{CC} = 5V \pm 10$ %,  $V_{SS} = 0V$ ; unless otherwise specified

| Symbol           | Parameter                   | Min  | Max                   | Units | Test Conditions                           |

|------------------|-----------------------------|------|-----------------------|-------|-------------------------------------------|

| V <sub>IL</sub>  | Input Low Voltage           | -0.5 | +0.8                  | ٧     |                                           |

| V <sub>IH</sub>  | Input High Voltage          | 2.2  | V <sub>CC</sub> + 0.5 | ٧     |                                           |

| V <sub>OL</sub>  | Output Low Voltage          |      | 0.45                  | ٧     | I <sub>OL</sub> = 2 mA                    |

| V <sub>OH</sub>  | Output High Voltage         | 2.4  |                       | V     | $I_{OH} = -400 \mu\text{A}$               |

| lcc              | Power Supply Current        |      | 200                   | mA    |                                           |

| I <sub>IL1</sub> | Input Leakage; Except Pin 1 |      | ±10                   | μА    | 0 ≤ V <sub>IN</sub> ≤ V <sub>CC</sub>     |

| IIL2             | Input Leakage Pin 1         |      | ±70                   | μΑ    | $0 \le V_{IN} \le V_{CC}$                 |

| lo               | Output Leakage              |      | ± 10                  | μΑ    | 0.45 ≤ V <sub>OUT</sub> ≤ V <sub>CC</sub> |

| V <sub>ILR</sub> | Input Low Level, RESET      | -0.5 | +0.8                  | V     |                                           |

| V <sub>IHR</sub> | Input High Level, RESET     | 2.4  | V <sub>CC</sub> + 0.5 | V     |                                           |

| V <sub>HY</sub>  | Hysteresis, RESET           | 0.25 |                       | V     |                                           |

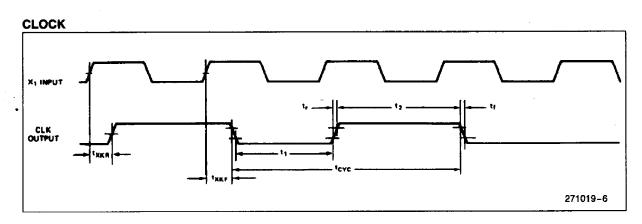

## A.C. CHARACTERISTICS $T_C(1) = -55^{\circ}C$ to $+125^{\circ}C$ , $V_{CC} = 5V \pm 10\%$ , $V_{SS} = 0V$

| Symbol                          | Parameter                                                          | M808 | Units |       |

|---------------------------------|--------------------------------------------------------------------|------|-------|-------|

| Зушьог                          | rai ailletei                                                       | Min  | Max   | Oints |

| tcyc                            | CLK Clock Period                                                   | 320  | 2000  | ns    |

| t <sub>1</sub>                  | CLK Low Time (Standard CLK Loading)                                | 80   |       | ns    |

| t <sub>2</sub>                  | CLK High Time (Standard CLK Loading)                               | 120  |       | ns    |

| t <sub>r</sub> , t <sub>f</sub> | CLK Rise and Fall Time                                             |      | 30    | ns    |

| txkr                            | X <sub>1</sub> Rising to CLK Rising                                | 20   | 120   | ns    |

| txkF                            | X <sub>1</sub> Hising to CLK Falling                               | 20   | 150   | ns    |

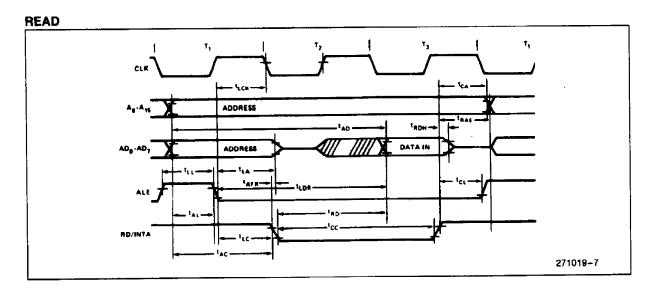

| t <sub>AC</sub>                 | A <sub>8-15</sub> Valid to Leading Edge of Control <sup>(1)</sup>  | 270  |       | ns    |

| t <sub>ACL</sub>                | A <sub>0-7</sub> Valid to Leading Edge of Control                  | 240  |       | ns    |

| t <sub>AD</sub>                 | A <sub>0-15</sub> Valid to Valid Data In                           |      | 575   | ns    |

| t <sub>AFR</sub>                | Address Float After Leading Edge of READ (INTA)                    |      | 0     | ns    |

| t <sub>AL</sub>                 | A <sub>8-15</sub> Valid Before Trailing Edge of ALE <sup>(1)</sup> | 90   |       | ns    |

| t <sub>ALL</sub>                | A <sub>0-7</sub> Valid Before Trailing Edge of ALE                 | 70   |       | ns    |

### NOTE:

<sup>1.</sup> Case temperatures are "instant on."

## A.C. CHARACTERISTICS (Continued)

| Symbol            | Parameter                                             | M808 | Units |    |  |

|-------------------|-------------------------------------------------------|------|-------|----|--|

| Symbol            | ratatiletei                                           |      | Max   |    |  |

| t <sub>ARY</sub>  | READY Valid from Address Valid                        |      | 220   | ns |  |

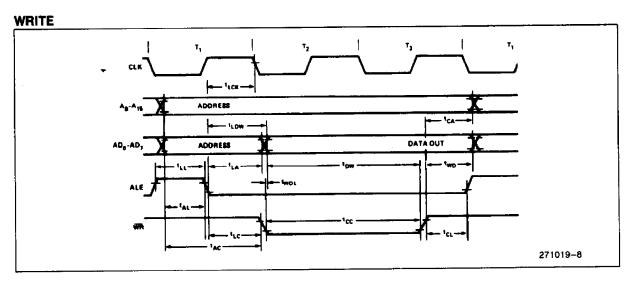

| t <sub>CA</sub>   | Address (A <sub>8-15</sub> ) Valid After Control      | 120  |       | ns |  |

| tcc               | Width of Control Low (RD, WR, INTA) Edge of ALE       | 400  |       | ns |  |

| t <sub>CL</sub>   | Trailing Edge of Control to Leading Edge of ALE       | 50   |       | ns |  |

| t <sub>DW</sub>   | Data Valid to Trailing Edge of WRITE                  | 420  |       | ns |  |

| t <sub>HABE</sub> | HLDA to Bus Enable                                    |      | 210   | ns |  |

| t <sub>HABF</sub> | Bus Float After HLDA                                  |      | 210   | ns |  |

| t <sub>HACK</sub> | HLDA Valid to Trailing Edge of CLK                    | 110  |       | ns |  |

| tHDH              | HOLD Hold Time                                        | 0    |       | ns |  |

| tHDS              | HOLD Setup Time to Trailing Edge of CLK               | 170  |       | ns |  |

| tinh              | INTR Hold Time                                        | 0    |       | ns |  |

| tins              | INTR, RST, and TRAP Setup Time to Falling Edge of CLK | 160  |       | ns |  |

| tLA               | Address Hold Time After ALE                           | 100  |       | ns |  |

| tLC               | Trailing Edge of ALE to Leading Edge of Control       | 130  |       | ns |  |

| t <sub>LCK</sub>  | ALE Low During CLK High                               | 100  |       | ns |  |

| tLDR              | ALE to Valid Data During Read                         |      | 460   | ns |  |

| tLDW              | ALE to Valid Data During Write                        |      | 200   | ns |  |

| t <sub>LL</sub>   | ALE Width                                             | 140  |       | ns |  |

| tLRY              | ALE to READY Stable                                   |      | 110   | ns |  |

| t <sub>RAE</sub>  | Trailing Edge of READ to Re-Enabling of Address       | 150  |       | ns |  |

| t <sub>RD</sub>   | READ (or INTA) to Valid Data                          |      | 300   | ns |  |

| t <sub>RV</sub>   | Control Trailing Edge to Leading Edge of Next Control | 400  |       | ns |  |

| t <sub>RDH</sub>  | Data Hold Time After READ INTA                        | 0    |       | ns |  |

| tRYH              | READY Hold Time                                       | 0    |       | ns |  |

| t <sub>RYS</sub>  | READY Setup Time to Leading Edge of CLK               | 110  |       | ns |  |

| t <sub>WD</sub>   | Data Valid After Trailing Edge of WRITE               | 100  |       | ns |  |

| twDL              | LEADING Edge of WRITE to Data Valid                   |      | 40    | ns |  |

<sup>1.</sup>  $A_8-A_{15}$  address Specs apply IO/ $\overline{M}$ ,  $S_0$ , and  $S_1$  except  $A_8-A_{15}$  are undefined during  $T_4-T_6$  of OF cycle whereas IO/ $\overline{M}$ ,  $S_0$ , and  $S_1$  are stable.

<sup>50,</sup> and 51 are stable.

2. Test Conditions: t<sub>CYC</sub> = 320 ns (M8085AH); C<sub>L</sub> = 150 pF.

3. For all output timing where C<sub>L</sub> ≠ 150 pF use the following correction factors: 25 pF ≤ C<sub>L</sub> < 150 pF: -0.10 ns/pF</li>

150 pF ≤ C<sub>L</sub> ≤ 300 pF; +0.30 ns/pF

4. Output timings are measured with purely capacitive load.

5. To extend the similar appendictions at other values of the pure Table 5.

<sup>5.</sup> To calculate timing specifications at other values of t<sub>CYC</sub> use Table 5.

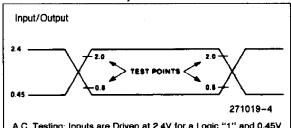

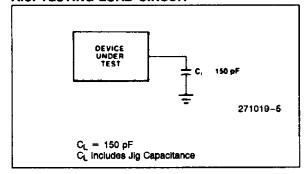

### A.C. TESTING INPUT, OUTPUT WAVEFORM

A.C. Testing; Inputs are Driven at 2.4V for a Logic "1" and 0.45V for a Logic "0". Tirning Measurements are made at 2.0V for a Logic "1" and 0.8V for a Logic "0".

## A.C. TESTING LOAD CIRCUIT

Table 5. Bus Timing Specification as T<sub>CYC</sub> Dependent

| Symbol           | M8085AH           |         |

|------------------|-------------------|---------|

| tal              | (1/2) T — 45      | Minimum |

| tLA              | (1/2) T - 60      | Minimum |

| tLL              | (1/2) T - 20      | Minimum |

| †LCK             | (1/2) T - 60      | Minimum |

| tLC              | (1/2) T - 30      | Minimum |

| t <sub>AD</sub>  | (5/2 + N) T - 225 | Maximum |

| t <sub>RD</sub>  | (3/2 + N) T - 180 | Maximum |

| t <sub>RAE</sub> | (1/2) T — 10      | Minimum |

| tCA              | (1/2) T — 40 .    | Minimum |

| t <sub>DW</sub>  | (3/2 + N) T - 60  | Minimum |

| twp              | (1/2) T - 60      | Minimum |

| Symbol            | M8085AH          |         |

|-------------------|------------------|---------|

| tcc               | (3/2 + N) T - 80 | Minimum |

| <sup>t</sup> CL   | (1/2) T - 110    | Minimum |

| tary              | (3/2) T - 260    | Maximum |

| <sup>t</sup> hack | (1/2) T - 50     | Minimum |

| tHABF             | (1/2) T + 50     | Maximum |

| tHABE             | (1/2) T - 50     | Maximum |

| t <sub>AC</sub>   | (2/2) T - 50     | Minimum |

| t <sub>1</sub>    | (1/2) T - 80     | Minimum |

| t <sub>2</sub>    | (1/2) T - 40     | Minimum |

| t <sub>RV</sub>   | (3/2) T - 80     | Minimum |

| t <sub>LDR</sub>  | (4/2) T — 180    | Minimum |

### NOTE:

N is equal to the total WAIT states.  $T = t_{CYC}$ .

### **WAVEFORMS**

# WAVEFORMS (Continued)

# **WAVEFORMS** (Continued)

### INTERRUPT AND HOLD