# μPD31442 RAB<sup>2</sup>IT-MEMC Memory Controller A Component of the RAB<sup>2</sup>IT Chip Set

# **Preliminary Information**

October 1994

#### **RAB2IT Chip Set**

The RISC Architecture Bus-Bridge Interface Technology (RAB²IT) chip set is a high-performance system solution for the RISC 64-bit architecture. The RAB²IT interface between the main memory, external I/O devices, and the VR4000™ family of microprocessors provides scalable performance that meets a variety of requirements. Two highly integrated VLSI components, RAB²IT-IOC and RAB²IT-MEMC, enable users to configure various system architectures from low-cost, lowend systems to high-performance workstations.

#### **Features**

- Highly integrated

- Secondary cache controller: supports 1M-byte secondary cache

- DRAM controller: supports high-speed synchronous DRAM and standard DRAM

- Data buffer: integrates data bus driver and parity generation logic

- Supports fully i486 CPU compatible interface

- □ Tightly coupled interface of high-speed VR4400™ (4000)PC/SC microprocessors and low-cost VR4200™ microprocessor

- Flexible system configuration

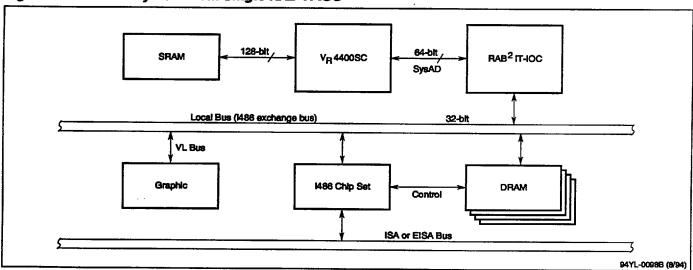

- Low-cost i486™ upgrade system with one RAB2IT-IOC (figure 1)

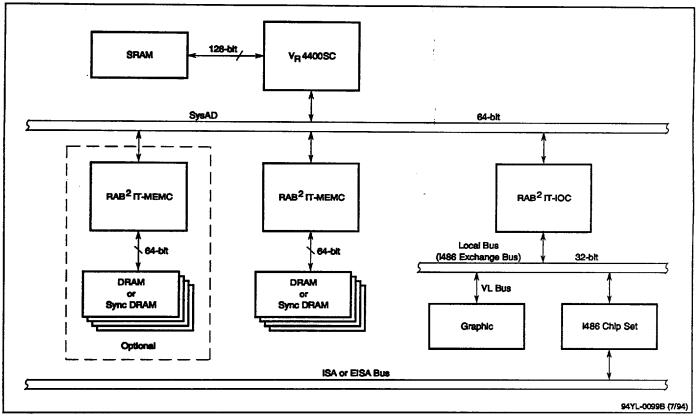

- High-performance VR4400 (4000)SC system with both RAB2IT-IOC and -MEMC (figure 2)

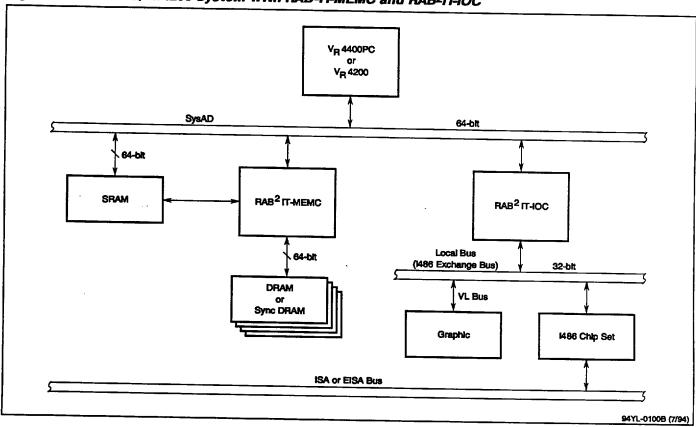

- High-performance VR4400 (4000)PC or VR4200 system with both RAB2IT-IOC and -MEMC to support local secondary cache (figure 3)

- Flexible memory implementation

- High-speed DRAM

- Synchronous DRAM

- i486 fully compatible local bus interface

- Big endian and little endian support

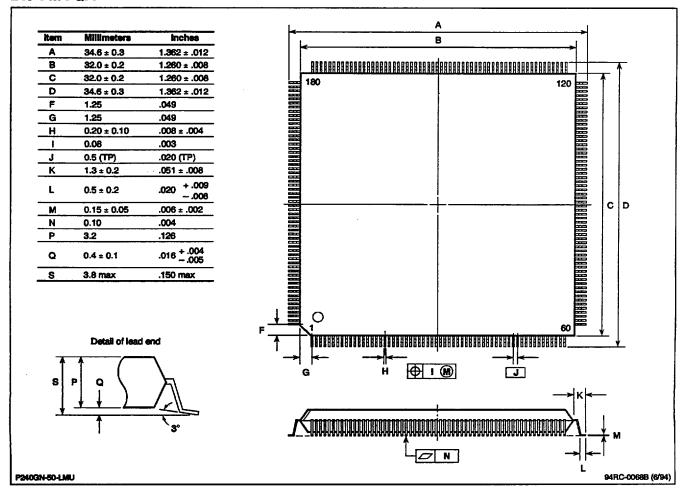

- 240-pin PQFP package

- 3.3-volt operation with 5-volt capability

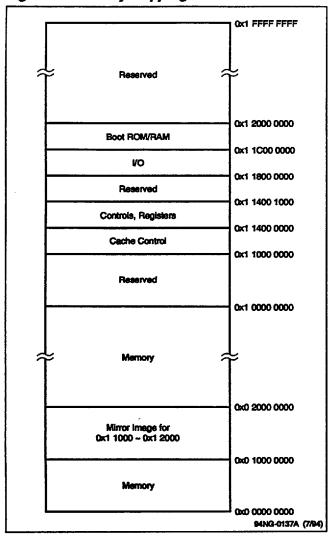

# System Address Mapping

Refer to figure 4, table 1, and table 2.

RAB2IT has an 8-gigabyte area for 33-bit addresses. In a VR4400/VR4000 (36-bit address) system, a mirror image appears due to the insufficient decoding (only 33-bit addresses are decoded). In the address area, the high-order 4 gigabytes are allocated to the system and the low-order 4 gigabytes are used as the memory area. The area between 0x0 1000 0000 and 0x0 1FFF FFFF can be allocated as an I/O area and internal register area according to the setting of the internal registers.

The addresses of the internal registers and the I/O area are allocated to 0x0 1000 0000 through 0x0 1FFF FFFF and 0x1 1000 0000 through 0x1 1FFF FFFF on reset. The area between 0x0 1000 0000 and 0x0 1FFF FFFF can be allocated to the I/O area by setting the Device Control register.

RAB2IT-MEMC samples the RAO state on reset to allocate the internal register address area if two -MEMCs are operating in parallel.

The area between 0x0 0000 0000 and 0x0 FFFF FFFF has to be set by the user; otherwise, the external agents might use this space later on. When the CPU issues an address in the RAB2IT-IOC I/O area, RAB2IT-IOC puts the low-order 16-bit address to the 486 compatible bus. The high-order 16-bit address is unchanged or 0 according to the mode select.

In a multiple external agents system (RAB2IT-IOC and -MEMC), the SysAD bus arbitration is done by decoding the given address map on each agent.

VR4000, VR4200, and VR4400 are trademarks of NEC Corporation i486 is a trademark of Intel Corporation.

50884

🖿 6427525 OlO3l8l T49 🖿

Figure 1. VR440SC System With Single RAB2IT-IOC

Figure 2. VR440SC System With RAB2IT-MEMC and RAB2IT-IOC

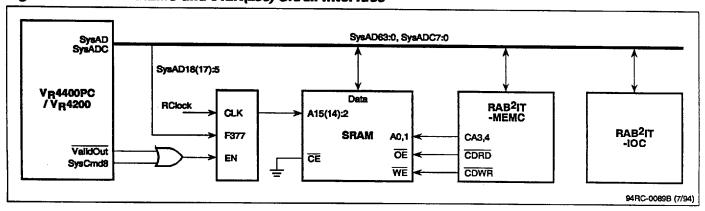

Figure 3. VR4400PC/VR4200 System With RAB2IT-MEMC and RAB2IT-IOC

Figure 4. Memory Mapping

Table 1. Address Map

| Addresses on SysAD            | Address on 486 Compatible Bus                                                   | Name                                    | Bus Master                                    |

|-------------------------------|---------------------------------------------------------------------------------|-----------------------------------------|-----------------------------------------------|

| 0x1 1C00 0000 ~ 0x1 1FFF FFFF | AT = 1: 0x1 1 C00 0000 ~ 0x1 1FFF FFFF<br>AT = 0: 0x0 000E 0000 ~ 0x0 000F FFFF | Boot ROM/RAM area                       | RAB <sup>2</sup> IT-IOC                       |

| 0x1 1800 0000 ~ 0x1 1BFF FFFF | AT = 1: 0x0 1800 0000 ~ 0x0 1BFF FFFF<br>AT = 0: 0x0 0000 0000 ~ 0x0 0000 FFFF  | VO                                      | RAB <sup>2</sup> IT-IOC                       |

| 0x1 1400 1000 ~ 0x1 17FF FFFF | _                                                                               | Reserved                                | Not valid for the RAB <sup>2</sup> IT system. |

| 0x1 1400 0F00 0x1 1400 0FFF   | 0x03                                                                            | Write back cycle                        | RAB <sup>2</sup> IT-IOC                       |

| 0x1 1400 0E00 ~ 0x1 1400 0EFF | 0x02                                                                            | Halt cycle                              |                                               |

| 0x1 1400 0D00 ~ 0x1 1400 0DFF | 0x01                                                                            | Flush cycle                             |                                               |

| 0x1 1400 0C00 ~ 0x1 1400 0CFF | 0x00 or 0x04<br>0x00                                                            | interrupt acknowledge<br>Shutdown cycle |                                               |

| 0x1 1400 0400 ~ 0x1 1400 0BFF |                                                                                 | Reserved                                | Not valid for the RAB <sup>2</sup> IT system. |

. 🖿 6427525 0103184 758 🖿

Table 1. Address Map (cont)

| Addresses on SysAD            | Address on 486 Compatible Bus  | Name                                                                                            | Bus Master               |

|-------------------------------|--------------------------------|-------------------------------------------------------------------------------------------------|--------------------------|

| 0x1 1400 0300 ~ 0x1 1400 03FF |                                | RAB <sup>2</sup> IT-MEMC<br>internal register; RAO =<br>high                                    | RAB <sup>2</sup> IT-MEMC |

| 0x1 1400 0200 ~ 0x1 1400 02FF |                                | RAB <sup>2</sup> IT-MEMC<br>internal register; RAO =<br>high                                    | RAB <sup>2</sup> IT-MEMC |

| 0x1 1400 0000 ~ 0x1 1400 01FF |                                | RAB <sup>2</sup> IT-IOC<br>internal register                                                    | RAB <sup>2</sup> IT-IOC  |

| 0x1 1000 0000 ~ 0x1 13FF FFFF | 0x00 0000 0000 ~ 0x0 0000 FFFF | Cache control                                                                                   | See table 2              |

| 0x1 0000 0000 ~ 0x1 0FFF FFFF |                                | † Reserved                                                                                      |                          |

| 0x0 2000 0000 ~ 0x1 FFFF FFF  |                                | † Memory                                                                                        | ·                        |

| 0x0 1000 0000 ~ 0x0 1FFF FFFF |                                | Mirror image for 0x1 1000<br>0000 ~ 0x1 1FFF FFFF<br>or memory (depends on<br>register setting) |                          |

| 0x0 0000 0000 ~ 0x0 0FFF FFFF |                                | † Memory                                                                                        |                          |

<sup>†</sup> This area will be the memory area on the 486 bus if only RAB<sup>2</sup>IT-IOC is used in the system. This area will be the memory area based on the setting of the memory base address register in the RAB<sup>2</sup>IT-IOC and IT in the system.

Table 2. Cache Control Area

| Device Control Register Bit 20 | SysAD Address                                                  | RAO = 0                    | RAO = 1                    |

|--------------------------------|----------------------------------------------------------------|----------------------------|----------------------------|

| RAMAPIO = 0                    | 0x0 1000 0000 ~ 0x0 11FF FFFF<br>0x1 1000 0000 ~ 0x1 11FF FFFF | Read/Write                 | Write                      |

|                                | 0x0 1200 0000 ~ 0x0 12FF FFFF<br>0x1 1200 0000 ~ 0x1 12FF FFFF | Read/Write                 | Tag memory access disabled |

|                                | 0x0 1300 0000 ~ 0x0 13FF FFFF<br>0x1 1300 0000 ~ 0x1 13FF FFFF | Tag memory access disabled | Read/Write                 |

| RAMAPIO = 1                    | 0x1 1000 0000 ~ 0x1 11FF FFFF                                  | Read/Write                 | Write                      |

|                                | 0x1 1200 0000 ~ 0x1 12FF FFFF                                  | Read/Write                 | Access disabled            |

|                                | 0x1 1300 0000 ~ 0x1 13FF FFFF                                  | Access disabled            | Read/Write                 |

Table 3. Pin Assignments, 240-Pin PQFP

| System<br>Address/Data | Pin No. | System Address/<br>Data/Command | Pin No. | Memory<br>Address/Data | Pin No. | Memory Data | Pin No. |

|------------------------|---------|---------------------------------|---------|------------------------|---------|-------------|---------|

| Sys AD0                | 218     | SysAD50                         | 44      | MAO                    | 182     | MD30        | 130     |

| 1                      | 219     | 51                              | 45      | 1                      | 179     | 31          | 129     |

| 2                      | 220     | 52                              | 46      | 2                      | 178     | 32          | 128     |

| 3                      | 221     | 53                              | 47      | 3                      | 177     | 33          | 127     |

| 4                      | 222     | 54                              | 50      | 4                      | 176     | 34          | 126     |

| 5                      | 223     | 55                              | 51      | 5                      | 175     | 35          | 125     |

| 6                      | 224     | 56                              | 52      | 6                      | 174     | 36          | 124     |

| 7                      | 225     | 57                              | 53      | 7                      | 173     | 37          | 123     |

| 8                      | 226     | 58                              | 54      | 8                      | 172     | 38          | 122     |

| 9                      | 227     | 59                              | 55      | 9                      | 171     | 39          | 119     |

| SysAD10                | 230     | SysAD60                         | 56      | MA10                   | 170     | MD40        | 118     |

| 11                     | 231     | 61                              | 57      | 11                     | 167     | 41          | 117     |

| 12                     | 232     | 62                              | 58      |                        |         | 42          | 116     |

| 13                     | 233     | 63                              | 59      |                        |         | 43          | 115     |

| 14                     | 234     |                                 |         | •                      |         | 44          | 114     |

| 15                     | 235     |                                 |         |                        |         | 45          | 113     |

| 16                     | 236     |                                 | İ       |                        |         | 46          | 112     |

| 17                     | 237     |                                 | 1       |                        |         | 47          | 111     |

| 18                     | 238     |                                 |         |                        | İ       | 48          | 110     |

| 19                     | 239     |                                 |         |                        |         | 49          | 107     |

| SysAD20                | 2       | SysADC0                         | 208     | MDO                    | 166     | MD50        | 106     |

| 21                     | 3       | 1                               | 209     | 1                      | 165     | 51          | 105     |

| 22                     | 4       | 2                               | 210     | 2                      | 164     | 52          | 104     |

| 23                     | 5       | 2<br>3                          | 211     | 3                      | 163     | 53          | 103     |

| 24                     | 6       | 4                               | 212     | 4                      | 162     | 54          | 102     |

| 25                     | 7       | 5<br>6                          | 213     | 5                      | 161     | 55          | 101     |

| 26                     | 8       | 6                               | 214     | 6                      | 160     | 56          | 100     |

| 27                     | 9       | 7                               | 215     | 7                      | 159     | 57          | 99      |

| 28                     | 10      |                                 |         | 8                      | 158     | 58          | 98      |

| 29                     | 11      |                                 |         | 9                      | 155     | 59          | 95      |

| SysAD30                | 14      | SysCmd0                         | 62      | MD10                   | 154     | MD60        | 94      |

| 31                     | 15      | 1                               | 63      | 11                     | 153     | 61          | 93      |

| 32                     | 16      | 2<br>3                          | 64      | 12                     | 152     | 62          | 92      |

| 33                     | 17      | 3                               | 65      | 13                     | 151     | 63          | 91      |

| . 34                   | 18      | 4                               | 66      | 14                     | 150     | 64          | 90      |

| 35                     | 19      | 5                               | 67      | 15                     | 149     | 65          | 89      |

| 36                     | 20      | 6                               | 68      | 16                     | 148     | 66          | 88      |

| 37                     | 21      | 7                               | 69      | 17                     | 147     | 67          | 87      |

| 38                     | 22      | 8                               | 70      | 18                     | 146     | 68          | 86      |

| 39                     | 23      |                                 |         | 19                     | 143     | 69          | 83      |

| SysAD40                | 32      |                                 |         | MD20                   | 142     | MD70        | 82      |

| 41                     | 33      |                                 |         | 21                     | 141     | 71          | 81      |

| 42                     | 34      |                                 |         | 22                     | 140     |             |         |

| 43                     | 35      |                                 |         | 23                     | 139     |             |         |

| 44                     | 38      |                                 |         | 24                     | 138     | ]           |         |

| 45                     | 39      |                                 |         | 25                     | 137     |             |         |

| 46                     | 40      |                                 |         | 26                     | 136     | 1           |         |

| 47                     | 41      |                                 |         | 27                     | 135     |             |         |

| 48                     | 42      |                                 |         | 28                     | 134     |             |         |

| 49                     | 43      |                                 | t .     | 29                     | 131     | i I         |         |

# NEC

Table 3. Pin Assignments, 240-Pin PQFP (cont)

| Clock and Control | Pin No.     | V <sub>DD</sub>                       | Pin No. | Gnd         | Pin No      |                                                  | Ι. |

|-------------------|-------------|---------------------------------------|---------|-------------|-------------|--------------------------------------------------|----|

| BS                | 197         | V <sub>DD</sub>                       | 12      | Gnd         | 1           | <del>                                     </del> |    |

| CA3A              | 202         |                                       | 24      |             | 13          |                                                  | 1  |

| CA3B              | 203         |                                       | 36      |             | 25          |                                                  |    |

| CA4A              | 206         |                                       | 48      |             | 29          |                                                  |    |

| CA4B              | 207         |                                       | 61      |             | 37          |                                                  |    |

| <del></del>       |             |                                       | 72      |             | 49          |                                                  | 1  |

| CDRD              | 201         |                                       | 84      |             | 60          |                                                  | 1  |

| CDWR              | 200         |                                       | 96      |             | 73          |                                                  | į  |

| CKE/SLVC          | 194         |                                       | 108     |             | 85          |                                                  |    |

|                   |             |                                       | 120     |             | 97          |                                                  |    |

| CS0/RAS0          | 188         | V <sub>DD</sub>                       | 132     | Gnd         | <del></del> |                                                  |    |

| CS1/RAS1          | 189         | טטי                                   | 144     | Gna         | 109         |                                                  |    |

| CS2/RAS2          | 190         |                                       | 156     |             | 121         |                                                  |    |

| CS3/RAS3          | 191         |                                       | 168     |             | 133         |                                                  |    |

|                   |             |                                       | 181     |             | 145         |                                                  |    |

| DQM0/CASO         | 183         |                                       | 192     |             | 157         |                                                  |    |

| DQM1/CAS1         | 184         |                                       | 204     |             | 169         |                                                  |    |

| DQM2/CAS2         | 185         | į                                     | 216     | 1           | 180         |                                                  |    |

| DQM3/CAS3         | 186         | İ                                     | 228     |             | 187         |                                                  |    |

|                   | 1           |                                       | 240     | 1           | 193<br>199  |                                                  | 1  |

| PERR              | 80          | · · · · · · · · · · · · · · · · · · · |         | <del></del> |             |                                                  |    |

| PwrRdy            | 31          |                                       |         | Gnd         | 205         | <u> </u>                                         |    |

|                   | 31          |                                       |         |             | 217         |                                                  | i  |

| RA0               | 30          |                                       |         |             | 229         | [                                                |    |

| RClock            | 26          |                                       |         |             |             |                                                  |    |

| Release           | 74          |                                       | 1       |             |             |                                                  | 1  |

| Reset             | 76          | 1                                     |         |             |             |                                                  | Ì  |

| RRelease          | 79          | 1                                     | 1       |             |             |                                                  |    |

| RValidin          | 77          |                                       |         |             |             |                                                  |    |

| RValidOut         | 78          |                                       |         |             |             |                                                  | l  |

|                   | <del></del> |                                       |         | <u></u>     |             |                                                  | Į  |

| SCAS              | 196         |                                       |         |             |             |                                                  |    |

| SRAS              | 195         |                                       |         |             |             |                                                  |    |

| TClock            | 28          |                                       |         |             |             |                                                  |    |

| Validin           |             |                                       |         |             |             |                                                  |    |

| ValidOut          | 71          |                                       |         |             |             |                                                  |    |

| validout          | 27          |                                       |         |             |             |                                                  |    |

| WE                | 400         |                                       |         |             |             |                                                  |    |

| WrRdy             | 198         |                                       |         |             |             |                                                  |    |

| TTINUY            | 75          | 1                                     |         |             |             |                                                  |    |

|                   |             |                                       |         |             |             |                                                  |    |

#### RAB2IT-MEMC MEMORY CONTROLLER

The RAB2IT-MEMC provides the high-performance memory interface solution for the VR4000 family of microprocessors. Due to the high integration, the flexible architecture brings the benefit for a variety of the CPUs and system configurations; for example, the internal secondary cache controller will boost the performance of systems with non-secondary cache controller integrated microprocessors: VR4400PC, VR4000PC, and VR4200. The 64-bit local system memory data bus as well as internal read/write buffers increases the data transfer bandwidth. Two of the RAB2IT-MEMC controllers can even be parallel-connected to the SysAD bus to support a 128-bit local DRAM bus.

#### **Features**

- DRAM and synchronous DRAM

- Secondary cache interface

- Slave mode DMA data transfer

- Ordering of block read response

- Programmable big endian or little endian configuration

- Addresses setting of the internal registers

- Optional dual devices operation

**■** 6427525 0103187 467 **■**

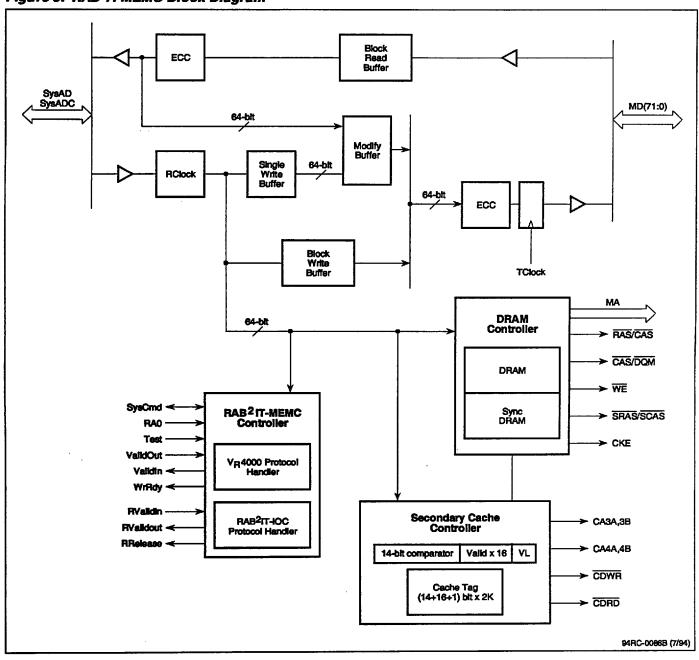

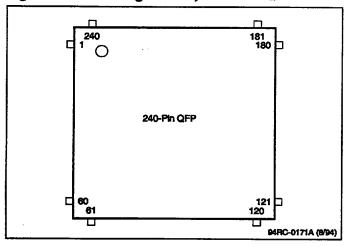

Figure 5 is the RAB2IT-MEMC block diagram, figure 6 is the package pin configuration drawing, table 3 lists package pin assignments, and table 4 describes pin functions.

Figure 5. RAB2IT-MEMC Block Diagram

Table 4. Pin Descriptions, 240-Pin PQFP

| Interface<br>Signals              | Symbol       | * Input/Output | Description                                                                                                                                                                                             |  |  |  |

|-----------------------------------|--------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

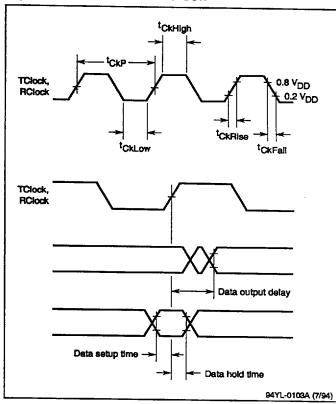

| VR4000 family                     | TClock       | Input          | Transmit clock from CPU establishes the system interface frequency.                                                                                                                                     |  |  |  |

| bus interface                     | RClock       | Input          | Receive clock from CPU establishes the system interface frequency, 90°-phase shift prior to TClock.                                                                                                     |  |  |  |

|                                   | SysAD[63:0]  | Input/Output   | System address and data bus is a 64-bit bus for communication between CPUs.                                                                                                                             |  |  |  |

|                                   | SysADC[7:0]  | Input/Output   | System address and data check bus is an 8-bit bus containing check bits fo the SysAD bus.                                                                                                               |  |  |  |

|                                   | SysCmd(8:0)  | input/Output   | System command and data identifier is a 9-bit bus for transmission between CPUs.                                                                                                                        |  |  |  |

|                                   | Release      | Input          | Release is the CPU response signal indicating that ownership of the system interface is available to the external agent.                                                                                |  |  |  |

|                                   | PWrRdy       | Input          | Processor write ready is the VR4x00 write ready control. It is asserted by the -IOC controller to indicate that the system is ready for the processor write request.                                    |  |  |  |

|                                   | Validin      | Input/Output   | Valid input informs the CPU that an address or data on the SysAD bus and a valid command or data identifier on the SysCmd bus are being driven. External pullup required.                               |  |  |  |

|                                   | ValidOut     | Input          | Valid output is asserted by the CPU to indicate that it is driving a valid address or data on the SysAD bus and a valid command or data ident the SysCmd bus.                                           |  |  |  |

| -                                 | PERR         | Output         | Parity error                                                                                                                                                                                            |  |  |  |

| Slave mode<br>montrol<br>nterface | WrRdy        | Output         | Write ready is the -IOC write ready control. It connects to RWrRdy1 of the -IOC controller to indicate that the memory is ready for the processor write request and DMA write.                          |  |  |  |

|                                   | RValidIn     | Output         | RAB2IT valid input is to inform the -IOC controller that an address or data on the SysAD bus and a valid command or data identifier on the SysCmd bus are being driven to it. External pullup required. |  |  |  |

|                                   | RValidOut    | Input          | RAB2IT valid output is asserted by the -IOC controller to indicate that it is driving a valid address or data on the SysAD bus and a valid command or data identifier on the SysCmd bus.                |  |  |  |

|                                   | RRelease     | Input          | RAB2IT release is the response signal from the -IOC controller to indicate the availability of the system interface                                                                                     |  |  |  |

| Secondary                         | CDRD         | Output         | Cache data read                                                                                                                                                                                         |  |  |  |

| cache interface                   | CDWR         | Output         | Cache data write                                                                                                                                                                                        |  |  |  |

|                                   | CA3(A:B)     | Output         | Least significant cache address, A0                                                                                                                                                                     |  |  |  |

|                                   | CA4(A:B)     | Output         | Second least significant cache address, A1                                                                                                                                                              |  |  |  |

| DRAM and                          | MD(71:0)     | Input/Ouput    | 72-bit memory data bus                                                                                                                                                                                  |  |  |  |

| synchronous<br>DRAM control       | MA(11:0)     | Output         | 12-bit memory address bus                                                                                                                                                                               |  |  |  |

| interface                         | BS           | Output         | Synchronous DRAM bank select                                                                                                                                                                            |  |  |  |

|                                   | WE           | Output         | Write enable                                                                                                                                                                                            |  |  |  |

|                                   | DQM/CAS(3:0) | Output         | Data mask for sync DRAM and column address strobe for regular DRAM.                                                                                                                                     |  |  |  |

|                                   | CS/RAS(3:0)  | Output         | Chip select for sync DRAM and row address strobe for regular DRAM.                                                                                                                                      |  |  |  |

|                                   | CKE/SLVC     | Input/Output   | Clock control for sync DRAM and master/slave control for regular DRAM                                                                                                                                   |  |  |  |

|                                   | SRAS         | Output         | Synchronous DRAM row address strobe                                                                                                                                                                     |  |  |  |

|                                   | SCAS         | Output         | Synchronous DRAM column address strobe                                                                                                                                                                  |  |  |  |

Table 4. Pin Descriptions, 240-Pin PQFP (cont)

| Interface<br>Signals | Symbol | * Input/Output | Description                                   |

|----------------------|--------|----------------|-----------------------------------------------|

| Test and             | Reset  | Input          | Reset must be asserted for any reset sequence |

| initialization       | RA0    | Input          | Initialize internal register address          |

|                      | TEST   | Input          | NEC test pin                                  |

<sup>\*</sup> I/O and O pins are Hi-Z in the Reset state.

Figure 6. Pin Configuration, 240-Pin PQFP

# MICROPROCESSOR INTERFACE

#### **CPU Protocol Handler**

The CPU protocol is the interface between the processor and the RAB2IT chip sets. All elements are identical to the system interface protocol of the VR4000 family processors except CPU WrRdy should be connected to PWrRdy of RAB2IT-MEMC.

#### Read Buffer

One 8-byte, 16-stage read buffer of the RAB2IT-MEMC gives the best processor read request performance to match the maximum readblock size (32-word) of VR4400SC. The effective data size is set by SysCmd in an address cycle.

#### **Write Buffers**

Two 8-byte wide write buffers—single- and block-write—of the RAB2IT-MEMC reduce the pipeline stall cycles during the processor write request.

The two-stage single-write butffer consecutively accepts doubleword, word, and partial word processor writes. The 16-stage buffer for block write, including memory write and DMA write, matches the maximum write block size (32-word) of VR4400SC. The effective data size is set by SysCmd in an address cycle.

RAB2IT-MEMC drives the WrRdy and PWrRdy active (low) all the time except if the first stage of the single-write buffer or any stage of the block-write buffer is filled. In addition, it performs weight control for all stages of the buffers to secure the received write data without failure. However, if single-write or block-write fails to receive the "busy" status of WrRdy, the buffer weight control cannot be performed.

#### **Address Register/Command Register**

An address register is to hold and decode addresses on the SysAD bus, and a command register is to hold and decode the system interface commands. The addresses of data that have been decoded and match the address area of the RAB2IT-MEMC will be registered in the address queue.

#### **RAB2IT-MEMC Controller**

A five-stage address queue handles the SysAD input and a one-stage address queue is used for SysAD output. Two out of five stages in the input SysAD queue are used for the DMA bypass access.

The values of the 32-bit registers are copied to both high-order and low-order bits of the data bus during a register read cycle. On a register write cycle, the high-order 32-bit data on the data bus is written to the 32-bit register when the big endian configuration is set on word write mode. Otherwise, the low-order 32-bit data on the data bus is written to the 32-bit register with the little endian configuration.

#### **MEMORY INTERFACE**

# **DRAM Controller**

The DRAM controller in RAB2IT-MEMC is capable of controlling the standard high-speed DRAM interface as well as a synchronous DRAM interface.

The RAB2IT-MEMC does not process the data but swaps, redirects, or merges the data among system memory, processor or I/O interface according to the endian configuration and data size.

ECC/Parity. RAB2IT-MEMC generates 1-bit correction and 2-bit detection for the ECC (Error Checking and Correcting) code during DRAM or sync DRAM access cycles by setting the device control register. RAB2IT-MEMC can also use the parity on SysAD bus operation.

Word Write. On doubleword, word, or partial word write cycles, RAB2IT-MEMC reads the data at the appropriate addresses in memory as doubleword data and rewrites the valid data by merging them. On processor read cycles, the RAB2IT-MEMC always sends the doubleword data to the processor. The processor will fetch the valid word or partial word data internally during the non-doubleword read cycles. The ECC code is included in the rewritten data when the ECC function is on. The data is correct if a 1-bit error is found.

Endian. The byte order of the doubleword (64-bit), word (32-bit), half-word (16-bit), and byte (8-bit) can be designated in big endian or little endian by a device

control register in RAB2IT-MEMC. See figures 7 and 8.

Figure 7. Addresses of Bytes Within Doublewords; Big-Endian Byte Alignment

|    |    |    |             |    |    |    |    | Doubleword |

|----|----|----|-------------|----|----|----|----|------------|

| 64 |    |    |             |    |    |    | 0  | Address    |

| 16 | 17 | 18 | 19          | 20 | 21 | 22 | 23 | 16         |

| 8  | 9  | 10 | 11          | 12 | 13 | 14 | 15 | 10         |

| 0  | 1  | 2  | 3           | 4  | 5  | 6  | 7  | 8          |

|    |    |    | <del></del> | ·  |    | L  |    | 0          |

- Most-significant byte is at lowest address.

- Word is addressed by byte address of most-significant byte.

Figure 8. Addresses of Bytes Within Doublewords; Little-Endian Byte Alignment

|    |    |    |    |    |    |          |    | Doubleword |

|----|----|----|----|----|----|----------|----|------------|

| 34 |    |    |    |    |    |          | 0  | Address    |

| 23 | 22 | 21 | 20 | 19 | 18 | 17       | 16 | 16         |

| 15 | 14 | 13 | 12 | 11 | 10 | 9        | 8  | 10         |

| 7  | 6  | 5  | 4  | 3  | 2  | 1        | 0  | 8          |

|    |    |    | ·  |    | ·  | <u> </u> |    | ۱ ۵        |

- Least-significant byte is at lowest address.

- Word is addressed by byte address of least-significant byte.

Table 5. Memory Type and Size for VR4x00/RAB2IT System

|                          |                                               |                                                | Rema                          | ks               |

|--------------------------|-----------------------------------------------|------------------------------------------------|-------------------------------|------------------|

| Type of SIMM             | Size In Minimum<br>Configuration<br>(2 SIMMs) | Number of SIMMs in<br>Maximum<br>Configuration | Double-Sided/Single-<br>Sided | NEC Product Code |

| 1M x 36 bit (4M byte)    | 8M byte                                       | 8                                              | Single                        | MC-421000A36     |

| 2M x 36 bit (8M byte)    | 16M byte                                      | 4                                              | Double                        | MC-422000A36     |

| 4M x 36 bit (16M byte)   | 32M byte                                      | 8                                              | Single                        | MC-424000A36     |

| 8M x 36 bit (32M byte)   | 64M byte                                      | 4                                              | Double                        | MC-428000A36     |

| 16M x 36 bit (64M byte)  | 128M byte                                     | 8                                              | Single                        |                  |

| 32M x 36 bit (128M byte) | 256M byte                                     | 4                                              | Double                        |                  |

#### Notes:

- The different memory-size SIMMs can be installed simultaneously.

- (2) Two banks for one double-sided SIMM.

- (3) In master/slave mode, the memory configurations of master side and slave side should be identical.

#### **DRAM Protocol Handler**

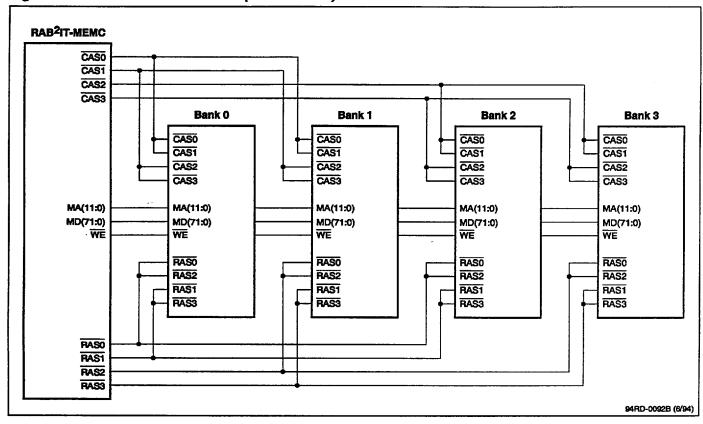

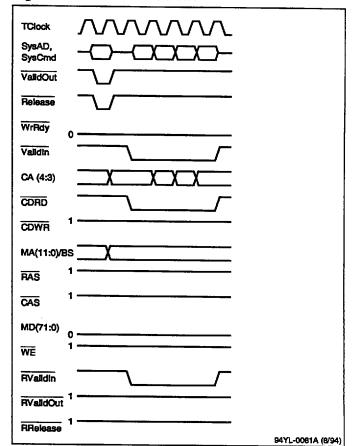

The standard DRAM interface—RAS, CAS, and multiplexed address—is controlled by the DRAM protocol handler. It is able to support the system memory configuration from 8M-byte to 512M-byte with the DRAM type from 4M (1M x 36) to 128M (32M x 36) DRAMs. See table 5 for details. Figure 9 and table 6 illustrate the four memory banks system configurations.

**■** 6427525 0103191 998 **■**

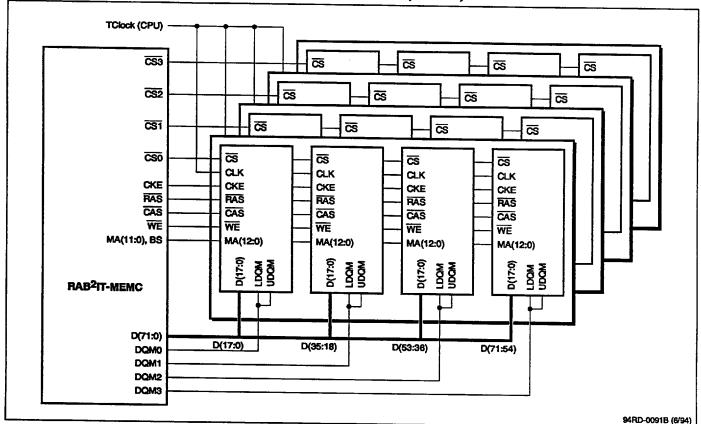

Figure 9. RAB2IT-MEMC and DRAM (72-Pin SIMM) Interface

Table 6. Memory and Capacity In Each Bank

|      | Memory |     |     |        |

|------|--------|-----|-----|--------|

| 0    | 1      | 2   | 3   | - Size |

| 8M   |        |     |     | 8M     |

| 8M   | 8M     |     |     | 16M    |

| 8M   | 8M     | 8M  |     | 24M    |

| 8M   | 8M     | 8M  | 8M  | 32M    |

| 32M  |        |     |     | 32M    |

| 32M  | 8M     |     |     | 40M    |

| 32M  | 8M     | 8M  |     | 48M    |

| 32M  | 8M     | 8M  | 8M  | 56M    |

| 32M  | 32M    |     |     | 64M    |

| 32M  | 32M    | 8M  |     | 72M    |

| 32M  | 32M    | 8M  | 8M  | MO8    |

| 32M  | 32M    | 32M |     | 96M    |

| 32M  | 32M    | 32M | 8M  | 104M   |

| 32M  | 32M    | 32M | 32M | 128M   |

| 128M |        |     |     | 128M   |

| 128M | 8M     | . • |     | 136M   |

| 128M | 8M     | 8M  |     | 144M   |

| 128M | 8M     | 8M  | 8M  | 152M   |

| 128M | 32M    |     |     | 160M   |

| 128M | 32M    | 8M  |     | 168M   |

|      |      | Memory |      |      |

|------|------|--------|------|------|

| 0    | 1    | 2      | 3    | Size |

| 128M | 32M  | 8M     | 8M   | 176M |

| 128M | 32M  | 32M    |      | 192M |

| 128M | 32M  | 32M    | 8M   | 200M |

| 128M | 32M  | 32M    | 32   | 224M |

| 128M | 128M |        |      | 256M |

| 128M | 128M | 8M     |      | 264M |

| 128M | 128M | 8M     | 8M   | 272M |

| 128M | 128M | 32M    |      | 288M |

| 128M | 128M | 32M    | 8M   | 296M |

| 128M | 128M | 32M    |      | 320M |

| 128M | 128M | 128M   |      | 384M |

| 128M | 128M | 128M   | 8M   | 392M |

| 128M | 128M | 128M   | 32M  | 416M |

| 128M | 128M | 128M   | 128M | 512M |

Note: Two 72-pin SIMMs are counted as one bank if single-sided or two banks if double-sided.

Figure 10. RAB2IT-MEMC and Synchronous DRAM Interface (1M x 18)

# Synchronous DRAM Protocol Handler

The synchronous DRAM protocol handler is to control SRAS, SCAS, CKE, CS, and the multiplexed address of the synchronous DRAM interface. It is able to support configurations from 8M-byte to 64M-byte with 2M (1M  $\times$  18 or 2M  $\times$  9) synchronous DRAMs. See table 7 for details. Table 8 and figure 10 illustrate the four memory banks system configurations.

Table 7. Synchronous DRAM Type and Size for VR 4x00/RAB2IT System

| Туре        | Minimum Config | NEC Product |            |

|-------------|----------------|-------------|------------|

|             | Size           | Number      | Code       |

| 1M x 18-bit | 8M byte        | 8           | μPD4516181 |

| 2M x 9-bit  | 16M byte       | 4           | μPD4516821 |

| 1M x 18-bit | 32M byte       | 16          | μPD4516181 |

| 2M x 9-bit  | 64M byte       | 32          | μPD4516821 |

Table 8. Synchronous DRAM Memory and Capacity In Each Bank

|     | Memor | Memory Bank |     |      |  |  |  |

|-----|-------|-------------|-----|------|--|--|--|

| 0   | 1     | 2           | 3   | Size |  |  |  |

| 8M  |       |             |     | 8M   |  |  |  |

| 8M  | 8M    |             |     | 16M  |  |  |  |

| 8M  | 8M    | 8M          |     | 24M  |  |  |  |

| 8M  | 8M    | 8M          | 8M  | 32M  |  |  |  |

| 16M |       |             |     | 16M  |  |  |  |

| 16M | 8M    |             |     | 24M  |  |  |  |

| 16M | 8M    | 8M          |     | 32M  |  |  |  |

| 16M | 8M    | 8M          | 8M  | 40M  |  |  |  |

| 16M | 16M   |             |     | 32M  |  |  |  |

| 16M | 16M   | 8M          |     | 40M  |  |  |  |

| 16M | 16M   | 8M          | 8M  | 48M  |  |  |  |

| 16M | 16M   | 16M         |     | 48M  |  |  |  |

| 16M | 16M   | 16M         | 8M  | 56M  |  |  |  |

| 16M | 16M   | 16M         | 16M | 64M  |  |  |  |

The synchronous DRAM mode should be set prior to operation of the synchronous DRAM access cycle. The mode should be set as follows.

Burst size = 2

CAS latency = 2 or 3

Wrap type may be either sequential or interleave (The same operation is performed when burst size = 2.)

The mode does not support a unique function from a manufacturer.

Ten commands for synchronous DRAMs are listed below.

Mode register set

**CBR** refresh

Entry self-refresh

Self-refresh end

Bank active

Write

Write and autoprecharge

Read

Read and autoprecharge

Data mask

Block write, partial write, block read, and partial read cycles are initiated by the processor or the -IOC controller. The -MEMC controller generates the corresponding synchronous DRAM interface protocol to accomplish the access cycles.

A refresh timer that has been initialized requests the refresh cycles at certain time intervals. The refresh cycles occur by issuing the "CBR refresh" command. But the command should not be issued until the RAS high pulse width meets the timing set in the DRAM speed register and all of the chip select signals are active. The self-refresh function is also provided when the DRAM sleep control register is set.

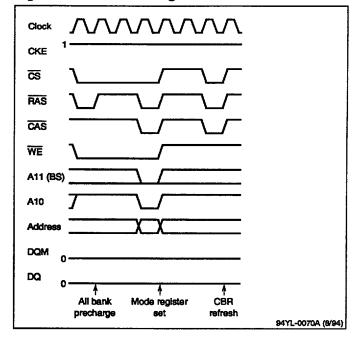

Mode Setting. Setting is done by writing 0021H or 0031H into the synchronous DRAM mode register. After the register is set, the "all bank precharge" command is issued followed by the "mode register set" command three clocks later. Then, wait for three or more clocks to activate "CBR refresh" twice and terminate the mode setting. See figure 11.

Figure 11. Mode Setting

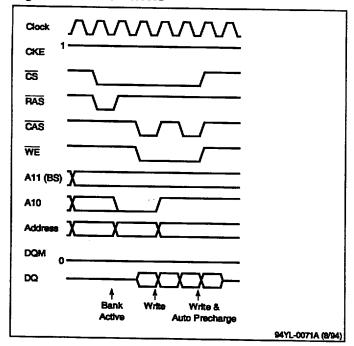

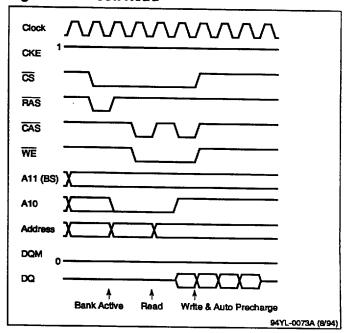

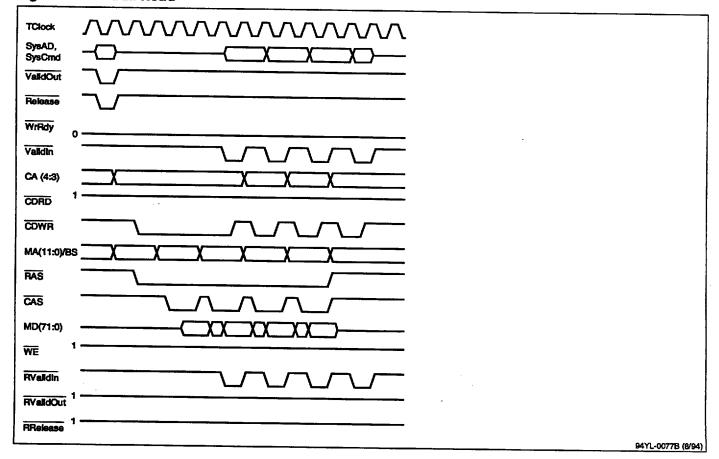

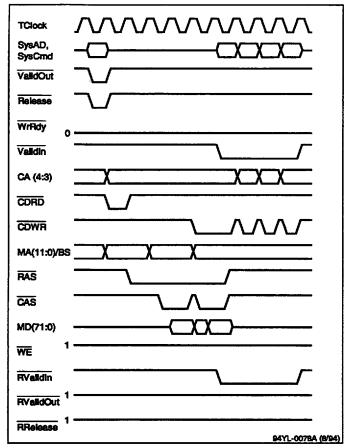

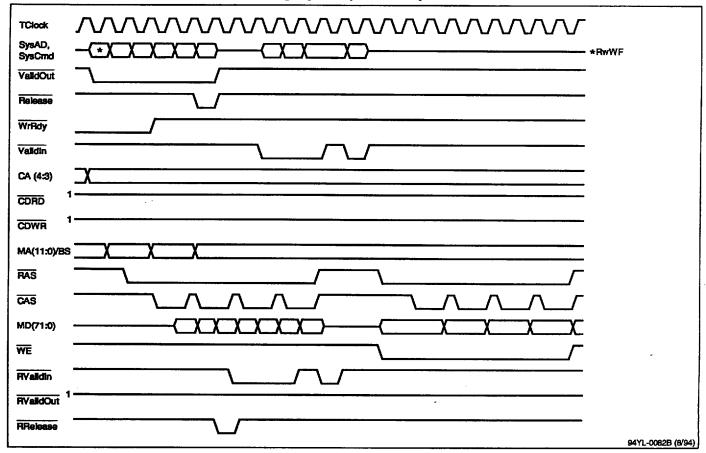

Block Write. The CPU or RAB2IT-IOC initiates the block write cycle by asserting MA(11:0) and BS for the period of time equal to RAS-high width and asserting CS. The RAS activates the bank select and the CAS, along with "write" command, performs the write operation with sub-block ordering. Instead of the last "write," "write and autoprecharge" is asserted to terminate the cycle and perform the precharge. See figure 12.

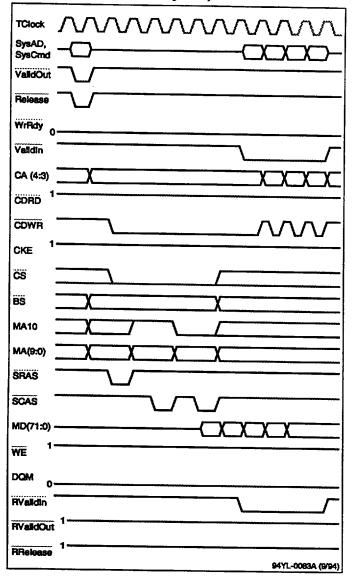

Partial Write. The CPU or RAB2IT-IOC initiates the partial write cycle by asserting MA(11:0) and BS for the period of time equal to RAS-high width and asserting CS. The RAS activates the bank select and the CAS, along with "read" command, reads the data, which is used to merge the data from the CPU. The merged data is written to memory with "write and autoprecharge" command two clocks later after "read." The data and "write and autoprecharge" command are asserted immediately without the first read if in doubleword write cycle. The "data mask" command is asserted in the next clock. See figure 13.

# NEC

Figure 12. Block Write

Figure 13. Partial Write

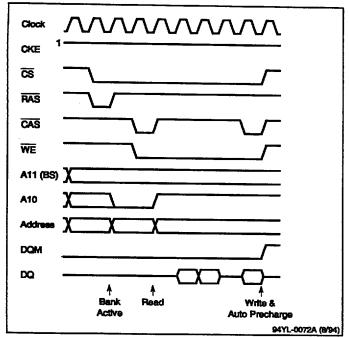

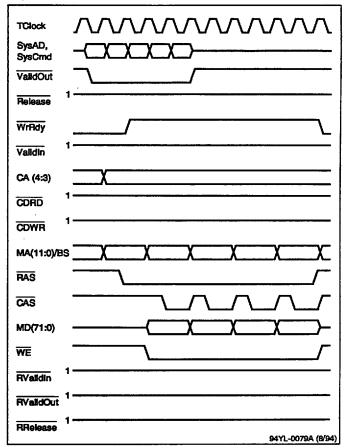

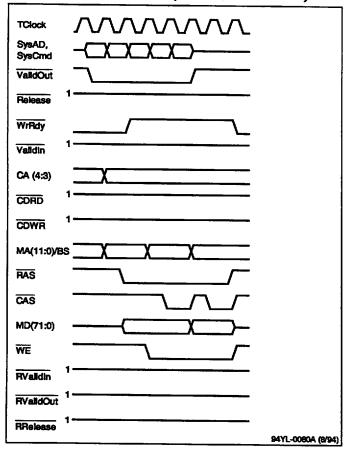

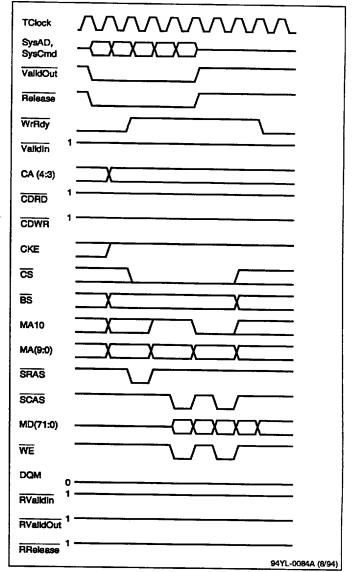

Block Read. The CPU or RAB2IT-IOC initiates the block write cycle by asserting MA(11:0) and BS for the period of time equal to RAS-high width and asserting CS. The RAS activates the bank select and the CAS, along with "read" command, performs the read operation with sub-block ordering. Instead of the last "write." "write and autoprecharge" is asserted to terminate the cycle and perform the precharge. See figure 14.

Figure 14. Block Read

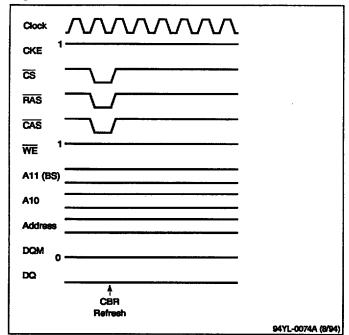

CBR Refresh. All "chip select" commands are activated after a period of time equal to the RAS-high width, which is set in the refresh timer. Then, the "CBR refresh" command is asserted to perform the refresh operation. See figure 15.

Figure 15. CBR Refresh

Figure 16. Self-Refresh

Figure 17. System Diagram With Buffer

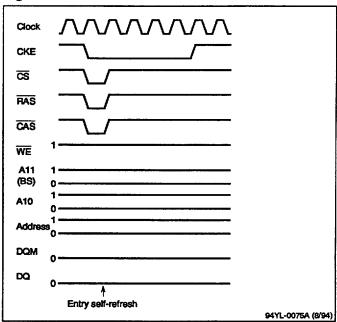

Self-Refresh. Self-refresh is required by a refresh request signal from the refresh timer in standby mode. All "chip select" commands are activated after a period of time equal to the RAS-high width, which is set in the refresh timer. Then, the "entry self-refresh" command is asserted to perform the refresh operation. Once the CPU or RAB2IT-IOC accesses the memory in the self-refresh state, the "self-refresh end" command is asserted to exit the self-refresh cycle. If the DRAM sleep control register is not written, the self-refresh is acti-

vated again on any refresh request signal sent by the refresh timer. See figure 16.

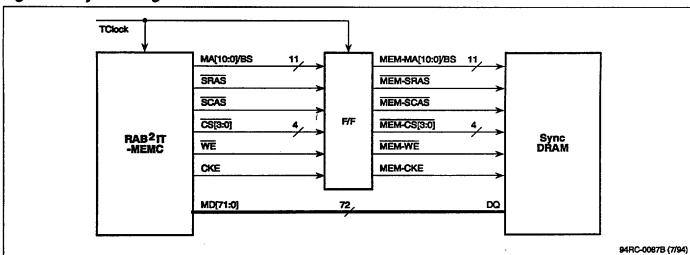

**Buffer.** The buffer mode can be configured as the system memory bus loading is overloaded. Access is made at one clock-pulse interval and the duration of the output is prolonged by two clock signals with the CKE signal. See figure 17.

Table 9. Multiplexer

|     |        |               |    |    |    |    |    |    | MA |    |    |    |     |    |         |

|-----|--------|---------------|----|----|----|----|----|----|----|----|----|----|-----|----|---------|

|     |        |               | 0  | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10  | 11 | -<br>BS |

|     | Ē      | AS            | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 22  | 24 | 11      |

| CAS | Single | 1M DRAM       | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 22 | 11 |     |    | 11      |

|     | Mode   | 4M DRAM       | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 23 | 11 | 24  |    | 11      |

|     |        | 16M DRAM      | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 23 | 11 | 25  | 26 | 11      |

|     |        | 16M Sync DRAM | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 23 |    | CMD | 24 | 11      |

|     |        | 64M Sync DRAM | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 23 | 25 | CMD | 24 | 11      |

|     | MS     | 1M DRAM       | 23 | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 22 | 11 |     |    | 11      |

|     |        | 4M DRAM       | 23 | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 22 | 11 | 24  |    | 11      |

|     |        | 16M DRAM      | 23 | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 22 | 11 | 25  | 26 | 11      |

#### Multiplexer

The RAB2IT-MEMC has a built-in multiplexer for the DRAM or Sync DRAM interface. Table 9 shows correspondence of the processor addresses and DRAM addresses. RAS addresses are common on all modes.

#### Parallel Mode

Two -MEMC controllers can be operated in parallel to increase the memory interface performance and expand memory size. For this feature, internal register address change function and master/slave mode function are provided.

Internal Register Address Change. This function is turned on for each device by the RAO input on reset. And the addresses of the registers are determined by the value of the RAO on the memory address bus of RAB2IT-MEMC during reset.

| <u>RAO</u> | Register Address Allocation    |

|------------|--------------------------------|

| 0          | 1 1400 03xx ~ 0 1400 03xx      |

| 1          | 1 1400 02xx $\sim$ 0 1400 02xx |

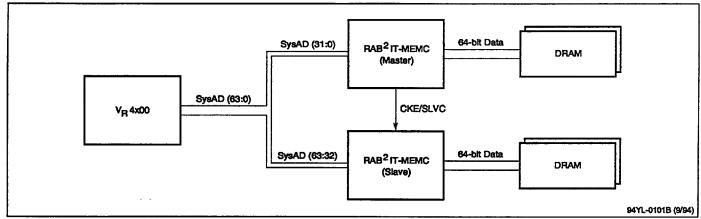

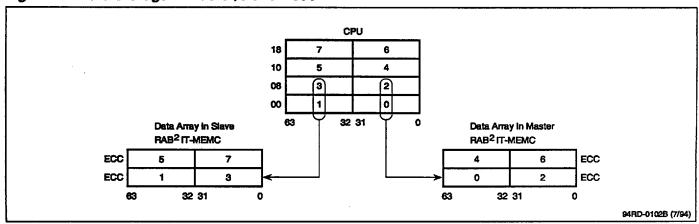

Master/Slave Operation. In this mode (figures 18 and 19), data transfer is performed at high bus bandwidth with 128-bit memory system bus configuration. One -MEMC performs as master with 64-bit DRAM data throughput; the other performs as slave with 64-bit DRAM data throughput. On the SysAD bus, master -MEMC only uses the SysAD[31:0] for data transfer and slave -MEMC uses SysAD[63:32] for data transfer. With this configuration, block cycles can be done by accessing memory once, 1.5 CPU bus cycle time, for one or two doublewords of data to satisfy the VR4x00 family processor. At the CPU point of view, it is identical to a single external agent configuration.

The CKE/SLV, which is controlled by the master -MEMC, is used to synchronize the master and slave -MEMCs during memory cycles.

**Parallel Operation.** Two -MEMCs are able to operate independently in parallel mode to meet the large memory size requirement with different address allocations.

#### **Error Detection and Correction**

The RAB2IT-MEMC has the function of detecting and correcting errors in memory access cycles with the parity and ECC (SECDED) code. Parity is used to read from and write to CPU/RAB2IT-IOC and ECC code is used for the data transfer between memory. In write cycles, -MEMC adds the ECC codes to the data sent by -IOC after parity check and writes them to memory. In read cycles, -MEMC sends data to -IOC after ECC checking. See table 10.

Data in the DRAM should be initialized at power on if the ECC function is active. Normal ECC codes are written to the memory area by using block write function, or by using partial write function to all memories with the MSKERR bit set to 1 in the device control register.

Table 10. Error Detection With MSKERR and MSKERR1 Status

| Error    | * MSKERR, MSKERR1      |           |              |              |  |  |  |  |

|----------|------------------------|-----------|--------------|--------------|--|--|--|--|

|          | 0,0                    | 0,1       | 1,0          | 1,1          |  |  |  |  |

| Parity   | Detected               | Detected  | Not detected | Not detected |  |  |  |  |

| 1-Bit    | Detected/<br>corrected | Corrected | Corrected    | Corrected    |  |  |  |  |

| Multibit | Detected               | Detected  | Not detected | Not detected |  |  |  |  |

<sup>\*</sup> Detected means detectable and will enable interrupt.

Figure 18. Data Bus Scheme in Master/Slave Mode

Figure 19. Data Storage in Master/Slave Mode

**Parity Error.** A parity error on the SysAD bus is detectable and correctable. Condition A or B below applies.

|            | A          | <u>B</u> |

|------------|------------|----------|

| PEO bit    | 0          | 1        |

| or MSKERR  | 1          | 0        |

| ERRADR bit | Indefinite | *Address |

| PERR bit   | 0          | 1        |

| PERR pin   | High       | Low      |

<sup>\*</sup>Error address is held until the bit is reset.

A parity error on the SysAD bus will cause the interrupt when (1) MSKERR = 0 and parity errors are detected in write cycles on the SysAD bus master device. Or (2) the address where the error occurs is set in the error address register and the PERR pin = low. Data is written to the memory but the values in the Error address register and the Error syndrome register and the status of the PERR pin are held until flushed by the Error flush register.

A parity error on the SysAD bus will not cause the interrupt when MSKERR = 1; the parity error check function is not active. The data will be written into the memory regardless of the parity error.

One-Bit Error. A one-bit error in memory is detectable (applicable to memory read) and correctable. RAB2IT-MEMC detects errors by using the ECC function in partial write to memory to perform read-modify-write. The detection occurs on A, B, or C below.

| A          | B          | C        |

|------------|------------|----------|

| 0          | 1          | 1        |

| 1          | 0          | 0        |

| _          | 1          | 1        |

| Indefinite | Indefinite | *Address |

| 0          | 1          | 1        |

| High       | Low        | Low      |

| _          | 0          | 0        |

|            | 0          | 0 1      |

<sup>\*</sup>Error address is held until the bit is reset.

**■** 6427525 0103198 242 **■**

A one-bit error in memory will cause the interrupt when (1) MSKERR = 0, MSKERR1 = 1, and one-bit errors are detected and corrected in read cycles or partial read cycles on the SysAD bus master device. Or (2) the data in memory is read, the address where the error occurs is set in the error address register, and the error syndrome is set in the error syndrome register.

Along with the PERR pin = low, SysCMD5 will inform the CPU that the data error occurs; then the data will be sent back as read response after being corrected. The values in the error address register and the error syndrome register and the status of the PERR pin are held until flushed by the error flush register.

A parity error on the SysAD bus will not cause the interrupt when MSKERR = 1, MSKERR1 = 1, and one-bit errors are detected in read cycles or partial write cycles on the SysAD bus master device. The results detected during error correction are not reported to the processor. In read cycles, data that has been corrected will not be written back to memory. In partial write cycles, data with errors will not be in the memory since the corrected data is merged to the original data and written back to memory.

Multibit Error. Two-bit errors and 3/4-bit nibble errors can be detected and corrected (applicable to memory read). RAB2IT-MEMC detects errors by using the ECC function in partial write to memory to perform read-modify-write. The detection occurs on condition A or B below.

|               | A          | B          |

|---------------|------------|------------|

| PEO bit       | 0          | 1          |

| or MSKERR     | 1          | 0          |

| MSKERR1       | _          | 1          |

| ERRADR bit    | Indefinite | Indefinite |

| PERR bit      | 0          | 1          |

| PERR pin      | High       | Low        |

| Read response | _          | 0          |

| SysCmd5       |            |            |

A multibit error in memory will cause the interrupt when (1) MSKERR = 0, MSKERR = 1, and multibit errors are detected and corrected in read cycles or partial read cycles on the SysAD bus master device. Or (2) the data in memory is read, the address where the error occurred is set in the error address register, and the error syndrome is set in the error syndrome register.

Along with the PERR pin = Low, SysCMD5 will inform the CPU that the data error occurred; then the data will be sent back as read response without being corrected.

The values in the error address register and the error syndrome register and the status of the PERR pin are held until flushed by the error flush register.

In partial write cycles, the merged data with the new ECC codes that are generated based on the data for which error correction has failed are written into memory. Therefore, the errors in memory are not corrected and will not be detected again on memory access cycles because of the new ECC codes. (The interrupt will occur in the first access.)

A parity error on the SysAD bus will not cause the interrupt when (1) MSKERR bit = 1, multibit errors are not detected. Or (2) multibit errors occur, but the data that has not been corrected is returned as response data.

**Illegal Access.** RAB2IT-MEMC inhibits the following bus cycles.

- Block access to the register area and cache tag area.

- Access to the memory location whose address is in the address base register and address master register, but the memory size is not in the device control register.

A special process is performed on any illegal access. The illegal access can be detected on condition A or B below.

|               | A          | <u>B</u>   |

|---------------|------------|------------|

| MSKERR        | 0          | 1          |

| ERRADR bit    | Indefinite | Indefinite |

| ILLACC bit    | 0          | 0          |

| PERR pin      | Low        | Low        |

| Read response | 0          | 1          |

| SysCmd5       |            |            |

In write cycles, access to these areas is ignored. In read, the indefinite values are returned. The ILLACC bit in the error syndrome register will be set to 1 on accessing these areas. The bus error will be reported to the CPU by SysCMD if MSKERR bit = 0; otherwise, the SysCMD will not inform the CPU of the bus error if MSKERR bit = 1.

An interrupt request is generated by the  $\overline{\text{PERR}}$  pin regardless of the status of the MSKERR bit.

**Reset Error Bits.** All four bits below are reset simultaneously by RESET = 0. When error bits are cleared, the ERRADDR bit is cleared.

| ERFRR bit | Bit Reset  |

|-----------|------------|

| 0 = 1     | ERRI = 0   |

| 1 = 1     | ERR = 0    |

| 2 = 1     | PERR = 0   |

| 3 = 1     | ILLACC = 0 |

ECC in Master/Slave Mode. ECC detection is also performed on the 128-bit basis in master/slave mode. That is, as error exists in a four-word area, which masked bit 3 in the error address register. Master RAB2IT-MEMC asserts SysCMD5 in memory access cycles, and the PERR pin is used for error notification by slave RAB2IT-MEMC. The error address register, error syndrome register, and error flush register are in both the master and slave RAB2IT-MEMC.

#### SECONDARY CACHE CONTROLLER

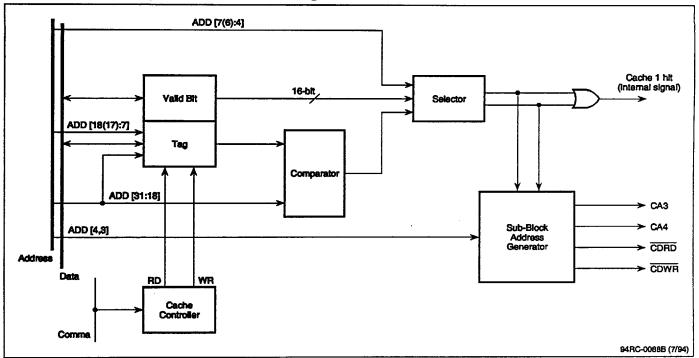

The RAB2IT-MEMC incorporates the secondary cache interface controller to support VR4x00PC and VR4200 processors, which do not have the integration of the secondary cache interface. The local secondary cache can be configured as 256K- or 512K-byte size. The internal Tag and Comparator determines the hit/miss cycles; data flows are handled through the interface signals: CA3, CA4, CDRD, and CDWR. See figure 20.

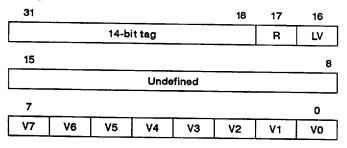

# Cache Tag

The internal cache tag memory has 2048 entries. Each entry consists of a 14-bit tag part, 16-bit valid bit part, and one-line valid bit. For a 256K-byte configuration, a 32-word cache line size and a 4-word sub-block are used. For the 512K-byte configuration, a 64-word cache line size and a 4-word sub-block are used. On system reset, all the line invalid bits are reset. Validity of each sub-block is checked by ANDing valid bits of each sub-block.

The cache tag can be read and written by accessing the address 0x1 1800 0000 through 0x1 IBFF FFFF. The values for read and write are shown below. Writing to the undefined location is ignored.

| 31 |            |    |    |    | 18 | 17 | 16 |

|----|------------|----|----|----|----|----|----|

|    | 14-bit tag |    |    |    |    |    | LV |

| 15 |            |    |    |    |    |    | 8  |

| Vf | Ve         | Vd | Vc | Vb | Va | V9 | V8 |

| 7  |            |    |    |    |    |    | 0  |

| V7 | V6         | V5 | V4 | VЗ | V2 | V1 | Vo |

Figure 20. 512K (256K) Mode Cache Block Diagram

In 256K mode, 2K entries are selected by address bits 17-7. The address written into the cache tag is A[31:18]; A[6:4] select the valid bits.

In the 512K mode, 2K entries are selected by address bits 18-8. The address written into the cache tag is A[31:19]; A[7:4] select the valid bits.

| 31 |            |    |    | 19 | 18 | 17 | 16 |

|----|------------|----|----|----|----|----|----|

|    | 13-bit tag |    |    |    |    | R  | LV |

| 15 |            |    |    |    |    |    | 8  |

| Vf | Ve         | Vd | Vc | Vb | Va | V9 | V8 |

| 7  |            |    |    |    |    |    | 0  |

| V7 | V6         | V5 | V4 | V3 | V2 | V1 | Vo |

Comparator. The cache address comparator is 14 bits wide.

Selector. The selector selects 2 bits correspondent to an 8-word block transfer from among the 16 valid bits.

#### Cache Control Operation

On cache read miss, the tag values are updated and appropriate valid bits are set; then the rest of the valid bits are reset. Cache line fill cycle is asserted with sub-block ordering after the line valid bit is set.

On cache read hit if valid bit = 0 (invalid), appropriate valid bits are set, but the rest of the valid bits are not reset. Cache line fill cycle is asserted with sub-block ordering.

On cache write hit, correspondent valid bits are reset. There is no operation on cache write miss.

For block read cycles generated by the processor, data will be provided to the processor in doubleword, word, and partial word format on cache hit.

#### **Cache Coherency**

- Processor Write. Tag memory is checked and valid bits of the hit tag are set invalid. Data in the secondary cache will not be updated.

- Processor Read. If a tag memory is checked and hit, the values in the tag are not changed and data in the secondary cache is sent to the processor without being modified.

In block read miss, the tag addresses are updated and appropriate valid bits are set. Data in the secondary cache will be replaced with data from the DRAM (cache line fill).

#### Cache Interface

Figure 21 shows the system configuration with 512K (256K) secondary cache memory interface. RAB2IT-MEMC generates the low-order address bits, A3 and A4, according to the sub-block ordering.

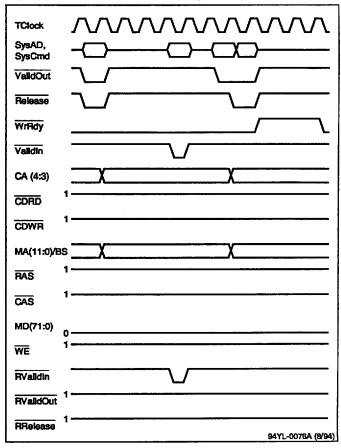

# RAB2IT-IOC PROTOCOL HANDLER

Signals RValidin, RVAlidOut, and RRelease are the interface signals between -IOC and -MEMC. This protocol is used when the processor releases the bus mastership, such as DMA transfer function. The details of the DMA operation are in the RAB2IT-IOC data sheet.

Figure 21. RAB2IT-MEMC and 512K(256) SRAM Interface

| 6427525 0103201 667 🖿

#### **RAB2IT-MEMC CONTROL REGISTERS**

Table 11 shows the internal registers of the RAB2IT-MEMC. The addresses of these internal registers are determined by the status of RAO.

Table 11. Internal Register Map

|                                        | Read/ | Address     | (on reset)  |                                 |

|----------------------------------------|-------|-------------|-------------|---------------------------------|

| Register Name                          | Write | RAO = 0     | RAO =1      | Default                         |

| Device control register                | R/W   | 1 1400 0200 | 1 1400 0300 | 0002 0000                       |

| Address base register                  | R/W   | 1 1400 0208 | 1 1400 0308 | 0000 0000                       |

| Address mask register                  | R/W   | 1 1400 0210 | 1 1400 0310 | 0000 0000                       |

| Sync DRAM mode register                | R/W   | 1 1400 0218 | 1 1400 0318 | 000 0001                        |

| DRAM speed register                    | R/W   | 1 1400 0220 | 1 1400 0320 | 0000 0000                       |

| Refresh counter                        | R/W   | 1 1400 0228 | 1 1400 0328 | 000F 0000<br>Refresh<br>Disable |

| DRAM sleep<br>control register         | RW    | 1 1400 0230 | 1 1400 0330 | 0000 0000                       |

| Secondary<br>cache control<br>register | R/W   | 1 1400 0238 | 1 1400 0338 | 000 0000                        |

| Secondary<br>cache flush<br>register   | W     | 1 1400 0240 | 1 1400 0340 | Invalid                         |

| Error address<br>register              | R     | 1 1400 0248 | 1 1400 0348 | Invalid                         |

| Error syndrome register                | R     | 1 1400 0250 | 1 1400 0350 | Invalid                         |

| Error flush<br>register                | W     | 1 1400 0258 | 1 1400 0358 | Invalid                         |

| Address limit register                 | RW    | 1 1400 0260 | 1 1400 0360 |                                 |

|                                        | R     | 1 1400 0264 | 1 1400 0364 |                                 |

#### **Device Control Register**

The device control register (table 13) contains the basic setting information of the RAB2IT-MEMC. The setting information includes Slave mode, re-mapping of the I/O area, endian, ECC/Parity operation, DRAM type, and bank configuration; the register is initialized on the system initialization sequence.

Table 12. Device Control Register

| 31 |      |          | 26  | 25  | 24  | 23  | 22   | 21  |

|----|------|----------|-----|-----|-----|-----|------|-----|

|    | -    | <b>-</b> |     | MER | 2BK | N   | 18   | DP  |

| 20 | 19 - | 18       | 17  | 16  | 15  | 14  | 13   | 12  |

| RI | BED  | EPO      | MEI | SDR | взЕ | B2E | B1 E | BOE |

| 11 | \$   | 8        |     | 6 5 |     | 3 : | 2    | 0   |

|    | B3S  |          | B2S |     | B1S |     | Bos  | 3   |

| Field | Name       | Description                                                                 |

|-------|------------|-----------------------------------------------------------------------------|

| 25    | MSKERR     | ECC error/parity detecting mask.  1: Default setting on DRAM initialization |

| 24    | 2 Bank     |                                                                             |

| 23-22 | M_Slave    | 00: Single mode; 10: Master mode; 01:<br>Undefined; 11: Slave mode          |

| 21    | D_Pat      | Read response data pattern. 0: D; 1: Dx                                     |

| 20    | Remap_IO   | 0: Remap 0x1 1000 0000 ~ 0x1 1FFF FFF<br>to 0x0 1000 0000 ~ 0x0 1FFF FFFF   |

| 19    | Big_Endian | 0: Little endian (default); 1: Big endian                                   |

| 18    | EPO        | 0: Parity; 1: ECC                                                           |

| 17    | MSKERR1    | 0: Interrupt on 1-bit error occurs during ECC mode (default)                |

| 16    | SyncDRAM   | 0: Standard DRAM; 1: Synchronous DRAM                                       |

| 15    | Bank3_En   | 1: Memory is installed in Bank 3                                            |

| 14    | Bank2_En   | 1: Memory is installed in Bank 2                                            |

| 13    | Bank1_En   | 1: Memory is installed in Bank 1                                            |

| 12    | Bank0_En   | 1: Memory is installed in Bank 0                                            |

| 11-9  | Bank3_Size | Memory size on each bank                                                    |

| 8-6   | Bank2_Size | 000: 8M-byte; 011: 64M-byte;<br>001: 16M-byte; 100: 128M-byte;              |

| 5-3   | Bank1_Size | 010: 32M-byte; 101: 256M-byte.                                              |

| 2-0   | Bank0_Size |                                                                             |

#### **Address Base Register**

The Address Base register (table 13) indicates the address of the memory area controlled by the RAB2IT-MEMC.

# NEC

# Table 13. Address Base Register

| 31       | 23 | 22 | 0 |

|----------|----|----|---|

| Mem_Base |    |    |   |

| Field | Name     | Description                                               |

|-------|----------|-----------------------------------------------------------|

| 31-23 | Mem_Base | The base address of the installed area for 8M-byte block. |

# **Address Mask Register**

The Address Mask register (table 14) is used to mask the address decoder and specify the range of memory area to be controlled by the RAB2IT-MEMC. A 1 is set in a bit correspondent to the address for masking. For this register, a 1 must be set beginning with bit 23. Thus, the following nine values can be set:

| 0 0000 0001 | 0 0001 1111 | 1 1111 1111 |

|-------------|-------------|-------------|

| 0 0000 0011 | 0 0011 1111 |             |

| 0 0000 0111 | 0 0111 1111 |             |

| 0 0000 1111 | 0 1111 1111 |             |

#### Table 14. Address Mask Register

| 31       | 23 | 22 |   | 0 |

|----------|----|----|---|---|

| Mem_Mask |    |    | _ |   |

| Field | Name     | Description                                                                                                                |

|-------|----------|----------------------------------------------------------------------------------------------------------------------------|

| 31-23 | Mem_Mask | Designates a bit used to mask address decoding of a memory area;. 0's are in the least significant 23 bits in the address. |

#### Synchronous DRAM Mode Register

The Synchronous DRAM Mode register (table 15) indicates the synchronous DRAM mode. The least significant 13 bits are invalid and the most significant 15 bits are ignored in write. The values are latched inside the RAB2IT-MEMC and written into the mode register of synchronous DRAM. The values are read into the least significant 13 bits and 0 is written to the most significant 51 bits in read. Burst length should be set to 2. CAS latency should be 2 or 3. Do not set any other values.

Table 15. Synchronous DRAM Mode Register

| 63 | 17 | 16     | 13 | 12 |          | 0 |

|----|----|--------|----|----|----------|---|

| _  |    | Buffer | _  |    | Sync Set |   |

| Field | Name     |              | Description                                              |

|-------|----------|--------------|----------------------------------------------------------|

| 16    | Buffer   |              | Set for using buffer. Timing changed by one clock pulse. |

| 12-7  | Sync Set |              |                                                          |

| † 6-4 |          | Latency      | 001: 1; 010: 2; 011: 3                                   |

| 3     |          | Wrap type    | 0: Interleave (sub block);<br>1: Sequential              |

| *2-0  |          | Burst length | 000: 1; 001: 2; 010: 4;<br>011: 8; 111: Full page        |

<sup>\*</sup> Bits 2 through 0 are fixed at 001 for RAB2IT-MEMC.

# **DRAM Speed Register**

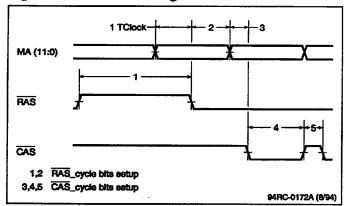

The DRAM Speed register (table 16) specifies the access timing for DRAM. The least significant 7 bits are valid and the most significant 57 bits are ignored in write. The values are read into the least significant 7 bits, and 0 is written to the most significant 57 bits in read. See figure 22.

# Table 16. DRAM Speed Register

| 63 | 7 | 6   | 5   | 4   | 3 | 2   | 1  | 0 |

|----|---|-----|-----|-----|---|-----|----|---|

| _  |   | CAS | RFU | RIC |   | RFU | CI | С |

| Field    | Name      | Description |                                              |            |  |  |  |

|----------|-----------|-------------|----------------------------------------------|------------|--|--|--|

| 6        | CA_Sup    |             | oulse is added as the<br>st column address t |            |  |  |  |

| 5<br>4-3 | RFU       | Reserved    |                                              |            |  |  |  |

|          | RAS_Cycle |             | † RAS to Addr                                | RAS min    |  |  |  |

|          |           | 00          | 1 TClock                                     | 3 TClock   |  |  |  |

|          |           | 01          | 2 TClock                                     | 4 TClock   |  |  |  |

|          |           | 10          | 3 TClock                                     | 5 TClock   |  |  |  |

|          |           | 11          | 4 TClock                                     | 6 TClock   |  |  |  |

| 1-0      | CAS_Cycle |             | CAS low                                      | CAS high   |  |  |  |

|          |           | 00          | 1.5 TClock                                   | 0.5 TClock |  |  |  |

|          |           | 01          | 2.0 TClock                                   | 1.0 TClock |  |  |  |

|          |           | 10          | 2.5 TClock                                   | 1.5 TClock |  |  |  |

|          |           | 11          | 3.0 TClock                                   | 2.0 TClock |  |  |  |

<sup>†</sup> Time from RAS to column address.

<sup>†</sup> Set 010 or 011 in bits 6 through 4.

Figure 22. DRAM Timing

Figure 23. Refresh Counter Block Diagram

### **Refresh Timing**

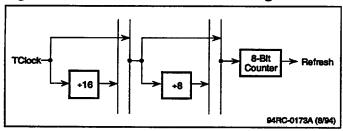

The 8-bit counter is used to count the refresh timing for DRAM or Sync DRAM. A 4-bit prescaler scales the divide-by-16 of TClock and an additional 3-bit prescaler (divide-by-8) provides the slow refresh function by setting bit 8. The prescalers can be bypassed with bit 9 set for testing purpose. See figure 23.

The refresh timing should be written into the refresh counter (bits 23-16) with the counting value equal to the desired number of clocks minus one. In bypass mode, the counting value written to the counter should be equal to the desired number of clocks minus two to ensure the read values are available one clock before the read response cycle.

The least significant 11 bits are valid and the most significant 53 bits are ignored in write cycle. In read cycle, the written value is read from the least significant 11 bits and the current count is read from the field. See table 17.

Table 17. Refresh Counter

| 63 |    |    |     | 24  | 23 |                 | 16 |

|----|----|----|-----|-----|----|-----------------|----|

|    |    | _  |     |     |    | Refresh counter |    |

| 15 | 11 | 10 | 9   | 8   | 7  |                 | 0  |

|    |    | RE | CAS | SLO |    | Refresh timer   |    |

| Field | Name      | Description                     |

|-------|-----------|---------------------------------|

| 23-16 | Ref_Count | Refresh counter (Read only)     |

| 10    | Ref_En    | 1: Refresh enable               |

| 9     | B_P       | Bypass prescaler                |