|                                                                      |         |                                                                                                                                                                                                                   |     |                                |                 |                        |                                   |                                     | REVIS            | IONS               |             |                     |                       |                       |         |         |         |       |      |                                                     |  |  |  |  |  |

|----------------------------------------------------------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------------------|-----------------|------------------------|-----------------------------------|-------------------------------------|------------------|--------------------|-------------|---------------------|-----------------------|-----------------------|---------|---------|---------|-------|------|-----------------------------------------------------|--|--|--|--|--|

| LTR                                                                  |         |                                                                                                                                                                                                                   |     |                                | [               | DESCF                  | RIPTIO                            | N                                   |                  |                    |             |                     | С                     | ATE (                 | /R-MO-D | A)      |         | APPR  | OVED |                                                     |  |  |  |  |  |

| А                                                                    |         | device<br>irement                                                                                                                                                                                                 |     |                                |                 |                        |                                   | rplate t                            | to inclu         | de rad             | hard        |                     | 96-03-13 Monica L. Po |                       |         | . Poelk | ing     |       |      |                                                     |  |  |  |  |  |

| В                                                                    |         | device                                                                                                                                                                                                            |     | 07, 08,                        | and 09          | . Upda                 | ate boile                         | erplate.                            | Edito            | rial cha           | nges        |                     | 98-08-27 Monica I     |                       |         | onica L | . Poelk | ing   |      |                                                     |  |  |  |  |  |

| С                                                                    | reset   | In table I, change $I_{IN}$ limits; add footnote to $I_{DDQ}$ ; add $t_c$ in reset timing section; add footnote to $V_{OS}$ and $V_{DIS}$ . Correwaveforms. Change footnote $\underline{3}$ / in table III. – tvn |     |                                |                 |                        | t <sub>c</sub> in po<br>correct t | ower-up                             | maste<br>G timir | er<br>ng           |             | 99-0                | 14-28                 |                       | Mo      | onica L | . Poelk | ing   |      |                                                     |  |  |  |  |  |

|                                                                      |         |                                                                                                                                                                                                                   |     |                                |                 |                        |                                   |                                     |                  |                    |             |                     |                       |                       |         |         |         |       |      |                                                     |  |  |  |  |  |

| REV                                                                  | Тв      | В                                                                                                                                                                                                                 | В   | С                              |                 |                        |                                   |                                     |                  | T                  |             |                     |                       |                       |         | 1       |         |       | 1    | Ī                                                   |  |  |  |  |  |

| SHEET                                                                | 35      | 36                                                                                                                                                                                                                | 37  | 38                             |                 |                        |                                   |                                     |                  |                    |             |                     |                       |                       |         |         |         |       |      |                                                     |  |  |  |  |  |

| REV                                                                  | С       | В                                                                                                                                                                                                                 | В   | В                              | В               | В                      | В                                 | В                                   | В                | В                  | В           | В                   | В                     | С                     | В       | С       | В       | В     | В    | В                                                   |  |  |  |  |  |

| SHEET                                                                | 15      | 16                                                                                                                                                                                                                | 17  | 18                             | 19              | 20                     | 21                                | 22                                  | 23               | 24                 | 25          | 26                  | 27                    | 28                    | 29      | 30      | 31      | 32    | 33   | 34                                                  |  |  |  |  |  |

| REV STATUS                                                           | ·       |                                                                                                                                                                                                                   | •   | REV                            | ,<br>,          |                        | С                                 | В                                   | В                | В                  | В           | В                   | С                     | С                     | С       | С       | С       | С     | С    | С                                                   |  |  |  |  |  |

| OF SHEETS                                                            |         |                                                                                                                                                                                                                   |     | SHE                            | ET              |                        | 1                                 | 2                                   | 3                | 4                  | 5           | 6                   | 7                     | 8                     | 9       | 10      | 11      | 12    | 13   | 14                                                  |  |  |  |  |  |

| PMIC N/A                                                             |         |                                                                                                                                                                                                                   |     |                                | PAREI<br>omas N |                        | S                                 |                                     |                  |                    | D           | EFEN                | SE S                  | UPPL                  | Y CEI   | NTER    | COL     | UMBI  | US   |                                                     |  |  |  |  |  |

|                                                                      | NDAI    |                                                                                                                                                                                                                   |     |                                | CKED<br>omas N  |                        | S                                 |                                     |                  |                    |             |                     |                       |                       |         |         |         |       |      | DEFENSE SUPPLY CENTER COLUMBUS COLUMBUS, OHIO 43216 |  |  |  |  |  |

| THIS DRAWI                                                           | NG IS A | MICROCIRCUIT  THIS DRAWING IS AVAILABLE                                                                                                                                                                           |     | APPROVED BY Monica L. Poelking |                 |                        |                                   | MICROCIRCUIT, DIGITAL, CMOS, SERIAL |                  |                    |             |                     |                       |                       |         |         |         |       |      |                                                     |  |  |  |  |  |

| FOR USE BY ALL DEPARTMENTS AND AGENCIES OF THE DEPARTMENT OF DEFENSE |         |                                                                                                                                                                                                                   | BLE |                                | nica L.         | Poelki                 | ing                               |                                     |                  |                    |             |                     |                       |                       |         |         |         |       |      |                                                     |  |  |  |  |  |

|                                                                      |         | ALL<br>ITS<br>OF THE                                                                                                                                                                                              | ≣   | Mo                             |                 | APPR                   | ing<br>OVAL [<br>03-31            | DATE                                |                  | MIC                | ROC         | ODEC<br>NSCI        | MUL                   | TI-MO                 | DDE I   | NTEL    |         |       | RMIN | IAL                                                 |  |  |  |  |  |

| DEPARTME                                                             |         | ALL<br>ITS<br>OF THE<br>DEFEN                                                                                                                                                                                     | ≣   | DRA                            |                 | APPRO<br>95-0<br>LEVEL | OVAL [<br>03-31                   | DATE                                |                  | MIC<br>ANI<br>SIZE | ROCO<br>TRA | ODED<br>NSCI<br>CAG | MUL                   | TI-M(<br>R, SILI<br>E | DDE I   | NTEL    |         | NT TE |      | IAL                                                 |  |  |  |  |  |

5962-E267-99

DSCC FORM 2233

APR 97

DISTRIBUTION STATEMENT A. Approved for public release; distribution is unlimited.

### 1. SCOPE

- 1.1 <u>Scope</u>. This drawing documents two product assurance class levels consisting of high reliability (device classes Q and M) and space application (device class V). A choice of case outlines and lead finishes are available and are reflected in the Part or Identifying Number (PIN). When available, a choice of Radiation Hardness Assurance (RHA) levels are reflected in the PIN.

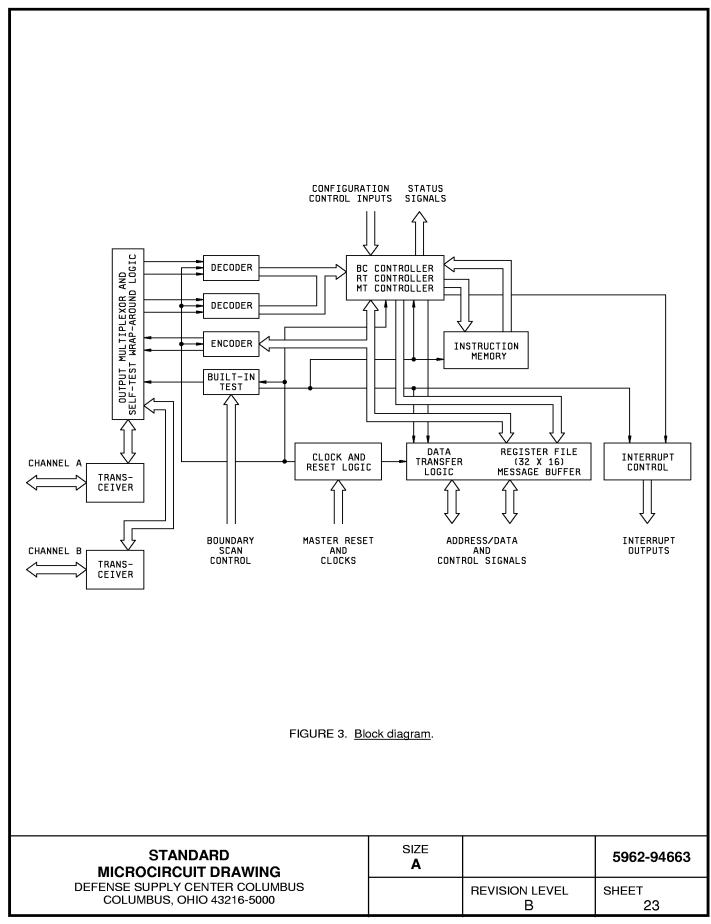

- 1.2 PIN. The PIN is as shown in the following example:

- 1.2.1 RHA designator. Device classes Q and V RHA marked devices meet the MIL-PRF-38535 specified RHA levels and are marked with the appropriate RHA designator. Device class M RHA marked devices meet the MIL-PRF-38535, appendix A specified RHA levels and are marked with the appropriate RHA designator. A dash (-) indicates a non-RHA device.

- 1.2.2 <u>Device type(s)</u>. The device type(s) identify the circuit function as follows:

| Device type | Generic number | Circuit function                                                                                         |

|-------------|----------------|----------------------------------------------------------------------------------------------------------|

| 01          | 69151-LX15     | Serial microcoded multi-mode intelligent terminal with 15-volt transceiver                               |

| 02          | 69151-DX       | Serial microcoded multi-mode intelligent terminal with 5-volt transceiver                                |

| 03          | 69151-LX12     | Serial microcoded multi-mode intelligent terminal with<br>12-volt transceiver                            |

| 04          | 69151-LXE15    | Enhanced serial microcoded multi-mode intelligent terminal with 15-volt transceiver radiation hardened   |

| 05          | 69151-DXE      | Enhanced serial microcoded multi-mode intelligent<br>terminal with 5-volt transceiver radiation hardened |

| 06          | 69151-LXE12    | Enhanced serial microcoded multi-mode intelligent terminal with 12-volt transceiver                      |

| 07          | 69151-LXE15    | Enhanced serial microcoded multi-mode intelligent terminal with 15-volt transceiver                      |

| 08          | 69151-DXE      | Enhanced serial microcoded multi-mode intelligent terminal with 5-volt transceiver                       |

| 09          | 69151-LXE12    | Enhanced serial microcoded multi-mode intelligent terminal with 12-volt transceiver                      |

1.2.3 <u>Device class designator</u>. The device class designator is a single letter identifying the product assurance level as follows:

| <u>Device class</u> | <u>Device requirements documentation</u>                                                                                                                  |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| М                   | Vendor self-certification to the requirements for MIL-STD-883 compliant, non-JAN class level B microcircuits in accordance with MIL-PRF-38535, appendix A |

| Q or V              | Certification and qualification to MIL-PRF-38535                                                                                                          |

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                     | 5962-94663 |

|-------------------------------------------------------------|------------------|---------------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL<br>B | SHEET 2    |

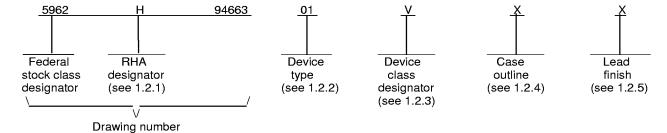

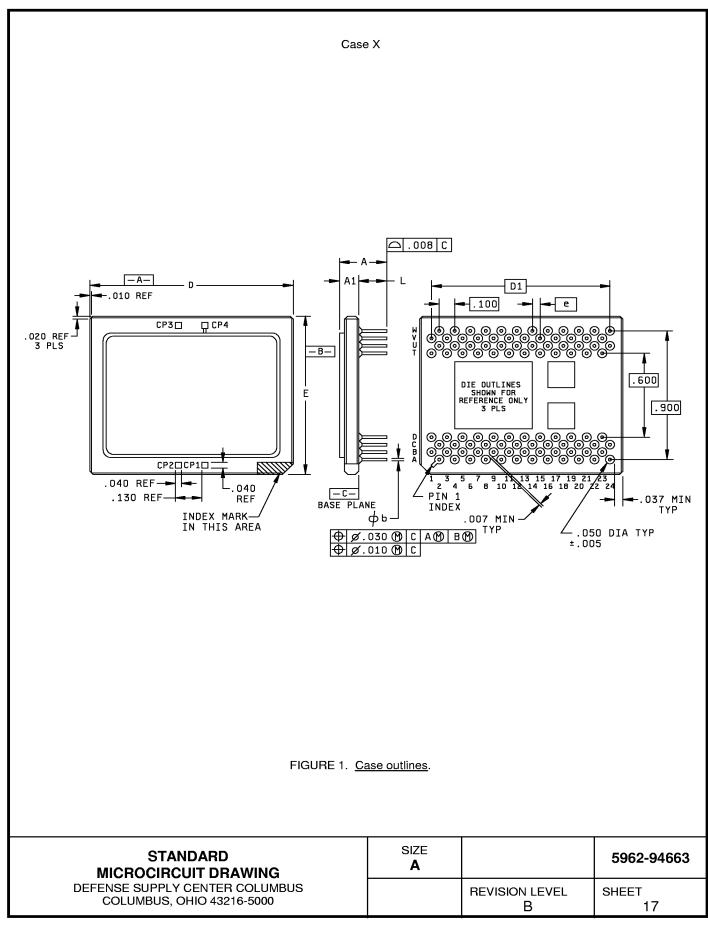

1.2.4 <u>Case outline(s)</u>. The case outline(s) are as designated in MIL-STD-1835 and as follows:

| Outline letter | Descriptive designator | <u>Terminals</u> | Package style             |

|----------------|------------------------|------------------|---------------------------|

| X              | See figure 1           | 100              | Pin grid array <u>1</u> / |

| Υ              | See figure 1           | 100              | Leaded chip carrier with  |

1.2.5 <u>Lead finish</u>. The lead finish is as specified in MIL-PRF-38535 for device classes Q and V or MIL-PRF-38535, appendix A for device class M.

1.3 Absolute maximum ratings. 2/

| Storage temperature range ( $T_{STG}$ )                                       |                        |

|-------------------------------------------------------------------------------|------------------------|

| Device types 01, 03, 04, 06, 07, 09                                           | -22 V dc               |

| Transceiver supply voltage range (V <sub>CC</sub> ):  Device types 02, 05, 08 | -0.3 V dc to +7.0 V dc |

| Logic supply voltage range (V <sub>DD</sub> )                                 |                        |

| Input voltage range (V <sub>DR</sub> ):                                       |                        |

| Device types 01, 03, 04, 06, 07, 09                                           |                        |

| Device types 02, 05, 08                                                       |                        |

| Maximum power dissipation (P <sub>D</sub> )                                   |                        |

| Logic voltage on any pin range (V <sub>I/O</sub> )                            |                        |

| Logic latch-up immunity (ILU)                                                 | 150 mA                 |

| Logic input current (I <sub>I</sub> )                                         | 10 mA                  |

| Output current (Io):                                                          |                        |

| Device types 01, 03, 04, 06, 07, 09                                           | 190 mA                 |

| Device types 02, 05, 08                                                       |                        |

| Maximum junction temperature (T <sub>J</sub> )                                | +150 C                 |

| Receiver common mode input voltage range (V <sub>IC</sub> ):                  |                        |

| Device types 01, 03, 04, 06, 07, 09                                           | -11 V dc to +11 V dc   |

| Device types 02, 05, 08                                                       | -5 V dc to +5 V dc     |

| Lead temperature (soldering, 5 seconds)                                       |                        |

| Thermal resistance junction-to-case ( Jc): 3/                                 |                        |

| Cases X and Y                                                                 | 7 C/W                  |

|                                                                               |                        |

3/ Per MIL-STD-883, Method 1012.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 5962-94663 |

|----------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43216-5000        |                  | B              | 3          |

<sup>1/</sup> This package contains 96 terminals on the bottom and 4 terminals on top of the package, see figure 1.

Stress outside the listed absolute maximum rating may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions beyond limits indicated in the operational sections of this specification is not recommended. Exposure to absolute maximum rating conditions for extended periods affect device reliability.

| 1.4 Recommended operating conditions.                                                     |                                         |

|-------------------------------------------------------------------------------------------|-----------------------------------------|

| Transceiver supply voltage range (V <sub>CC</sub> ):                                      |                                         |

| Device types 01, 03, 04, 06, 07, 09                                                       | 14.75 V do to 15.5 V do                 |

| Device type 02                                                                            |                                         |

| <b>21</b>                                                                                 |                                         |

| Device types 05, 08                                                                       |                                         |

| Logic supply voltage range (V <sub>DD</sub> )                                             | +4.5 V dc to +5.5 V dc                  |

| Transceiver supply voltage range (V <sub>EE</sub> ):                                      | 45 V -I-                                |

| Device types 01, 04, 07                                                                   |                                         |

| Device types 03, 06, 09                                                                   | -12 V dc                                |

| Receiver differential voltage (V <sub>DR</sub> ):                                         | 40.14                                   |

| Device types 01, 03, 04, 06, 07, 09                                                       |                                         |

| Device types 02, 05, 08                                                                   |                                         |

| Logic dc input voltage range (V <sub>IN</sub> )                                           | 0 V dc to V <sub>DD</sub>               |

| Receiver common mode input voltage (V <sub>IC</sub> ):                                    |                                         |

| Device types 01, 03, 04, 06, 07, 09                                                       | 10 V dc                                 |

| Device types 02, 05, 08                                                                   | 5.0 V dc                                |

| Driver peak output current (Io):                                                          |                                         |

| Device types 01, 03, 04, 06, 07, 09                                                       | 180 mA                                  |

| Device types 02, 05, 08                                                                   | 700 mA                                  |

| Serial data rate range (S <sub>D</sub> )                                                  | 0 to 1 MHz                              |

| Clock duty cycle (Dc)                                                                     | 50 5%                                   |

| Case operating temperature range (T <sub>C</sub> )                                        |                                         |

| Operating frequency (F <sub>IN</sub> )                                                    |                                         |

| Radiation features:                                                                       | Z+ WIT IZ 0.01 /8                       |

| Total dose                                                                                |                                         |

|                                                                                           | 100k Dada (Si)                          |

| Device type 04                                                                            | 100k Rads (Si)                          |

| Device type 05(OFR) of facility                                                           | 1M Rads (SI)                            |

| Single event phenomenon (SEP) effective                                                   | 47                                      |

| linear energy threshold, no upsets                                                        |                                         |

| Neutron fluence (TM 1017)                                                                 | <u>1</u> /                              |

| 1.5 Digital logic testing for device classes Q and V.                                     |                                         |

|                                                                                           |                                         |

| Fault coverage measurement of manufacturing                                               |                                         |

| logic tests (MIL-STD-883, test method 5012)                                               | 95.12 percent                           |

|                                                                                           |                                         |

| 2. APPLICABLE DOCUMENTS                                                                   |                                         |

| 2.1 Government specification, standards, and handbooks. The following specification       | on standards and handbooks form a       |

| part of this drawing to the extent specified herein. Unless otherwise specified, the issu |                                         |

| the issue of the Department of Defense Index of Specifications and Standards (DoDIS       |                                         |

| solicitation.                                                                             | b) and supplement thereto, cited in the |

| Solicitation.                                                                             |                                         |

| SPECIFICATION                                                                             |                                         |

|                                                                                           |                                         |

| DEPARTMENT OF DEFENSE                                                                     |                                         |

| MIL-PRF-38535 - Integrated Circuits, Manufacturing, General Specification for             | •                                       |

|                                                                                           |                                         |

|                                                                                           |                                         |

|                                                                                           |                                         |

|                                                                                           |                                         |

|                                                                                           |                                         |

|                                                                                           |                                         |

|                                                                                           |                                         |

|                                                                                           |                                         |

| 1/ Values will be added when they become available. Rad hard devices have not yet         | been tested for neutron or SEP.         |

|                                                                                           |                                         |

|                                                                                           |                                         |

| STANDARD MICROCIRCUIT DRAWING DEFENSE SUPPLY CENTER COLUMBUS COLUMBUS, OHIO 43216-5000 | SIZE<br><b>A</b> |                     | 5962-94663 |

|----------------------------------------------------------------------------------------|------------------|---------------------|------------|

|                                                                                        |                  | REVISION LEVEL<br>B | SHEET<br>4 |

### **STANDARDS**

### DEPARTMENT OF DEFENSE

MIL-STD-883 - Test Methods and Procedures for Microelectronics.

MIL-STD-973 - Configuration Management.

MIL-STD-1835 - Interface Standard For Microcircuit Case Outlines.

### **HANDBOOKS**

### DEPARTMENT OF DEFENSE

MIL-HDBK-103 - List of Standard Microcircuit Drawings (SMD's).

MIL-HDBK-780 - Standard Microcircuit Drawings.

(Unless otherwise indicated, copies of the specification, standards, and handbooks are available from the Standardization Document Order Desk, 700 Robbins Avenue, Building 4D, Philadelphia, PA 19111-5094.)

2.2 <u>Non-Government publications</u>. The following document(s) form a part of this document to the extent specified herein. Unless otherwise specified, the issues of the documents which are DOD adopted are those listed in the issue of the DODISS cited in the solicitation. Unless otherwise specified, the issues of documents not listed in the DODISS are the issues of the documents cited in the solicitation.

### INSTITUTE OF ELECTRICAL AND ELECTRONICS ENGINEERS (IEEE)

IEEE Standard 1149.1 - IEEE Standard Test Access Port and Boundary Scan Architecture.

(Applications for copies should be addressed to the Institute of Electrical and Electronics Engineers, 445 Hoes Lane, Piscataway, NJ 08854-4150.)

(Non-Government standards and other publications are normally available from the organizations that prepare or distribute the documents. These documents may also be available in or through libraries or other informational services.)

2.3 <u>Order of precedence</u>. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing takes precedence. Nothing in this document, however, supersedes applicable laws and regulations unless a specific exemption has been obtained.

## 3. REQUIREMENTS

- 3.1 <u>Item requirements</u>. The individual item requirements for device classes Q and V shall be in accordance with MIL-PRF-38535 and as specified herein or as modified in the device manufacturer's Quality Management (QM) plan. The modification in the QM plan shall not affect the form, fit, or function as described herein. The individual item requirements for device class M shall be in accordance with MIL-PRF-38535, appendix A for non-JAN class level B devices and as specified herein.

- 3.2 <u>Design, construction, and physical dimensions</u>. The design, construction, and physical dimensions shall be as specified in MIL-PRF-38535 and herein for device classes Q and V or MIL-PRF-38535, appendix A and herein for device class M.

- 3.2.1 Case outlines. The case outlines shall be in accordance with 1.2.4 and figure 1 herein.

- 3.2.2 <u>Terminal connections</u>. The terminal connections shall be as specified on figure 2.

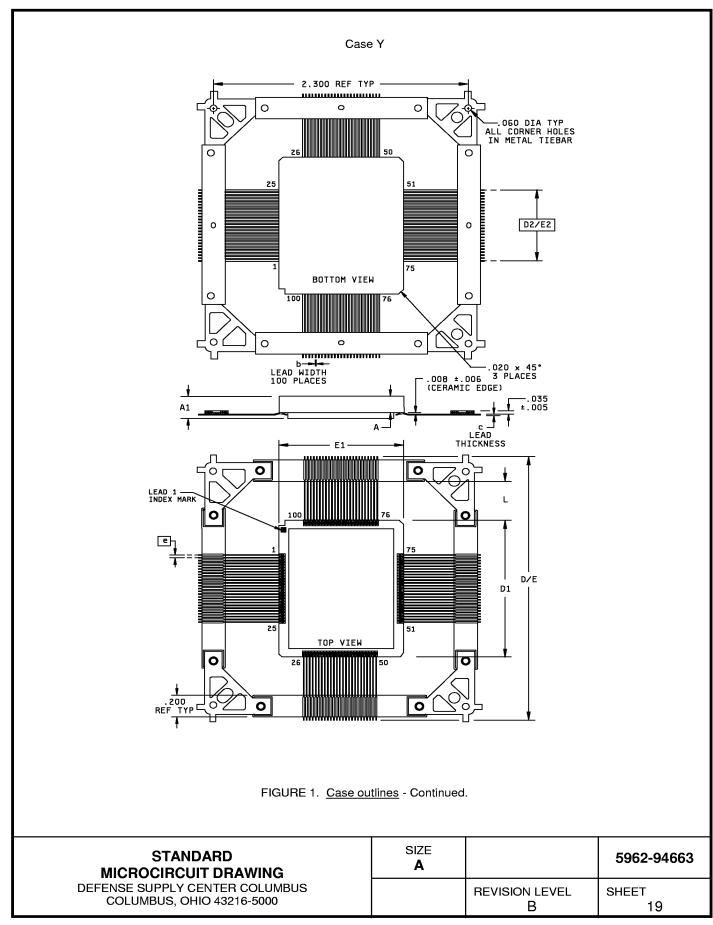

- 3.2.3 Block diagram. The block diagram shall be as specified on figure 3.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 5962-94663 |

|----------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43216-5000        |                  | B              | 5          |

- 3.2.4 Boundary scan instruction codes. The boundary scan instruction codes shall be as specified on figure 4.

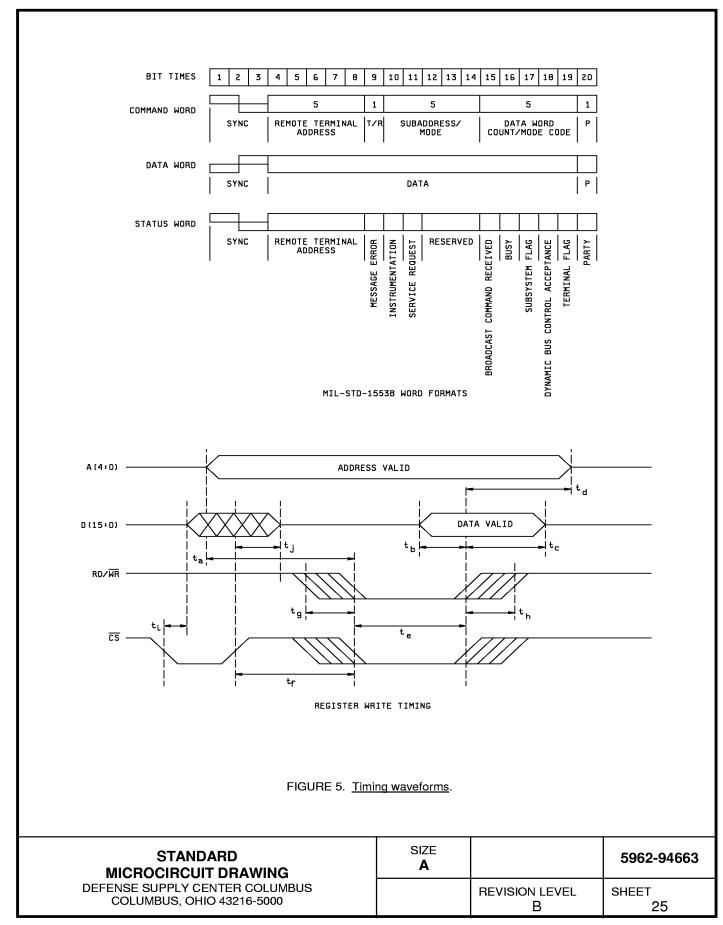

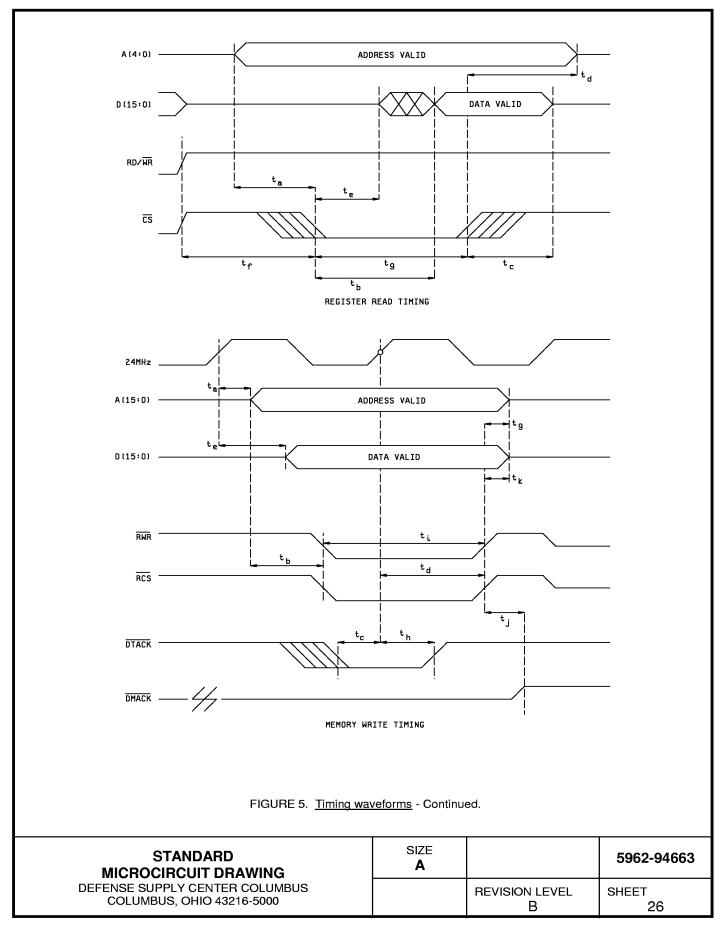

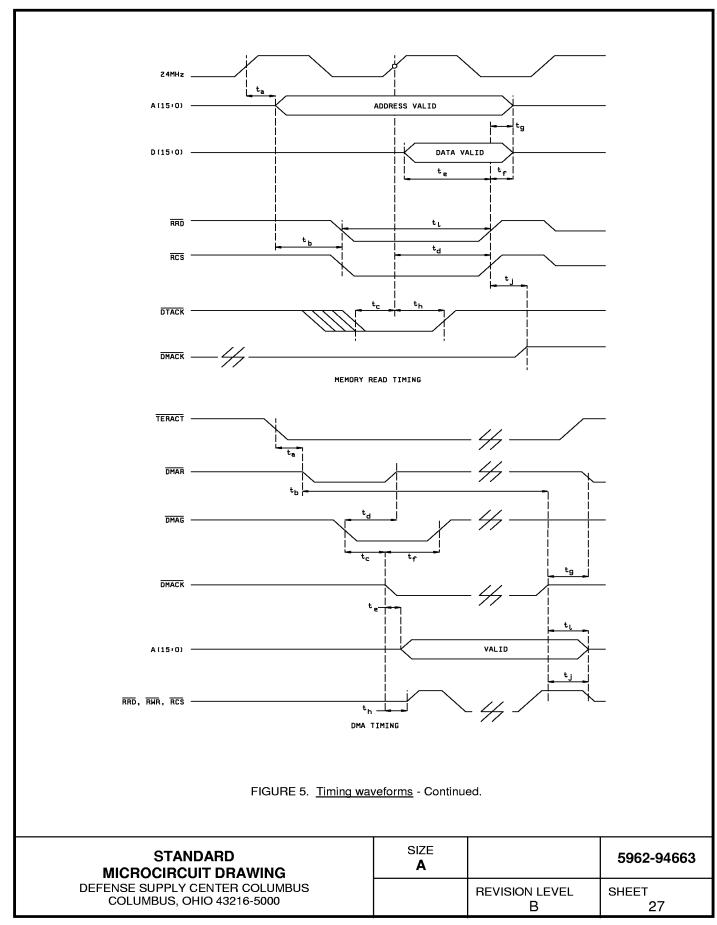

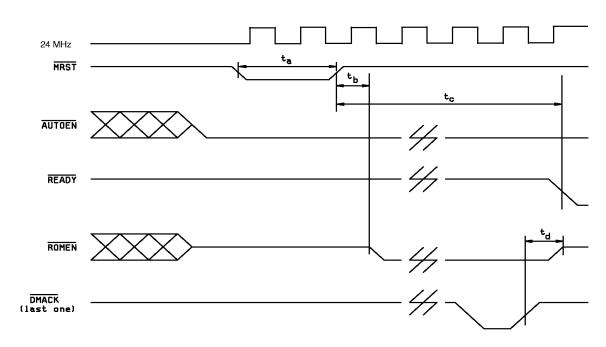

- 3.2.5 Timing waveforms. The timing waveforms shall be as specified on figure 5.

- 3.2.6 Radiation exposure connections. The radiation exposure connections shall be as specified on figure 6.

- 3.3 <u>Electrical performance characteristics and postirradiation parameter limits</u>. Unless otherwise specified herein, the electrical performance characteristics and postirradiation parameter limits are as specified in table IA and shall apply over the full case operating temperature range.

- 3.4 <u>Electrical test requirements</u>. The electrical test requirements shall be the subgroups specified in table IIA. The electrical tests for each subgroup are defined in table IA.

- 3.5 <u>Marking</u>. The part shall be marked with the PIN listed in 1.2 herein. In addition, the manufacturer's PIN may also be marked as listed in MIL-HDBK-103. For packages where marking of the entire SMD PIN number is not feasible due to space limitations, the manufacturer has the option of not marking the "5962-" on the device. For RHA product using this option, the RHA designator shall still be marked. Marking for device classes Q and V shall be in accordance with MIL-PRF-38535. Marking for device class M shall be in accordance with MIL-PRF-38535, appendix A.

- 3.5.1 <u>Certification/compliance mark</u>. The certification mark for device classes Q and V shall be a "QML" or "Q" as required in MIL-PRF-38535. The compliance mark for device class M shall be a "C" as required in MIL-PRF-38535, appendix A.

- 3.6 <u>Certificate of compliance</u>. For device classes Q and V, a certificate of compliance shall be required from a QML-38535 listed manufacturer in order to supply to the requirements of this drawing (see 6.6.1 herein). For device class M, a certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in MIL-HDBK-103 (see 6.6.2 herein). The certificate of compliance submitted to DSCC-VA prior to listing as an approved source of supply for this drawing shall affirm that the manufacturer's product meets, for device classes Q and V, the requirements of MIL-PRF-38535 and herein or for device class M, the requirements of MIL-PRF-38535, appendix A and herein.

- 3.7 <u>Certificate of conformance</u>. A certificate of conformance as required for device classes Q and V in MIL-PRF-38535 or for device class M in MIL-PRF-38535, appendix A shall be provided with each lot of microcircuits delivered to this drawing.

- 3.8 <u>Notification of change for device class M.</u> For device class M, notification to DSCC-VA of change of product (see 6.2 herein) involving devices acquired to this drawing is required for any change as defined in MIL-STD-973.

- 3.9 <u>Verification and review for device class M.</u> For device class M, DSCC, DSCC's agent, and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available onshore at the option of the reviewer.

- 3.10 <u>Microcircuit group assignment for device class M.</u> Device class M devices covered by this drawing shall be in microcircuit group number H (see MIL-PRF-38535, appendix A).

- 3.11 IEEE 1149.1 compliance. Theses devices shall be compliant to IEEE 1149.1.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 5962-94663 |

|----------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43216-5000        |                  | B              | 6          |

|                                                                             |                              | TABLE IA. <u>Elec</u>                                                                                  | ctrical performance                                    | <u>characteri</u>            | stics.            |                            |                    |    |

|-----------------------------------------------------------------------------|------------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------|------------------------------|-------------------|----------------------------|--------------------|----|

| Test                                                                        | Symbol                       | -55 C To                                                                                               | ditions <u>1</u> /<br>C +125 C                         | Device<br>type               | Group A subgroups | Limi                       | Unit               |    |

|                                                                             |                              |                                                                                                        | $4.5~V~V_{\text{DD}}~5.5~V$ unless otherwise specified |                              |                   | Min                        | Max                |    |

| Low level input voltage                                                     | V <sub>IL1</sub>             |                                                                                                        |                                                        | All                          | 1, 2, 3           |                            | 0.8                | V  |

| Low level input voltage,<br>TCK only                                        | V <sub>IL2</sub>             |                                                                                                        |                                                        | 01, 02<br>03, 04<br>05, 06   | 1, 2, 3           |                            | 0.8                |    |

|                                                                             |                              |                                                                                                        |                                                        | 07, 08<br>09                 | 1, 2, 3           |                            | 0.7                |    |

| High level input voltage                                                    | V <sub>IH</sub>              |                                                                                                        |                                                        | All                          | 1, 2, 3           | 2.2                        |                    | V  |

| Low level input voltage <u>2</u> /                                          | V <sub>ILC</sub>             |                                                                                                        |                                                        | All                          | 1, 2, 3           |                            | 0.3V <sub>DD</sub> | V  |

| High level input voltage 2/                                                 | V <sub>IHC</sub>             |                                                                                                        |                                                        | All                          | 1, 2, 3           | <b>0</b> .7V <sub>DD</sub> |                    | V  |

| Low level output                                                            | V <sub>OL</sub>              | Output loads                                                                                           | I <sub>OL</sub> = 4.0 mA                               | All                          | 1, 2, 3           |                            | 0.4                | V  |

| voltage                                                                     |                              | '                                                                                                      | I <sub>OL</sub> = 1.0 A <u>3</u> /                     | 1 '                          | '                 |                            | 0.05               | 1  |

| High level output                                                           | V <sub>OH</sub>              | Output loads                                                                                           | I <sub>OH</sub> = 4.0 mA                               | All                          | 1, 2, 3           | 2.4                        |                    | V  |

| voltage                                                                     |                              | '                                                                                                      | I <sub>OH</sub> = 1.0 A <u>3</u> /                     | 1 '                          | 1                 | V <sub>DD</sub> -0.05      |                    | 1  |

| Input leakage current                                                       | I <sub>IN</sub>              | TTL driven inputs                                                                                      | V <sub>IN</sub> = V <sub>DD</sub> or V <sub>SS</sub>   | All                          | 1, 2, 3           | -10                        | +10                | А  |

|                                                                             |                              | Inputs with                                                                                            | $V_{\text{IN}} = V_{\text{DD}}$                        | 1                            |                   | -10                        | +10                | 1  |

|                                                                             |                              | pull-up resistors                                                                                      | V <sub>IN</sub> = V <sub>SS</sub>                      | 01, 02,<br>03, 04,<br>05, 06 | 1, 2, 3           | -900                       | -150               |    |

|                                                                             |                              | !<br>!                                                                                                 |                                                        | 07, 08,<br>09                |                   | -167                       | -27                |    |

| Three-state output leakage current, TTL loaded outputs, single-drive buffer | loz                          | $V_O = V_{DD}$ or $V_{SS}$                                                                             |                                                        | All                          | 1, 2, 3           | -10                        | +10                | А  |

| Short-circuit output current, output loads                                  | los<br><u>4</u> / <u>5</u> / | $V_{DD} = 5.5 \text{ V}, V_{O} = V_{DD} = 5.5 \text{ V}, V_{O} = 0.0000000000000000000000000000000000$ |                                                        | All                          | 1, 2, 3           | -100                       | +100               | mA |

| Input capacitance                                                           | C <sub>IN</sub>              | f = 1 MHz at 0 V                                                                                       |                                                        | All                          | 4                 |                            | 45                 | pF |

| Output capacitance                                                          | C <sub>OUT</sub>             | See 4.4.1c                                                                                             |                                                        | All                          | 4                 |                            | 45                 |    |

| Bi-directional capacitance <u>6</u> /                                       | C <sub>IO</sub>              |                                                                                                        |                                                        | All                          | 4                 |                            | 45                 |    |

| Quiescent current                                                           | I <sub>DDQ</sub>             | f = 0 MHz                                                                                              |                                                        | All                          | 1, 3              |                            | 35                 | А  |

| <u>7</u> / <u>8</u> /                                                       |                              |                                                                                                        |                                                        | !                            | 2                 |                            | 1                  | mA |

| Standby operating current                                                   | I <sub>DDS</sub>             | f = 24 MHz                                                                                             |                                                        | All                          | 1, 2, 3           |                            | 40                 | mA |

See footnotes at end of table.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 5962-94663 |

|----------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43216-5000        |                  | C              | 7          |

|                                | TAF             | 3LE IA. <u>Electri</u>                           | ical performance chara                         | acteristics    | - Continued.      |     |      |          |     |   |

|--------------------------------|-----------------|--------------------------------------------------|------------------------------------------------|----------------|-------------------|-----|------|----------|-----|---|

| Test                           | Symbol          |                                                  | conditions <u>1</u> /<br>T <sub>C</sub> +125 C | Device<br>type | Group A subgroups | Lim | iits | Unit     |     |   |

|                                |                 | 4.5 V                                            | V <sub>DD</sub> 5.5 V<br>herwise specified     | <u> </u>       |                   | Min | Max  | ]        |     |   |

| V <sub>CC</sub> supply current | lcc             | V <sub>EE</sub> = -12 V<br>V <sub>CC</sub> = 5 V | 0% duty cycle<br>(non-transmitting)            | 03, 06<br>09   | 1, 2, 3           |     | 140  | mA       |     |   |

|                                |                 |                                                  | 50% duty cycle<br>(f = 1 MHz) <u>9</u> /       |                | [                 |     | 140  | ]        |     |   |

|                                |                 |                                                  | 100% duty cycle<br>(f = 1 MHz) <u>9</u> /      |                | [                 |     | 140  | ]        |     |   |

|                                |                 | V <sub>EE</sub> = -15 V<br>V <sub>CC</sub> = 5 V | 0% duty cycle<br>(non-transmitting)            | 01, 04<br>07   | [                 |     | 140  | ]        |     |   |

|                                |                 |                                                  | 50% duty cycle<br>(f = 1 MHz) <u>9</u> /       |                |                   |     | 140  |          |     |   |

|                                |                 |                                                  | 100% duty cycle<br>(f = 1 MHz) <u>9</u> /      |                |                   |     | [    |          | 140 | ] |

|                                |                 | V <sub>CC</sub> = 5 V                            | 0% duty cycle<br>(non-transmitting)            | 02, 05<br>08   | 1, 2, 3           | 55  | 55   |          |     |   |

|                                |                 |                                                  | 25% duty cycle <u>10</u> /                     | 1              |                   |     | 250  | 1        |     |   |

|                                |                 |                                                  | 50% duty cycle<br>(f = 1 MHz) <u>10</u> /      |                |                   |     | 410  |          |     |   |

|                                |                 |                                                  | 87.5% duty cycle<br>(f = 1 MHz) <u>10</u> /    | l'             |                   |     | 650  |          |     |   |

|                                |                 |                                                  | 100% duty cycle<br>(f = 500 kHz)               | 02             |                   |     | 855  | ]        |     |   |

| I <sub>EE</sub> supply current | I <sub>EE</sub> | V <sub>EE</sub> = -12 V<br>V <sub>CC</sub> = 5 V | 0% duty cycle<br>(non-transmitting)            | 03, 06<br>09   | 1, 2, 3           |     | 80   | mA       |     |   |

|                                |                 |                                                  | 50% duty cycle<br>(f = 1 MHz) ) <u>9</u> /     |                |                   |     | 180  |          |     |   |

|                                |                 |                                                  | 100% duty cycle<br>(f = 1 MHz) ) <u>9</u> /    | l              |                   |     | 270  | ]        |     |   |

|                                |                 | V <sub>EE</sub> = -15 V<br>V <sub>CC</sub> = 5 V | 0% duty cycle<br>(non-transmitting)            | 01, 04<br>07   |                   |     | 80   |          |     |   |

|                                |                 |                                                  | 50% duty cycle<br>(f = 1 MHz) ) <u>9</u> /     |                |                   |     | 180  |          |     |   |

|                                |                 |                                                  | 100% duty cycle<br>(f = 1 MHz) ) <u>9</u> /    |                |                   |     | 270  | <u>]</u> |     |   |

| Functional tests               |                 | See 4.4.1b                                       |                                                | All            | 7, 8              |     |      |          |     |   |

See footnotes at end of table.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                     | 5962-94663 |

|-------------------------------------------------------------|------------------|---------------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL<br>C | SHEET<br>8 |

|                                                     | TAB               | SLE IA. <u>Electrical performan</u> o                                                    | ce characteristics         | - Continued.      |      |            |      |

|-----------------------------------------------------|-------------------|------------------------------------------------------------------------------------------|----------------------------|-------------------|------|------------|------|

| Test                                                | Symbol            | Test conditions <u>1</u> /<br>-55 C T <sub>C</sub> +125 C<br>4.5 V V <sub>DD</sub> 5.5 V | type                       | Group A subgroups |      | mits       | Unit |

|                                                     |                   | unless otherwise speci                                                                   |                            |                   | Min  | Max        |      |

|                                                     | •                 | Register wr                                                                              | ite timing                 | •                 |      | •          | •    |

| Address setup time 9/                               | t <sub>a</sub>    | V <sub>CC</sub> = minimum                                                                | All                        | 9, 10, 11         | 0    |            | ns   |

| Data setup time 9/                                  | t <sub>b</sub>    | See figure 5                                                                             | All                        | 9, 10, 11         | 10   |            |      |

| Data hold time 9/                                   | tc                |                                                                                          | All                        | 9, 10, 11         | 8    |            |      |

| Address hold time 9/                                | t <sub>d</sub>    |                                                                                          | All                        | 9, 10, 11         | 8    |            |      |

| CS to CS 9/                                         | te                |                                                                                          | All                        | 9, 10, 11         | 105  |            |      |

| Access delay <u>9</u> / <u>11</u> / <u>12</u> /     | t <sub>f</sub>    |                                                                                          | All                        | 9, 10, 11         | 85   |            | 1    |

| RD/WR assertion to CS assertion 10/                 | tg                |                                                                                          | All                        | 9, 10, 11         | 0    |            |      |

| CS negation to                                      | t <sub>h</sub>    |                                                                                          | All                        | 9, 10, 11         | 0    |            |      |

| RD/WR negation 10/                                  |                   |                                                                                          |                            |                   |      |            | _    |

| CS assertion to output enable <u>9</u> /            | t <sub>i</sub>    |                                                                                          | All                        | 9, 10, 11         | 0    | 40         |      |

| CS negation to output three-state 10/               | tj                |                                                                                          | All                        | 9, 10, 11         | 5    | 35         |      |

|                                                     |                   | Register re                                                                              | ad timing                  |                   |      |            |      |

| Address setup time 9/                               | ta                | V <sub>CC</sub> = minimum<br>See figure 5                                                | All                        | 9, 10, 11         | 0    |            | ns   |

| CS assertion to output enable data valid <u>9</u> / | t <sub>b</sub>    | See ligure 3                                                                             | All                        | 9, 10, 11         |      | 95         |      |

| CS negation to output disabled 10/                  | tc                |                                                                                          | All                        | 9, 10, 11         | 5    | 35         |      |

| Address hold time 9/                                | t <sub>d</sub>    |                                                                                          | All                        | 9, 10, 11         | 0    |            |      |

| CS assertion to output enable data invalid 9/       | t <sub>e</sub>    |                                                                                          | All                        | 9, 10, 11         | 0    | 40         |      |

| Access delay <u>9</u> / <u>11</u> / <u>12</u> /     | t <sub>f</sub>    |                                                                                          | All                        | 9, 10, 11         | 45   |            |      |

| CS to CS 9/                                         | tg                |                                                                                          | All                        | 9, 10, 11         | 105  |            |      |

| <del>_</del>                                        | 1                 | Memory wr                                                                                | ite timing                 |                   |      |            |      |

| Address propagation delay                           | ta                | V <sub>CC</sub> = minimum<br>See figure 5                                                | 01, 02<br>03, 04<br>05, 06 |                   | 0    | 18         | ns   |

|                                                     |                   |                                                                                          | 07, 08<br>09               |                   | 0    | 21         |      |

| Address valid to RCS, RWR assertion 9/              | t <sub>b</sub>    |                                                                                          | All                        | 9, 10, 11         | 15   | 35         |      |

| See footnotes at end of tal                         | ole.              |                                                                                          | ,                          |                   |      |            | •    |

| S <sup>-</sup><br>Microci                           | TANDAR<br>RCUIT D |                                                                                          | SIZE<br><b>A</b>           |                   |      | 5962-9     | 4663 |

| DEFENSE SUPI<br>COLUMBU                             |                   |                                                                                          |                            | REVISION LI       | EVEL | SHEET<br>9 |      |

|                                                                               | TAB            | SLE IA. <u>Electrical performanc</u>                                                    | ce characteristics         | - Continued.      |          |        |      |

|-------------------------------------------------------------------------------|----------------|-----------------------------------------------------------------------------------------|----------------------------|-------------------|----------|--------|------|

| Test                                                                          | Symbol         | Test conditions <u>1/</u><br>-55 C T <sub>C</sub> +125 C<br>4.5 V V <sub>DD</sub> 5.5 V | ; type                     | Group A subgroups |          | nits   | Unit |

|                                                                               |                | unless otherwise specif                                                                 |                            |                   | Min      | Max    |      |

|                                                                               |                | Memory write timi                                                                       | ng - Continued             |                   |          |        |      |

| DTACK setup time <u>9</u> /                                                   | tc             | V <sub>CC</sub> = minimum<br>See figure 5                                               | All                        | 9, 10, 11         | 10       |        | ns   |

| RCS and RWR hold time <u>9</u> / <u>13</u> /                                  | t <sub>d</sub> | Goo ligure o                                                                            | All                        | 9, 10, 11         | 20       | 50     |      |

| Data propagation delay <u>9</u> /                                             | t <sub>e</sub> |                                                                                         | All                        | 9, 10, 11         | 20       | 60     |      |

| Address hold time 9/                                                          | t <sub>g</sub> |                                                                                         | All                        | 9, 10, 11         | 10       | 30     | 1    |

| DTACK hold time 9/                                                            | t <sub>h</sub> |                                                                                         | All                        | 9, 10, 11         | 10       |        |      |

| RWR and RCS pulse width (DTACK tied to ground)                                | t <sub>i</sub> |                                                                                         | 01, 02<br>03, 04<br>05, 06 | 9, 10, 11         | 34       |        |      |

| ground)                                                                       |                |                                                                                         | 07, 08<br>09               | 9, 10, 11         | 32       |        |      |

| RWR and RCS to DMACK 10/                                                      | tj             |                                                                                         | All                        | 9, 10, 11         | 15       | 125    |      |

| Data hold time 10/                                                            | t <sub>k</sub> |                                                                                         | All                        | 9, 10, 11         | 10       | 40     |      |

|                                                                               |                | Memory rea                                                                              |                            | T T               |          | T      | 1    |

| Address propagation delay                                                     | t <sub>a</sub> | V <sub>CC</sub> = minimum<br>See figure 5                                               | 01, 02<br>03, 04<br>05, 06 | 9, 10, 11         | 0        | 18     | ns   |

|                                                                               |                |                                                                                         | 07, 08<br>09               | 9, 10, 11         | 0        | 21     |      |

| Address valid to RCS, RRD assertion 9/                                        | t <sub>b</sub> |                                                                                         | All                        | 9, 10, 11         | 15       | 35     |      |

| DTACK setup time 9/                                                           | tc             |                                                                                         | All                        | 9, 10, 11         | 10       |        | 1    |

| RCS and RRD hold time 9/ 13/                                                  | t <sub>d</sub> |                                                                                         | All                        | 9, 10, 11         | 20       | 50     |      |

| Data setup delay 9/                                                           | t <sub>e</sub> |                                                                                         | 01, 02<br>03, 04<br>05, 06 | 9, 10, 11         | 12       |        |      |

|                                                                               |                |                                                                                         | 07, 08<br>09               | 9, 10, 11         | 10       |        |      |

| Data hold delay                                                               | t <sub>f</sub> |                                                                                         | 01, 02<br>03, 04<br>05, 06 | 9, 10, 11         | 0        |        |      |

|                                                                               |                |                                                                                         | 07, 08<br>09               | 9, 10, 11         | 2        |        |      |

| Address hold time <u>9</u> /                                                  | tg             |                                                                                         | All                        | 9, 10, 11         | 10       | 30     |      |

| Address hold time 9/ See footnotes at end of tal                              |                |                                                                                         |                            |                   | 10       | 30     |      |

|                                                                               | TANDAR         |                                                                                         | SIZE<br><b>A</b>           |                   |          | 5962-9 | 4663 |

| MICROCIRCUIT DRAWING DEFENSE SUPPLY CENTER COLUMBUS COLUMBUS, OHIO 43216-5000 |                |                                                                                         | REVISION LE                | EVEL              | SHEET 10 | )      |      |

| Test                                           | Symbol         |                                           | onditions <u>1</u> /<br>T <sub>C</sub> +125 C | Device<br>type             | Group A subgroups | Lim | nits | Unit |

|------------------------------------------------|----------------|-------------------------------------------|-----------------------------------------------|----------------------------|-------------------|-----|------|------|

|                                                |                | 4.5 V                                     | V <sub>DD</sub> 5.5 V<br>erwise specified     | 1 2/1-                     |                   | Min | Max  | 1    |

|                                                |                | Mem                                       | ory read timing - Co                          | ntinued                    |                   |     |      |      |

| DTACK hold time                                | th             | V <sub>CC</sub> = minimum                 | n                                             | All                        | 9, 10, 11         | 10  |      | ns   |

| RRD and RCS pulse width (DTACK tied to ground) | ti             | See figure 5                              |                                               | 01, 02<br>03, 04<br>05, 06 | 9, 10, 11         | 34  |      |      |

| ground)                                        |                |                                           |                                               | 07, 08<br>09               | 9, 10, 11         | 32  |      |      |

| RRD and RCS to DMACK <u>10</u> /               | tj             |                                           |                                               | All                        | 9, 10, 11         | 15  | 45   |      |

|                                                | _              | •                                         | DMA timing                                    |                            |                   |     |      |      |

| TERACT assertion to DMAR assertion 9/          | t <sub>a</sub> | V <sub>CC</sub> = minimum<br>See figure 5 | n                                             | All                        | 9, 10, 11         | 5   |      | s    |

| DMAR assertion to DMACK negation 9/            | t <sub>b</sub> |                                           | Bus controller                                | 01, 02<br>03               | 9, 10, 11         |     | 7    |      |

| Daniel Hegaler <u>G</u>                        |                |                                           |                                               | 04, 05<br>06, 07<br>08, 09 | 9, 10, 11         |     | 16   |      |

|                                                |                |                                           | Remote terminal                               | All                        | 9, 10, 11         |     | 7    |      |

|                                                |                |                                           | Remote terminal with monitor                  | All                        | 9, 10, 11         |     | 7    |      |

|                                                |                |                                           | Monitor                                       | All                        | 9, 10, 11         |     | 7    |      |

| DMAG assertion to DMACK assertion              | tc             |                                           |                                               | 01, 02<br>03, 04<br>05, 06 | 9, 10, 11         | 0   | 30   | ns   |

| <u>9</u> /                                     |                |                                           |                                               | 07, 08<br>09               | 9, 10, 11         | 5   | 30   |      |

| DMAG assertion to  DMAR negation 10/           | t <sub>d</sub> |                                           |                                               | All                        | 9, 10, 11         | 0   | 35   |      |

| DMACK assertion to address bus active          | t <sub>e</sub> |                                           |                                               | 01, 02<br>03, 04<br>05, 06 | 9, 10, 11         | 0   | 5    |      |

|                                                |                |                                           |                                               | 07, 08<br>09               | 9, 10, 11         | -5  | 5    |      |

| DMACK assertion to DMAG negation 9/            | t <sub>f</sub> |                                           |                                               | All                        | 9, 10, 11         | 10  |      |      |

| DMACK negation to DMAR assertion 9/            | tg             |                                           |                                               | All                        | 9, 10, 11         | 500 |      |      |

| See footnotes at end of ta                     | ble.           |                                           |                                               |                            |                   |     |      |      |

|                                                |                |                                           |                                               |                            | 1                 |     |      |      |

|                                                                               | TABL            | E IA. <u>Electrical performan</u>                                                                             | ce charac   | cteristics                 | - Continued.      |                          |          |       |

|-------------------------------------------------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------|-------------|----------------------------|-------------------|--------------------------|----------|-------|

| Test                                                                          | Symbol          | Test conditions 1/<br>-55 C T <sub>C</sub> +125 (                                                             | c           | Device<br>type             | Group A subgroups | Lim                      | nits     | Unit  |

|                                                                               |                 | 4.5 V V <sub>DD</sub> 5.5 V unless otherwise speci                                                            |             |                            |                   | Min                      | Max      |       |

|                                                                               |                 | DMA timing -                                                                                                  | Continue    | ed                         |                   |                          |          |       |

| DMACK assertion to<br>RAM control active<br>(negated)                         | t <sub>h</sub>  | V <sub>CC</sub> = minimum<br>See figure 5                                                                     |             | 01, 02<br>03, 04<br>05, 06 | 9, 10, 11         | 0                        | 5        | ns    |

| (110 gant 0)                                                                  |                 |                                                                                                               |             | 07, 08<br>09               |                   | -5                       | 5        |       |

| DMACK negation to address three-state 10/                                     | ti              |                                                                                                               | _           | All                        | 9, 10, 11         |                          | 5        |       |

| DMACK negation to RAM control disabled 10/                                    | t <sub>j</sub>  |                                                                                                               |             | All                        | 9, 10, 11         |                          | 5        |       |

|                                                                               |                 | Power-up maste                                                                                                | er reset ti | ming                       |                   |                          |          |       |

| MRST pulse width 9/                                                           | ta              | V <sub>CC</sub> = minimum                                                                                     |             | All                        | 9, 10, 11         | 500                      |          | ns    |

| MRST negation to ROMEN assertion 9/                                           | t <sub>b</sub>  | See figure 5                                                                                                  | ļ           | All                        | 9, 10, 11         |                          | 5        | s     |

| MRST negation to READY assertion 9/                                           | t <sub>c</sub>  |                                                                                                               |             | All                        | 9, 10, 11         |                          | 10       | s     |

| DMACK negation to ROMEN negation 9/                                           | t <sub>d</sub>  |                                                                                                               |             | All                        | 9, 10, 11         |                          | 500      | ns    |

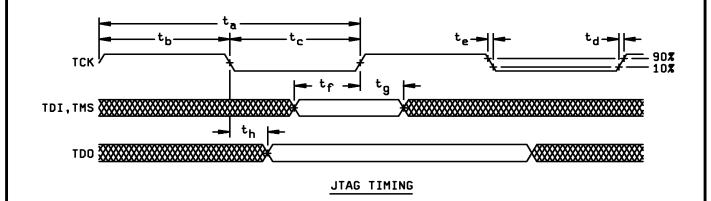

|                                                                               | l               | JTAG ti                                                                                                       | iming       |                            |                   |                          | •        |       |

| TCK frequency                                                                 |                 | See figure 5                                                                                                  |             | All                        | 9, 10, 11         |                          | 1        | MHz   |

| TCK period                                                                    | ta              |                                                                                                               |             | All                        | 9, 10, 11         | 1000                     |          | ns    |

| TCK high time                                                                 | t <sub>b</sub>  |                                                                                                               |             | All                        | 9, 10, 11         | 1/2t <sub>a</sub>        |          |       |