## **Infrared Encoder/Decoder**

### **Features**

- · Pinout compatible with HSDL-7000

- Compliant with IrDA<sup>®</sup> Standard Physical Layer Specification (version 1.3)

- · UART to IrDA Standard Encoder/Decoder

- Interfaces with IrDA Standard Compliant Transceiver

- · Baud rates:

- Up to IrDA standard 115.2 Kbaud operation

- Transmit/Receive formats (bit width) supported:

- 1.63 µs

- Low-power mode (2 μA at 1.8V, +125°C)

### **CMOS Technology**

- · Low-voltage operation

- · Extended temperature range

- · Low power consumption

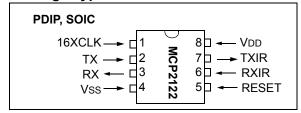

### **Package Types**

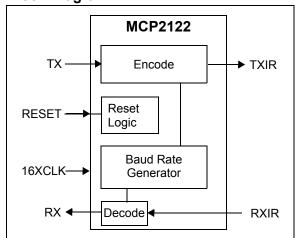

### **Block Diagram**

### IrDA Family Selection

|         | Baud Rate                        |                                  | Encoder/ | Protocol   | Clock  | Host UART              |                                                            |  |

|---------|----------------------------------|----------------------------------|----------|------------|--------|------------------------|------------------------------------------------------------|--|

| Device  | Host<br>UART                     | IR                               | Decoder  | l aver     |        | Baud Rate<br>Selection | Comment                                                    |  |

| MCP2120 | 2400 -<br>312,500 <sup>(1)</sup> | 2400 -<br>312,500 <sup>(1)</sup> | Yes      | No         | XTAL   | HW/SW                  |                                                            |  |

| MCP2122 | 2400 -<br>115,200 <sup>(1)</sup> | 2400 -<br>312,500 <sup>(1)</sup> | Yes      | No         | 16XCLK | By 16XCLK              | Extended Temperature Range (-40°C to +125°C)               |  |

| MCP2140 | 9600                             | 9600                             | Yes      | IrCOMM (3) | XTAL   | None -Fixed            |                                                            |  |

| MCP2150 | 9600 -<br>115,200 <sup>(2)</sup> | 9600 -<br>115,200 <sup>(2)</sup> | Yes      | IrCOMM (3) | XTAL   | HW                     | Host UART easily interfaces to a PC's serial port (DTE)    |  |

| MCP2155 | 9600 -<br>115,200 <sup>(2)</sup> | 9600 -<br>115,200 <sup>(2)</sup> | Yes      | IrCOMM (3) | XTAL   | HW                     | Host UART easily interfaces to a modem's serial port (DCE) |  |

- Note 1: The host UART and the IR operate at the same baud rates.

- 2: The host UART baud rate and the IR baud rates operate independent of each other.

- 3: Supports the 9-wire "cooked" service class of the IrCOMM Application Layer Protocol.

NOTES:

### 1.0 DEVICE OVERVIEW

The MCP2122 is a stand-alone IrDA standard encoder/decoder device that is pinout-compatible with the Agilent® HSDL-7000 Encoder/Decoder.

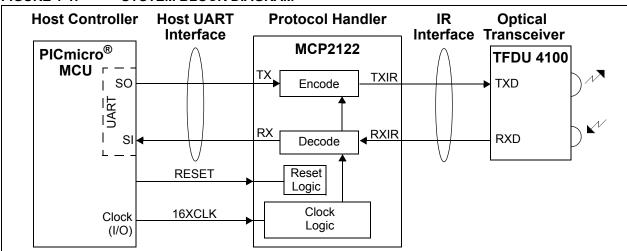

The MCP2122 has two interfaces: the host UART interface and the IR interface (see Figure 1-1). The host UART interfaces to the UART of the host controller. The host controller is the device in the embedded system that transmits and receives the data. The IR interface connects to an infrared (IR) optical transceiver circuit, which converts electrical pulses into IR light (encode) and converts IR light into electrical pulses (decode). This IR optical transceiver circuit could be either a standard infrared (IR) optical transceiver (such as a Vishay® TFDU 4100) or it could be implemented with discrete components. For additional information, please refer to Application Note 243, "Fundamentals of the Infrared Physical Layer" (DS00243).

When the host controller transmits the UART format data, the MCP2122 receives this UART data and encodes (modulates) the data bit by bit. This encoded data is then output as electrical pulses to the IR Transceiver. The IR transceiver will then convert these electrical pulses to IR light pulses.

The IR Transceiver also receives IR light pulses (data), which are outputted as electrical pulses. The MCP2122 decodes (demodulates) these electrical pulses, with the data then transmitted by the MCP2122 UART. This modulation and demodulation method is performed in accordance with the IrDA standard.

Table 1-1 shows an overview of some of the device features. Figure 1-1 shows a typical application block diagram. Table 1-2 shows the pin definitions of the MCP2122 in normal operation.

TABLE 1-1: MCP2122 FEATURES OVERVIEW

| Features               | MCP2122                  |  |  |  |  |  |  |

|------------------------|--------------------------|--|--|--|--|--|--|

| Serial Communications: | UART, IR                 |  |  |  |  |  |  |

| Baud Rate Selection:   | 16XCLK                   |  |  |  |  |  |  |

| Low Power Mode:        | Yes                      |  |  |  |  |  |  |

| Resets: (and Delays)   | RESET pin (none)         |  |  |  |  |  |  |

| Packages:              | 8-pin PDIP<br>8-pin SOIC |  |  |  |  |  |  |

Infrared Technology Features:

- Universal standard for connecting portable computing devices

- · Easy, effortless implementation

- Economical alternative to other connectivity solutions

- · Reliable, high speed connection

- Safe to use in any environment; can even be used during air travel

- · Eliminates the hassle of cables

- Allows PC's and non-PC's to communicate to each other

- Enhances mobility by allowing users to easily connect

### 1.1 Applications

Some applications where an IR interface (MCP2122) could be used include:

- · Data Logging/Data Exchange

- System Setup

- · System Diagnostic Read Out

- Manufacturing Configuration

- · Host Controller Firmware Updates

- · System Control

FIGURE 1-1: SYSTEM BLOCK DIAGRAM

**PIN DESCRIPTION TABLE 1-2:**

| Din Nama | Pin N | umber | Pin         | Buffer |                                                            |  |  |  |  |  |

|----------|-------|-------|-------------|--------|------------------------------------------------------------|--|--|--|--|--|

| Pin Name | PDIP  | SOIC  | OIC Type Ty |        | Description                                                |  |  |  |  |  |

| 16XCLK   | 1     | 1     | I           | ST     | 16x external clock source input                            |  |  |  |  |  |

| TX       | 2     | 2     | I           | ST     | Asynchronous receive from host controller UART             |  |  |  |  |  |

| RX       | 3     | 3     | 0           | _      | Asynchronous transmit to host controller UART              |  |  |  |  |  |

| Vss      | 4     | 4     | _           | Р      | Ground reference for logic and I/O pins                    |  |  |  |  |  |

| RESET    | 5     | 5     | I           | ST     | Resets the Device H = Normal Operation L = Device in Reset |  |  |  |  |  |

| RXIR     | 6     | 6     | I           | ST     | Asynchronous receive from infrared transceiver             |  |  |  |  |  |

| TXIR     | 7     | 7     | 0           | _      | Asynchronous transmit to infrared transceiver              |  |  |  |  |  |

| Vdd      | 8     | 8     | _           | Р      | Positive supply for logic and I/O pins                     |  |  |  |  |  |

Legend: ST = Schmitt Trigger input with CMOS levels I = Input P = Power O = Output

### 2.0 DEVICE OPERATION

The MCP2122 is a low-cost infrared encoder/decoder. The baud rate is the same for the host UART and IR interfaces and is determined by the frequency of the 16XCLK signal, with a maximum baud rate of 115.2 Kbaud.

The MCP2122 is made up of these functional modules:

- Clock Driver (16XCLK)

- Reset

- IR Encoder/Decoder

- IrDA Standard Encoder

- IrDA Standard Decoder

The **16XCLK** circuit allows a clock input to provide the device clock.

The **Reset** circuit supports an external reset signal.

The IR Encoder logic takes a data bit and converts it to the IrDA signal according to the IrDA Standard Physical Layer specification, while the IR Decoder logic takes the IrDA standard signal and converts it to 8-bit data bytes.

### 2.1 Power-up

As the device is powered up, there will be a voltage range where the device will not operate properly. The device should be reset once the device has entered the normal operating range (from an out-of-voltage condition). The RESET pin may then be forced high.

Other device operating parameters (such as frequency, temperature, etc.) must also be within their operating ranges when the device exits reset. Otherwise, the device may not function as desired.

### 2.2 Device Reset

The MCP2122 is forced into the known state (RESET) when the RESET pin is in the low state. Once the RESET pin is brought to a high state, the device begins normal operation (if the device operating parameters are met). Table 2-1 shows the states of the output pins while the device is in reset (RESET = Low). Table 2-2 shows the state of the output pins once the device exits reset, RESET =  $L \rightarrow H$  (device in Normal Operation mode).

The MCP2122 has a RESET noise filter in the RESET input signal path. The filter will detect and ignore small pulses.

Using the RESET pin to enter a low-power state is discussed in **Section 2.9 "Minimizing Power"**.

TABLE 2-1: DEFAULT OUTPUT PIN STATES IN DEVICE RESET

| Input | Pin              |   | ut Pin<br>ate | Comments             |  |

|-------|------------------|---|---------------|----------------------|--|

| Name  | ne State RX TXIR |   | TXIR          |                      |  |

| RESET | L                | Η | L             | Device in Reset mode |  |

TABLE 2-2: DEFAULT OUTPUT PIN STATES AFTER DEVICE RESET (RESET =  $L\rightarrow H$ )

| Input | t Pin | Output Pin<br>State |           | Comments                                                 |

|-------|-------|---------------------|-----------|----------------------------------------------------------|

| Name  | State | RX                  | TXIR      |                                                          |

| TX    | L     | _                   | L→H<br>→L | After 7 - 8 16XCLK pulses, the TXIR pin will pulse high. |

|       | Н     | _                   | L         |                                                          |

| RXIR  | L     | H→L                 | _         | After 4 16XCLK pulses,<br>RX = L.                        |

|       | Н     | Н                   |           |                                                          |

### 2.3 Decoupling

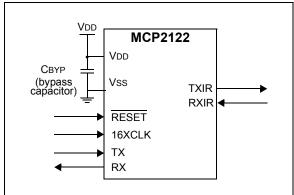

It is highly recommended that the MCP2122 have a decoupling capacitor ( $C_{BYP}$ ). A 0.01  $\mu F$  capacitor is recommended as a starting value, but evaluation of the best value for your circuit/layout should be done. Place this decoupling capacitor ( $C_{BYP}$ ) as close to the MCP2122 as possible (see Figure 2-1).

FIGURE 2-1: DEVICE DECOUPLING

### 2.3.1 BROWN-OUTS

Some applications may subject the MCP2122 to a brown-out condition. Good design practice requires that when a system is in brown-out, the system should be in reset to ensure that the system is in a known state when the system exits the brown-out. This brown-out circuitry is external to the MCP2122.

### 2.3.1.1 External Brown-Out Reset Circuits

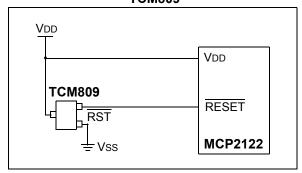

Figure 2-2 shows a circuit for external brown-out protection using the TCM809 device.

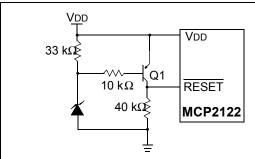

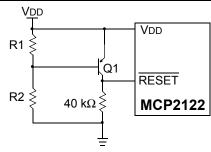

Figure 2-3 and Figure 2-4 illustrate two examples of external circuitry that may be implemented. Each option needs to be evaluated to determine if they satisfy the requirements of the application.

FIGURE 2-2: EXTERNAL BROWN-OUT PROTECTION USING THE TCM809

FIGURE 2-3: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 1

- **Note 1:** Resistors should be adjusted for the characteristics of the transistor.

- 2: This circuit will activate reset when VDD goes below (Vz + 0.7V), where Vz = Zener voltage.

## FIGURE 2-4: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2

Note 1: This circuit is less expensive, but less accurate. Transistor Q1 turns off when VDD is below a certain level such that:

$$V_{DD} \cdot \frac{R1}{R1 + R2} = 0.7V$$

**2:** Resistors should be adjusted for the characteristics of the transistor.

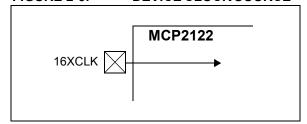

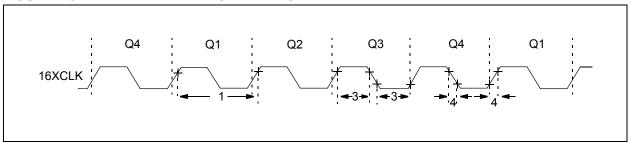

### 2.4 16XCLK (Bit Clock)

The MCP2122 requires an external clock source to operate. The 16XCLK pin is the device clock input (see Figure 2-5) and is independent of the host UART interface or the IR interface. The 16XCLK determines all timing during device operation. It is the edge of the 16XCLK pin that causes activity to occur.

The 16XCLK signal can also be referred to as a bit clock (BITCLK). There are 16 BITCLKs for each bit time. The BITCLKs are used for the generation of the Start bit, the eight data bits and the Stop bit.

When the embedded system could be receiving IR communication, the MCP2122 is required to have the 16XCLK signal clocking at the expected frequency and have minimal variation in frequency. Between data bytes (Stop bit to Start bit), the 16XCLK frequency can be changed. This may occur in systems where the host controller is implementing one of the IrDA standard application layer protocols (such as IrObex).

When the embedded system does not want to receive IR communications, the 16XCLK clock can be disabled (static). This will reduce the power consumption of the system.

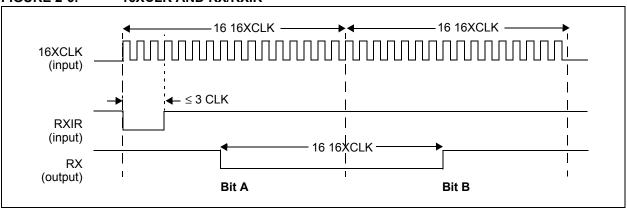

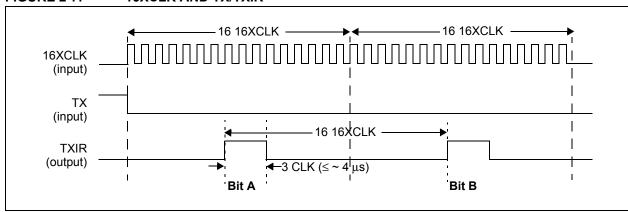

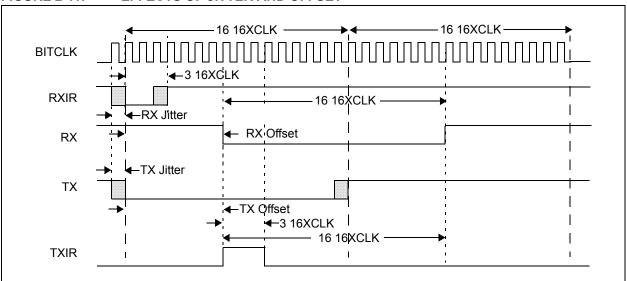

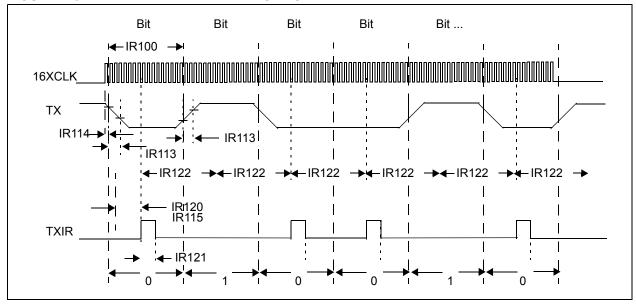

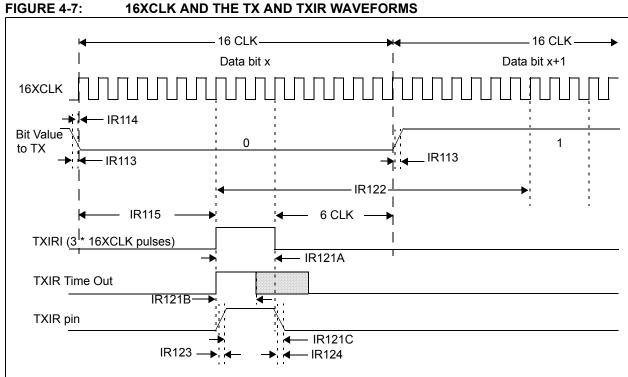

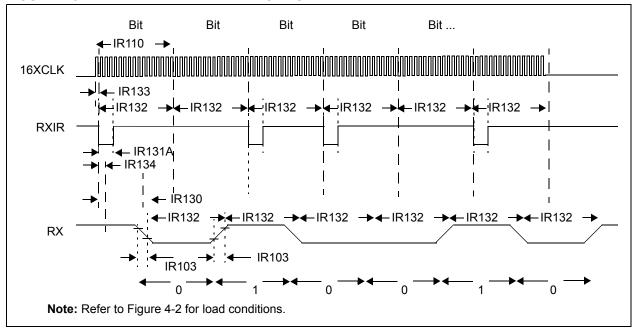

Figure 2-6 shows the relationship of the 16XCLK signal to the RXIR input, which then determines the RX output signal. Figure 2-7 shows the relationship of the 16XCLK signal to the TX input, which then determines the TXIR output signal. For device timing information, refer to Section 4.0 "Electrical Characteristics".

FIGURE 2-5: DEVICE CLOCK SOURCE

FIGURE 2-6: 16XCLK AND RX/RXIR

FIGURE 2-7: 16XCLK AND TX/TXIR

© 2004 Microchip Technology Inc. Preliminary DS21894A-page 7

### 2.4.1 BAUD RATE

The baud rate for the MCP2122 is determined by the frequency of the 16XCLK signal. Equation 2-1 demonstrates how to calculate the 16XCLK frequency based on the desired baud rate. Table 2-3 shows some common baud rates and the corresponding 16XCLK frequency.

**EQUATION 2-1: 16XCLK FREQUENCY**

$F_{16XCLK} = 16 \bullet (Desired Baud Rate)$

TABLE 2-3: COMMON BAUD RATE/ 16XCLK FREQUENCY

| Baud<br>Rate | 16XCLK<br>Frequency<br>(F <sub>16xclk</sub> ) | Comment |

|--------------|-----------------------------------------------|---------|

| 9600         | 153,600                                       |         |

| 19,200       | 307,200                                       |         |

| 38,400       | 614,400                                       |         |

| 57,600       | 921,600                                       |         |

| 115,200      | 1,843,200                                     |         |

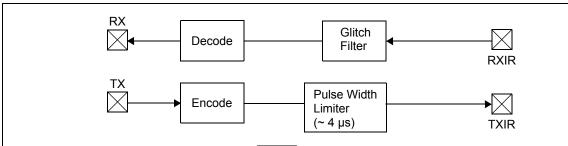

### 2.5 Encoder/Decoder

The IR Encoder/Decoder is made up of two major components. They are:

- · IR Decoder

- · IR Encoder

The encoder receives UART data (bit by bit) and outputs a data bit in the IrDA standard bit format. Figure 2-8 shows a functional block diagram of the encoder.

The decoder receives IrDA standard data (bit by bit) and outputs data in UART data bit format. Figure 2-8 shows a functional block diagram of the decoder.

The encoder/decoder has two interfaces. They are:

- · host UART interface

- · IR interface

### 2.5.1 ENCODING (MODULATION)

Each bit time is comprised of 16 bit clocks. If the value to be transmitted (as determined by the TX pin) is a logic-low, the TXIR pin will output a low level for 7-bit clock cycles, a logic-high level for 3-bit clock (with a maximum high-time of about 4 µs) cycles, with the remaining time (6-bit clock cycles or more) being low. If the value to transmit is a logic-high, the TXIR pin will output a low level for the entire 16 bit clock cycle.

### 2.5.2 DECODING (DEMODULATION)

Each bit time is comprised of 16 bit clocks. If the value to be received is a logic-low, the RXIR pin will be a low level for the first 3-bit clock cycle (or a minimum of 1.6  $\mu$ s), with the remaining time (13-bit clock cycles) being high. If the value to be received is a logic high, the RXIR pin will be a high level for the entire 16 bit clock cycle. The level on the RX pin will be in the appropriate state for an entire 16-bit clock cycle.

FIGURE 2-8: MCP2122 RECEIVE DETECT TO ENCODER/DECODER BLOCK DIAGRAM

The following table shows the state on the RESET pin and how this effects the operation of the TXIR pin.

| RESET State | Comment                             |  |  |  |  |

|-------------|-------------------------------------|--|--|--|--|

| VIH         | TXIR output encoded value of TX pin |  |  |  |  |

| VIL         | TXIR is forced low                  |  |  |  |  |

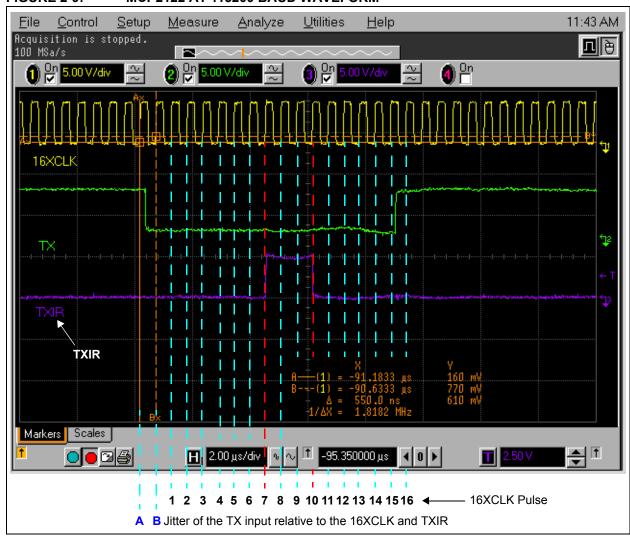

## 2.5.3 ENCODING AND SCREEN CAPTURES

Table 2-4 shows the TXIR pin high-time at different common baud rates. The internal TXIR pulse width high-time limiter is a feature that minimizes the system current consumption at lower baud rates. The IrDA standard specification requires that optical receiver circuitry detect pulses as narrow as 1.41 µs (1.63 µs is the typical time at 115200 baud). Therefore, the time that the TXIR pin is high after this valid detection is additional current that is driven by the emitter LED. The MCP2122 will force the TXIR pin low after the pulse width limiter has timed out. Figure 2-9 shows the MCP2122 16XCLK, TX and TXIR waveforms at 115200 baud for a single TX low bit. In this case the TXIR is high for three 16XCLK pulses. In Figure 2-10 the MCP2122 is at 9600 baud for a single TX low bit. In this case the TXIR is high for 3.55 µs.

TABLE 2-4: TXIR HIGH PULSE WIDTH

|              | TXIR Pul              | se Width                                 |                           |  |  |

|--------------|-----------------------|------------------------------------------|---------------------------|--|--|

| Baud<br>Rate | 3xT <sub>16XCLK</sub> | Pulse<br>Width<br>Limiter <sup>(2)</sup> | Comment                   |  |  |

| 9600         | 19.53 µs              | 4.00 µs                                  | Note 1                    |  |  |

| 19200        | 9.77 µs               | 4.00 µs                                  | Note 1                    |  |  |

| 38400        | 4.88 µs               | 4.00 µs                                  | Note 1                    |  |  |

| 46875        | 4.00 μs               | 4.00 µs                                  | Target Crossover<br>Point |  |  |

| 57600        | 3.26 µs               | 4.00 µs                                  |                           |  |  |

| 115200       | 1.63 µs               | 4.00 µs                                  |                           |  |  |

- **Note 1:** The pulse width limiter on the TXIR pin saves system current for this baud rate.

- 2: This TXIR pulse width time is a design target and is not tested. Actual times may be greater than or less than this value.

FIGURE 2-9: MCP2122 AT 115200 BAUD WAVEFORM

Control 11:41 AM <u>F</u>ile Setup: <u>M</u>easure <u>A</u>nalyze <u>U</u>tilities <u>H</u>elp **□** 100 MSa/s 16XCLK \$ TXIR Markers Scales H 20.0 µs/div 🕠 🗸 📘 -99.450000 дз T 2.50 V 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 ← 16XCLK Pulse A B Jitter of the TX input relative to the 16XCLK and TXIR

FIGURE 2-10: MCP2122 AT 9600 BAUD WAVEFORM

### 2.6 Host UART Interface

The UART interface is used to communicate with the host controller. Though a UART is capable of a full-duplex interface, the direct coupling to the IR encoder/decoder allows only half-duplex operation (since the IR side is either receiving or transmitting and not both at the same time). This means that the system can not transmit and receive at the same time.

#### 2.6.1 TRANSMITTING

When the controller sends serial data to the MCP2122, the baud rates are required to match.

There will be some jitter on the detection of the high to low edge of the start bit. This jitter will affect the placement of the encoded start bit. All subsequent bits will be 16 BITCLK times later.

While RXIR is receiving data (low pulse), the TXIR pin is disabled from transmitting.

### 2.6.2 RECEIVING

When the controller receives serial data from the MCP2122, the baud rates are required to match.

There will be some jitter on the detection of the high-tolow edge of the Start bit. This jitter will affect the placement of the decoded Start bit. All subsequent bits will be 16 BITCLK times later.

The TXIR pin is disabled when data is being received (low pulse) on the RXIR pin.

### 2.7 IR Interface

The IR interface is used to communicate with the optical receiver circuitry. The IR interface is either transmitting data or receiving data (half-duplex).

## 2.8 Encoding/Decoding Jitter and Offset

Figure 2-11 shows the jitter on the RXIR and TX pins, and the offset on the RX pin and the TXIR pin.

Jitter is the possible variation of the desired edge. Figure 2-9 and Figure 2-10 show the jitter of the TX pin (range is indicated by red dashed lines).

Offset is the propagation delay of the input signal (RXIR or TX) to the output signal (RX or TXIR). Figure 2-9 and Figure 2-10 show the offset of the TXIR pin from the 16XCLK signal that starts the bit time.

### 2.9 Minimizing Power

The device can be placed in a Low Power mode by forcing the RESET pin low. This disables the internal state machine. To ensure that the lowest power consumption is obtained, ensure that the 16XCLK pin is not active and that the other input pins (TX and RXIR) are at a logic-high or logic-low level.

### 2.9.1 RETURNING TO OPERATION

When returning to normal operation, the RESET pin must be forced high and the 16XCLK signal should be operating. Time should be given to ensure that the 16XCLK is stabilized at the desired frequency before data is allowed to be transmitted or received.

FIGURE 2-11: EFFECTS OF JITTER AND OFFSET

### 3.0 DEVELOPMENT TOOLS

There are currently no development tools for the MCP2122. A demo board is scheduled to be available soon.

#### 4.0 **ELECTRICAL CHARACTERISTICS**

### **Absolute Maximum Ratings†**

| Ambient Temperature under bias                      | 40°C to +125°C |

|-----------------------------------------------------|----------------|

| Storage Temperature                                 | 65°C to +150°C |

| Voltage on VDD with respect to Vss                  | 0.3V to +6.5V  |

| Voltage on RESET with respect to Vss                | 0.3V to +14V   |

| Voltage on all other pins with respect to Vss       |                |

| Total Power Dissipation <sup>(1)</sup>              | 800 mW         |

| Max. Current out of Vss pin                         | 500 mA         |

| Max. Current into VDD pin                           | 500 mA         |

| Input Clamp Current, IIK (VI < 0 or VI > VDD)       | ±20 mA         |

| Output Clamp Current, IOK (V0 < 0 or V0 > VDD)      | ±20 mA         |

| Max. Output Current sunk by any Output pin          | 25 mA          |

| Max. Output Current sourced by any Output pin       | 25 mA          |

| Note 1: Power Dissipation is calculated as follows: |                |

PDIS = VDD x {IDD -  $\sum$  IOH} +  $\sum$  {(VDD-VOH) x IOH} +  $\sum$ (VOL x IOL)

<sup>†</sup>NOTICE: Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

### 4.1 DC Characteristics

| DC Characteristics |     |                                           | Standard Operating Conditions (unless otherwise specified) Operating Temperature: -40°C ≤ TA ≤ +125°C (Extended) |                    |     |       |                                                          |  |

|--------------------|-----|-------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|----------------------------------------------------------|--|

| Param.<br>No.      | Sym | Characteristic                            | Min                                                                                                              | Typ <sup>(1)</sup> | Max | Units | Conditions                                               |  |

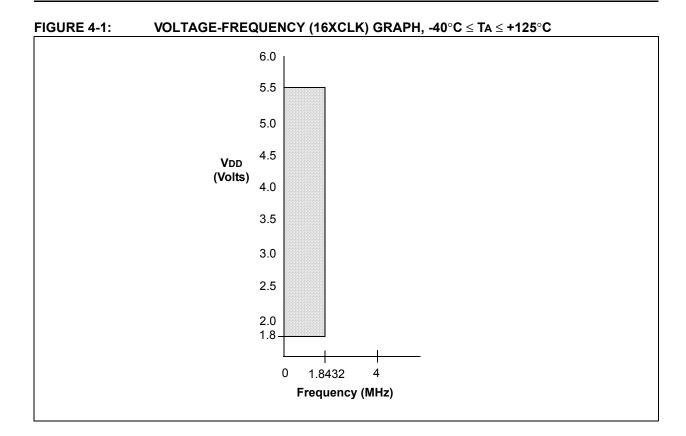

| D001               | VDD | Supply Voltage                            | 1.8                                                                                                              | _                  | 5.5 | V     | See Figure 4-1                                           |  |

| D010               | IDD | Supply Current (2)                        | _                                                                                                                | 0.1                | 1   | mA    | Fosc = 1.8432 MHz, VDD = 5.5V<br>(TX = H, RXIR = H)      |  |

|                    |     |                                           |                                                                                                                  |                    |     |       | Transmitter (TX = L, RXIR = H)                           |  |

|                    |     |                                           | _                                                                                                                | _                  | 300 | μΑ    | Fosc = 1.8432 MHz, V <sub>DD</sub> = 1.8V <sup>(4)</sup> |  |

|                    |     |                                           | _                                                                                                                |                    | 1   | mA    | Fosc = 1.8432 MHz, VDD = 5.5V                            |  |

|                    |     |                                           |                                                                                                                  |                    |     |       | Receiver (RXIR = L, TX = H)                              |  |

|                    |     |                                           | _                                                                                                                | _                  | 500 | μΑ    | Fosc = 1.8432 MHz, VDD = 1.8V (4)                        |  |

|                    |     |                                           | _                                                                                                                | _                  | 2   | mA    | Fosc = 1.8432 MHz, VDD = 5.5V                            |  |

| D020               | IPD | Device Disabled<br>Current <sup>(3)</sup> | _                                                                                                                | _                  | 2   | μΑ    | VDD = 1.8V <sup>(4)</sup>                                |  |

|                    |     |                                           | _                                                                                                                | _                  | 4   | μΑ    | VDD = 5.5V                                               |  |

- **Note 1:** Data in the Typical ("Typ") column is based on characterization results at +25°C. This data is for design guidance only and is not tested.

- **2:** The supply current is mainly a function of the operating voltage and frequency. Pin loading, pin rate and temperature have an impact on the current consumption.

- a)The test conditions for all IDD measurements are:

16XCLK = external square wave, from rail-to-rail; TX = Vss, RXIR = Vss, RESET = VDD.

- **3:** The device disable current is mainly a function of the operating voltage. Temperature also has an impact on the current consumption. When the device is disabled (RESET = Vss). The test conditions for all IDD measurements are:

- 16XCLK = external square wave, from rail-to-rail; TX = Vss, RXIR = VDD, RESET = Vss; The output pins are driving a high or low level into infinite impedance.

- **4:** These parameters (shaded) are characterized but are not tested. These values should be used for design guidance only.

© 2004 Microchip Technology Inc. Preliminary DS21894A-page 15

### **DC Characteristics** (Continued)

| DC CHAI      | RACTER | ISTICS                                     | Standard Operating Conditions (unless otherwise specified) Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$ (extended) Operating voltage VDD range as described in DC spec, Section 4.1 "DC Characteristics". |                    |         |       |                                            |  |  |

|--------------|--------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------|-------|--------------------------------------------|--|--|

| Param<br>No. | Sym    | Characteristic                             | Min                                                                                                                                                                                                                                             | Typ <sup>(1)</sup> | Max     | Units | Conditions                                 |  |  |

|              | VIL    | Input Low Voltage Input pins               |                                                                                                                                                                                                                                                 |                    |         |       |                                            |  |  |

| D031         |        | TX, RXIR                                   | Vss                                                                                                                                                                                                                                             | _                  | 0.2 VDD | V     |                                            |  |  |

| D032         |        | RESET                                      | Vss                                                                                                                                                                                                                                             | _                  | 0.2 VDD | V     |                                            |  |  |

| D033         |        | 16XCLK                                     | Vss                                                                                                                                                                                                                                             | _                  | 0.2 VDD | V     |                                            |  |  |

|              | VIH    | Input High Voltage                         |                                                                                                                                                                                                                                                 |                    |         |       |                                            |  |  |

|              |        | Input pins                                 |                                                                                                                                                                                                                                                 | _                  |         |       |                                            |  |  |

| D041         |        | TX, RXIR                                   | 0.8 VDD                                                                                                                                                                                                                                         | _                  | VDD     | V     |                                            |  |  |

| D042         |        | RESET                                      | 0.8 VDD                                                                                                                                                                                                                                         | _                  | VDD     | V     |                                            |  |  |

| D043         |        | 16XCLK                                     | 0.8 VDD                                                                                                                                                                                                                                         |                    | VDD     | V     |                                            |  |  |

|              | lıL    | Input Leakage<br>Current <sup>(2, 3)</sup> |                                                                                                                                                                                                                                                 |                    |         |       |                                            |  |  |

| D060A        |        | TX, and 16XCLK                             | _                                                                                                                                                                                                                                               | _                  | ±1      | μΑ    | Vss ≤ Vpin ≤ Vdd,<br>Pin at high-impedance |  |  |

| D061         |        | RESET                                      | _                                                                                                                                                                                                                                               | _                  | ±1      | μΑ    | Vss ≤ Vpin ≤ Vdd                           |  |  |

| D060B        | Iн     | RXIR                                       | _                                                                                                                                                                                                                                               | _                  | ±1      | μΑ    | VDD = 5.5V, VRXIR = VDD                    |  |  |

**Note 1:** Data in the Typical ("Typ") column is based on characterization results at +25°C. This data is for design guidance only and is not tested.

<sup>2:</sup> The leakage current on the RESET pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

<sup>3:</sup> Negative current is defined as coming out of the pin.

### **DC Characteristics** (Continued)

| DC CHARACTERISTICS           |      |                                         | Standard Operating Conditions (unless otherwise specified) Operating temperature: $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$ (Extended) Operating voltage VDD range as described in DC spec, Section 4.1 "DC Characteristics". |                    |     |       |                           |

|------------------------------|------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|---------------------------|

| Param No. Sym Characteristic |      |                                         | Min                                                                                                                                                                                                                                              | Typ <sup>(1)</sup> | Max | Units | Conditions                |

|                              | Vol  | Output Low Voltage                      |                                                                                                                                                                                                                                                  |                    |     |       |                           |

| D080B                        |      | RX                                      | _                                                                                                                                                                                                                                                | _                  | 0.6 | V     | IOL = 2 mA, VDD = 1.8V    |

| D081                         |      | TXIR                                    | _                                                                                                                                                                                                                                                | _                  | 0.6 | V     | IOL = 2 mA, VDD = 1.8V    |

|                              | Vон  | Output High Voltage                     |                                                                                                                                                                                                                                                  |                    |     |       |                           |

| D090B                        |      | RX <sup>(2)</sup>                       | VDD - 0.7                                                                                                                                                                                                                                        | _                  | _   | V     | IOH = -0.8 mA, VDD = 1.8V |

| D091                         |      | TXIR (2)                                | VDD - 0.7                                                                                                                                                                                                                                        | _                  | _   | V     | IOH = -0.8 mA, VDD = 1.8V |

|                              |      | Capacitive Loading Specs on Output Pins |                                                                                                                                                                                                                                                  |                    |     |       |                           |

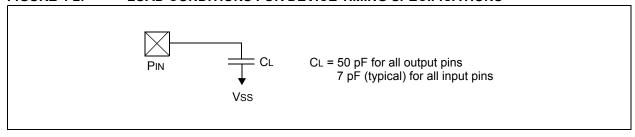

| D101A                        | Cout | All Output pins                         | –                                                                                                                                                                                                                                                | _                  | 50  | pF    |                           |

| D101B                        | CIN  | All Input pins                          | _                                                                                                                                                                                                                                                | 7                  | _   | pF    | TA = +25°C, Fc = 1.0 MHz  |

Note 1: Data in the Typical ("Typ") column is based on characterization results at +25°C. This data is for design guidance only and is not tested.

<sup>2:</sup> Negative current is defined as coming out of the pin.

### 4.2 Timing Parameter Symbology and Load Conditions

The timing parameter symbols have been created following one of the following formats:

### 4.2.1 TIMING CONDITIONS

The temperature and voltages specified in Table 4-2 apply to all timing specifications unless otherwise noted. Figure 4-2 specifies the load conditions for the timing specifications.

TABLE 4-1: SYMBOLOGY

| 1. TppS2pp | S                                   | 2. TppS |                |

|------------|-------------------------------------|---------|----------------|

| T          |                                     |         |                |

| F          | Frequency                           | Т       | Time           |

| Е          | Error                               |         |                |

| Lowercas   | se letters (pp) and their meanings: |         |                |

| pp         |                                     |         |                |

| io         | Input or Output pin                 | xclk    | Oscillator     |

| rx         | Receive                             | tx      | Transmit       |

| bitclk     | RX/TX BITCLK                        | RST     | Reset          |

| Uppercas   | se letters and their meanings:      |         |                |

| S          |                                     |         |                |

| F          | Fall                                | Р       | Period         |

| Н          | High                                | R       | Rise           |

| 1          | Invalid (Hi-impedance)              | V       | Valid          |

| L          | Low                                 | Z       | High-impedance |

### TABLE 4-2: AC TEMPERATURE AND VOLTAGE SPECIFICATIONS

| AC CHARACTERISTICS | Standard Operating Conditions (unless otherwise stated)  Operating temperature: $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ (Extended)  Operating voltage VDD range as described in DC spec,  Section 4.1 "DC Characteristics". |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

### FIGURE 4-2: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

### 4.3 Timing Diagrams and Specifications

FIGURE 4-3: EXTERNAL CLOCK TIMING

TABLE 4-3: EXTERNAL CLOCK TIMING REQUIREMENTS

| AC Cha        | racteristic       | s                                                     | Standard Operating Conditions (unless otherwise specified) Operating Temperature: $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$ (Extended) Operating Voltage VDD range is described in Section 4.1 "DC Characteristics" |   |        |     |        |

|---------------|-------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--------|-----|--------|

| Param.<br>No. | Conditions        |                                                       |                                                                                                                                                                                                                                        |   |        |     |        |

| 1             | TXCLK             | External 16XCLK Period (2, 3)                         | 542.5                                                                                                                                                                                                                                  | _ | _      | ns  |        |

| 1A            | Fxclk             | External 16XCLK<br>Frequency <sup>(2, 3)</sup>        | DC                                                                                                                                                                                                                                     | _ | 1.8432 | MHz |        |

| 1C            | Exclk             | Clock Error (4, 5)                                    | _                                                                                                                                                                                                                                      | _ | ±2     | %   | Note 5 |

| 3             | ,                 | Clock in (16XCLK)<br>Low or High Time                 | 50                                                                                                                                                                                                                                     | _ | _      | ns  |        |

| 4             | TXCLKR,<br>TXCLKF | Clock in (16XCLK)<br>Rise or Fall Time <sup>(5)</sup> | _                                                                                                                                                                                                                                      | _ | 7.5    | ns  | Note 5 |

**Note 1:** Data in the Typical ("Typ") column is at 5V, +25°C, unless otherwise stated. These parameters are for design guidance only and are not tested.

- 2: All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption.

When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

- **3:** A duty cycle of no more than 60/40 (High Time/Low Time or Low Time/High Time) is recommended for external clock inputs.

- **4:** This is the clock error from the desired clock frequency. The total system clock error includes the error from the transmitter and the error of receiver (from the desired clock frequency). If the transmitter is 2% fast from the target frequency and the receiver is 2% slow from the target frequency, then the total error is 4%.

- **5:** These parameters (shaded) are characterized but are not tested. These values should be used for design guidance only.

© 2004 Microchip Technology Inc. Preliminary DS21894A-page 19

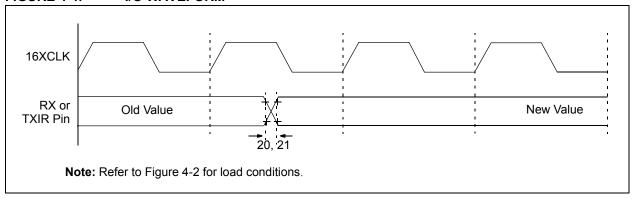

### FIGURE 4-4: I/O WAVEFORM

TABLE 4-4: I/O TIMING REQUIREMENTS

| AC Characteristics |     |                           | Standard Operating Conditions (unless otherwise specified) Operating Temperature: $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ (Extended) Operating Voltage VDD range is described in Section 4.1 "DC Characteristics" |    |    |    |                                          |  |  |

|--------------------|-----|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|----|------------------------------------------|--|--|

| Param.<br>No.      | Sym | Characteristic            | Min Typ (1) Max Units Conditions                                                                                                                                                                                                       |    |    |    |                                          |  |  |

| 20A                | ToR | RX pin rise time (2, 3)   | _                                                                                                                                                                                                                                      | 10 | 25 | ns | V <sub>DD</sub> ≥ 2.7V ( <b>Note 3</b> ) |  |  |

| 20B                |     |                           | _                                                                                                                                                                                                                                      | 10 | 60 | ns | VDD = 1.8V (Note 3)                      |  |  |

| 20C                |     | TXIR pin rise time (2, 3) | -                                                                                                                                                                                                                                      | 10 | 25 | ns | VDD ≥ 2.7V ( <b>Note 3</b> )             |  |  |

| 20D                |     |                           |                                                                                                                                                                                                                                        | 10 | 60 | ns | VDD = 1.8V (Note 3)                      |  |  |

| 21A                | ToF | RX pin fall time (2, 3)   | _                                                                                                                                                                                                                                      | 10 | 35 | ns | Note 3                                   |  |  |

| 21C                |     | TXIR pin fall time (2, 3) | _                                                                                                                                                                                                                                      | 10 | 25 | ns | Note 3                                   |  |  |

**Note 1:** Data in the Typical ("Typ") column is at 5V, +25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- 2: See Figure 4-2 for loading conditions.

- **3:** These parameters (shaded) are characterized but are not tested. These values should be used for design guidance only.

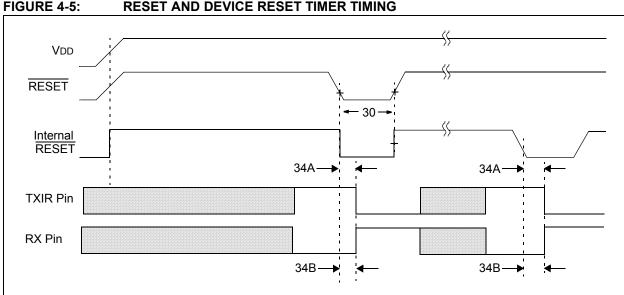

**RESET AND DEVICE RESET TIMER TIMING** FIGURE 4-5:

**RESET AND DEVICE RESET TIMER REQUIREMENTS TABLE 4-5**:

| AC Chai       | racteristic | s                                               | Standard Operating Conditions (unless otherwise specified) Operating Temperature: $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ (Extended) Operating Voltage VDD range is described in Section 4.1 "DC Characteristics". |                    |     |       |             |

|---------------|-------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|-------------|

| Param.<br>No. | Sym         | Characteristic                                  | Min                                                                                                                                                                                                                                     | Typ <sup>(1)</sup> | Max | Units | Conditions  |

| 30            | TRSTL       | RESET Pulse Width (low)                         | 2000                                                                                                                                                                                                                                    | _                  |     | ns    | VDD = 5.0 V |

| 34A           | Tod         | Default output state of TXIR pin from RESET Low | _                                                                                                                                                                                                                                       |                    | 2   | μs    |             |

| 34B           | Tod         | Default output state of RX pins from RESET Low  | _                                                                                                                                                                                                                                       | _                  | 2   | μs    |             |

**Note 1:** Data in the Typical ("Typ") column is at 5V, +25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Preliminary** © 2004 Microchip Technology Inc. DS21894A-page 21

FIGURE 4-6: TX AND TXIR WAVEFORMS

TABLE 4-6: TX AND TXIR REQUIREMENTS

| AC Chai       | racteristics |                                                                                    | Standard Operating Conditions (unless otherwise specified)<br>Operating Temperature: $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$ (Extended)<br>Operating Voltage VDD range is described in<br><b>Section 4.1 "DC Characteristics"</b> . |                    |     |       |                       |  |

|---------------|--------------|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|-----------------------|--|

| Param.<br>No. | Sym          | Characteristic                                                                     | Min                                                                                                                                                                                                                                                      | Typ <sup>(1)</sup> | Max | Units | Conditions            |  |

| IR100A        | Ттхвіт       | Transmit Baud Rate                                                                 | _                                                                                                                                                                                                                                                        | 16                 |     | TXCLK |                       |  |

| IR100B        | TTXIRBIT     | Transmit Baud Rate                                                                 | 16                                                                                                                                                                                                                                                       |                    | 16  | TXCLK |                       |  |

| IR102A        | Етхвіт       | Host UART TX Error                                                                 | _                                                                                                                                                                                                                                                        | _                  | ± 2 | %     | Note 2, 3             |  |

| IR102B        | ETXIRBIT     | TXIR Error from 16XCLK                                                             | _                                                                                                                                                                                                                                                        | 0                  | l   | %     | Note 2, 4             |  |

| IR113         | TTXRF        | TX pin rise time and fall time                                                     | _                                                                                                                                                                                                                                                        |                    | 25  | ns    | Note 2                |  |

| IR114         | TtxpdirJ     | 16XCLK to TX jitter                                                                | _                                                                                                                                                                                                                                                        | _                  | 1   | TXCLK | Note 2                |  |

| IR120         | TTXL2TXIRH   | TX falling edge ( $\downarrow$ ) to TXIR rising edge ( $\uparrow$ ) <sup>(1)</sup> | 7                                                                                                                                                                                                                                                        |                    | 8   | TXCLK |                       |  |

| IR121A        | TTXIRPW      | TXIR pulse width                                                                   | 3                                                                                                                                                                                                                                                        | _                  | 3   | TXCLK | At 115200 baud        |  |

| IR121B        |              |                                                                                    | 1.41                                                                                                                                                                                                                                                     | 3.5                | 5   | μs    | At 9600 baud (Note 5) |  |

| IR122         | TTXIRP       | TXIR bit period (1)                                                                | _                                                                                                                                                                                                                                                        | 16                 |     | TXCLK |                       |  |

| IR123         | TTXIRRF      | TXIR pin rise time and fall time                                                   | _                                                                                                                                                                                                                                                        | _                  | 10  | ns    | 50 pF load (Note 2)   |  |

**Note 1:** Data in the Typical ("Typ") column is at 5V, +25°C, unless otherwise stated. These parameters are for design guidance only and are not tested.

- **2:** These parameters (shaded) are characterized but are not tested. These values should be used for design guidance only.

- **3:** The TX pin operation may be asynchronous to the 16XCLK pin. This is the error from the desired baud rate for the system.

- **4:** The TXIR pin operation is synchronous to the 16XCLK pin. Any error present on the 16XCLK pin (Parameter 1C) will be refelected on the TXIR pin.

- 5: This specification is not tested. This value is from the design target.

**16XCLK AND THE TX AND TXIR WAVEFORMS**

**TABLE 4-7: TX AND TXIR REQUIREMENTS**

| AC Cha        | racteristics |                                                                                    | Standard Operating Conditions (unless otherwise specified) Operating Temperature: $-40^{\circ}C \le TA \le +125^{\circ}C$ (Extended) Operating Voltage VDD range is described in <b>Section 4.1 "DC Characteristics"</b> . |     |            |       |                              |  |

|---------------|--------------|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------|-------|------------------------------|--|

| Param.<br>No. | Symbol       | Characteristic                                                                     | Conditions                                                                                                                                                                                                                 |     |            |       |                              |  |

| IR113         | TTXRF        | TX pin rise time and fall time                                                     | _                                                                                                                                                                                                                          | _   | 25         | ns    | Note 2                       |  |

| IR114         | T⊤xJ         | TX to 16XCLK jitter                                                                | _                                                                                                                                                                                                                          |     | 1          | TXCLK | Note 2                       |  |

| IR120         | TTXL2TXIRH   | TX falling edge ( $\downarrow$ ) to TXIR rising edge ( $\uparrow$ ) <sup>(1)</sup> | 7                                                                                                                                                                                                                          |     | 8          | TXCLK |                              |  |

|               | TTXIRPW      | TXIR pulse width                                                                   | Smaller of                                                                                                                                                                                                                 |     | Smaller of |       |                              |  |

| IR121A        |              |                                                                                    | 3                                                                                                                                                                                                                          | _   | 3          | TXCLK | At 115200 baud               |  |

| IR121B        |              |                                                                                    | 1.41                                                                                                                                                                                                                       | 3.5 | 5          | μs    | At 9600 baud (Note 3)        |  |

| IR122         | TTXIRP       | TXIR bit period                                                                    | _                                                                                                                                                                                                                          | 16  |            | TXCLK |                              |  |

| 20C           | TTXIRR       | TXIR pin rise time                                                                 | _                                                                                                                                                                                                                          | 10  | 25         | ns    | VDD ≥ 2.7V ( <b>Note 2</b> ) |  |

| 20D           |              |                                                                                    | _                                                                                                                                                                                                                          | 10  | 60         | ns    | VDD = 1.8V (Note 2)          |  |

| 21C           | TTXIRF       | TXIR pin fall time                                                                 | _                                                                                                                                                                                                                          | 10  | 25         | ns    | Note 2                       |  |

Note 1: Data in the Typical ("Typ") column is at 5V, +25°C, unless otherwise stated. These parameters are for design guidance only and are not tested.

- 2: These parameters (shaded) are characterized but are not tested. These values should be used for design guidance only.

- 3: This specification is not tested. This value is from the design target

**Preliminary** © 2004 Microchip Technology Inc. DS21894A-page 23

FIGURE 4-8: RXIR AND RX WAVEFORMS

TABLE 4-8: RXIR REQUIREMENTS

| AC Cha        | racteristics |                                                                         | Standard Operating Conditions (unless otherwise specified) Operating Temperature: $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ (Extended) Operating Voltage VDD range is described in <b>Section 4.1 "DC Characteristics"</b> . |    |         |       |                 |  |

|---------------|--------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|---------|-------|-----------------|--|

| Param.<br>No. | Sym          | Characteristic                                                          | Conditions                                                                                                                                                                                                                                      |    |         |       |                 |  |

| IR101A        | ERXIRBIT     | RXIR Error                                                              | _                                                                                                                                                                                                                                               | _  | ± 2     | %     | Note 2, 3       |  |

| IR101B        | ERXBIT       | Host UART RX Error                                                      | _                                                                                                                                                                                                                                               | 0  | 1       | %     | Note 2, 4       |  |

| IR103         | TTXRF        | RX pin rise time and fall time                                          | _                                                                                                                                                                                                                                               |    | 25      | ns    |                 |  |

| IR110         | TRXBIT       | Receive (RX pin) Bit Rate                                               | 16                                                                                                                                                                                                                                              | 1  | 16      | TXCLK |                 |  |

| IR130         | TRXIRL2RXH   | RXIR Low AND 16XCLK                                                     | _                                                                                                                                                                                                                                               | 4  | 1       | TXCLK | At 115,200 baud |  |

|               |              | edge ( $\downarrow$ or $\uparrow$ ) to RX falling edge ( $\downarrow$ ) | _                                                                                                                                                                                                                                               | 3  |         | Txclk | At 9600 baud    |  |

| IR131A        | TRXIRPW      | RXIR pulse width                                                        | 1.41                                                                                                                                                                                                                                            |    | 3 TXCLK | μs    |                 |  |

| IR132         | TRXIRP       | RXIR bit period (1)                                                     | _                                                                                                                                                                                                                                               | 16 |         | TXCLK |                 |  |

| IR133         | TRXIRJ       | 16XCLK to RXIR jitter                                                   | _                                                                                                                                                                                                                                               | _  | 1       | TXCLK | Note 2          |  |

| IR134         | TRXSKW       | 16XCLK to RX skew                                                       | _                                                                                                                                                                                                                                               |    | 2.5     | μs    |                 |  |

| IR135         | TRXPDFIL     | RXIR Filter                                                             | 0.7                                                                                                                                                                                                                                             |    | 1.4     | μs    | Note 5          |  |

- **Note 1:** Data in the Typical ("Typ") column is at 5V, +25°C, unless otherwise stated. These parameters are for design guidance only and are not tested.

- 2: These parameters (shaded) are characterized but are not tested. These values should be used for design guidance only.

- **3:** The RXIR pin operation is asynchronous to the 16XCLK pin. This is the error from the desired baud rate for the system.

- **4:** The RX pin operation is synchronous to the 16XCLK pin. Any error present on the 16XCLK pin (Parameter 1C) will be refelected on the RX pin.

- 5: The minimum specification ensures that ALL pulses less then this pulse width are rejected, the maximum specification ensures that ALL pulses greater than this pulse width are never rejected, and pulse widths between these may or may not be rejected.

### 5.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES

The graphs and tables are not available at this time

© 2004 Microchip Technology Inc. **Preliminary** DS21894A-page 25

NOTES:

### 6.0 PACKAGING INFORMATION

### 6.1 Package Marking Information

## 8-Lead PDIP (300 mil)

### Example:

### 8-Lead SOIC (150 mil)

### Example:

Legend: XX...X Customer specific information\*

Y Year code (last digit of calendar year)

YY Year code (last 2 digits of calendar year)

WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

**Note**: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line thus limiting the number of available characters for customer specific information.

\* Standard device marking consists of Microchip part number, year code, week code, and traceability code..

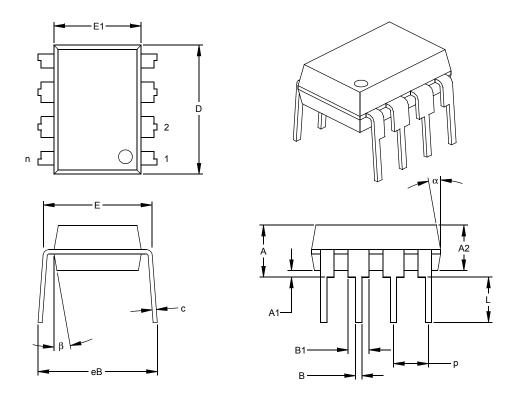

## 8-Lead Plastic Dual In-line (P) - 300 mil Body (PDIP)

|                            | Units  |      | INCHES* |      | MILLIMETERS |      |       |

|----------------------------|--------|------|---------|------|-------------|------|-------|

| Dimension                  | Limits | MIN  | NOM     | MAX  | MIN         | NOM  | MAX   |

| Number of Pins             | n      |      | 8       |      |             | 8    |       |

| Pitch                      | р      |      | .100    |      |             | 2.54 |       |

| Top to Seating Plane       | Α      | .140 | .155    | .170 | 3.56        | 3.94 | 4.32  |

| Molded Package Thickness   | A2     | .115 | .130    | .145 | 2.92        | 3.30 | 3.68  |

| Base to Seating Plane      | A1     | .015 |         |      | 0.38        |      |       |

| Shoulder to Shoulder Width | Е      | .300 | .313    | .325 | 7.62        | 7.94 | 8.26  |

| Molded Package Width       | E1     | .240 | .250    | .260 | 6.10        | 6.35 | 6.60  |

| Overall Length             | D      | .360 | .373    | .385 | 9.14        | 9.46 | 9.78  |

| Tip to Seating Plane       | L      | .125 | .130    | .135 | 3.18        | 3.30 | 3.43  |

| Lead Thickness             | С      | .008 | .012    | .015 | 0.20        | 0.29 | 0.38  |

| Upper Lead Width           | B1     | .045 | .058    | .070 | 1.14        | 1.46 | 1.78  |

| Lower Lead Width           | В      | .014 | .018    | .022 | 0.36        | 0.46 | 0.56  |

| Overall Row Spacing §      | eB     | .310 | .370    | .430 | 7.87        | 9.40 | 10.92 |

| Mold Draft Angle Top       | α      | 5    | 10      | 15   | 5           | 10   | 15    |

| Mold Draft Angle Bottom    | β      | 5    | 10      | 15   | 5           | 10   | 15    |

Notes: Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

.010" (0.254mm) per side. JEDEC Equivalent: MS-001 Drawing No. C04-018

<sup>\*</sup> Controlling Parameter § Significant Characteristic

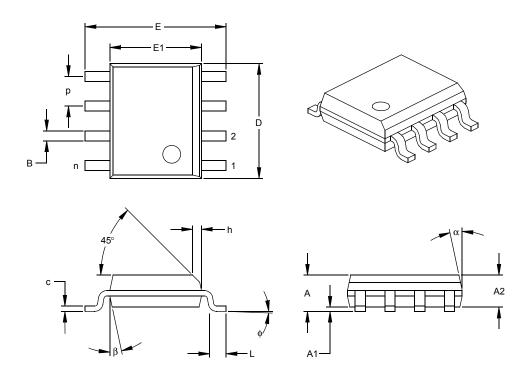

## 8-Lead Plastic Small Outline (SN) - Narrow, 150 mil Body (SOIC)

|                          |        | INCHES* |      | MILLIMETERS |      |      |      |

|--------------------------|--------|---------|------|-------------|------|------|------|

| Dimensior                | Limits | MIN     | NOM  | MAX         | MIN  | NOM  | MAX  |

| Number of Pins           | n      |         | 8    |             |      | 8    |      |

| Pitch                    | р      |         | .050 |             |      | 1.27 |      |

| Overall Height           | Α      | .053    | .061 | .069        | 1.35 | 1.55 | 1.75 |

| Molded Package Thickness | A2     | .052    | .056 | .061        | 1.32 | 1.42 | 1.55 |

| Standoff §               | A1     | .004    | .007 | .010        | 0.10 | 0.18 | 0.25 |

| Overall Width            | Е      | .228    | .237 | .244        | 5.79 | 6.02 | 6.20 |

| Molded Package Width     | E1     | .146    | .154 | .157        | 3.71 | 3.91 | 3.99 |

| Overall Length           | D      | .189    | .193 | .197        | 4.80 | 4.90 | 5.00 |

| Chamfer Distance         | h      | .010    | .015 | .020        | 0.25 | 0.38 | 0.51 |

| Foot Length              | L      | .019    | .025 | .030        | 0.48 | 0.62 | 0.76 |

| Foot Angle               | ф      | 0       | 4    | 8           | 0    | 4    | 8    |

| Lead Thickness           | С      | .008    | .009 | .010        | 0.20 | 0.23 | 0.25 |

| Lead Width               | В      | .013    | .017 | .020        | 0.33 | 0.42 | 0.51 |

| Mold Draft Angle Top     | α      | 0       | 12   | 15          | 0    | 12   | 15   |

| Mold Draft Angle Bottom  | β      | 0       | 12   | 15          | 0    | 12   | 15   |

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed

.010" (0.254mm) per side.

JEDEC Equivalent: MS-012

Drawing No. C04-057

<sup>\*</sup> Controlling Parameter § Significant Characteristic

NOTES:

### PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.          | <u> </u>    |         | <u>/XX</u>     | <u>X</u>                                          | Exa | mples:          |                                                                  |

|-------------------|-------------|---------|----------------|---------------------------------------------------|-----|-----------------|------------------------------------------------------------------|

| <br>  Device Tem  | <br>nperati | ıre     | <br>Package    | <br>Lead Finish                                   | a)  | MCP2122-E/PG:   | Extended Temperature,<br>PDIP package, Pb-free                   |

| F                 | Range       |         |                |                                                   | b)  | MCP2122-E/SNG:  | Extended Temperature,<br>SOIC package, Pb-free                   |

| Device            | MCP2        | 122: li | nfrared Encode | er/Decoder                                        | c)  | MCP2122T-E/SNG: | Tape and Reel,<br>Extended Temperature,<br>SOIC package. Pb-free |