# TECHNICAL MANUAL

LSIFC929X Dual Channel Fibre Channel I/O Processor

June 2003 Version 2.0

www.DataSheet4U.com DB14-000202-01 This document contains proprietary information of LSI Logic Corporation. The information contained herein is not to be used by or disclosed to third parties without the express written permission of an officer of LSI Logic Corporation.

LSI Logic products are not intended for use in life-support appliances, devices, or systems. Use of any LSI Logic product in such applications without written consent of the appropriate LSI Logic officer is prohibited.

#### DB14-000202-01, June 2003

This document describes the LSI Logic Corporation LSIFC929X Dual Channel Fibre Channel I/O Processor and will remain the official reference source for all revisions/releases of this product until rescinded by an update.

LSI Logic Corporation reserves the right to make changes to any products herein at any time without notice. LSI Logic does not assume any responsibility or liability arising out of the application or use of any product described herein, except as expressly agreed to in writing by LSI Logic; nor does the purchase or use of a product from LSI Logic convey a license under any patent rights, copyrights, trademark rights, or any other of the intellectual property rights of LSI Logic or third parties.

Copyright © 2002, 2003 by LSI Logic Corporation. All rights reserved.

#### TRADEMARK ACKNOWLEDGMENT

LSI Logic, the LSI Logic logo design, Fusion-MPT, and GigaBlaze are trademarks or registered trademarks of LSI Logic Corporation. ARM is a registered trademark of ARM Ltd., used under license. All other brand and product names may be trademarks of their respective companies.

DB

To receive product literature, visit us at http://www.lsilogic.com.

For a current list of our distributors, sales offices, and design resource centers, view our web page located at

http://www.lsilogic.com/contacts/index.html

# Preface

This book is the primary reference and technical manual for the LSIFC929X Dual Channel Fibre Channel I/O Processor. It contains a complete functional description for the LSIFC929X and includes complete physical and electrical specifications for the product.

#### Audience

This document was prepared for logic designers and applications engineers and is intended to provide an overview of the LSI Logic LSIFC929X and to explain how to use the LSIFC929X in the initial stages of system design.

This document assumes that you have some familiarity with microprocessors and related support devices. The people who benefit from this book are

- engineers and managers who are evaluating the LSIFC929X for possible use in a system

- engineers who are designing the LSIFC929X into a system

#### Organization

This document has the following chapters and appendixes:

- Chapter 1, Introduction, provides a general description of the LSIFC929X.

- Chapter 2, Fibre Channel Overview, briefly describes some key elements of Fibre Channel, including layers, topologies, and classes of service.

- Chapter 3, LSIFC929X Overview, provides an introduction to the basic features of the LSIFC929X, including the message interface, protocol assist engines, and support components.

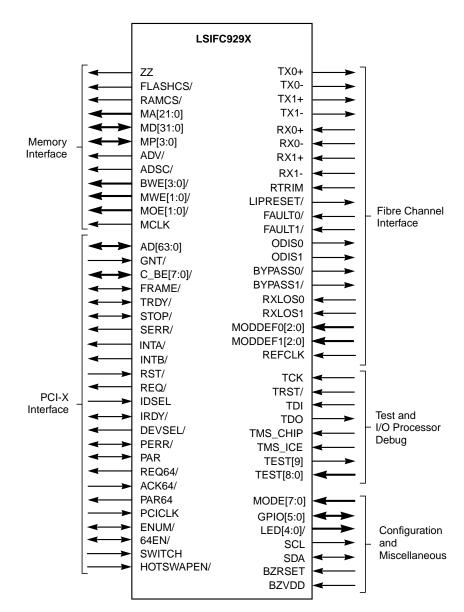

- Chapter 4, Signal Descriptions, lists and describes the signals on the LSIFC929X.

- Chapter 5, PCI-X Functional Description, describes the PCI-X features contained in the LSIFC929X.

- Chapter 6, **Registers**, briefly describes the PCI-X address space, the Configuration registers, and the Host Interface registers.

- Chapter 7, Specifications, describes the electrical specifications of the LSIFC929X, and provides pinout information and packaging dimensions.

- Appendix A, Register Summary, is a register summary.

- Appendix B, Reference Specifications, lists several specifications and applicable World Wide Web URLs that may benefit the reader.

- Appendix C, **Glossary of Terms and Abbreviations**, provides definitions for terms and abbreviations used in this manual.

#### **Related Publications**

*Fusion-MPT™ Message Passing Interface Specification, Volume 1.2,* Document No. DB14-000174-02

PCI Local Bus Specification, Version 2.2

PCI-X Addendum to the PCI Local Bus Specification, Version 1.0a

#### **Conventions Used in This Manual**

Preface

The word *assert* means to drive a signal true or active. The word *deassert* means to drive a signal false or inactive. Signals that are active LOW end in a "/."

Hexadecimal numbers are indicated by the prefix "0x" —for example, 0x32CF. Binary numbers are indicated by the prefix "0b" —for example, 0b0011.0010.1100.1111.

#### **Revision Record**

| Revision | Date   | Remarks                            |

|----------|--------|------------------------------------|

| 0.5      | 3/2002 | First Advance Information release. |

| 2.0      | 6/2003 | Final release.                     |

# Contents

| Introduction |                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1          | Overvi                                                                     | ew                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|              | 1.1.1                                                                      | Hardware Features                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|              | 1.1.2                                                                      | FC Features                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|              | 1.1.3                                                                      | Software Features                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|              | 1.1.4                                                                      | OS Support                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|              | 1.1.5                                                                      | Targeted Applications                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1.2          | Genera                                                                     | al Description                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|              | 1.2.1                                                                      | Multifunction PCI-X                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|              | 1.2.2                                                                      | Autospeed Negotiation                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|              | 1.2.3                                                                      | Autotopology Negotiation                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|              | 1.2.4                                                                      | Failover and Load Balancing                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1.3          | Hardw                                                                      | are Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|              | 1.3.1                                                                      | PCI/PCI-X Interface                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|              | 1.3.2                                                                      | 32-Bit Memory Controller                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|              | 1.3.3                                                                      | I/O Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|              | 1.3.4                                                                      | System Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|              | 1.3.5                                                                      | Integrated 2 Gbit/s Transceivers                                                                                                                                                                                                                                                                                                                                                                                                                                | 1-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|              | 1.3.6                                                                      | Link Controllers                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|              | 1.3.7                                                                      | Datapath                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|              | 1.3.8                                                                      | Context Managers                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1.4          | Initiato                                                                   | r Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1.5          | Target                                                                     | Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1.6          | Diagno                                                                     | ostics                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Fibr         | e Chann                                                                    | el Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2.1          | Introdu                                                                    | iction                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2.2          | FC La                                                                      | yers                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2.3          | Frame                                                                      | S                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|              | 1.1<br>1.2<br>1.3<br>1.3<br>1.4<br>1.5<br>1.6<br><b>Fibr</b><br>2.1<br>2.2 | 1.1       Overvi         1.1.1       1.1.2         1.1.3       1.1.3         1.1.4       1.1.5         1.2       Genera         1.2.1       1.2.2         1.2.3       1.2.4         1.3       Hardw         1.3.1       1.3.2         1.3.3       1.3.4         1.3.5       1.3.6         1.3.7       1.3.8         1.4       Initiato         1.5       Target         1.6       Diagno         Fibre Chann         2.1       Introdu         2.2       FC Lay | <ul> <li>1.1 Overview <ul> <li>1.1.1 Hardware Features</li> <li>1.1.2 FC Features</li> <li>1.1.3 Software Features</li> <li>1.1.3 Software Features</li> <li>1.1.4 OS Support</li> <li>1.1.5 Targeted Applications</li> </ul> </li> <li>1.2 General Description <ul> <li>1.2.1 Multifunction PCI-X</li> <li>1.2.2 Autospeed Negotiation</li> <li>1.2.3 Autotopology Negotiation</li> <li>1.2.4 Failover and Load Balancing</li> </ul> </li> <li>1.3 Hardware Overview <ul> <li>1.3.1 PCI/PCI-X Interface</li> <li>1.3.2 32-Bit Memory Controller</li> <li>1.3.3 I/O Processor</li> <li>1.3.4 System Interface</li> <li>1.3.5 Integrated 2 Gbit/s Transceivers</li> <li>1.3.6 Link Controllers</li> <li>1.3.7 Datapath</li> <li>1.3.8 Context Managers</li> </ul> </li> <li>1.4 Initiator Operations</li> <li>1.5 Target Operations</li> <li>1.6 Diagnostics</li> </ul> <li>Fibre Channel Overview <ul> <li>2.1 Introduction</li> <li>2.2 FC Layers</li> </ul></li> |

|           |      |            |                                  | www.DataSheet4U.com |

|-----------|------|------------|----------------------------------|---------------------|

|           | 2.4  | Exchang    | es                               | 2-5                 |

|           | 2.5  | FC Ports   | i                                | 2-7                 |

|           | 2.6  | FC Topo    | logies                           | 2-7                 |

|           |      | 2.6.1      | Point-to-Point Topology          | 2-8                 |

|           |      | 2.6.2      | Fabric Topology                  | 2-8                 |

|           |      | 2.6.3      | Arbitrated Loop Topology         | 2-8                 |

|           | 2.7  | Classes    | of Service                       | 2-9                 |

| Chapter 3 | LSIF | C929X Ov   | erview                           |                     |

|           | 3.1  | Introduct  | ion                              | 3-1                 |

|           | 3.2  | Message    | Interface                        | 3-3                 |

|           |      | 3.2.1      | Messages                         | 3-3                 |

|           |      | 3.2.2      | Message Flow                     | 3-4                 |

|           | 3.3  | SCSI Me    | essage                           | 3-6                 |

|           | 3.4  | LAN Mes    | ssage                            | 3-6                 |

|           | 3.5  | Target M   | essage                           | 3-8                 |

|           | 3.6  | Support    | Components                       | 3-8                 |

|           |      | 3.6.1      | SSRAM Memory                     | 3-9                 |

|           |      | 3.6.2      | Flash ROM                        | 3-10                |

|           |      | 3.6.3      | Serial EEPROM                    | 3-10                |

| Chapter 4 | Sign | al Descrip | tions                            |                     |

|           | 4.1  | PCI/PCI-   | X Interface                      | 4-3                 |

|           | 4.2  | Fibre Ch   | annel Interface                  | 4-7                 |

|           | 4.3  | Memory     | Interface                        | 4-10                |

|           | 4.4  | Configura  | ation and Miscellaneous          | 4-14                |

|           | 4.5  | Test and   | I/O Processor Debug              | 4-15                |

|           | 4.6  | Power ar   | nd Ground                        | 4-16                |

| Chapter 5 | PCI- | X Function | nal Description                  |                     |

|           | 5.1  | Overview   | /                                | 5-1                 |

|           | 5.2  | PCI-X Ad   | ddressing                        | 5-2                 |

|           |      | 5.2.1      | PCI Configuration Space          | 5-2                 |

|           |      | 5.2.2      | PCI I/O Space                    | 5-3                 |

|           |      | 5.2.3      | PCI Memory Space                 | 5-3                 |

|           | 5.3  | PCI/PCI-   | X Bus Commands and Implementatic | n 5-3               |

|           |      |            | www.DataSheet4                              | U.com |

|-----------|------|------------|---------------------------------------------|-------|

|           |      | 5.3.1      | Interrupt Acknowledge Command               | 5-5   |

|           |      | 5.3.2      | Special Cycle Command                       | 5-5   |

|           |      | 5.3.3      | I/O Read Command                            | 5-5   |

|           |      | 5.3.4      | I/O Write Command                           | 5-5   |

|           |      | 5.3.5      | Memory Read Command                         | 5-5   |

|           |      | 5.3.6      | Memory Read Dword Command                   | 5-5   |

|           |      | 5.3.7      | Memory Write Command                        | 5-6   |

|           |      | 5.3.8      | Alias to Memory Read Block Command          | 5-6   |

|           |      | 5.3.9      | Alias to Memory Write Block Command         | 5-6   |

|           |      | 5.3.10     | Configuration Read Command                  | 5-6   |

|           |      | 5.3.11     | Configuration Write Command                 | 5-6   |

|           |      | 5.3.12     | Memory Read Multiple Command                | 5-7   |

|           |      | 5.3.13     | Split Completion Command                    | 5-7   |

|           |      | 5.3.14     | Dual Address Cycles (DAC) Command           | 5-8   |

|           |      | 5.3.15     | Memory Read Line Command                    | 5-8   |

|           |      | 5.3.16     | Memory Read Block Command                   | 5-8   |

|           |      | 5.3.17     | Memory Write and Invalidate Command         | 5-8   |

|           |      | 5.3.18     | Memory Write Block Command                  | 5-9   |

|           | 5.4  | PCI Art    | pitration                                   | 5-9   |

|           | 5.5  | PCI Ca     | che Mode                                    | 5-9   |

| Chapter 6 | Regi | sters      |                                             |       |

|           | 6.1  |            | Configuration Space Register Description    | 6-2   |

|           | 6.2  | PCI I/O    | Space and Memory Space Register Description | 6-32  |

|           | 6.3  |            | Memory                                      | 6-44  |

| Chapter 7 | Spec | cification | S                                           |       |

|           | 7.1  |            | al Requirements                             | 7-2   |

|           | 7.2  | AC Tim     | ing                                         | 7-7   |

|           |      | 7.2.1      | PCI/PCI-X Interface Timings                 | 7-7   |

|           |      | 7.2.2      | -                                           | 7-7   |

|           |      | 7.2.3      | Memory Interface Timings                    | 7-8   |

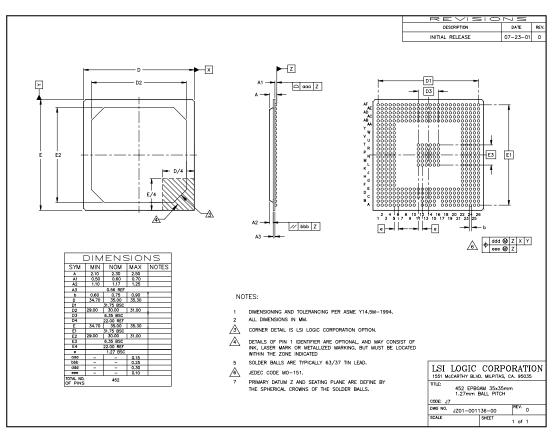

|           | 7.3  | Packag     | · ·                                         | 7-11  |

|           | 7.4  |            | nical Drawing                               | 7-18  |

|           | 7.5  |            | e Thermal Considerations                    | 7-19  |

|           |      | 0          |                                             |       |

| Appendix A | Register Summary                    |

|------------|-------------------------------------|

| Appendix B | Reference Specifications            |

| Appendix C | Glossary of Terms and Abbreviations |

|            | Index                               |

|            | Customer Feedback                   |

### Figures

| 1.1 | LSIFC929X Typical Implementation       | 1-5  |

|-----|----------------------------------------|------|

| 1.2 | LSIFC929X Functional Block Diagram     | 1-7  |

| 2.1 | FC Layers                              | 2-2  |

| 2.2 | Link Control Frame                     | 2-4  |

| 2.3 | Data Frame                             | 2-4  |

| 2.4 | Exchange to Character                  | 2-5  |

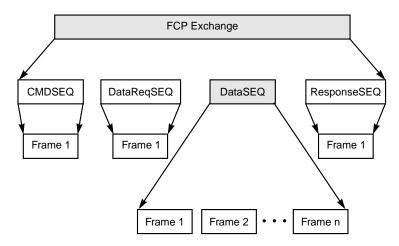

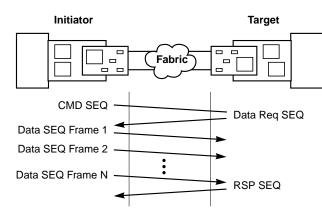

| 2.5 | FCP Exchange                           | 2-6  |

| 2.6 | Write Event Trellis                    | 2-7  |

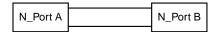

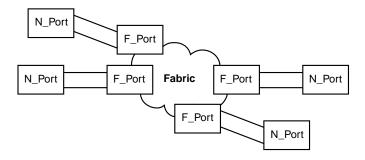

| 2.7 | Point-to-Point Topology                | 2-8  |

| 2.8 | Fabric Topology                        | 2-8  |

| 2.9 | Arbitrated Loop Topology               | 2-9  |

| 3.1 | LSIFC929X Block Diagram                | 3-2  |

| 3.2 | LSIFC929X Message Flow                 | 3-5  |

| 3.3 | LAN Protocol Stack                     | 3-7  |

| 3.4 | LSIFC929X Typical Implementation       | 3-9  |

| 4.1 | LSIFC929X Functional Signal Grouping   | 4-2  |

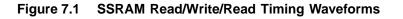

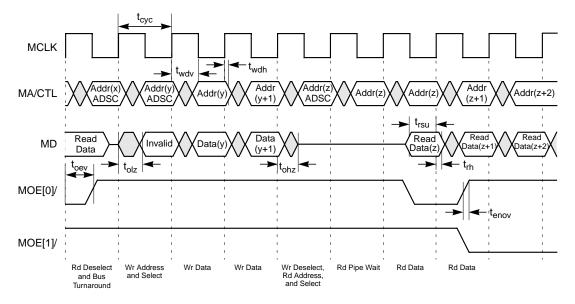

| 7.1 | SSRAM Read/Write/Read Timing Waveforms | 7-8  |

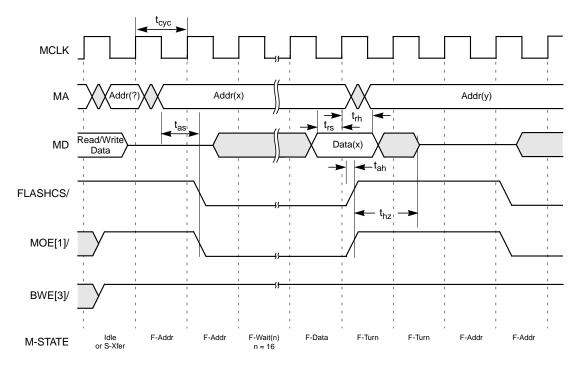

| 7.2 | Flash ROM Read Timing Waveforms        | 7-9  |

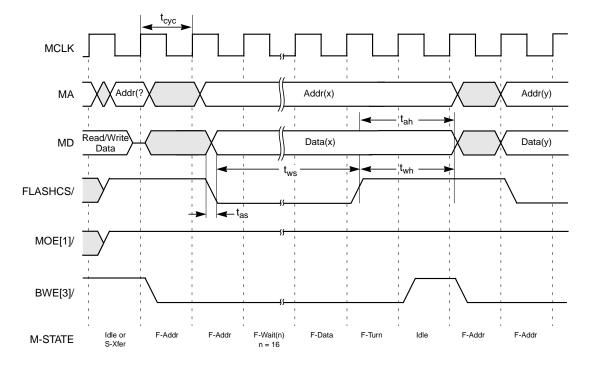

| 7.3 | Flash ROM Write Timing Waveforms       | 7-10 |

| 7.4 | LSIFC929X 456-Pin PBGA Top View        | 7-12 |

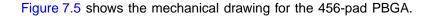

| 7.5 | 456-Pad Plastic Ball Grid Array        | 7-18 |

www.DataSheet4U.com

#### Tables

| 4.1  | PCI/PCI-X Interface                                                                                         | 4-3  |

|------|-------------------------------------------------------------------------------------------------------------|------|

| 4.2  | Fibre Channel Interface                                                                                     | 4-7  |

| 4.3  | Memory Interface                                                                                            | 4-10 |

| 4.4  | Configuration and Miscellaneous                                                                             | 4-14 |

| 4.5  | Test and I/O Processor Debug                                                                                | 4-15 |

| 4.6  | Power and Ground                                                                                            | 4-16 |

| 5.1  | PCI/PCI-X Bus Commands and Encodings                                                                        | 5-4  |

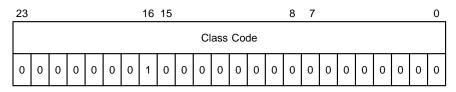

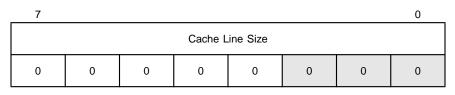

| 6.1  | LSIFC929X PCI-X Configuration Space Address Map                                                             | 6-3  |

| 6.2  | Device ID Values                                                                                            | 6-5  |

| 6.3  | Multiple Message Enable Field Bit Encoding                                                                  | 6-25 |

| 6.4  | Maximum Outstanding Split Transactions                                                                      | 6-29 |

| 6.5  | Maximum Memory Read Byte Count                                                                              | 6-29 |

| 6.6  | PCI I/O Space Address Map                                                                                   | 6-33 |

| 6.7  | PCI Memory [0] Address Map                                                                                  | 6-33 |

| 6.8  | PCI Memory [1] Address Map                                                                                  | 6-34 |

| 6.9  | Interrupt Signal Routing                                                                                    | 6-41 |

| 7.1  | Absolute Maximum Stress Ratings                                                                             | 7-3  |

| 7.2  | Operating Conditions                                                                                        | 7-3  |

| 7.3  | Capacitance                                                                                                 | 7-4  |

| 7.4  | Input Signals (FAULT1/, FAULT0/, MODE[7:0], SWITCH,<br>HOTSWAPEN/)                                          | 7-4  |

| 7.5  | Schmitt Input Signals (REFCLK, TCK, TDI, TRST/,                                                             |      |

|      | TMS_CHIP, TMS_ICE)                                                                                          | 7-4  |

| 7.6  | 4 mA Bidirectional Signals (LIPRESET/, ODIS1, ODIS0,                                                        |      |

|      | BYPASS1/, BYPASS0/, MD[31:0], MA[21:0], MWE[1:0]/,                                                          |      |

|      | FLASHCS/, BWE[3:0]/, RAMCS/, ZZ, MP[3:0], SCL,                                                              |      |

|      | SDA, RXLOS1, RXLOS0, ADSC/, ADV/, TDO)                                                                      | 7-4  |

| 7.7  | 8 mA Bidirectional Signals (MODDEF1[2:0],                                                                   |      |

|      | MODDEF0[2:0], GPIO[5:0], MOE[1:0]/, LED[4:0]/, MCLK)                                                        | 7-5  |

| 7.8  | PCI Input Signals (PCICLK, GNT/, IDSEL, RST/)                                                               | 7-5  |

| 7.9  | PCI Bidirectional Signals (AD[63:0], C_BE[7:0]/, FRAME/,<br>IRDY/, TRDY/, STOP/, PERR/, PAR, ACK64/, ENUM/, |      |

|      | 64EN/)                                                                                                      | 7-6  |

| 7.10 | PCI Output Signals (PAR64, REQ/, REQ64/, DEVSEL/,                                                           |      |

|      | SERR/, INTA/, INTB/)                                                                                        | 7-6  |

| 7.11 | SSRAM Read/Write/Read Timings                                                                               | 7-8  |

| 7.12 | FLASH ROM Read Timings                                                                                      | 7-9  |

| 7.13 | Flash ROM Write Timings                           | 7-10 |

|------|---------------------------------------------------|------|

| 7.14 | Alphanumeric Pad Listing by PBGA Position         | 7-14 |

| 7.15 | Alphanumeric Pad Listing by Signal Name           | 7-16 |

| 7.16 | Maximum Allowable Ambient Temperature vs. Airflow | 7-19 |

| A.1  | LSIFC929X Multifunction PCI Registers             | A-1  |

| A.2  | LSIFC929X Host Interface Registers                | A-3  |

| B.1  | Reference Specifications                          | B-1  |

# Chapter 1 Introduction

This chapter provides an overview of the LSIFC929X Dual Channel Fibre Channel I/O Processor. The chapter contains the following sections:

- Section 1.1, "Overview"

- Section 1.2, "General Description"

- Section 1.3, "Hardware Overview"

- Section 1.4, "Initiator Operations"

- Section 1.5, "Target Operations"

- Section 1.6, "Diagnostics"

# 1.1 Overview

The LSIFC929X is a high-performance, cost-effective, Dual Channel Fibre Channel (FC) I/O processor. It represents the latest system level integration technology in intelligent I/O processors from LSI Logic. The Storage Area Network (SAN) environment is fully supported with both Fibre Channel Protocol (FCP) for SCSI and LAN/IP.

#### 1.1.1 Hardware Features

The LSIFC929X supports the following list of hardware features:

- Highly integrated, full duplex, Dual Channel FC I/O processor

- Integrated 2 Gbit/s Dual Channel FC serial link

- 64-bit/66 MHz host PCI bus and 133 MHz PCI-X bus (both are backward compatible with 32-bit/33 MHz)

- Integrated bit error rate (BER) link testing

- 32-bit ARM<sup>®</sup> RISC processor

- Intelligent, high-performance context management

- Synchronous SRAM (SSRAM) external memory interface

- Full simultaneous target and initiator operations

- Implementation of common Message Passing Interface (MPI)

- Firmware support for concurrent host commands

- 1000 concurrent commands with 1 Mbyte SRAM (default)

- 2000 concurrent commands with 2 Mbytes SRAM

- 4000 concurrent commands with 4 Mbytes SRAM

- PC2001 compliant

- Peripheral Component Interface (PCI) 2.2 compliant

- JTAG debug interface

- 456-pin plastic ball grid array (PBGA)

#### 1.1.2 FC Features

The LSIFC929X supports the following list of FC features:

- Class 2 and Class 3 support (with optional confirmed delivery)

- BB credit of 16, alternate login of 1 (each channel)

- FC-PH compliance

- FC-AL 7.0 compliance

- FC-FCP, FC-PLDA compliance

- FC-FLA compliance

- FCA-IP, IETF-IPFC compliance

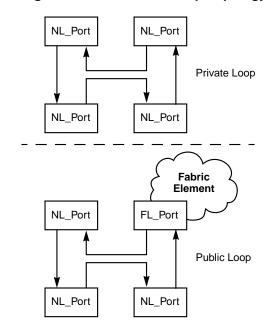

- NL\_Port (Arbitrated Loop)

- N\_Port (Point-to-Point)

- FL\_Port (Public Loop Attach)

- F\_Port (Fabric Attach)

- AutoNegotiation between link speeds under firmware control; provides automatic interoperability between 1 Gbit/s and 2Gbit/s links (independent for each channel)

## 1.1.3 Software Features

The LSIFC929X supports the following list of software features:

- Fusion-MPT<sup>™</sup> drivers

- Optimum server I/O profile with low CPU utilization

- Optimum workstation I/O profile with maximum I/O performance

- Diagnostic capability

- Host driver support for failover and load balancing

- SAN Storage Management

#### 1.1.4 OS Support

The LSIFC929X supports the following list of operating systems:

- Windows 2000

- Windows NT 4.0 SP4 and Windows NT 5.0

- Windows XP

- NetWare 4.11 and 5.0

- UnixWare 2.12 and Gemini

- Solaris 2.6, 2.7–X86

- Solaris SPARC

- Linux susi, Turbolinux, and Red Hat Linux

## 1.1.5 Targeted Applications

The LSIFC929X targets the following list of key applications:

- SANs

- Storage virtualization

- Server clustering environments

- Embedded RAID

- Low cost PCI-X/FC host adapters

- Host main boards

- Routers and bridges

# 1.2 General Description

The LSIFC929X Dual Channel FC I/O processor is a high-performance, Intelligent I/O processor (IOP) that simultaneously supports mass storage and IP protocols on a full duplex, 2 Gbit/s FC link. The sophisticated design and local memory architecture work together to reduce the host CPU and PCI bandwidth required to support FC I/O operations.

From the host CPU perspective, the LSIFC929X manages the FC link at the exchange level for mass storage (FCP) protocols. The LSIFC929X supports multiple I/O requests per host interrupt in most applications.

From the FC link perspective, the LSIFC929X is a highly efficient NL\_Port supporting point-to-point, public and private loop topologies, and the FC switch/attach topology defined under the ANSI X3T11 FC-FS standard. The LSIFC929X uniquely supports FC environments where independent, full duplex transmission is required for maximum FC link efficiency. Special attention has been given to the design to accelerate context switching and link utilization.

The LSIFC929X includes a 64-bit, 66 MHz host PCI interface and a 133 MHz PCI-X interface to the host environment. The host interface minimizes the amount of time spent on the PCI bus for nondata moving activities such as initialization, command, and error recovery. In addition, the host interface has inherent flexibility to support the OEM implementation tradeoffs between CPU, PCI-X, and I/O bandwidth.

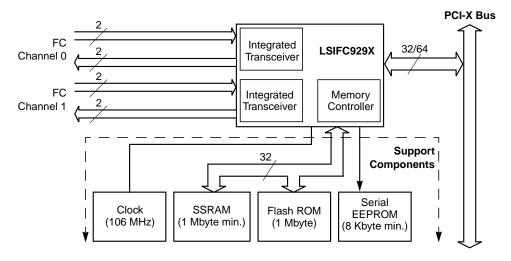

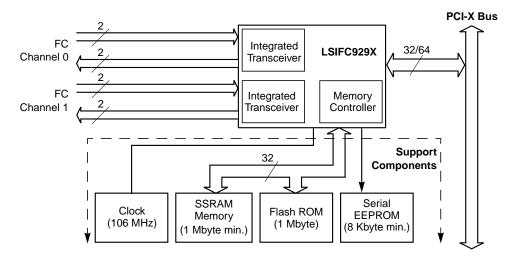

The high level of integration in the LSIFC929X controller enables low cost FC implementations. Figure 1.1 shows a typical implementation incorporating the LSIFC929X controller.

#### Figure 1.1 LSIFC929X Typical Implementation

## 1.2.1 Multifunction PCI-X

Coupled with the dual channel operation, the LSIFC929X adds multifunction capability on the PCI-X bus. This capability allows the host to see two distinct "channels" or host adapters. Each channel provides full, concurrent support for FCP Initiator, Target, and LAN protocols.

## 1.2.2 Autospeed Negotiation

Backward compatibility with 1 Gbit/s FC devices is maintained through Autospeed Negotiation. After a power-on, loss of signal, or loss of word synchronization for longer than the R\_T\_TOV time-out, the LSIFC929X performs this operation to determine whether a point-to-point device or all of the devices on a link are either 1 Gbit/s or 2 Gbit/s devices, and it automatically configures itself to be compatible with the devices on the link.

## 1.2.3 Autotopology Negotiation

The LSIFC929X maintains compatibility with private loop, public loop, and point-to-point topologies through Autotopology Negotiation. The LSIFC929X performs this operation to determine the type of attached link, and automatically configures each LSIFC929X port to the current port type.

### 1.2.4 Failover and Load Balancing

The LSIFC929X supports two PCI-X functions and two FC ports, which improves performance and provides a redundant path in high-availability systems that require failover capabilities. In case of a Link Failure, the LSIFC929X architecture allows the OS driver to support automatic failover without the need for LSIFC929X intervention. Load Balancing also can be provided in the host driver to partition the I/O workload across each channel of the LSIFC929X.

# 1.3 Hardware Overview

In today's fast growing SAN, storage virtualization, server/workstation, and RAID storage systems marketplaces, higher levels of performance, scalability, and reliability are required to stay competitive.

The LSIFC929X provides the performance and flexibility to meet future FC connectivity requirements.

The LSIFC929X and LSI Logic software drivers provide superior performance and lower host CPU overhead than other competitive solutions. Because of its high level of integration and streamlined architecture, the LSIFC929X provides the highest level of performance in a more cost effective FC solution.

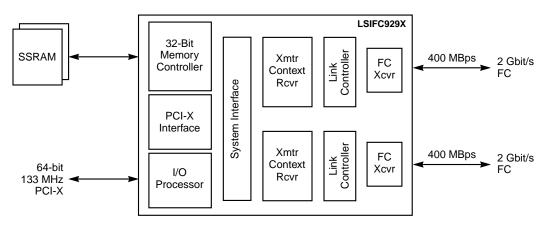

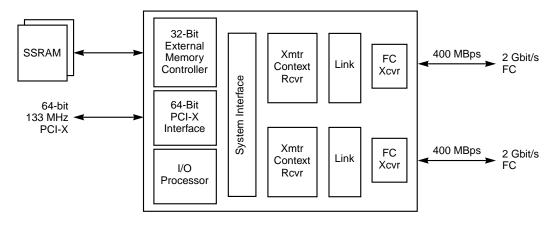

Figure 1.2 shows the functional block diagram for the LSIFC929X. The architecture maximizes performance and flexibility by deploying fixed gates in critical performance areas and utilizing multiple ARM RISC processors (two for context management and one for the I/O processor). Each of the major blocks is described briefly.

## 1.3.1 PCI/PCI-X Interface

The LSIFC929X uses a 64-bit (33 MHz, 66 MHz, or 133 MHz) PCI/PCI-X interface or a 32-bit (33 MHz, 66 MHz, or 133 MHz) PCI/PCI-X interface. In addition, support is provided for Dual Address Cycle (DAC), PCI-X power management, Subsystem Vendor ID, Vendor Product Data (VPD), and Message Signaled Interrupt (MSI).

#### 1.3.2 32-Bit Memory Controller

The memory controller provides access to Flash ROM and 32-bit Synchronous SRAM and nonvolatile SRAM (NVSRAM). It supports both interleaved and noninterleaved configurations up to a maximum of 4 Mbytes of synchronous SRAM. A general purpose memory expansion bus supports up to 1 Mbyte of Flash ROM.

#### 1.3.3 I/O Processor

The LSIFC929X uses a 32-bit ARM RISC processor to control all system interface and message transport functionality. This frees the host CPU for other processing activity and improves overall I/O performance. The RISC processor and associated firmware can manage an I/O from start to finish without host intervention. The RISC processor also manages the message passing interface.

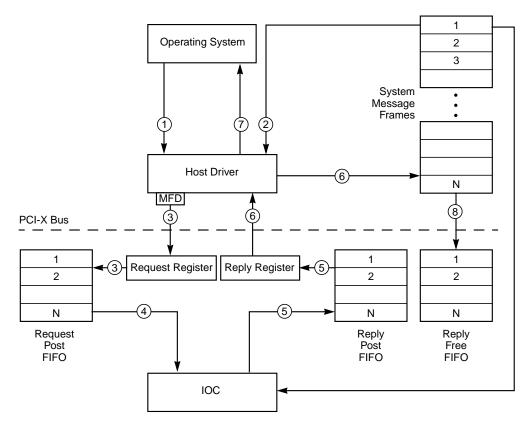

### 1.3.4 System Interface

The system interface efficiently passes messages between the LSIFC929X and other I/O agents. It consists of four hardware FIFOs for the message queuing lists: Request Free, Request Post, Reply Free, and Reply Post. Control logic for the FIFOs is provided within the LSIFC929X system interface with messages stored in external memory.

### 1.3.5 Integrated 2 Gbit/s Transceivers

The LSIFC929X implements GigaBlaze<sup>®</sup> 2 Gbit/s transceivers. GigaBlaze is backward-compatible with 1 Gbit/s systems, using a firmware-implemented "Autospeed Negotiation" for automatic compatibility between 1 Gbit/s and 2 Gbit/s links. The integrated 2 Gbit/s transceivers provide a FC-compliant physical interface for cost conscious and real estate limited applications.

#### 1.3.6 Link Controllers

The integrated link controller is FC-AL-2 (Rev. 7.0) compatible and performs all link operations. The controller monitors the Link State and strictly adheres to the Loop Port State Machine, ensuring maximum system interoperability. The link controller interfaces to the integrated transceiver.

#### 1.3.7 Datapath

The transmitter builds sequences based on context information and transmits resulting frames to the FC link using the Link Controller. Each transmitter includes two 2 Kbyte buffers to support frame payloads.

The receivers accept frame data from the Link Controller and DMAs the encapsulated information to local or system memory. Each receiver contains sixteen 2112-byte buffers that support a BB Credit of up to sixteen or an Alternate Login BB Credit of 1 on each channel.

#### 1.3.8 Context Managers

The LSIFC929X uses an ARM RISC processor in each channel to support I/O context swap to external memory and FCP management for both Initiator and Target applications. Context operations include support for transmit and resource queue management, as well as scatter/gather list management.

## **1.4 Initiator Operations**

The LSIFC929X autonomously handles FCP exchanges upon request from the host. The LSIFC929X generates appropriate sequences and frames necessary to complete the request and provides feedback to the host on the status of the request.

## 1.5 Target Operations

The LSIFC929X provides for general purpose target functions such as those required for front-end RAID applications.

## 1.6 Diagnostics

The LSIFC929X provides the capabilities to do a simplified "Link Check" BER test on the link for diagnostic purposes. In a special test mode the controller can transmit and verify a programmed data pattern for link evaluation.

# Chapter 2 Fibre Channel Overview

This chapter provides general overview information on Fibre Channel (FC). The chapter contains the following sections:

- Section 2.1, "Introduction"

- Section 2.2, "FC Layers"

- Section 2.3, "Frames"

- Section 2.4, "Exchanges"

- Section 2.5, "FC Ports"

- Section 2.6, "FC Topologies"

- Section 2.7, "Classes of Service"

## 2.1 Introduction

FC is a high-performance, hybrid interface. It is both a channel and a network interface that contains network features to provide the required connectivity, distance, protocol multiplexing, as well as traditional channel features to retain the required simplicity, repeatable performance, and guaranteed delivery. Popular industry standard networking protocols such as Internet Protocol (IP) and channel protocols such as Small Computer System Interface (SCSI) have been mapped to the FC standard.

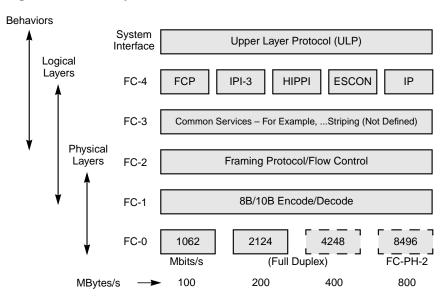

The FC structure is defined by five functional layers. These layers, shown in Figure 2.1, define the physical media and transmission rates, encoding scheme, framing protocol and flow control, common services, and the Upper Level Protocol (ULP) interfaces.

#### Figure 2.1 FC Layers

# 2.2 FC Layers

The lowest layer, FC-0, is the media interface layer. It defines the physical characteristics of the interface. It includes transceivers, copper-to-optical transducers, connectors, and any other associated circuitry necessary to transmit or receive at 1062 or greater Mbit/s rates over copper or optical cable.

The FC-1 layer defines the 8B/10B encoding/decoding scheme, the transmission protocol necessary to integrate the data and transmit clock, and the receive clock recovery. Implementation of this layer is usually divided between the hardware implementing the FC-0 layer in a transceiver, and the protocol device that implements the FC-2 layer. Specifically, the FC-0 transceivers can include the clock recovery circuitry while the 8B/10B encoding/decoding is provided in the protocol device.

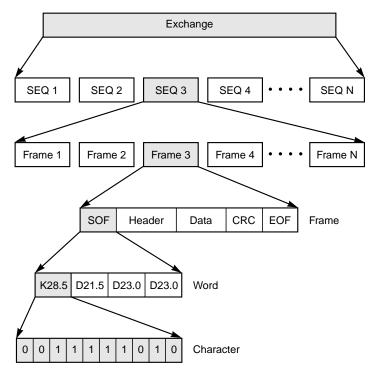

The FC-2 layer defines the rules for the signaling protocol and describes transfer of the frames, sequences, and exchanges. The meaning of the data being transmitted or received is transparent to the FC-2 layer. However, the context between any given set of frames is maintained at the FC-2 layer through the Sequence and Exchange constructs. The framing protocol creates the constructs necessary to form frames with the data being packetized within the payload of each frame.

The FC-3 layer provides common services that span multiple N\_Ports (refer to Section 2.5, "FC Ports," on page 2-7 for details). Some of these services include Striping, Hunt Groups, and Multicasting. All of these services allow a single port or fabric to communicate to several N\_Ports at one time.

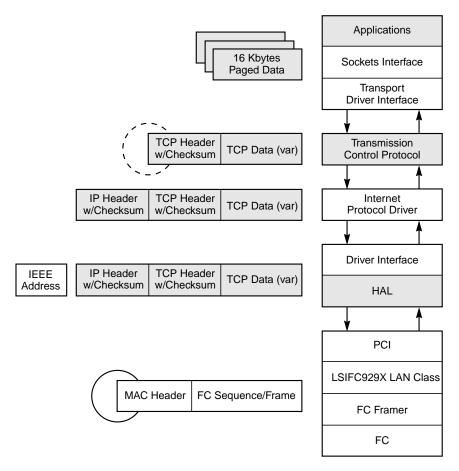

The FC-4 layer is the top layer defined in the FC. The FC-4 layer provides a seamless integration of existing standards. It specifies the mapping of ULPs to the layers below. Some of these ULPs include SCSI and IP. Each of these ULPs is defined in its own ANSI document.

## 2.3 Frames

There are two types of frames used in FC: Link Control frames and Data frames. Link Control frames, which contain no payload, are flow control responses to Data frames. An example of a Link Control frame is the ACK frame.

Figure 2.2 Link Control Frame

| Start<br>of<br>Frame | Frame<br>Header | CRC       | End<br>of<br>Frame |

|----------------------|-----------------|-----------|--------------------|

| (4 Bytes)            | (24 Bytes)      | (4 Bytes) | (4 Bytes)          |

A Data frame is any frame that contains data in the payload field. An example of a Data frame is the LOGIN frame.

#### Figure 2.3 Data Frame

| Start<br>of<br>Frame | Frame<br>Header | Data Field<br>(Optional Headers<br>and Payload) | CRC       | End<br>of<br>Frame |

|----------------------|-----------------|-------------------------------------------------|-----------|--------------------|

| (4 Bytes             |                 | (0 to 2112 Bytes)                               | (4 Bytes) | (4 Bytes)          |