# 50 Hz to 2.7 GHz 60 dB TruPwr<sup>™</sup> Detector

# AD8362

#### FEATURES

Complete Fully Calibrated Measurement/ Control System Accurate RMS-to-DC Conversion from 50 Hz to 2.7 GHz Input Dynamic Range of >60 dB -52 dBm to 8 dBm in 50 Ω Waveform and Modulation Independent (GSM/CDMA/TDMA, and so on) Linear-in-Decibels Output, Scaled 50 mV/dB Law Conformance Error of 0.5 dB All Functions Temperature and Supply Stable Operates from 4.5 V to 5.5 V at 24 mA from -40°C to +85°C Power-Down Capability to 1.3 mW

#### APPLICATIONS

Power Amplifier Linearization/Control Loops Transmitter Power Control Transmitter Signal Strength Indication (TSSI) RF Instrumentation

#### **GENERAL DESCRIPTION**

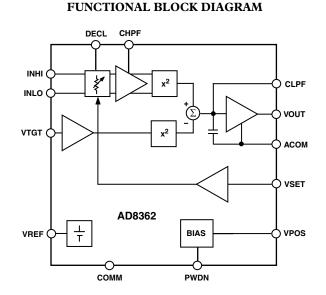

The AD8362 is a true-rms-responding power detector having a 60 dB measurement range. It is intended for use in a variety of high frequency communication systems, and in instrumentation requiring an accurate response to signal power. It is easy to use, requiring only a single supply of 5 V and a few capacitors. It can operate from arbitrarily low frequencies to over 2.7 GHz and can accept inputs that have rms values from 1 mV to at least 1 V rms, with peak crest factors of up to six, exceeding the requirements for accurate measurement of CDMA signals.

The input signal is applied to a resistive ladder attenuator that comprises the input stage of a variable gain amplifier. The twelve tap points are smoothly interpolated using a proprietary technique to provide a continuously variable attenuator, which is controlled by a voltage applied to Pin VSET. The resulting signal is applied to a high performance broadband amplifier. Its output is measured by an accurate square law detector cell. The fluctuating output is then filtered and compared with the output of an identical squarer, whose input is a fixed dc voltage applied to Pin VTGT, usually the accurate reference of 1.25 V provided at Pin VREF.

The difference in the outputs of these squaring cells is integrated in a high gain error amplifier, generating a voltage at Pin VOUT with rail-to-rail capabilities. In a controller mode, this low noise output can be used to vary the gain of a host system's RF amplifier, thus balancing the set point against the input power. Optionally, the voltage at VSET may be a replica of the RF

#### REV.0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective companies.

signal's amplitude modulation, in which case the overall effect is to remove the modulation component prior to detection and low pass filtering. The corner frequency of the averaging filter may be lowered without limit by the addition of an external capacitor at Pin CLPF, the AD8362 can be used to determine the true power of a high frequency signal having a complex low frequency modulation envelope (or simply as a low frequency rms voltmeter). The high-pass corner generated by its offsetnulling loop can be lowered by a capacitor added on Pin CHPF.

Used as a power measurement device, Pin VOUT is strapped to VSET, and the output is then proportional to the logarithm of the rms value of the input; that is, the reading is presented directly in decibels, and is conveniently scaled 1 V per decade, that is, 50 mV/dB; other slopes are easily arranged. In controller modes, the voltage applied to VSET determines the power level required at the input to null the deviation from the set point. The output buffer can provide high load currents.

The AD8362 is powered down by a logic high applied to the PWDN pin, i.e., the consumption is reduced to about 1.3 mW. It powers up within about 20  $\mu$ s to its nominal operating current of 20 mA at 25°C.

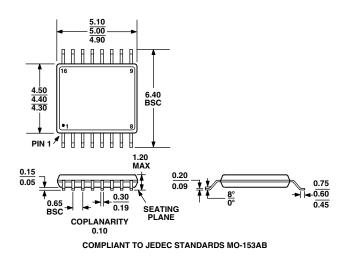

The AD8362 is supplied in a 16-lead TSSOP package for operation over the industrial temperature range of  $-40^{\circ}$ C to  $+85^{\circ}$ C. An evaluation board is available.

# **AD8362—SPECIFICATIONS** $(V_s = 5 V, T = 25^{\circ}C, Z_0 = 50 \Omega, differential input drive via Balun<sup>1</sup>, VTGT connected to V<sub>REF</sub> V<sub>OUT</sub> tied to V<sub>SET</sub>, unless otherwise noted.)$

| Parameter                                           | Conditions                                                       | Min   | Тур          | Max   | Unit                                   |

|-----------------------------------------------------|------------------------------------------------------------------|-------|--------------|-------|----------------------------------------|

| OVERALL FUNCTION                                    |                                                                  |       |              |       |                                        |

| Maximum Input Frequency                             |                                                                  |       | 2.7          |       | GHz                                    |

| Input Power Range (Diff'l)                          | dB referred to 50 $\Omega$ Impedance level, f $\leq$ 2.7 GHz,    |       |              |       |                                        |

| Nominal Low End of Range                            | into 1:4 Balun <sup>1</sup>                                      |       | -52          |       | dBm                                    |

| Nominal High End of Range                           |                                                                  |       | +8           |       | dBm                                    |

| Input Voltage Range (Diff'l)                        | RMS Voltage at Input Terminals, $f \le 2.7$ GHz, into            |       | 1.10         |       |                                        |

| Nominal Low End of Range                            | Input of the Device.                                             |       | 1.12         |       | mV rms                                 |

| Nominal High End of Range                           |                                                                  |       | 1.12         |       | V rms                                  |

| Input Power Range (S-Sided)                         | Single-Ended Drive, CW Input, $f \le 2.7$ GHz, into              |       | 40           |       | 1D                                     |

| Nominal Low End of Range                            | Input Resistive Network <sup>2</sup>                             |       | -40          |       | dBm<br>dBm                             |

| Nominal High End of Range                           | DMC Maltana at Lanat Transinals from CH-                         |       | 0            |       | dbin                                   |

| Input Voltage Range (S-Sided)                       | RMS Voltage at Input Terminals, $f \le 2.7$ GHz                  |       | 2.22         |       | The second                             |

| Nominal Low End of Range                            |                                                                  |       | 2.23         |       | mV rms<br>V rms                        |

| Nominal High End of Range                           | $\mathbf{P} > 200 \text{ O to Crownd}$                           |       | 223          |       | V THIS                                 |

| Output Voltage Range                                | $R_L \ge 200 \ \Omega$ to Ground                                 |       | 1100         |       | TT I I I I I I I I I I I I I I I I I I |

| Nominal Low End of Range                            | In Conoral V 0.1 V                                               |       | +100<br>+4.9 |       | mV<br>V                                |

| Nominal High End of Range                           | In General, V <sub>S</sub> –0.1 V                                |       | +4.9<br>50   |       | w<br>mV/dB                             |

| Output Scaling (Log Slope)<br>Law Conformance Error | Over Central 60 dB Range, $f \le 2.7$ GHz                        |       | $\pm 0.5$    |       | dB                                     |

|                                                     |                                                                  |       | 10.5         |       | uБ                                     |

| RF INPUT INTERFACE                                  | Pins INHI, INLO, AC-Coupled                                      |       |              |       |                                        |

| Input Resistance                                    | Single-Ended Drive, wrt DECL                                     |       | 100          |       | Ω                                      |

|                                                     | Differential Drive                                               |       | 200          |       | Ω                                      |

| OUTPUT INTERFACE                                    | Pin VOUT                                                         |       |              |       |                                        |

| Available Output Range                              | $R_L \ge 200 \ \Omega$ to Ground                                 | 0.5   |              | 4.9   | V                                      |

| Absolute Voltage Range                              |                                                                  |       |              |       | v                                      |

| Nominal Low End of Range                            | Measurement mode, f = 900 MHz $P_{IN}$ = -52 dBm                 | 0.32  |              | 0.48  | V                                      |

| Nominal High End of Range                           | Measurement mode, $f = 900 \text{ MHz } P_{IN} = +8 \text{ dBm}$ | 3.44  |              | 3.52  | V                                      |

| Source/Sink Current                                 | VOUT held at $V_8/2$ , to 1% change                              |       | 48           |       | mA                                     |

| Slew Rate Rising                                    | $C_L = Open$                                                     |       | 60           |       | V/µs                                   |

| Slew Rate Falling                                   | $C_{\rm L} = Open$                                               |       | 5            |       | V/µs                                   |

| Rise Time, 10%–90%                                  | 0.2 V to $1.8$ V, CLPF = 0                                       |       | 45           |       | ns                                     |

| Fall Time, 90%–10%                                  | 1.8  V to  0.2  V,  CLPF = 0                                     |       | 0.4          |       | μs                                     |

| Wide-Band Noise                                     | CLPF = 1000 pF, $f_{SPOT} \le 100 \text{ kHz}$                   |       | 70           |       | nV/√Hz                                 |

| VSET INTERFACE                                      | Pin VSET                                                         |       |              |       |                                        |

| Nominal Input Voltage Range                         | To $\pm 1$ dB Error                                              | 0.5   |              | 3.75  | v                                      |

| Input Resistance                                    |                                                                  | 0.5   | 68           | 5.15  | kΩ                                     |

| Scaling (Log Slope)                                 | f = 900 MHz                                                      | 46    | 50           | 54    | mV/dB                                  |

| Scaling (Log Intercept)                             | f = 900  MHz, into 1:4 Balun                                     | -64   | -60          | -56   | dBm                                    |

| Scaling (Log intercept)                             |                                                                  | -77   | -73          | -69   | dBV                                    |

|                                                     |                                                                  |       |              |       |                                        |

| VOLTAGE REFERENCE                                   | Pin VREF                                                         |       |              |       |                                        |

| Output Voltage                                      | 25°C                                                             | 1.225 | 1.25         | 1.275 | V                                      |

| Temperature Sensitivity <sup>3</sup>                | $-40^{\circ}C \le T_A \le +85^{\circ}C$                          |       | 0.08         |       | mV/°C                                  |

| Input Resistance                                    |                                                                  |       | 8            |       | Ω                                      |

| RMS TARGET INTERFACE                                | Pin VTGT                                                         |       |              |       |                                        |

| Nominal Input Voltage Range                         | Measurement Range = 60 dB, to $\pm 1$ dB Error                   | 0.625 |              | 2.5   | V                                      |

| Input Bias Current                                  | VTGT = 1.25 V                                                    |       | -28          |       | μA                                     |

| -                                                   | VTGT = 0 V                                                       |       | -52          |       | μA                                     |

| Incremental Input Resistance                        |                                                                  |       | 52           |       | kΩ                                     |

| Parameter                             | Conditions                                                                                                      | Min | Тур          | Max | Unit     |

|---------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----|--------------|-----|----------|

| POWER DOWN INTERFACE                  | Pin PWDN                                                                                                        |     |              |     |          |

| Logic Level to Enable                 | Logic Low Enables                                                                                               |     |              | 1   | V        |

| Logic Level to Disable                | Logic High Disables                                                                                             | 3   |              |     | V        |

| Input Current                         | Logic High                                                                                                      |     | 230          |     | μA       |

| -                                     | Logic Low                                                                                                       |     | 5            |     | μA       |

| Enable Time                           | From PWDN Low to VOUT within 10% of final value,                                                                |     |              |     |          |

|                                       | CLPF = 1000  pF                                                                                                 |     | 14.5         |     | ns       |

| Disable Time                          | From PWDN High to VOUT within 10% of final value,                                                               |     |              |     |          |

|                                       | CLPF = 1000  pF                                                                                                 |     | 2.5          |     | us       |

| POWER SUPPLY INTERFACE                | Pin VPOS                                                                                                        |     |              |     |          |

| Supply Voltage                        |                                                                                                                 | 4.5 | 5            | 5.5 | V        |

| Quiescent Current                     |                                                                                                                 | 115 | 20           | 22  | mA       |

| Supply Current                        | When disabled                                                                                                   |     | 0.2          |     | mA       |

|                                       |                                                                                                                 |     |              |     |          |

| 900 MHz                               | Enne Defensed to Dest Et Line (Linear Descusion)                                                                |     |              |     |          |

| Dynamic Range                         | Error Referred to Best Fit Line (Linear Regression)<br>±1 dB Linearity, CW Input                                |     | 65           |     | dB       |

|                                       | ±0.5 dB Linearity, CW Input                                                                                     |     |              |     | dB<br>dB |

| Deviation vs. Temperature             | Deviation from Output at 25°C                                                                                   |     | 62           |     | ub       |

| Deviation vs. Temperature             | $-40^{\circ}C < T_A < +85^{\circ}C; P_{IN} = -45 \text{ dBm}$                                                   |     | -1.7         |     | dB       |

|                                       | $-40^{\circ}\text{C} < \text{T}_{\text{A}} < +85^{\circ}\text{C}; \text{ P}_{\text{IN}} = -20 \text{ dBm}$      |     | -1.7<br>-1.4 |     | dB       |

|                                       | $-40^{\circ}\text{C} < \text{T}_{\text{A}} < +85^{\circ}\text{C}; \text{P}_{\text{IN}} = -20^{\circ}\text{dBm}$ |     | -1.4<br>-1   |     | dB       |

| Logarithmic Slope                     | $40 \text{ C} \times 1_{\text{A}} \times 105 \text{ C}, 1_{\text{IN}} = 5 \text{ dbm}$                          | 46  | 50           | 54  | mV/dB    |

| Logarithmic Intercept                 |                                                                                                                 | -64 | -60          | -56 | dBm      |

| Deviation from CW Response            | 5.5 dB Peak-to-RMS Ratio (IS95 Reverse Link)                                                                    | 01  | 0.2          | 50  | dB       |

| Deviation from GW Response            | 12 dB Peak-to-RMS Ratio (WCDMA 4 Channels)                                                                      |     | 0.2          |     | dB       |

|                                       | 18 dB Peak-to-RMS Ratio (WCDMA 15 Channels)                                                                     |     | 0.5          |     | dB       |

| 1.9 GHz                               |                                                                                                                 |     |              |     |          |

| Dynamic Range                         | Error Referred to Best Fit Line (Linear Regression)                                                             |     |              |     |          |

| Dynamic Range                         | $\pm 1$ dB Linearity, CW Input                                                                                  |     | 65           |     | dB       |

|                                       | ±0.5 dB Linearity, CW Input                                                                                     |     | 62           |     | dB       |

| Deviation vs. Temperature             | Deviation from Output at 25°C                                                                                   |     | 02           |     | uD       |

| Deviation vs. Temperature             | $-40^{\circ}\text{C} < \text{T}_{\text{A}} < +85^{\circ}\text{C}; \text{ P}_{\text{IN}} = -45 \text{ dBm}$      |     | -0.6         |     | dB       |

|                                       | $-40^{\circ}\text{C} < \text{T}_{\text{A}} < +85^{\circ}\text{C};  \text{P}_{\text{IN}} = -20 \text{ dBm}$      |     | -0.5         |     | dB       |

|                                       | $-40^{\circ}\text{C} < \text{T}_{\text{A}} < +85^{\circ}\text{C}; \text{ P}_{\text{IN}} = 5 \text{ dBm}$        |     | -0.3         |     | dB       |

| Logarithmic Slope                     |                                                                                                                 |     | 51           |     | mV/dB    |

| Logarithmic Intercept                 |                                                                                                                 |     | -59          |     | dBm      |

| Deviation from CW Response            | 5.5 dB Peak-to-RMS Ratio (IS95 Reverse Link)                                                                    |     | 0.2          |     | dB       |

| L.                                    | 12 dB Peak-to-RMS Ratio (WCDMA 4 Channels)                                                                      |     | 0.2          |     | dB       |

|                                       | 18 dB Peak-to-RMS Ratio (WCDMA 15 Channels)                                                                     |     | 0.5          |     | dB       |

| 2.2 GHz                               |                                                                                                                 |     |              |     |          |

| Dynamic Range                         | Error Referred to Best Fit Line (Linear Regression)                                                             |     |              |     |          |

| ,                                     | $\pm 1$ dB Linearity, CW Input                                                                                  |     | 65           |     | dB       |

|                                       | ±0.5 dB Linearity, CW Input                                                                                     |     | 65           |     | dB       |

| Deviation vs. Temperature             | Deviation from Output at 25°C                                                                                   |     |              |     |          |

| · · · · · · · · · · · · · · · · · · · | $-40^{\circ}\text{C} < \text{T}_{\text{A}} < +85^{\circ}\text{C}; \text{ P}_{\text{IN}} = -45 \text{ dBm}$      |     | -1.8         |     | dB       |

|                                       | $-40^{\circ}\text{C} < \text{T}_{\text{A}} < +85^{\circ}\text{C}; P_{\text{IN}} = -20 \text{ dBm}$              |     | -1.6         |     | dB       |

|                                       | $-40^{\circ}\text{C} < \text{T}_{\text{A}} < +85^{\circ}\text{C}; \text{ P}_{\text{IN}} = 5 \text{ dBm}$        |     | -1.3         |     | dB       |

| Logarithmic Slope                     |                                                                                                                 |     | 50.5         |     | mV/dB    |

| Logarithmic Intercept                 |                                                                                                                 |     | -61          |     | dBm      |

|                                       | 5.5 dB Peak-to-RMS Ratio (IS95 Reverse Link)                                                                    |     | 0.2          |     | dB       |

| Deviation from CW Response            |                                                                                                                 |     |              |     |          |

| Deviation from CW Response            | 12 dB Peak-to-RMS Ratio (WCDMA 4 Channels)                                                                      |     | 0.2          |     | dB       |

| Parameter                  | Conditions                                                                                                 | Min | Тур  | Max | Unit  |

|----------------------------|------------------------------------------------------------------------------------------------------------|-----|------|-----|-------|

| 2.7 GHz                    |                                                                                                            |     |      |     |       |

| Dynamic Range              | Error Referred to Best Fit Line (Linear Regression)                                                        |     |      |     |       |

|                            | ±1 dB Linearity, CW Input                                                                                  |     | 63   |     | dB    |

|                            | ±0.5 dB Linearity, CW Input                                                                                |     | 62   |     | dB    |

| Deviation vs. Temperature  | Deviation from Output at 25°C                                                                              |     |      |     |       |

|                            | $-40^{\circ}\text{C} < \text{T}_{\text{A}} < +85^{\circ}\text{C}; \text{ P}_{\text{IN}} = -40 \text{ dBm}$ |     | -5.3 |     | dB    |

|                            | $-40^{\circ}\text{C} < \text{T}_{\text{A}} < +85^{\circ}\text{C}; \text{ P}_{\text{IN}} = -15 \text{ dBm}$ |     | -5.5 |     | dB    |

|                            | $-40^{\circ}\text{C} < \text{T}_{\text{A}} < +85^{\circ}\text{C}; \text{P}_{\text{IN}} = 15 \text{ dBm}$   |     | -4.8 |     | dB    |

| Logarithmic Slope          |                                                                                                            |     | 50.5 |     | mV/dE |

| Logarithmic Intercept      |                                                                                                            |     | -58  |     | dBm   |

| Deviation from CW Response | 5.5 dB Peak-to-RMS Ratio (IS95 Reverse Link)                                                               |     | 0.2  |     | dB    |

|                            | 12 dB Peak-to-RMS Ratio (WCDMA 4 Channels)                                                                 |     | 0.2  |     | dB    |

|                            | 18 dB Peak-to-RMS Ratio (WCDMA 15 Channels)                                                                |     | 0.4  |     | dB    |

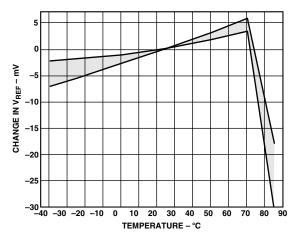

NOTES <sup>1</sup>1:4 balun transformer, M/A-COM ETC 1.6-4-2-3 <sup>2</sup>Resistive network consists of 33  $\Omega$  shunt and 25  $\Omega$  series. <sup>3</sup>See TPC 29

Specifications subject to change without notice.

#### **ABSOLUTE MAXIMUM RATINGS\***

| Supply Voltage V <sub>POS</sub> 5.5 V             |

|---------------------------------------------------|

| Input Power (into input of device) 13 dBm         |

| Equivalent Voltage 2 V rms                        |

| Internal Power Dissipation 500 mW                 |

| $\theta_{I\!A} \ \ldots \ \ldots \ 125^\circ C/W$ |

| Maximum Junction Temperature 125°C/W              |

| Operating Temperature Range40°C to +85°C          |

| Storage Temperature Range                         |

| Lead Temperature Range (Soldering 60 sec) 300°C   |

|                                                   |

\*Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

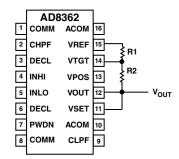

#### PIN CONFIGURATION

| COMM 1<br>CHPF 2<br>DECL 3<br>INHI 4<br>INLO 5<br>DECL 6<br>PWDN 7 | •<br>AD8362<br>TOP VIEW<br>(Not to Scale) | 15<br>14<br>13<br>12<br>11 | VPOS<br>VOUT<br>VSET<br>ACOM |

|--------------------------------------------------------------------|-------------------------------------------|----------------------------|------------------------------|

| PWDN 7                                                             |                                           | 10                         | ACOM                         |

| COMM 8                                                             |                                           | 9                          | CLPF                         |

#### **ORDERING GUIDE**

| Model                                       | Temperature Range | Package Option                                              |  |

|---------------------------------------------|-------------------|-------------------------------------------------------------|--|

| AD8362ARU<br>AD8362ARU-REEL7<br>AD8362-EVAL | -40°C to +85°C    | Tube, 16-Lead TSSOP<br>7" Tape and Reel<br>Evaluation Board |  |

#### CAUTION \_\_

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD8362 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

| Pin No. | Mnemonic | Description                                                                                                                                                                   | Equivalent<br>Circuit |

|---------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| 1, 8    | СОММ     | Common Connection. Connect via low impedance to system common.                                                                                                                |                       |

| 2       | CHPF     | Input HPF. Connect to common via a capacitor to determine 3 dB point of input signal high-pass filter.                                                                        |                       |

| 3, 6    | DECL     | Decoupling Terminals for INHI and INLO. Connect to common via a large capacitance to complete input circuit.                                                                  |                       |

| 4       | INHI     | High Signal Input Terminal. Part of a differential input port with INLO.                                                                                                      | Circuit A             |

| 5       | INLO     | Low Signal Input Terminal. Part of a differential input port with INHI.                                                                                                       | Circuit A             |

| 7       | PWDN     | Disable/Enable Control Input. Apply logic high voltage to shut down the AD8362.                                                                                               |                       |

| 9       | CLPF     | Connection for Loop Filter Integration (Averaging) Capacitor, the other pin of which is usually grounded via a resistor to improve loop stability and response time.          |                       |

| 10, 16  | ACOM     | Analog Common Connection for Output Amplifier                                                                                                                                 |                       |

| 11      | VSET     | The voltage applied to this pin sets the decibel value of the required RF input voltage that results in zero current out of pin CLPF and thus the loop integrating capacitor. | Circuit B             |

| 12      | VOUT     | Output of Error Amplifier. In measurement mode, normally connected directly to VSET.                                                                                          | Circuit C             |

| 13      | VPOS     | Connect to 5 V Power Supply                                                                                                                                                   |                       |

| 14      | VTGT     | The logarithmic intercept voltage is proportional to the voltage applied to this pin. The use of a lower target voltage increases the crest factor capacity.                  | Circuit D             |

| 15      | VREF     | General-Purpose Reference Voltage Output of 1.25 V (usually connected only to VTGT)                                                                                           | Circuit E             |

#### **PIN FUNCTION DESCRIPTIONS**

### **Equivalent Circuits**

### **Typical Performance Characteristics–AD8362**

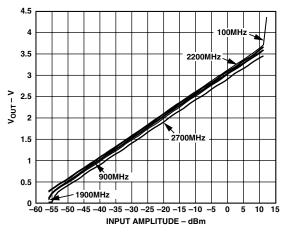

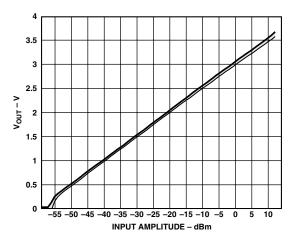

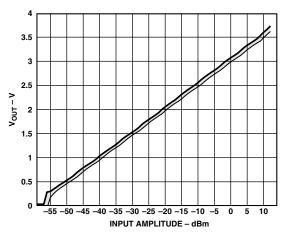

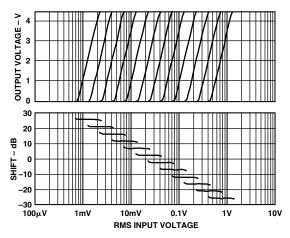

TPC 1. Output Voltage ( $V_{OUT}$ ) vs. Input Amplitude (dBm), Frequencies 100 MHz, 900 MHz, 1900 MHz, 2200 MHz, 2700 MHz, Sine Wave, Differential Drive

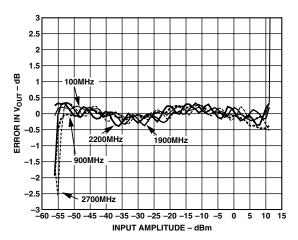

TPC 2. Logarithmic Law Conformance vs. Input Amplitude, Frequencies 100 MHz, 900 MHz, 1900 MHz, 2200 MHz, 2700 MHz, Sine Wave, Differential Drive

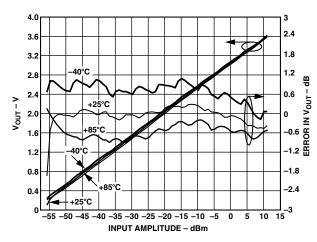

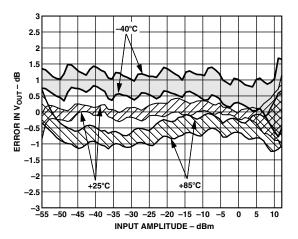

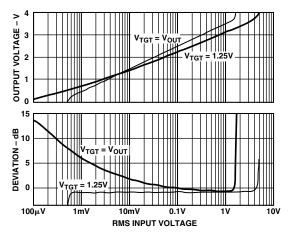

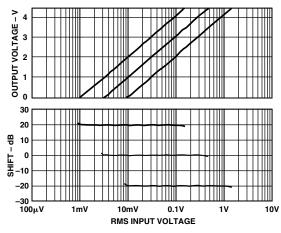

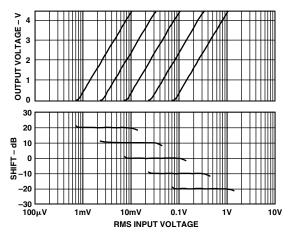

*TPC 3.*  $V_{OUT}$  and Law Conformance vs. Input Amplitude, Frequency 900 MHz, Sine Wave, Temperature -40°C, +25°C, and +85°C

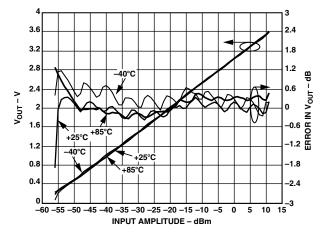

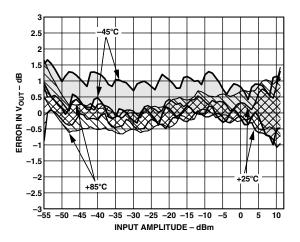

TPC 4.  $V_{OUT}$  and Law Conformance vs. Input Amplitude, Frequency 1900 MHz, Sine Wave, Temperature -40° C, +25° C, and +85° C

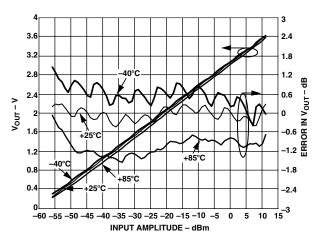

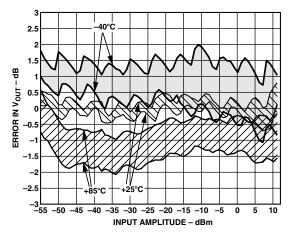

TPC 5.  $V_{OUT}$  and Law Conformance vs. Input Amplitude, Frequency 2200 MHz, Sine Wave, Temperature –40° C, +25° C, and +85° C

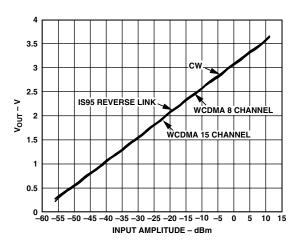

TPC 6. V<sub>OUT</sub> vs. Input Amplitude with Different Waveforms, CW, IS95-ReverseLink, WCDMA 8-Channel, WCDMA 15-Channel, Frequency 900 MHz

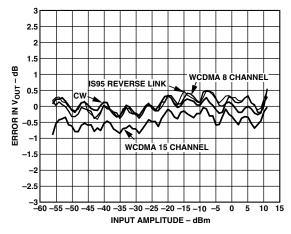

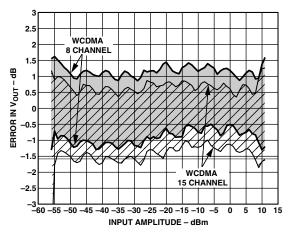

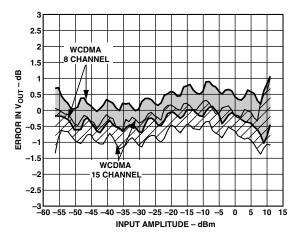

TPC 7. Output Error from CW Linear Reference vs. Input Amplitude with Different Waveforms, CW, IS95 Reverse Link, WCDMA 8-Channel, WCDMA 15-Channel, Frequency 900 MHz

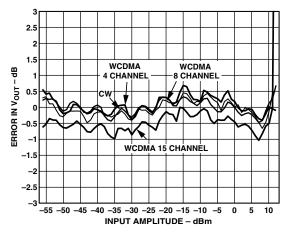

TPC 8. Output Error from CW Linear Reference vs. Input Amplitude with Different WCDMA Channel Loading, 4-Channel, 8-Channel, 15-Channel, Frequency 2200 MHz

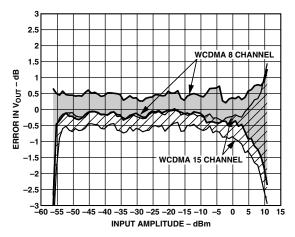

TPC 9. Output Error from CW Linear Reference vs. Input Amplitude, 3 Sigma to Either Side of Mean, with WCDMA 8-Channel, WCDMA 15-Channel, Frequency 1900 MHz

TPC 10. Output Error from CW Linear Reference vs. Input Amplitude, 3 Sigma to Either Side of Mean, with WCDMA 8-Channel, WCDMA 15-Channel, Frequency 1900 MHz

TPC 11. Output Error from CW Linear Reference vs. Input Amplitude, 3 Sigma to Either Side of Mean, with WCDMA 8-Channel, WCDMA 15-Channel, Frequency 2200 MHz

*TPC 12. V*<sub>OUT</sub> vs. Input Amplitude, 3 Sigma to Either Side of Mean, Sine Wave, Frequency 900 MHz, Part-to-Part Variation

TPC 13.  $V_{OUT}$  vs. Input Amplitude, 3 Sigma to Either Side of Mean, Sine Wave, Frequency 1900 MHz, Part-to-Part Variation

TPC 14. Logarithmic Law Conformance vs. Input Amplitude, 3 Sigma to Either Side of Mean, Sine Wave, Frequency 900 MHz, Temperature –40°C, +25°C, and +85°C

TPC 15. Logarithmic Law Conformance vs. Input Amplitude, 3 Sigma to Either Side of Mean, Sine Wave, Frequency 1900 MHz, Temperature –40°C, +25°C, and +85°C

TPC 16. Logarithmic Law Conformance vs. Input Amplitude, 3 Sigma to Either Side of Mean, Sine Wave, Frequency 2200 MHz, Temperature –40°C, +25°C, and +85°C

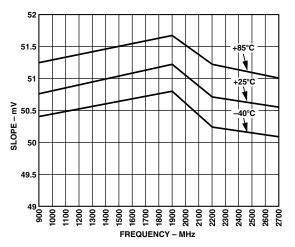

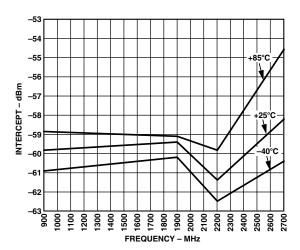

TPC 17. Logarithmic Slope vs. Frequency, Temperature  $-40^{\circ}C$ ,  $+25^{\circ}C$ , and  $+85^{\circ}C$

TPC 18. Logarithmic Intercept vs. Frequency, Temperature –40°C, +25°C, and +85°C

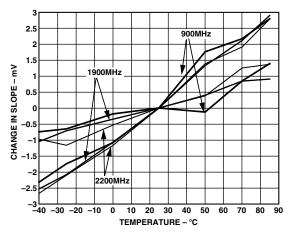

*TPC 19. Change in Logarithmic Slope vs. Temperature, 3 Sigma to Either Side of Mean, Frequencies 900 MHz, 1900 MHz, 2200 MHz*

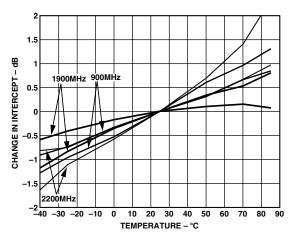

TPC 20. Change in Logarithmic Intercept vs. Temperature, 3 Sigma to Either Side of Mean, Frequencies 900 MHz, 1900 MHz, and 2200 MHz

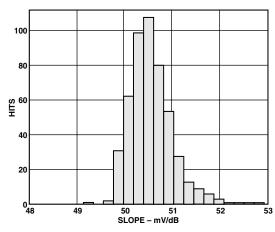

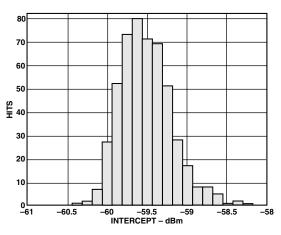

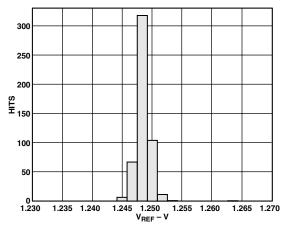

TPC 21. Slope Distribution, Frequency 900 MHz

TPC 22. Logarithmic Intercept Distribution, Frequency 900 MHz

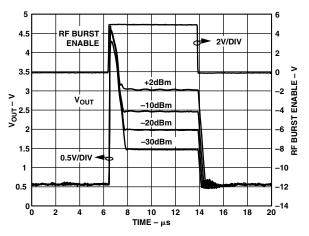

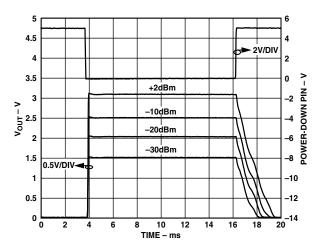

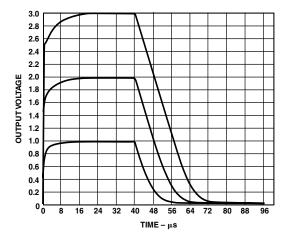

TPC 23. Output Response to RF Burst Input for Various RF Input Levels, Carrier Frequency 900 MHz,  $C_{LPF} = 0$

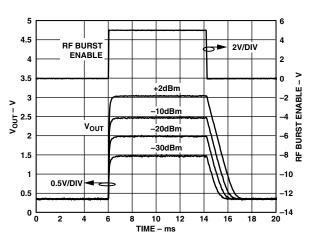

TPC 24. Output Response to RF Burst Input for Various RF Input Levels, Carrier Frequency 900 MHz, CLPF =  $0.1 \,\mu F$

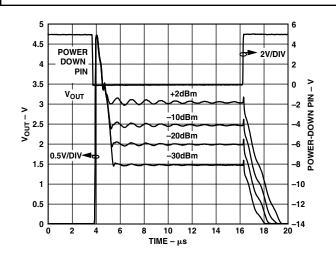

TPC 25. Output Response Using Power-Down Mode for Various RF Input Levels, Carrier Frequency 900 MHz,  $C_{LPF} = 0$

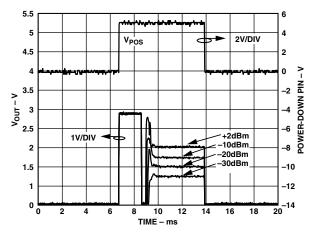

TPC 26. Output Response Using Power-Down Mode for Various RF Input Levels, Carrier Frequency 900 MHz,  $C_{LPF} = 0.1 \, \mu F$

TPC 27. Output Response to Gating on Power Supply for Various RF Input Levels, Carrier Frequency 900 MHz,  $C_{LPF} = 0$

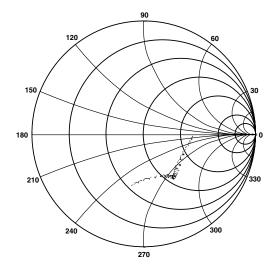

TPC 28. Input Impedance,  $Z_0 = 50 \Omega$ , Differential Drive

TPC 29. Change in  $V_{REF}$  vs. Temperature, 3 Sigma to Either Side of Mean

TPC 30. V<sub>REF</sub> Distribution

#### CHARACTERIZATION SETUP

#### Equipment

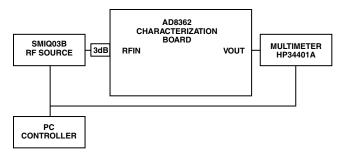

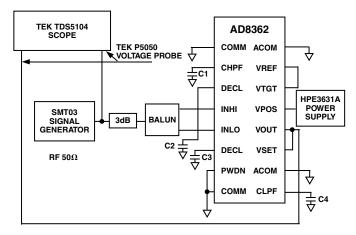

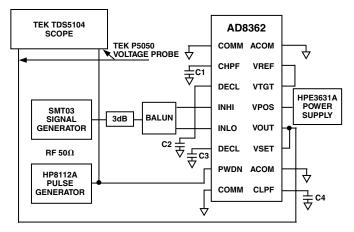

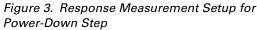

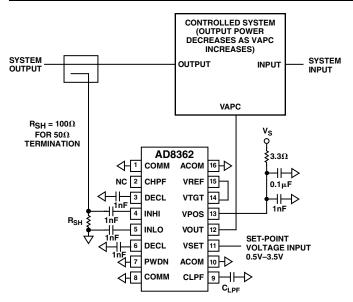

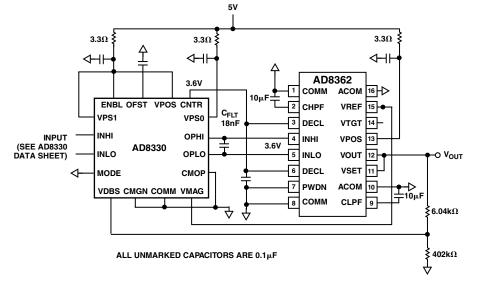

The general hardware configuration used for most of the AD8362 characterization is shown in Figure 1. The signal source used was a Rohde & Schwarz SMIQ03B. A 1:4 balun transformer was used to transform the single-ended RF signal to differential form. For the response measurements in TPC 23 and TPC 24, the configuration shown in Figure 2, was used for TPC 25 and TPC 26 the configuration shown in Figure 3 was used, and for TPC 27 the configuration shown in Figure 4 was used.

Figure 1. Primary Characterization Setup

#### Analysis

The slope and intercept are derived using the coefficients of a linear regression performed on data collected in its central operating range. Error is stated in two forms: error from linear response to CW waveform, and output delta from 25°C performance.

The error from linear response to CW waveform is the decibel difference in output from the ideal output defined by the conversion gain and output reference. This is a measure of the linearity of the device response to both CW and modulated waveforms. The error in dB is calculated by subtracting the ideal voltage, i.e., slope times the input level plus the intercept, from the actual input level and dividing this quantity by the slope. Error from linear response to CW waveform is not a measure of absolute accuracy, since it is calculated using the slope and intercept of each device. However, it verifies the linearity and effect of modulation on the device response. Error from 25°C performance uses the performance of a given device and waveform type as the reference; it is predominantly a measure of output variation with temperature.

Figure 2. Response Measurement Setup for Modulated Pulse

Figure 4. Response Measurement Setup for Gated Supply

#### CIRCUIT DESCRIPTION

The AD8362 is a fully calibrated, high accuracy, rms-to-dc converter providing a measurement range of over 60 dB and capable of operation from signals as low in frequency as a few Hertz to at least 2.7 GHz. Unlike earlier rms-to-dc converters, the response bandwidth is completely independent of the signal magnitude. The -3 dB point occurs at about 3.5 GHz. The capacity of this part to accurately measure waveforms having a high peak-to-rms ratio (crest factor) is independent of either the signal frequency or its absolute magnitude, over a wide range of conditions.

This unique combination allows the AD8362 be to used with equal ease as a calibrated RF wattmeter covering a power ratio of >1,000,000:1, as a power controller in closed-loop systems, or as a general-purpose rms-responding voltmeter, and in many other low frequency applications.

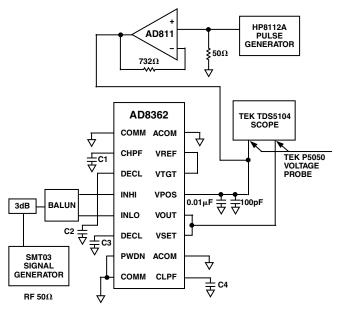

Figure 5. Basic Structure of the AD8362

It is essentially the core elements of a high performance AGC loop (Figure 5), laser-trimmed during manufacture to close tolerances while fully operational at a test frequency of 100 MHz. Its linear, wideband, variable gain amplifier (VGA) provides a general voltage gain,  $G_{SET}$ ; this may be controlled in a precisely exponential (linear-in-dB) manner over the full 68 dB range from -25 dB to +43 dB by a voltage  $V_{SET}$ . However, to provide adequate guard-banding, only the central 60 dB of this range, from -21 dB to +39 dB is normally used. Later, it will be shown how this basic range may be shifted either up or down, and even extended to >80 dB. The VGA gain has the form

$$G_{SET} = G_O \exp\left(-V_{SET} / V_{GNS}\right) \tag{1}$$

where  $G_O$  is a basic fixed gain and  $V_{GNS}$  is a scaling voltage that defines the gain slope (the "dB-change-per-volt"). Note that the gain decreases with  $V_{SET}$ . The VGA output is

$$V_{SIG} = G_{SET} V_{IN} = G_O V_{IN} \exp(V_{SET} / V_{GNS})$$

<sup>(2)</sup>

where  $V_{IN}$  is the ac voltage applied to the input terminals of the AD8362.

As will later be explained more fully, the input drive may be either single-sided or differential, but optimum performance at high frequencies will be realized only when using a differential input drive. The effect of HF imbalances when using a singlesided drive is less apparent at low frequencies (say, from 50 Hz to 500 MHz), but the peak input voltage capacity is always halved relative to differential operation (see USING THE AD8362).

#### **Square-Law Detection**

The output of the variable-gain amplifier,  $V_{SIG}$ , is applied to a wideband square law detector that provides a true-rms response to this alternating signal that is essentially independent of wave-form up to crest-factors of 6. Its output is a fluctuating current,  $I_{SQU}$ , having a positive mean value. This current is integrated by an on-chip capacitance,  $C_F$ ; this will usually be augmented by an external capacitance, CLPF, to extend the averaging time. The resulting voltage is buffered by a gain-of-5 dc-coupled amplifier, whose rail-to-rail output,  $V_{OUT}$ , may be used either for measurement or control purposes.

In most applications, the AGC loop is closed via the set-point interface pin, VSET, to which the VGA gain-control voltage  $V_{SET}$  is applied. In measurement modes, the closure is direct and local, by a simple connection from the output Pin VOUT to VSET. In controller modes, the feedback path is around some larger system, but the operation is basically the same.

The fluctuating current  $I_{SQU}$  is balanced against a fixed set-point target current,  $I_{TGT}$ , using current mode subtraction. With the exact integration provided by the capacitor(s), the AGC loop equilibrates when

$$MEAN(I_{SOU}) = I_{TGT}$$

(3)

The current  $I_{TGT}$  is provided by a second "reference" squaring cell, whose input is the amplitude-target voltage  $V_{ATG}$ . This is a fraction of the voltage  $V_{TGT}$  applied to a special interface that accepts this input at pin VTGT. Since the two squaring cells are electrically identical, and are carefully implemented in the IC, process and temperature-dependent variations in the detailed behavior of the two square-law functions cancel.

Accordingly,  $V_{TGT}$  (and its fractional part  $V_{ATG}$ ) determines the output that must be provided by the VGA in order for the AGC loop to settle. Since the scaling parameters of the two squarers are accurately matched, it follows that Equation 3 will only be satisfied when

$$MEAN\left(V_{SIG}^{2}\right) = V_{ATG}^{2}$$

$$\tag{4}$$

In a formal solution, one would then extract the square-root of both sides to provide an explicit value for the root-mean-square (rms) value. However, it is apparent that by forcing this identity, through varying the VGA gain, and extracting the mean value by the filter provided by the capacitor(s) the system inherently establishes the relationship

$$rms(V_{SIG}) = V_{ATG} \tag{5}$$

Substituting the value of  $V_{SIG}$  from Equation 2, we have

$$rms[G_{O}V_{IN} exp(-V_{SET}/V_{GNS})] = V_{ATG}$$

(6)

As a measurement device,  $V_{IN}$  is the unknown quantity and all other parameters can be fixed by design. Solving (6):

$$ms[G_O V_{IN} / V_{ATG}] = exp(V_{SET} / V_{GNS})$$

<sup>(7)</sup>

$V_{SET} = V_{GNS} \log \left[ rms \left( V_{IN} \right) / V_Z \right]$ (8)

r

so

The quantity  $V_Z = V_{ATG}/G_0$  is defined as the intercept voltage, since  $V_{SET}$  must be zero when rms  $(V_{IN}) = V_Z$ .

When connected as a measurement device, the output of the buffer is tied directly to VSET, which closes the AGC loop. Making the substitution  $V_{OUT} = V_{SET}$ , and changing the log base to ten, as needed in a decibel conversion, we have

$$V_{OUT} = V_{SLP} \log_{10} \left[ rms(V_{IN}) / V_Z \right]$$

(9)

where  $V_{SLP}$  is the slope voltage, that is, the change in output voltage for each decade of change in the input amplitude. (Note in passing that  $V_{SLP} = V_{GNS} \log (10) = 2.303 V_{GNS}$ ). In the AD8362,  $V_{SLP}$  is laser-trimmed to 1 V using a 100 MHz test signal. Since a decade corresponds to 20 dB, this slope may also be stated as 50 mV/dB. It is later shown how the effective value of  $V_{SLP}$  may be altered by the user.

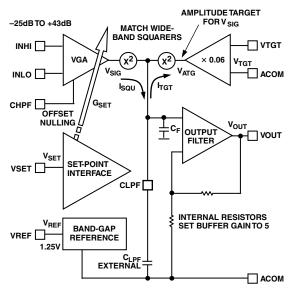

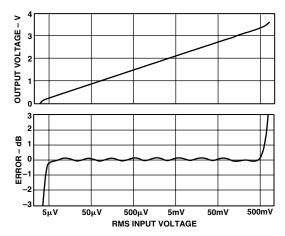

Likewise, the intercept  $V_Z$  is also laser-trimmed to 316  $\mu$ V (-70 dBV). In an ideal system  $V_{OUT}$  would cross zero for an rms input of that value. In a single-supply realization of the function,  $V_{OUT}$  cannot run fully down to ground; here,  $V_Z$  is the extrapolated value. In measurement modes the output ranges from 0.5 V for  $V_{IN} = 1$  mV (inputs are stated as rms values, outputs as dc values), up to a voltage 60 dB  $\times$  50 mV/dB = 3 V above this for  $V_{IN} = 1$  V, that is, to 3.5 V. Figure 6 shows the ideal form of Equation 9 scaled as in the AD8362.

Figure 6. Ideal Response of the AD8362

#### Effect of Input Coupling on the Intercept Value

Reductions of  $V_{\rm IN}$  due to coupling losses directly affect  $V_Z$ . In high frequency applications several factors contribute to the coupling of the source into the IC, including the board and package resonances and attenuation. Any uncertainties in the input impedance will result in the intercept expressed in power terms, which is nominally –57 dBm for a 50  $\Omega$  system, being less accurately determined than when stated in dBV (that is, in pure voltage) terms. On the other hand, the slope  $V_{\rm SLP}$  is unaffected by all such impedance or coupling uncertainties.

#### **Offset Elimination**

To address the small dc offsets that arise in the variable-gain amplifier, an offset-nulling loop is used. The high-pass corner frequency of this loop is internally preset to 1 MHz, sufficiently low for most HF applications. When using the AD8362 in LF applications, it can be reduced as needed by the addition of a capacitor from Pin CHPF to ground having a nominal value of 200  $\mu$ F/Hz. For example, to lower the high-pass corner

frequency to 150 Hz, a capacitance of  $0.33 \,\mu\text{F}$  is required. The offset voltage varies depending on the actual gain at which the VGA is operating, and thus, on the input signal amplitude.

Baseline variations of this sort are a common aspect of all VGAs, although more evident in the AD8362 because of the method of its implementation, which causes the offsets to ripple along the gain axis with a period of 6.33 dB. When an excessively large value of  $C_{\rm HPF}$  is used, the offset correction process may lag the more rapid changes in the VGA's gain, which may increase the time required for the loop to fully settle for a given steady input amplitude.

#### Voltage versus Power Calibration

The AD8362 can be used as an accurate rms voltmeter from arbitrarily low frequencies to microwave frequencies. For low frequency operation, the input is usually specified either in volts rms, or in dBV (decibels relative to 1 V rms). Driven differentially, the specified input range in dBV runs from -60 dBV to 0 dBV (1 mV to 1 V rms). In these terms, the intercept is at -70 dBV.

At high frequencies, signal levels are commonly specified in power terms. In these circumstances, the source and termination impedances are an essential part of the overall scaling. To set the AD8362's input impedance to 50  $\Omega$ , it is necessary to add a resistor of 66.7  $\Omega$  across the internal 200  $\Omega$  differential input impedance of the IC. (This is discussed further in later sections). For this condition, the intercept occurs at a nominal power level of -57 dBm, and  $V_{OUT}$  can be stated in this way:

$$V_{OUT} = \left(P_{IN} + 57\right) \times 50 \ mV/dB \tag{10}$$

where  $P_{IN}$  is expressed in dBm. For example, an input of -30 dBm will generate an output of 1.35 V.

#### Effect of Signal Waveform

The measurement accuracy of an rms-responding device is ideally unaffected by the waveform of the input signal. This is a valuable asset in wideband CDMA systems, and in many other modulation modes, where there is a significant amount of random variation of the RF carrier amplitude at baseband frequencies. The high accuracy of the AD8362 in such cases is indicated by the Performance Curves and in the Specifications pages. Note that at low frequencies, it is customary to provide a specification of measurement errors due to waveform effects as a function of the crest factor,  $\sigma$ , rather than in terms of a system-specific modulation mode.

When measuring signals whose waveforms have high but brief peak values (that is, having high crest factors), these peaks may be clipped, causing a reduction in the apparent value of the input being measured. This issue is discussed further in connection with the detailed description of the input system.

#### **Operation at Low Frequencies**

In conventional rms-to-dc converters, based on junction techniques, the effective signal bandwidth is proportional to the signal amplitude. For a '1 MHz' rms-to-dc converter, this is the full-scale bandwidth. However, at an input 60 dB below full-scale, the bandwidth could be as low as 1 kHz. In sharp contrast, the 3.5 GHz bandwidth of the VGA in the AD8362 is independent of its gain; and since this amplifier is internally dc-coupled, the system can also be used as a high accuracy rms voltmeter at low frequencies, retaining its temperature-stable decibel-scaled output, for example, in seismic, audio, and sonar instrumentation. In such cases, the input coupling capacitors should be large enough that the lowest frequency components of the signal which are to be included in the measurement are minimally attenuated. For example, for a 3 dB reduction at 1.5 kHz, capacitances of 1  $\mu$ F are needed, since the input resistance is 100  $\Omega$  at each input pin, (200  $\Omega$  differentially), and we calculate 1/( $2\pi \times$ 1.5 k $\Omega \times 100$ ) = 1  $\mu$ F. Also, to lower the high pass corner frequency of the VGA, a capacitor of value 200  $\mu$ F-Hz should be used between the Pin CHPF and ground; to provide a similar 1.5 kHz high-pass corner, a capacitor of 33 nF should be used.

#### Time-Domain Response of the Closed Loop

The external low-pass averaging capacitance,  $C_{LPF}$ , added at the output of the squaring cell, will be chosen to provide adequate filtering of the fluctuating detected signal. The optimum value depends on the application; as a guideline a value of roughly 900 nF-Hz should be used. For example, a capacitance of 5  $\mu$ F will provide adequate filtering down to 180 Hz. Note that the fluctuation in the quasi-dc output of a squaring cell operating on a sinewave input is a raised-cosine at twice the signal frequency, easing this filtering function.

In the standard connections for the measurement mode, Pin VSET is tied to VOUT. For small changes in input amplitude (a few decibels), the time-domain response of this loop will be essentially linear, with a 3 dB low-pass corner frequency of nominally  $f_{LP} = 1/(C_{LPF} \times 1.1 \text{ k}\Omega)$ . Internal time delays around this local loop set the minimum recommended value of this capacitor to about 300 pF, giving  $f_{LP} = 3$  MHz.

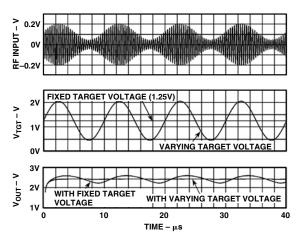

When large and abrupt changes of input amplitude occur, the loop response becomes nonlinear and exhibits slew rate limitations. Further, due to the fundamentals of a system using transconductance squaring cells, as employed in the AD8362, the slewing is asymmetric for increasing and decreasing inputs. Figure 7 shows typical waveforms for  $V_{OUT}$  for three value of  $V_{IN}$ , using  $C_{LPF} = 1$  nF.

Figure 7. Typical Large-Signal Response

The most satisfactory way to quantify slew-rate limitations is by considering the peak currents that can be generated by the squaring cells. During a fast increase in input level, the peak current into the integrating (loop filter) capacitance,  $C_{LPF}$ , is approximately 2.5 mA. The actual value depends on several factors, including the size of the step, and extremes in chip temperature. The voltage across the 1 nF capacitor will thus increase at a rate of nominally 2.5 V/µs. Since the output buffer has a gain of 5, the output slew rate will be 12.5 V/µs. The peak rate persists up to a point about 10 dB below the final value, after which the response gradually converges on the linear-system response, as noted above.

On the other hand, during a fast decrease in input level, the peak current in  $C_{LPF}$  in the opposite (discharging) direction is much smaller: it is roughly 25  $\mu$ A. Thus, the slew rate for  $V_{OUT}$  in the descending direction is only about 0.125 V/ $\mu$ s for  $C_{LPF}$  = 1 nF. To discharge over the full 3 V range (a 60 dB reduction of input) requires a time interval of ~24  $\mu$ s. These figures are verified in the results shown in Figure 7.

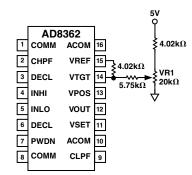

#### Alteration of the Internal Target Voltage

The AD8362 incorporates several features which extend its versatility. One of these is the ability to alter the "target" voltage. As noted, the output of the VGA is forced to a value set by the internal bias voltage ( $V_{STP} = 0.06 \times V_{TGT}$ ) applied to the reference squaring cell. It is normally set to 75 mV dc, by connecting VTGT to the 1.25 V reference voltage at Pin VREF. However, it may optionally be varied from 0 V up to ±0.24 V (±4 V at VTGT). Note that the sign of this input is unimportant, since it is internally squared.

By lowering  $V_{SPT}$ , the output of the VGA needed to balance the output currents of the two matched squaring cells will be similarly lowered. This reduces the intercept in precisely the same ratio. Thus, if we halve the set-point target voltage by halving the voltage applied to Pin VTGT, the intercept moves to the left (to a smaller input level) by 6.02 dB. This effectively doubles the measurement system's sensitivity.

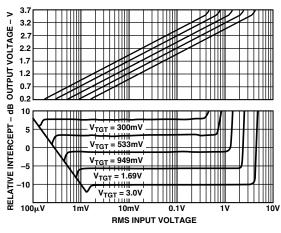

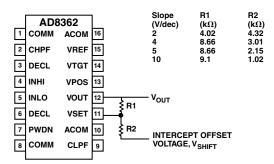

Furthermore, because the signal amplitude needed to drive the squaring cell is halved, the output stage of the VGA now has twice the dynamic headroom (before clipping), and can handle waveforms having crest-factors that are twice as large. Figure 8 shows the overall response for an illustrative set of values of VTGT = 0.3 V, 0.533 V, 0.949 V, 1.687 V, and 3.0 V. While this will usually be a fixed dc voltage, it can also be a time-varying, unipolar or bipolar voltage, in which case the overall operation is rather more complex. For example, when  $V_{TGT}$  is derived from  $V_{OUT}$  the dynamic range can be extended to over 80 dB. Examples of such uses of this feature are presented later.

Figure 8. Response with  $V_{TGT}$  Varied from 0.3 V to 3 V in 5 dB Steps, Showing the Proportional Shift in Intercept

#### Effects at Each End of Dynamic Range

All AGC loops have a limited minimum and maximum input beyond which the system cannot respond correctly. However, the output of a well-behaved system will be in error in such a way as to avoid anomalous measurements. For an input below its minimum capability, the output should not "turn around," to falsely indicate a higher input value; for inputs above its maximum capability, the output should not "fold over," and return to some lower value.

The actual behavior of the AD8362 under these conditions can be seen in the set of plots in Figure 8, the lower panel of which shows the deviation from the ideal response with a slope of 50 mV/dB. For inputs below a certain level, corresponding to the point at which the VGA is operating at its maximum gain, its output can no longer meet the rms amplitude target set by  $V_{TGT}$ , so the output moves quickly to its minimum value, in an attempt to provide the needed extra gain. As  $V_{TGT}$  is altered, the corresponding end-limit voltage moves to the left or right.

On the other hand, when the input is above a certain upper limit, where the VGA gain has been driven to its minimum gain, any further increase will drive its output well above the target voltage needed to balance the loop, and the resulting integration of this internal error signal causes  $V_{OUT}$  to rise abruptly. In either case, this output takes on a safe value, and does not fold back under any conditions.

The dynamic range, the "dB distance" between these limits, is not basically dependent on VTGT. The middle line in the plots of Figure 8 (VTGT = 0.949 V), extends from 0.5 mV to 1.5 V between the  $\pm 1\%$  error points; the dynamic range is thus slightly over 68 dB. For other values of V<sub>TGT</sub>, this basic 68 dB range just moves to the left or the right.

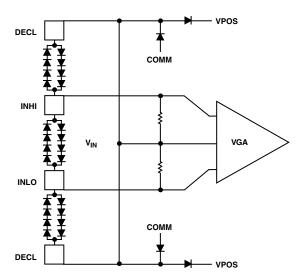

Figure 9. Input Protection at INHI and INLO Pins

#### Input Protection

Like all robust ICs, the AD8362 requires input protection against high voltage transients at the input (ESD), but the techniques normally employed for this purpose, based on breakdown diodes from the input Pins INHI and INLO to the supply Pins VPOS and COMM cannot be used here, since this raises the risk of excessive signal coupling to internal nodes at the upper end of the frequency range, due to feedthrough in the capacitances of these diodes. Package inductances cause all internal nodes, including the supply and common lines, to have a significant impedance back to the external ground plane; even small disturbances on these nodes can cause anomalous operation.

This risk is particularly evident since the main amplifier in the AD8362's VGA (an advanced X-AMP<sup>®</sup>) operates at full gain under all conditions, while the signal input is variably attenuated. Since this attenuation may be as high as 70 dB, very small feedthrough effects in the 0.5 GHz–3 GHz range can have a pronounced impact on measurement accuracy.

Figure 9 shows the protection method used. The multiple diodes arranged in back-to-back pairs limit the voltage swing on the input pins by clamping to the two DECL pins, which form a common ac low impedance node for the attenuators, independently grounded via two external capacitors. The HF currents in the capacitances of these diodes are thus shunted directly to a signal null-point.

An unavoidable consequence of this method is that the diodes will forward-conduct when the input amplitude is sufficient. This is not an all-or-nothing effect, of course; they shunt the input progressively as the signal increases. This conduction will be strongest at high temperatures, when the forward drop voltage of these diodes is lowest. The overall consequence is that high amplitude peaks will be clamped, to a greater or lesser degree. This will affect the measurement accuracy at the top extreme of the dynamic range whenever the signal waveform has a high crest factor. These effects are, of course, included in the overall performance specifications.

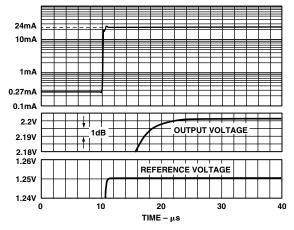

#### **Power-Enable Response Time**

The operating and stand-by currents for the AD8362 at  $27^{\circ}$ C are 24 mA and 275  $\mu$ A, respectively; their variations versus temperature are shown in TPC 31. The power-down mode is activated by a logic HI on Pin PWDN. When the shut-down feature is used, the normal operating conditions are restored relatively quickly when this pin is taken LO.

Figure 10 shows typical response times for a midscale signal ( $V_{IN} = 50 \text{ mV}$ ). The output rises to within 0.1 dB of its steadystate value in about 20 µs; the reference voltage is available to full accuracy in a much shorter time. This "wake-up" response will vary in detail depending on the input coupling means and the capacitances  $C_{DEC}$ ,  $C_{HPF}$ , and  $C_{LPF}$ . These results are for a measurement system operating in the 0.8 GHz to 2 GHz range, balun-coupled at the input port, with CDEC = 1 nF, CHPF = 0, and CLPF = 1 nF.

Figure 10. Typical "Wake-up" Response;  $t_0 = 10 \,\mu s$

#### **USING THE AD8362**

The AD8362 requires a single supply of nominally 5 V; its performance is essentially unaffected by variations of up to  $\pm 10\%$ , the range over which the stated specifications apply. Supplies as low as 2.7 V may be used with some loss of performance at high inputs and at temperature extremes.

The AD8362 is disabled by a logic HI on the PWDN pin, which may be directly grounded for continuous operation, when the supply current at  $27^{\circ}$ C is nominally 24 mA and essentially independent of supply voltage. When powered down by a LO on PWDN, the supply current is reduced to about 275  $\mu$ A.

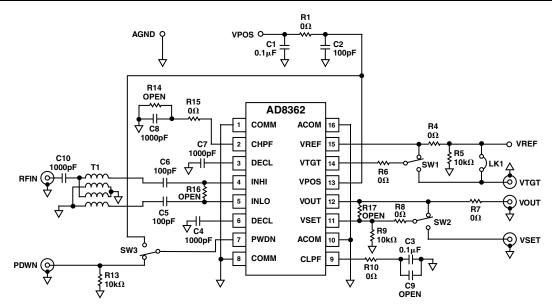

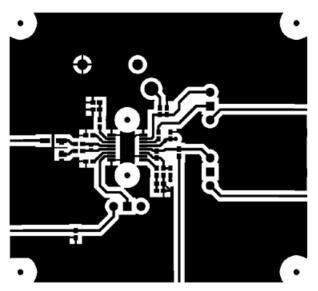

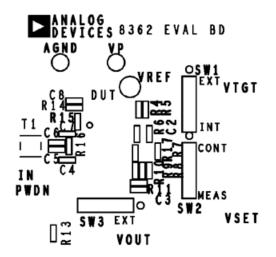

#### **Basic Connections**

The supply is connected to Pin VPOS, using the decoupling network shown in Figure 11, whose capacitors must provide a low impedance over the full frequency range of the input, and should be placed as close as possible to the VPOS pin. Two different capacitors are used in parallel to reduce the overall impedance, since these will have different resonant frequencies. However, the measurement accuracy is not critically dependent on supply decoupling, since the high frequency signal path is confined to the relevant input pins. It is more important that the lead lengths to INHI and INLO, and in the decoupling capacitors from both of the DECL pins to ground, and the connections from COMM to the ground plane all use the shortest possible connections.

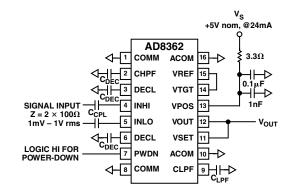

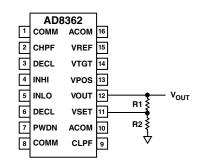

Figure 11. Basic Measurement Mode Connections

#### MAIN MODES OF OPERATION

Both measurement and controller modes are supported by the AD8362. Typical connections for the Measurement mode, which may also be viewed as the "RMS Voltmeter" mode, are also illustrated in Figure 11. The output,  $V_{OUT}$ , is proportional to the logarithm of the rms magnitude of the input signal (that is, a "linear-on-dB" response). When used in an accurately known system impedance (but only then), the output is a scaled decibel measurement of the power represented by the input voltage.

The choice of the capacitances  $C_{CPL}$ ,  $C_{DEC}$ ,  $C_{HPF}$ , and  $C_{LPF}$ , will depend on the lowest frequency to be included in the measurement spectrum. The default values shown support operation down to 100 Hz. Using a large enough value of  $C_{LPF}$ (10 µF) to ensure sufficient filtering at this low input frequency, the response time is approximately 20 ms over most of the dynamic range. In high frequency applications, this capacitor will be much smaller, and will usually be chosen to minimize the responsetime, consistent with well-behaved large-signal behavior. In this figure,  $C_{HPF}$  is also shown as 10 µF, to lower the high-pass corner to about 90 Hz. However, no capacitor will be needed here in most HF applications, since the internally-set high-pass corner is at about 2 MHz.

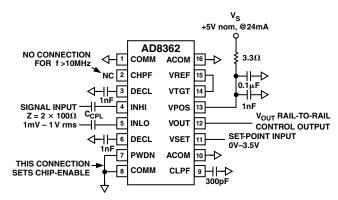

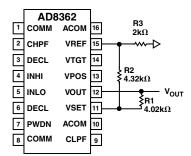

Now briefly comparing the controller mode, illustrated in Figure 12, the AD8362 is here used to monitor the output of a variable-gain (or variable output power) signal processing element, frequently a power amplifier, and adjust its output to a desired target value (the set-point), under the control of VSET. In this mode, its function is somewhat like an RF comparator. With the path from VOUT to VSET broken, any input larger than the corresponding set-point causes V<sub>OUT</sub> to rail to its maximum value (which might loosely be viewed as a logic HI). For inputs smaller than the set-point, the controller's output will fall to a near-ground level (logic LO). Using the AD8362 simply as a threshold detector, this viewpoint may be useful, but in most applications it is an oversimplification. The AD8362 will invariably operate with the control loop closed, either locally, with VOUT connected to VSET (as in measurement mode), or globally, via some external nonlinear element (as in controller mode).

Figure 12. Basic Controller Mode Connections

Controller mode operation is more closely analogous to that of a classical proportional/integral/derivative (PID) loop. The error corresponding to the decibel deviation from the set-point is integrated, by current into a capacitor (the sum of the internal and external capacitance  $C_{LPF}$ ), until such deviation is nulled. This action provides the fundamental proportional part of the loop response (although  $V_{OUT}$  has decibel scaling). The Q of this system can be adjusted to minimize the loop response time by including a resistor in series with  $C_{LPF}$ , generating a transmission zero, which provides the derivative term of a standard PID loop.

As a simple example, assume that the AD8362 operates at an input power level of -20 dBm re:  $50 \Omega$ . Connected in the Measurement mode it will generate a VOUT of 2.00 V (since this input is 40 dB above the intercept at -60 dBm, and is scaled 50 mV/dB. Rearranged to the controller mode, with exactly this voltage now externally applied to Pin VSET, the loop forces VOUT to the control voltage required by the gain element to provide a power sample of -20 dBm.

Of course, any control loop of this sort will only operate correctly if VSET corresponds to a power level (or a small sample of such) than can actually be provided by the external gain element. When this is a power amplifier, the inclusion of the required amount of RF attenuation ensures this condition. In certain instrumentation situations, it may be necessary to provide some low noise gain ahead of the AD8362's input.

These two primary modes of use of are now discussed in more detail, with emphasis on practical considerations.

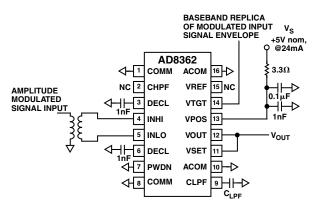

Figure 13. Connections for RF Power Measurement

#### **OPERATION IN MEASUREMENT MODES**

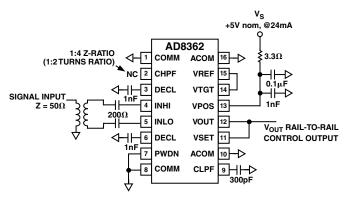

Figure 13 shows the general connections for operating the AD8362 as an RF power detector, more correctly viewed as an accurate measurement system. The full performance potential of this part, particularly at very high frequencies (above 500 MHz) will only be realized when the input is presented to the AD8362 in differential (balanced) form. In this illustrative example, a flux-coupled transformer is used at the input. Having a 1:4 impedance ratio, (1:2 turns ratio) the 200  $\Omega$  differential input resistance of the AD8362 becomes 50  $\Omega$  at the input to the transformer, whose outputs can be connected directly to INHI and INLO. If a center-tapped transformer is used, connect the tap to the DECL pins, which are biased to the same potential as the inputs (~3.6 V). Over the 0.9 GHz-2.2 GHz range a transmission line transformer ("balun") may be used, as explained later. (The evaluation board is supplied with a M/A-COM ETC1.6-4-2-3, 0.5 GHz-2.5 GHz, 4:1 balun).

The output in this mode of use is a continuous, decibel-scaled voltage:

$$V_{OUT} = \left(P_{IN} \ P_Z\right) \times 50 \ mV / dB \tag{11}$$

ranging from about 0.5 V to 3.5 V. The equivalent input power  $P_{IN}$  is expressed in dBm, (decibels above 1 mW) in a particular system impedance, which in this case is 50  $\Omega$ . The intercept,  $P_{Z}$ , is that input power for which the back-extrapolated output crosses zero. Expressed as a voltage it is 0.447 mV rms (-67 dBV, laser-calibrated at 100 MHz), corresponding to a P<sub>Z</sub> of -60 dBm in 200  $\Omega$ . However, the 1:2 turns ratio of the transformer halves the required input voltage, which moves the intercept down by 6 dB, to 0.224 mV rms (-73 dBV) at the transformer's input.

Impedance mismatches and attenuation in the coupling elements will significantly affect the intercept position. This error will be stable over temperature and time, and thus can be removed during calibration in a specific system. The logarithmic slope of 50 mV/dB varies only slightly with frequency; corrected values for several common frequencies are provided in the Specifications.

#### Law Conformance Error

In practice, the response will deviate slightly from the ideal straight line suggested by Equation 11. This deviation is called the "law conformance error." In defining the performance of high accuracy measurement devices, it is customary to provide plots of this error. In general terms, it is computed by extracting the best straight line to the measured data using linear regression over a substantial region of the dynamic range, and under clearly specified conditions.

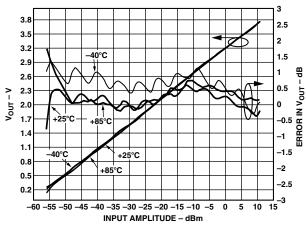

Figure 14. Output Voltage and Law Conformance Error, at  $T_A = -40^{\circ}C$ ,  $+25^{\circ}C$  and  $+85^{\circ}C$

Figure 14 shows the output of the circuit of Figure 13 over the full input range. The agreement with the ideal function (law conformance) is also shown. This was determined by linear regression on the data points over the central portion of the transfer function (35 mV to 250 mV rms) for the 25°C data. The error at  $+25^{\circ}$ C,  $-40^{\circ}$ C, and  $+85^{\circ}$ C was then calculated by subtracting the ideal output voltage at each input signal level from the actual output, and dividing this quantity by the mean slope of the regression equation to provide a measurement of the error in decibels (scaled on the right-hand axis of Figure 14).

The error curves generated in this way reveal not only the deviations from the ideal transfer function at a nominal temperature, but also all of the additional errors caused by temperature changes. Notice there is a small temperature-dependence in the intercept (the vertical position of the error plots); this variation is within 0.5 dB at high powers.

Figure 14 further reveals that there is a periodic ripple in the conformance curves. This is due to the interpolation technique used to select the signals from the attenuator, not only at discrete tap points, but anywhere in between, thus providing continuous attenuation values. The selected signal is then applied to the 3.5 GHz, 40 dB fixed gain amplifier in the remaining stages of the AD8362's VGA.

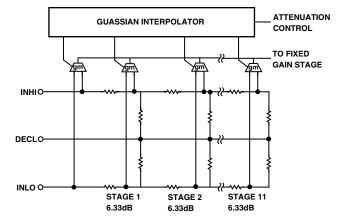

An approximate schematic of the signal input section of the AD8362 is shown in Figure 15. The ladder attenuator is composed of a eleven sections (twelve taps), each of which progressively attenuates the input signal by 6.33 dB. Each tap is connected to a variable-transconductance cell, whose bias current determines the signal weighting given to that tap. The interpolator determines which stages are active, by generating a discrete set of bias currents, each having a Gaussian profile. These are arranged to move from left to right, thereby determining the attenuation applied to the input signal, as the gain is progressively lowered over the 69.3 dB range under control of the VSET input. The detailed manner in which the transconductance of adjacent stages varies, as the "virtual tap point" slides along the attenuator, accounts for the ripple observed in the conformance curves. Its magnitude is slightly temperature-dependent, and also varies with frequency (see TPCs 3–5). Notice that the system's responses to signal inputs at INHI and INLO are not completely independent: these pins do not constitute a fully floating differential input.

Figure 15. Simplified Input Circuit

#### Alternative Input Coupling Means

The input stages of the AD8362 are optimally driven from a fully-balanced source, which should be provided wherever possible. The ac low side of both halves of the attenuator internally connect to the DECL pin, which is therefore the RF signal low terminal for both INHI and INLO. In many cases, unbalanced sources can be applied directly to one or the other of these two pins. The chief disadvantage of this driving method is a reduction in dynamic range, particularly at very high frequencies.

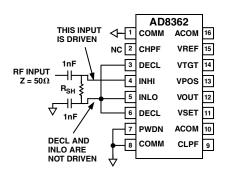

#### Figure 16. Input Coupling from a Single-Ended Source

Figure 16 illustrates one of many ways of coupling the signal source to the AD8362. Since the input pins are biased to about 3.6 V (for  $V_S = 5$  V) dc-blocking capacitors are required when driving from a grounded source. For signal frequencies >5 MHz, a value of 1 nF is adequate. While either INHI or INLO may be used, the former is chosen here, and INLO is connected to the low side of the source. The resistor RSH is not needed if a 100  $\Omega$  termination is acceptable. The corresponding intercept will still be -67 dBV, that is, 447  $\mu$ V rms. However, specified in power terms re: 100  $\Omega$ , the P<sub>Z</sub> is now at 2 nW, or -57 dBm.

For a source termination of 50  $\Omega$ , the internal 100  $\Omega$  from INHI to DECL must be shunted by a chip resistor of 100  $\Omega$ . At high frequencies, a low attenuation pad at the input will improve the VSWR. For example, with a resistor of  $R_{SH} = 33 \Omega$  and an added resistor of 25  $\Omega$  from the source to INHI, a termination of 50  $\Omega$  is provided, with 6 dB of attenuation, raising the intercept to -48 dBm.

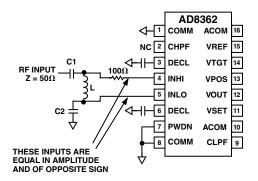

#### Use of a Narrow-Band Input Match

While transformers offer the simplest method for providing single-sided to balanced conversion, a good alternative is the use of a specially designed narrow-band LC network, shown in

Figure 17, which also provides an input match. Using this basic formulation, the match is to 50  $\Omega$ , with a voltage gain of 1.5 (3.56 dB) from the input connector to the AD8362. This network is specially designed to provide a high degree of amplitude balance at INHI and INLO, as well as an exact phase inversion. The narrow-band match provides a useful degree of frequency selectivity, and the capacitors also serve to provide the required dc blocking.

Figure 17. Narrow Band Reactive Input Coupling

The network can readily be scaled to other frequencies by varying the product LC, while keeping the ratio L/C constant to preserve a 50  $\Omega$  input impedance. Table I provides some spot values; these take into account the reactive Z<sub>IN</sub> of the AD8362.

Table I. Suggested Components for Narrow-Band 50  $\Omega$  Match

| Frequency<br>(MHz) | L<br>(nH) | C1<br>(pF) | C2<br>(pF) |

|--------------------|-----------|------------|------------|

| 1                  | 21850     | 2230       | 2765       |

| 2                  | 10925     | 1115       | 1383       |

| 5                  | 4370      | 446        | 553        |

| 10                 | 2185      | 223        | 276        |

| 20                 | 1093      | 112        | 138        |

| 50                 | 437       | 45         | 55         |

| 100                | 220       | 22         | 27         |

| 200                | 100       | 10         | 12         |

| 500                | 40        | 3.9        | 4.7        |

This coupling method can be used down to much lower frequencies than shown in Table I, simply by multiplying the 1 MHz component values proportionally. The effects of the reactive components of the AD8362's inputs above 500 MHz may require some fine-tuning of the suggested values, and in the gigahertz region the input coupling will usually be more effectively implemented using a balun.

#### Uncertainties in R<sub>IN</sub> and Power Calibration

In all these cases where a 50  $\Omega$  to 200  $\Omega$  transformation is implemented, the voltage gain is only nominally  $\times 2$  (6 dB). This ideal is impaired by the fact that the input resistances of the AD8362 are not precise: variations of  $\pm 20\%$  can be expected from lot to lot. Therefore, it is necessary to use a calibration step whenever an accurate value for the power intercept,  $P_Z$ , must be established.

When driven differentially, a significant improvement in intercept accuracy can be achieved by shunting the 200  $\Omega$  resistance from INHI to INLO with a 66.5  $\Omega$  resistor, to set the differential input resistance to 50  $\Omega$ . Assuming a tolerance of  $\pm 20\%$  for the basic R<sub>IN</sub> and  $\pm 1\%$  for the chip resistor, the net input resistance could exhibit an error of  $\pm 2.5\%$ . The resulting error in P<sub>Z</sub> (and thus in the absolute power measurement) may vary from -0.26 dB to +0.21 dB.

These precautions regarding input impedance do not apply when the input is presented in voltage form, as will often be the case at low frequencies, or when the source impedance is low compared to 200  $\Omega$ . For example, using a feedback amplifier as an impedance buffer ahead of the input, as in the later example of Figure 24, the loss at the interface at moderate frequencies is negligible.

#### Choosing the Right Value of CHPF and CLPF

The AD8362's 3.5 GHz variable gain amplifier includes an offset cancellation loop, which introduces a high-pass filter effect in its transfer function. The corner frequency,  $f_{HP}$  of this filter must be below that of the lowest input signal in the desired measurement bandwidth frequency in order to properly measure the amplitude of the input signal. The required value of the external capacitor is given by

$$C_{HPF} = 200\,\mu F \big/ f_{HP} \left( f_{HP} \text{ in } Hz \right) \tag{12}$$

Thus, for operation at frequencies down to 100 kHz,  $C_{HPF}$  should be 2 nF.