# Agilent AMMC-6120 8-20 GHz Output x2 Active Frequency Multiplier

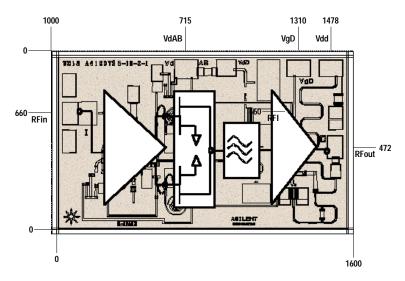

Chip Size:  $1600 \times 1000 \ \mu m \ (64 \times 40 \ mils)$  Chip Size Tolerance:  $\pm 10 \ \mu m \ (\pm 0.4 \ mils)$  Chip Thickness:  $100 \pm 10 \ \mu m \ (4 \pm 0.4 \ mils)$  Pad Dimensions:  $120 \times 80 \ \mu m \ (5x3 \pm 0.4 \ mils)$

## Description

Agilent's AMMC-6120 is an easyto-use x2 active frequency multiplier MMIC designed for commercial communication systems. Though capable of doubling to 24 GHz with reduced fundamental suppression, the MMIC is designed to take a 4 to 10 GHz input and double it to 8 to 20 GHz. It has integrated output amplifier, matching harmonic suppression, and bias networks. The input/output are matched to  $50 \Omega$  and fully DC blocked. The MMIC is fabricated using PHEMT technology. The backside of this die is both RF and DC ground.

This helps simplify the assembly process and reduces assembly related performance variations and costs. This MMIC is a cost effective alternative to bulky hybrid FET and diode doublers that require high input drive power, have high C.L. and poor fundamental suppression.

#### **Features**

- Input frequency range: 4-10 GHz

- Broad input power range: -3 to +6 dBm

- Output power: +14 dBm (Pin = +2 dBm)

- · Fundamental Suppression of 25 dBc

- 50  $\Omega$  Input and Output Match

- Supply bias of -1.2 V, 4.5 V and 85 mA

## **Applications**

- · Microwave radio systems

- Satellite VSAT, DBS Up/Down Link

- · LMDS & Pt-Pt mmW Long Haul

- Broadband Wireless Access (including 802.16 and 802.20 WiMax)

- WLL and MMDS loops

- · Commercial grade military

## AMMC-6120 Absolute Maximum Ratings<sup>[1]</sup>

| Symbol           | Parameters/Conditions                    | Units | Min. | Max. |

|------------------|------------------------------------------|-------|------|------|

| $\overline{V_d}$ | Positive Drain Voltage                   | V     |      | 7    |

| $\overline{V_g}$ | Gate Supply Voltage                      | V     | -3.0 | 0.5  |

| I <sub>d</sub>   | Drain Current                            | mA    |      | 120  |

| P <sub>in</sub>  | CW Input Power                           | dBm   |      | 15   |

| T <sub>ch</sub>  | Operating Channel Temp.                  | °C    |      | +150 |

| T <sub>stg</sub> | Storage Case Temp.                       | °C    | -65  | +150 |

| T <sub>max</sub> | Maximum Assembly Temp.<br>(60 sec. max.) | °C    |      | +300 |

### Note:

1. Operation in excess of any one of these conditions may result in permanent damage to this device.

Attention: Observe precautions for handling electrostatic sensitive devices. ESD Machine Model (Class A)

ESD Human Body Model (Class 0)

Refer to Agilent Application Note A004R: Electrostatic Discharge Damage and Control.

# AMMC-6120 DC Specifications/Physical Properties<sup>[1]</sup>

| Symbol                    | Parameters and Test Conditions                                                          | Units | Min. | Тур. | Max. |

|---------------------------|-----------------------------------------------------------------------------------------|-------|------|------|------|

| I <sub>d</sub>            | Drain Supply Current (under any RF power drive and temperature) $(V_d = 4.5 \text{ V})$ | mA    | 80   | 85   | 105  |

| $\overline{V_g}$          | Gate Supply Operating Voltage                                                           | V     | -1.5 | -1.2 | -1.0 |

| $\overline{	heta_{ch-b}}$ | Thermal Resistance <sup>[2]</sup> (Backside Temperature, T <sub>b</sub> = 25°C)         | °C/W  |      | 25   |      |

#### Notes:

- 1. Ambient operational temperature  $T_A = 25^{\circ}C$  unless otherwise noted.

- 2. Channel-to-backside Thermal Resistance ( $\theta_{ch-b}$ ) = 26°C/W at  $T_{channel}$  ( $T_c$ ) = 34°C as measured using infrared microscopy. Thermal Resistance at backside temperature ( $T_b$ ) = 25°C calculated from measured data.

## AMMC-6120 RF Specifications [3,4,5]

$T_A = 25^{\circ}C$ ,  $V_d = 4.5$  V,  $I_{d(\Omega)} = 85$  mA,  $Z_o = 50$   $\Omega$

| Symbol            | Parameters and Test Conditions                           | Units  | Minimum | Typical | Maximum | Sigma |

|-------------------|----------------------------------------------------------|--------|---------|---------|---------|-------|

| Fin               | Input Frequency                                          | GHz    |         | 4 to 10 |         |       |

| Fout              | Output Frequency                                         | GHz    |         | 8 to 20 |         |       |

| Po                | Output Power <sup>[4]</sup>                              | dBm    | 11.5    | 14      |         | 0.6   |

| Fo                | Fundamental Isolation (referenced to Po)                 | dBc    | 18      | 25      |         | 1.8   |

| 3Fo               | 3 <sup>rd</sup> Harmonic Isolation<br>(referenced to Po) | dBc    |         | 25      |         | 2.5   |

| P <sub>-1dB</sub> | Input Power at 1dB Gain Compression                      | dBm    |         | +1      |         |       |

| RLin              | Input Return Loss <sup>[6]</sup>                         | dB     |         | -15     |         |       |

| RLout             | Output Return Loss <sup>[6]</sup>                        | dB     |         | -9      |         |       |

| SSB               | Single Sideband Phase Noise<br>(100 KHz offset)          | DBc/Hz | :       | -135    |         |       |

### Notes:

- 3. Small/Large -signal data measured in wafer form  $T_A = 25$ °C.

- 4. 100% on-wafer RF test is done at Pin = +2 dBm, output frequency = 9, 16, and 20 GHz.

- 5. Specifications are derived from measurements in a 50-Ω test environment. Aspects of the multiplier performance may be improved over a more narrow bandwidth by application of additional matching.

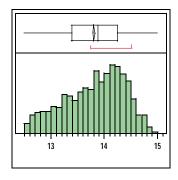

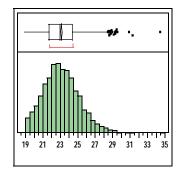

# Typical Distribution of Pout, $2^{nd}$ -Harmonic & $3^{rd}$ -Harmonic Suppression (Fin = 10 GHz, Pin = 0 dBm). Based on 1800 parts sampled over several production lots.

2Fo Pout (dBm) @ 20-GHz

Fo-Suppression (dBc) @ 10-GHz

3Fo-Suppression(dBc) @ 30-GHz

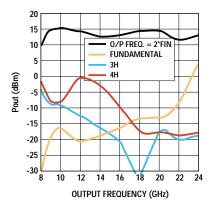

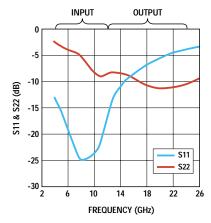

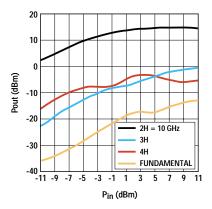

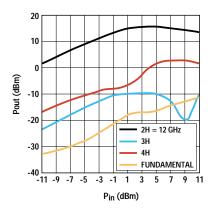

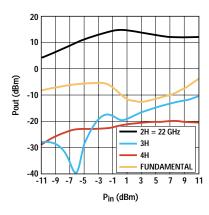

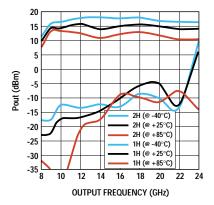

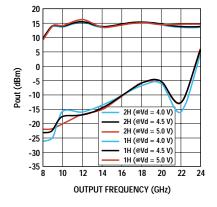

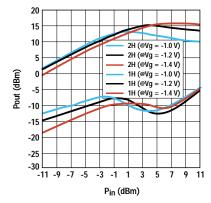

AMMC-6120 Typical Performances ( $T_A = 25^{\circ}\text{C}$ ,  $V_d = 4.5 \text{ V}$ ,  $I_D = 85 \text{ mA}$ ,  $V_g = -1.2 \text{ V}$ ,  $Z_{in} = Z_{out} = 50 \Omega$  unless otherwise stated) Note: These measurements are in  $50 \Omega$  test environment. Aspects of the amplifier performance may be improved over a narrower bandwidth by application of additional conjugate, linearity or low noise ( $\Gamma$ opt) matching.

15 14 13 12 11 10 Pin = 0 dBmPin = +2 dBmPin = +4 dBmPin = +6 dBm10 12 14 16 18 20 22 24 **OUTPUT FREQUENCY (GHz)**

Figure 1. Typical output power against fundamental,  $3^{rd}$ , and  $4^{th}$  harmonic suppression ( $P_{in}=+2$  dBm) vs. frequency.

Figure 2. Typical output power at different fundamental input power vs. frequency.

Figure 3. Typical input and output return loss.

Figure 4. Typical output power against fundamental,  $3^{rd}$ , and  $4^{th}$  harmonic suppression vs.  $P_{in}$  (2H = 10 GHz).

Figure 5. Typical output power against fundamental,  $3^{rd}$ , and  $4^{th}$  harmonic suppression vs.  $P_{in}$  (2H = 12 GHz).

Figure 6. Typical output power against fundamental,  $3^{rd}$ , and  $4^{th}$  harmonic suppression vs.  $P_{in}$  (2H = 22 GHz).

Figure 7. Typical output power and fundamental suppression vs. temperature.

Figure 8. Typical output power and fundamental suppresion vs. Vd.

Figure 9. Typical Pout and fundamental suppression vs. Vg (Fout = 16 GHz).

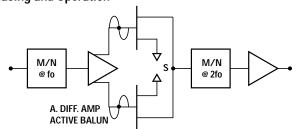

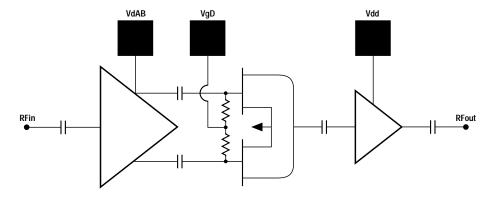

### **Biasing and Operation**

The frequency doubler MMIC consists of a differential amplifier circuit that acts as an active balun. The outputs of this balun feed the gates of balanced FETs and the drains are connected to form the single-ended output. This results in the fundamental frequency and odd harmonics canceling and the even harmonic drain currents (in phase) adding in superposition. Node 'S' acts as a virtual ground. An input matching network (M/N) is designed to provide good match at fundamental frequencies and produces high impedance mismatch at higher harmonics.

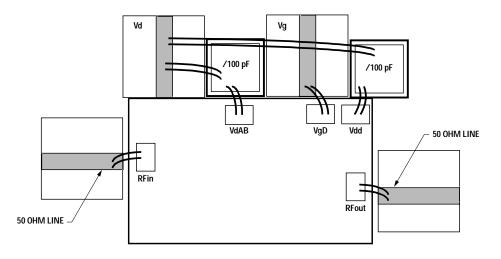

AMMC-6120 is biased with a single positive drain supply and single negative gate supply using separate bypass capacitors. It is normally biased with the drain supply connected to both the VdAB and the Vdd bond pads and the gate supply connected to the VgD bond pad. It is important to bypass both VdAB and Vdd with 100 pF capacitors placed as close to the die as possible. Typical bias connections are shown in Figure 12. For most of the application it is recommended to use a Vg = -1.2 Vand Vd = 4.5 V.

The AMMC-6120 performance changes very slightly with Drain (Vd) and Gate bias (Vg) as shown in Figure 8 and 9. Minor improvements in performance are possible for output power or fundamental suppression by optimizing the Vg from -1.0 V to -1.4 V and/or Vd from 4.0 to 5.0 V.

The RF input and output port are AC coupled thus no DC voltage is present at either ports. However, the RF output port has a internal output-matching circuit that presents a DC short. Proper care should be taken while biasing sequential circuit to AMMC-6120 as it might cause DC short (use a DC block if sub sequential circuit is not AC coupled). No ground wires are needed since ground connections are made with plated through-holes to the backside of the device.

Refer the Absolute Maximum Ratings table for allowed DC and thermal conditions.

## **Assembly Techniques**

The backside of the MMIC chip is RF ground. For microstrip applications the chip should be attached directly to the ground plane (e.g. circuit carrier or heatsink) using electrically conductive epoxy<sup>[1]</sup>.

For best performance, the topside of the MMIC should be brought up to the same height as the circuit surrounding it. This can be accomplished by mounting a gold plate metal shim (same length and width as the MMIC) under the chip which is of correct thickness to make the chip and adjacent circuit the same height. The amount of epoxy used for the chip and/or shim attachment should be just enough to provide a thin fillet around the bottom perimeter of the chip or shim. The ground plan

should be free of any residue that may jeopardize electrical or mechanical attachment.

The location of the RF bond pads is shown in Figure 11. Note that all the RF input and output ports are in a Ground-Signal-Ground configuration.

RF connections should be kept as short as reasonable to minimize performance degradation due to undesirable series inductance. A single bond wire is normally sufficient for signal connections, however double bonding with 0.7 mil gold wire or use of gold mesh<sup>[2]</sup> is recommended for best performance, especially near the high end of the frequency band.

Thermosonic wedge bonding is the preferred method for wire attachment to the bond pads. Gold mesh can be attached using a 2 mil round tracking tool and a tool force of approximately 22 grams and a ultrasonic power of roughly 55 dB for a duration of  $76\pm 8$  mS. The guided wedge at an ultrasonic power level of 64 dB can be used for 0.7 mil wire. The recommended wire bond stage temperature is  $150\pm 2^{\circ}$ C.

Caution should be taken to not exceed the Absolute Maximum Rating for assembly temperature and time.

The chip is 100 µm thick and should be handled with care. This MMIC has exposed air bridges on the top surface and should be handled by the edges or with a custom collet (do not pick up the die with a vacuum on die center).

This MMIC is also static sensitive and ESD precautions should be taken.

### Notes:

- 1. Ablebond 84-1 LM1 silver epoxy is recommended.

- 2. Buckbee-Mears Corporation, St. Paul, MN, 800-262-3824

Figure 10. AMMC-6120 simplified schematic.

Figure 11. AMMC-6120 bonding pad locations.

Figure 12. AMMC-6120 assembly diagram.

## **Ordering Information:**

AMMC-6120-W10 = 10 devices per tray AMMC-6120-W50 = 50 devices per tray

# www.agilent.com/semiconductors

For product information and a complete list of distributors, please go to our web site.

For technical assistance call:

Americas/Canada: +1 (800) 235-0312 or

(916) 788-6763

Europe: +49 (0) 6441 92460 China: 10800 650 0017 Hong Kong: (+65) 6756 2394

India, Australia, New Zealand: (+65) 6755 1939 Japan: (+81 3) 3335-8152 (Domestic/International), or 0120-61-1280 (Domestic Only)

Korea: (+65) 6755 1989

Singapore, Malaysia, Vietnam, Thailand, Philippines, Indonesia: (+65) 6755 2044

Taiwan: (+65) 6755 1843

Data subject to change.

Copyright © 2005 Agilent Technologies, Inc.

February 18, 2005

5989-2290EN