# NJ88C50 Dual Low Power Frequency Synthesiser

The NJ88C50 is a low power integrated circuit, designed as the heart of a fast locking PLL subsystem in a mobile radio application. It is manufactured on Mitel Semiconductor 1.4 micron double polysilicon CMOS process, which ensures that low power and low noise performance is achieved. The device contains two synthesisers, one for the generation of VHF signals up to 125MHz and a second for UHF (when used with a mulitmodulus prescaler such as the SP8713/14/15). The main synthesiser has the capability of driving a dual speed loop filter and also can perform Fractional-N interpolation. Both synthesisers use current source outputs from their phase detectors to minimise external components. Various sections may be powered down for battery economy.

#### **FEATURES**

- 30MHz main synthesiser

- 125MHz auxiliary synthesiser

- Programmable output current from phase detector - up to 10mA

- · High input sensitivity

- Fractional-N interpolator

- Supports up to 4 modulus prescalers

- SSOP package

#### **APPLICATIONS**

- NMT, AMPS, ETACS cellular

- · GSM, IS-54, RCR-27 cellular

- DCS1800 microcellular

- DLMR, DSRR, TETRA

- DECT, PHP cordless telephones

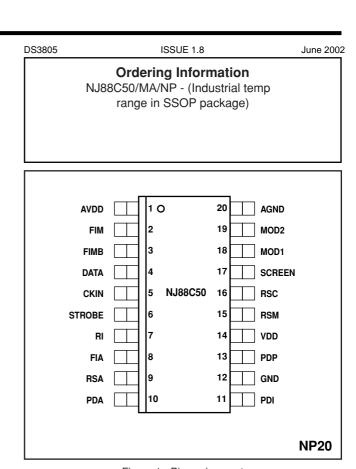

# Figure 1 - Pin assignment

#### **ABSOLUTE MAXIMUM RATINGS**

| Storage temperature   |  |

|-----------------------|--|

| Operating temperature |  |

| Supply voltage        |  |

| Voltage on any pin    |  |

-55°C to +150°C -40°C to +85°C -0.5 to 7.0V -0.3V to (V<sub>DD</sub> + 0.3V)

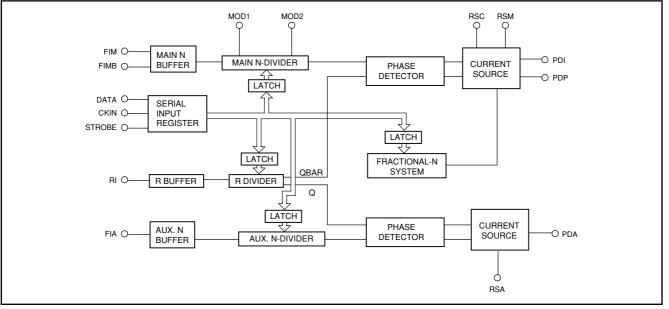

Figure 2 - Simplified block diagram

# Architecture

Fig.2 shows a simplified block diagram of the NJ88C50, a more detailed description of each block and its function is given later in this datasheet.

The synthesiser consists of the following blocks

- 35MHz reference frequency input buffer

- 35MHz programmable reference divider

- 125MHz Auxiliary synthesiser input buffer

- 125MHz Auxiliary synthesiser programmable divider

- Auxiliary synthesiser phase detector with current source outputs

- 30MHz main synthesiser input buffer (differential inputs)

- 30MHz main synthesiser programmable divider and control logic

- Main synthesiser Fractional-N interpolation system

- Main synthesiser phase detector with dual current source outputs

| Pin | Name   | Function                                                                                                                                                       |

|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | AVDD   | Analog supply pin (nominally 5V).                                                                                                                              |

| 2   | FIM    | Main synthesiser balanced input buffer, may be used with single ended prescaler output if Fimb<br>is biased.                                                   |

| 3   | FIMB   | Main synthesiser balanced input buffer, may be used with balanced prescaler output, or biased for single ended operation.                                      |

| 4   | DATA   | Serial input for programming data.                                                                                                                             |

| 5   | CKIN   | Serial clock input for programming bus.                                                                                                                        |

| 6   | STROBE | Program enable pin, active low.                                                                                                                                |

| 7   | RI     | Master reference frequency input, should be a.c coupled from an accurate source.                                                                               |

| 8   | FIA    | Auxiliary synthesiser frequency input, should be a.c coupled.                                                                                                  |

| 9   | RSA    | Current setting resistor connection defining auxiliary phase detector output current.                                                                          |

| 10  | PDA    | Tristate current output from auxiliary phase detector.                                                                                                         |

| 11  | PDI    | Tristate current output from the main synthesiser's phase detector giving integral control.                                                                    |

| 12  | GND    | Digital ground supply pin.                                                                                                                                     |

| 13  | PDP    | Tristate current output from the main synthesiser's phase detector giving proportional control.                                                                |

| 14  | VDD    | Digital supply pin (nominally 5V).                                                                                                                             |

| 15  | RSM    | Current setting resistor connection defining main synthesiser's phase detector output currents.                                                                |

| 16  | RSC    | Current setting resistor connection defining the compensation current for fractional-N ripple<br>elimination in the main synthesiser's current source outputs. |

| 17  | SCREEN | To be connected to ground to provide isolation of the modulus control pins from RF interference.                                                               |

| 18  | MOD1   | Modulus control pin (see truth table).                                                                                                                         |

| 19  | MOD2   | Modulus control pin (see truth table).                                                                                                                         |

| 20  | AGND   | Analog ground supply pin.                                                                                                                                      |

# **PIN Description**

It is recommended that power supply pins are well decoupled to minimise power rail born interference.

### **Functional Description**

The NJ88C50 has been designed using a modular concept, and its operation can be best summarised as these component blocks.

#### **Reference divider**

The reference divider is used to provide the reference signals needed for both the main and auxiliary synthesiser phase detectors. The divider allows for a twelve bit number to be loaded, via the serial bus, to select the required division ratio. Division ratios of 3 to 4095 can be used.

The reference divider input stage will accept a low level, AC coupled, sinewave input. It is anticipated that in most systems this will be provided by a stable reference source up to 35MHz, and so encompasses all the common TCXO (temperature controlled crystal oscillator) frequencies, such as 9.6, 12.8, 13.0, 19.44 and 26MHz.

A standby mode is supported so that the reference divider can be powered down, this is achieved using two of the serial program control bits.

To reduce the possibility of unwanted interaction between the main and auxiliary synthesisers, the charge pumps do not take current at the same time. To achieve this the output of the reference divider has a duty factor of approximately 50:50, which then allows the Q and QBAR taps to be used for the auxiliary and main synthesisers respectively. By doing this the current pulses can be taken alternatively, minimising modulation of the power supply rails as current is drawn.

The reference divider consists of a 12 bit programmable divider followed by a 4 bit binary counter. This 4 bit counter gives a choice of divide by M, 2M, 4M or 8M.

A pair of programmable control bits are used to determine which of the divide by M, 2M, 4M or 8M outputs is supplied to the auxiliary synthesiser's phase detector and a further pair of control bits are used to determine which are supplied to the main synthesiser's phase detector.

#### Auxiliary synthesiser

The auxiliary synthesiser operates over an input frequency range from 1 to 125MHz, without the use of an external prescaler. The synthesiser consists of a 12 bit N divider and a digital phase comparator with current source outputs. The reference frequency is supplied by the shared reference divider. Current source outputs allow a passive loop filter to be used.

When the auxiliary synthesiser is not in use, a standby mode is supported so that power consumption is reduced. This is achieved using one of the serial program control bits.

The divider is programmed with a 12 bit word allowing division ratios of 3 to 4095 to be used.

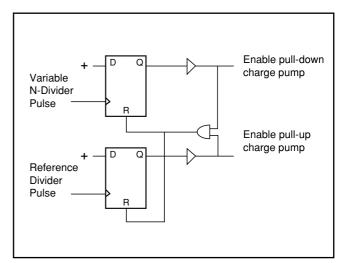

The auxiliary phase detector consists of the 2 D-type phase and frequency detector shown in Figure.3 below, the high and low outputs of which drive on-chip, opposing complementary charge pumps. This type of phase detector design eliminates non linearity or deadband around the zero phase error (locked) condition. The charge pump output current level is set by an external resistor on the RSA pin (pin 9) up to a limit of  $250\mu$ A +/-10%. A pull up current pulse will indicate that the VCO frequency must be increased, whilst a pull down pulse indicates that the frequency must be decreased.

Figure 3 - Auxiliary phase detector

#### Main Synthesiser

The main synthesiser is capable of operating at frequencies up to 30MHz. The synthesiser uses the 12 bit reference divider, shared with the auxiliary synthesiser, a 12 bit up/down N divider and a digital phase comparator with current source outputs.

The device also has a number of features which increase the design flexibility and performance of the synthesiser. These include fractional-N operation, speed up mode and support of 2, 3 and 4 modulus prescalers. A description of the operation and advantages of each of these features is given.

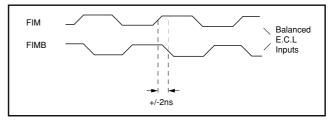

The main N divider input buffer will accept inputs from an external prescaler, either as balanced (2 wire) ECL levels at frequencies up to 30MHz, or DC coupled to a single ended prescaler output. Single ended operation requires the other buffer input (pin 3) to be externally biased to the correct slicing voltage for the prescaler and also externally decoupled.

If the inputs are in the form of balanced ECL levels, there must not be a skew of greater than 2ns between one input changing and the second input changing. The relationship of the signals is shown below in Fig.4.

Figure 4 - Maximum input skew

The main N divider is programmable so that it can determine how many cycles of each division ratio the external prescaler will perform.

The total division ratio of the output from the system VCO to the synthesiser's phase detector may be expressed as  $N_{TOT}$  and R1, R2, R3 and R4 are the available prescaler ratios and N1, N2, N3 and N4 are the corresponding number of cycles for each ratio selected, within one complete division cycle.

The divider is programmed via the serial data bus and the values needed to be programmed for each of the possible prescaler ratios are as follows:-

In 2 modulus mode (division ratios R1, R2)

#### NTOT = N1.R1 + N2.R2

Programmed values needed:

N1 - a 12 bit value giving the number of times R1 is to be used N2 - a 8 bit value giving the number of times R2 is to be used

In 3 modulus mode (division ratios R1, R2, R3) Nтот = N1.R1 + N2.R2 + N3.R3 Programmed values needed:

N1 - a 12 bit value giving the number of times R1 is to be used N2 - a 4 bit value giving the number of times R2 is to be used N2+N3 - a 4 bit value where N3 is the number of times R3 is to be used and (N2+N3) is modulo-16 addition

## In 4 modulus mode (division ratios R1, R2, R3, R4) Nтот = N1.R1 + N2.R2 + N3.R3 + N4.R4

Programmed values needed:

N1 - a 12 bit value giving the number of times R1 is to be used N2 - a 4 bit value giving the number of times R2 is to be used N2+N3 - a 4 bit value where N3 is the number of times R3 is to be used.

N2+N3+N4 - a 4 bit value where N4 is the number of times R4 is to be used. (N2+N3) and (N2+N3+N4) are modulo-16 addition.

To facilitate the use of multimodulus prescalers the N divider is based upon a twelve bit up/down counter which functions as follows

The first value, N1, is loaded into the counter which then counts down from N1 to zero. During this time, the modulus ratio R1 is selected.

When the counter reaches zero modulus R2 is selected and the counter then counts up to the N2 value. If 2 modulus operation is chosen, the counter is then reloaded with N1 and the count is repeated.

For operation with 3 or 4 modulus devices, the counter continues to count up once it has reached the N2 value. The count continues to the N2+N3 value and during this time the R3 ratio is selected. In the 3 modulus case, when the N2+N3 value is reached the counter is then reloaded with the N1 value and the modulus ratio R1 is selected.

For 4 modulus operation the counter will continue its count up to the N2+N3+N4 value before reloading the N1 value. During this time the R4 modulus is selected.

If N2, N3, or N4 are set to zero this will give a full count of 16 for the corresponding modulus.

The N divider block also has a special control line from the Fractional-N logic. When required this control will cause the total division ratio to be increased from N to N+1. This is achieved by forcing a cycle which would have normally used a prescaler ratio R1 to use ratio R2 instead. R1 and R2 are chosen so that R2 equals R1+1.

Further explanation of the operation of the synthesiser when using 2, 3 or 4 modulus prescaler is given in the section on multimodulus division (page 8).

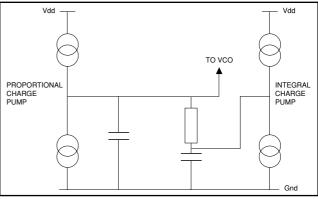

The phase detector used on the main synthesiser is similar to the type used on the auxiliary synthesiser (Figure.3). In this case, however, the detector will drive two pairs of complimentary charge pumps, one of which is intended to drive the loop integrator capacitor to provide integral control, whilst the other provides proportional control for the VCO. This system is shown in Fig 5, and has applications where fast locking of the loop is required.

Figure 5 - Loop filter using both charge pumps

#### **Modes of Operation**

#### Normal Mode

The synthesiser will operate in normal mode while the strobe line of the serial data bus is low. In this mode the following current levels are produced. The charge pump providing the proportional feedback term will have a normal current level designated by lprop(0), that is set by an external bias resistor, RSM. lprop(0) will vary when different N-divider ratios are programmed, so that it is proportional to the total division ratio. To avoid the necessity of computing the total division ratio on chip, an eight bit number representing the most significant bits of Ntot will be loaded via the serial data bus. lprop(0) is therefore given by

#### Iprop(0) = CN.Ibo

where CN is the loaded eight bit number and the value Ibo is scaled from the external current setting resistor RSM where Ibo = Irsm/32. Typically Ibo =  $1\mu$ A ,and therefore Iprop(0) will have a maximum value equal to  $255\mu$ A.

The normal value of Iprop, Iprop(0), is obtained while the strobe line of the serial programming bus is held low. In this condition, the second charge pump providing the integral feedback term is inactive.

#### Speed up Mode

a value lprop(1), where

In speed up mode the loop bandwith during switching is increased to allow faster initial frequency acquisition. This is done by using the dual phase detector outputs (PDP and PDI) connected to a standard passive loop filter as shown in fig.5. The effect of this is to increase the loop gain and hence the bandwidth while maintaining a constant phase margin when switching between speed up mode and normal mode.

The synthesiser operates in speed up mode when the strobe line goes high loading either word A or word A2 (see programming section Page 8-Page 9) and it will stay in this mode until the strobe line goes low. In this mode the following current levels are produced. The charge pump providing the

$lprop(1) = 2^{L+1}$  .lprop(0)

proportional feedback will increase its current from lprop(0) to

where L is a two bit number loaded as part of the serial programming data. Iprop(1) will therefore be 2, 4, 8 or 16 times Iprop(0). The charge pump supplying Iprop is specified up to a value of 1mA.

Also when the strobe line goes high loading word A or word A2, the charge pump providing the integral feedback term becomes active at a current level lint given by

where K is a four bit number loaded as part of the serial programming data. Although lint can be programmed to be 240 times greater than lprop(0), the charge pump supplying lint is only specified up to a value of 10mA.

For all charge pumps, a pull-up current indicates the VCO frequency should be increased while a pull-down current indicates the VCO frequency should be decreased.

For the proportional and integral charge pumps, the selected pulse current levels will remain substantially constant over the charge pumps output voltage ranges tabulated in the electric characteristics. "Substantially constant" means that the current will not have changed by more than 10% of the value measured at 2.5 volts on the output.

### FRACTIONAL-N OPERATION

Conventional, non fractional-N synthesisers have a frequency resolution or step size equal to the phase detector comparison frequency. Fractional-N refers to a technique which allows finer frequency steps to be obtained.

The synthesised frequency with a conventional synthesiser is equal to N times the phase detector comparison frequency, where N is the programmable integer loop divide

ratio. Using fractional-N the value of N is alternated between N and N+1 in order to simulate a fractional part. For example 9000.375 would be simulated by alternating between 9000 and 9001 in the pattern

9000, 9000, 9001, 9000, 9000, 9001, 9000, 9001 (mean value of 9000.375).

On the NJ88C50 the fractional-N circuit consists of an accumulator which can be set to overflow at a value of 5 or 8 (FMOD in programming word D, see page 9). The value in the accumulator, A, is incremented once every comparison cycle of the main phase detector and every time the accumulator overflows the total division ratio of the synthesiser and prescaler is increased from N to N+1. To obtain the pattern described above N=9000 and FMOD would be set to mod8 and the incremental value, NF(programmed in word A) would be set to 3. The accumulator would then behave as shown below.

| Increment | Accumulator | Total Division |

|-----------|-------------|----------------|

| Value     | Value       | Ratio          |

| 3         | 3           | 9000           |

| 3         | 6           | 9000           |

| 3         | 1           | 9001           |

| 3         | 4           | 9000           |

| 3         | 7           | 9000           |

| 3         | 2           | 9001           |

| 3         | 5           | 9000           |

| 3         | 0           | 9001           |

Varying NF allows different fractions to be obtained. If NF=1 and FMOD=8 the accumulator would overflow once in every 8 cycles giving a value of 9000.125. Similarly if NF=4 the accumulator overflows every other cycle giving 9000.5.

For a given step size this increase in resolution means a higher comparison frequency at the phase detector, and therefore a lower overall division ratio. For example,

> with a step size = 200kHz and carrier frequency = 900MHz

Non fractional-N synthesiser Comparison frequency=200kHz Division ratio=900MHz=4500 200kHz

Fractional-N synthesiser (using 5ths) Comparison frequency=1MHz Division ratio=900MHz=900 \_\_1MHz

In most applications the phase noise is proportional to the overall division ratio. Therefore fractional-N gives lower phase noise. This higher comparison frequency and lower phase noise allows circuits to be built with wider loop bandwidths while keeping the same stability. This means that phase locked loops (PLLs) can be made to either switch faster for a given phase noise or be quieter for a given switching speed, compared to conventional designs.

However the alternation between the N and N+1 values causes a ripple in the output frequency. This ripple is not desirable in radio frequency synthesisers. This ripple or jitter waveform is predictable from the pattern of N and N+1 values and so can be cancelled.

The instantaneous accumulator value, A, is proportional to the cumulative frequency error caused by ignoring the fractional part during the periods of the divide by N. The accumulator value, A, may therefore be used to generate a waveform corresponding to the jitter waveform, that is then used to cancel the jitter out of the phase detector. This jitter compensation current pulse is equal to A.Icomp where Icomp represents the step size as A is incremented.

Corresponding to the two alternative values of lprop, lprop(0) and lprop(1), lcomp will take the values lcomp(0) and lcomp(1). lcomp is always pull-up, and the magnitude of its steps for perfect jitter compensation are related to the value of lprop by the factors

0 , 1/Q.Ntot , 2/Q.Ntot , 3/Q.Ntot ....... Q-1/Q.Ntot where Q = accumulator modulus in use (5 or 8) Since

Iprop(0) = CN.lbo

CN is an approvimation to Ntat aport

and CN is an approximation to Ntot apart from a scaling factor, the value of lcomp(0) required becomes independent of Ntot and its steps are

0, 1/Q, 2/Q, 3/Q ...... Q-1/Q times Ibo.(scaling factor)

where scaling factor = Max. value of CN to be used Corresponding max. value of Ntot

| therefore | $lco = 1 \times CN(max)$                  | x Ibo |

|-----------|-------------------------------------------|-------|

|           | Q <u>Ntot(max)</u>                        |       |

|           | $\underline{\mathbf{Q}}$ <u>Nioi(max)</u> |       |

and Icomp(0) = A.Ico

where Ico is scaled from the external current setting resistor RSC.

lco = lrsc/128.

Typically Ntot(max) might be 10000, with CN(max)=250 and Q=8, so the current step will be of magnitude lbo/320. Since lbo is only 1 uA, this is a very small value; however this value only applies if Icomp is a continuous current. Icomp however will be a short current pulse coincident with the Iprop pulse, in order to cancel jitter components over the widest possible frequency range.

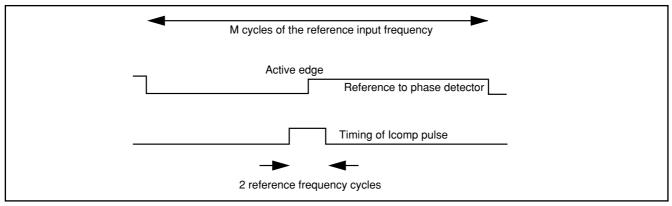

When the duty factor of lcomp is taken into account, its pulse value may be increased accordingly. Icomp is therefore generated as a pulse of fixed width equal to two periods of the input reference clock frequency, with a timing that straddles the active edge of the reference divider output pulse supplied to the main phase detector, as shown below: (Fig 6).

Since the duty factor of lcomp is 2/M and depends on the value of M programmed, it is possible to set the peak pulse value of lcomp(0) by means of the external current setting resistor RSC to correspond with the value of M intended, the value of 'scaling factor' defined above, the accumulator modulus Q and the value of lbo set by the other current setting resistor.

therefore  $Ico = 1 \times Nmax \times M \times Ibo$ <u>Q</u> <u>Ntot(max)</u> <u>2</u>

This gives a typical value for Ico of  $0.1\mu A$ .

The two values of lcomp, lcomp(0) and lcomp(1) are related by

$$lcomp(1) = 2^{L+1} . lcomp(0)$$

Icomp(0) occuring when the strobe line is low and Icomp(1) occuring when the strobe line is high loading either WORDA or WORDA2 (see programming section, page 8 and 9).

Corresponding to the pull-up pulse lcomp(1) that is added to the proportional charge pump pulse lprop(1), there is also a pull-up current pulse lcomp2 which is added to the integral charge pump pulse lint. This pulse lcomp2 only applies when the stobe line is high (loading either WORDA or WORDA2). When the strobe line is low there will be no lint or lcomp2 pulses. The value of lcomp2 is given by

#### Icomp2 = Icomp(1).K

where K is a four bit number entered as part of the serial programming data.

Figure 6

#### MULTIMODULUS DIVISION

The NJ88C50 supports the use of 2, 3 and 4 modulus prescalers. Two modulus prescalers such as the SP8714/15 are commonly used in PLLs. Additional information on using 2 modulus prescalers can be found in application note AN132 in the GEC Plessey Semiconductors Personal Communications handbook (May 1992).

When using a 2 modulus prescaler (R/R+1) the minimum division ratio above which all channels can be synthesised is given by

Minimum division ratio = R(R-1)

eg. for a 64/65 prescaler such as the SP8714/15

Minimum division ratio = 64(64-1) = 4032

When fractional-N operation is being used higher comparison frequencies are used, which are obtained by using lower division ratios. Use of a 3 or 4 modulus prescaler allows the minimum division ratio to be lowered.

For a 3 modulus prescaler (R/R+1/R+A)

Minimum division ratio = R(R+A+1)+A<u>A</u>

eg. for a 64/65/72 prescaler such as the SP8713

Minimum division ratio = 64(64+8+1)+8 = 1096

For a 4 modulus prescaler (R/R+1/R+A/R+B)

Minimum division ratio =

$$R(A+B+R+1)+A+B$$

A B

eg. for a 64/65/68/80 prescaler

Minimum division ratio =

$$64(4+16+64+1)+4+16 = 852$$

4 16

An example of where three modulus division would be implemented is given below.

The system in which the synthesiser is to operate has a lowest carrier frequency of 900MHz and a channel spacing of 30kHz. However due to the lock up time requirements fractional-N operation is being used in its 8ths mode (see section on fractional-N operation), giving a comparison frequency of  $30kHz \times 8 = 240kHz$ .

Therefore,

Minimum division ratio required =

$$900 \times 10^6 = 3750$$

240 \times 10^3

If a 64/65 prescaler is used not all the channels will be selectable as the minimum required division ratio is less than the minimum allowable division ratio (4032).

If a 64/65/72 prescaler is used all the channels will now be selectable as the minimum required division ratio will now be greater than the minimum allowable division ratio (1096).

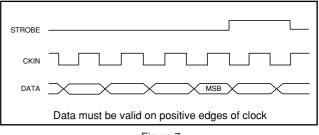

#### SERIAL DATA BUS

The data needed to program the synthesiser is entered via a high speed (10MBit/s) 3-wire bus, with serial data, serial clock and strobe pins. The input data is partitioned so that after initial programming the output frequency can be changed by re-programming only 24 or 32 bits. The timing diagram for the bus is given in Fig.7.

The data is programmed as either four twenty-four bit words or three twenty-four bit words and one thirty-two bit word. When initially programmed words A, B, C and D are loaded, though if the auxiliary synthesiser is disabled C is not needed. Following the initial programming the frequency can be subsequently shifted in one of the following ways:

- a) If a 2 or 3 ratio prescaler is being used and CN does not need to be reprogrammed word A should be loaded.

- b If a 2 or 3 ratio prescaler is being used and CN does need to be reprogrammed word A2 should be loaded.

In wide frequency band systems CN must be reprogrammed for best performance every time the frequency is changed.

- c) If a four ratio prescaler is being used word A and word B should be loaded

Figure 7

A strobe pulse occurs at the end of each word and loads the contents of the input shift register into the working registers, except when word B is being loaded, in which case the shift register contents are loaded into a temporary register and then loaded into the working register when either word A or A2 is loaded. The information is transferred on the rising edge of the strobe pulse which should occur one half clock period after the clock edge on which the MSB of a word is shifted in.

If word A or word A2 is being loaded, when the strobe goes high the main synthesiser will be put into speed-up mode. This mode will be maintained while the strobe remains high. During this time any pulses on the clock input will not affect the function of the synthesiser.

The information contained within each word is given below. Data bits are shifted in on the leading clock edge, with the least significant bit(LSB) of the word first and the MSB of the word last. (Note that individual sections of data within a word are loaded with the MSB of that section first. An example of this is given after this description of Word A)

#### Word Format

MSB.....LSB

Word A

|0|

NF

| N1

|N2 or N2 and N2+N3|

|3 bits|

12 bits |

8 bits

|

$$\label{eq:NF} \begin{split} &\mathsf{NF} = \mathsf{Fractional}\mathsf{-N} \text{ incremental value. (MSB first)} \\ &\mathsf{N1} = \mathsf{Number} \text{ of cycles prescaler ratio } \mathsf{R1} \text{ is used. (MSB first)} \\ &\mathsf{N2} = \mathsf{Number} \text{ of cycles prescaler ratio } \mathsf{R2} \text{ is used. (MSB first)} \\ &\mathsf{N3} = \mathsf{Number} \text{ of cycles prescaler ratio } \mathsf{R3} \text{ is used. (MSB first)} \\ &\mathsf{If a two modulus prescaler is being used } \mathsf{N2} = \mathsf{8} \text{ bits.} \\ &\mathsf{If a three or four modulus prescaler is being used} \\ &\mathsf{N2} = \mathsf{4} \text{ bits and } \mathsf{N2} + \mathsf{N3} = \mathsf{4} \text{ bits(modulo-16 addition).} \end{split}$$

Therefore if the following values are required NF=3 N1=51 N2=25 the input word would be

| 0       | 110 | 110011000000 | 10011000 |

|---------|-----|--------------|----------|

|         | NF  | N1           | N2       |

| /ord A2 | 110 |              |          |

|0|

NF | N1

|N2 or N2 and N2+N3 | CN |

|3

bits | 12 bits |

8 bits

|8 bits |

CN = Scaling factor for current setting. (MSB first)

Word B

w

- |1000 |N2+N3+N4| CN | K | L | P1,P2 |

- | 4 bits | 8 bits|4 bits|2 bits| 2 bits |

- N4 = Number of cycles prescaler ratio R4 is used and (N2+N3+N4) is modulo-16 addition. (MSB first)

- CN = Scaling factor for current setting. (MSB first)

- K = Acceleration factor for integral charge pump. (MSB first)

- L = Acceleration factor for proportional charge pump. (MSB first)

P1,P2 = Number of modulii of prescaler.

| No. of modulii | P2 P1 |

|----------------|-------|

| Two            | 0 0   |

| Three          | 0 1   |

| Four           | 10    |

Word C

|1001| NA | | | 12 bits | 8 bits free |

NA = Variable frequency for auxiliary synthesiser. (MSB first) Word D

|1010 | NR |SM1,SM2| DM |SA1,SA2| DA|FMOD|LONG| |12 bits| 2 bits | 1 bit | 2 bits |1 bit | 1 bit | 1 bit |

| NR = Reference frequency division value. (MSB first) |

|------------------------------------------------------|

| SM1,SM2 = Main reference source select (Rmain).      |

| SM1 | SM2 | RMAIN |

|-----|-----|-------|

| 0   | 0   | М     |

| 0   | 1   | 2M    |

| 1   | 0   | 4M    |

| 1   | 1   | 8M    |

SA1,SA2 = Auxiliary reference source select (Raux).

| SA1 | SA2 | RAUX |

|-----|-----|------|

| 0   | 0   | М    |

| 0   | 1   | 2M   |

| 1   | 0   | 4M   |

| 1   | 1   | 8M   |

FMOD = Fractional-N modulus select (5 or 8).

| FMOD | MODULUS |

|------|---------|

| 0    | 5       |

| 1    | 8       |

DA = Disable auxiliary synthesiser.

DA=1-disabled DA=0-enabled

DM = Disable main synthesiser.

DM=1-disabled DM=0-enabled

LONG = Word A or A2 select.

LONG=0 Word A selected LONG=1 Word A2 selected

# **Electrical Characteristics**

# **DC Characteristics**

$V_{dd}$  = 5V  $\pm$  10%,  $T_{amb}$  = -40 to +85°C

# Static

| Parameter                        | Min | Тур              | Мах    | Unit           | Condition                                                                                                                                                              |

|----------------------------------|-----|------------------|--------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Supply voltage<br>Supply current | 4.5 | 5.0<br>6         | 5.5    | V<br>mA        | Both synthesisers on<br>(Fia = 125MHz, Fim = 30MHz, Ri = 35MHz)                                                                                                        |

|                                  |     | 3<br>4           | 5      | mA<br>mA       | Both synthesisers on<br>(Fia = 10MHz, Fim = 10MHz, Ri = 10MHz)<br>Main on, Auxiliary in stand-by (Fim=30MHz, Ri=35MHz)                                                 |

|                                  |     | 4<br>2<br>4<br>2 | 3<br>3 | mA<br>mA<br>mA | Main on, Auxiliary in stand-by (Fim=10MHz, Ri =10MHz)<br>Auxiliary on, Main in stand-by (Fia=125MHz, Ri=35MHz)<br>Auxiliary on, Main in stand-by (Fia=10MHz, Ri=10MHz) |

|                                  |     | 10               | 5      | μA             | Main and auxiliary in standby                                                                                                                                          |

| DVNAMIO                          |     |                  |        |                |                                                                                                                                                                        |

# DYNAMIC

### **AC Characteristics**

$V_{dd}$  = 5V  $\pm$  10%,  $T_{amb}$  = -40 to +85  $^{\circ}C$

# Input signals - RF

| Parameter                          | Min  | Тур | Max   | Unit   | Condition                |

|------------------------------------|------|-----|-------|--------|--------------------------|

| Input-RI                           |      |     |       |        |                          |

| Reference input - Ri               | 10   |     | 35    | MHz    | sinewave input, Note 1   |

|                                    | 1    |     | 35    | MHz    | pulse input, Note 1      |

| Rise time                          |      |     | 20    | ns     |                          |

| Fall time                          |      |     | 20    | ns     |                          |

| Input voltage - Ri                 | 0.1  |     | 1     | Vpk-pk | Ri = 20-35MHz, Note 1    |

|                                    | 0.25 |     | 1     | Vpk-pk | Ri = 10-19MHz, Note 1    |

| Input capacitance                  |      |     | 10    | pF     |                          |

| Large signal input impedance       | 200  |     |       | kΩ     | Note 2                   |

| Source impedance Z <sub>s</sub>    |      |     | 1.5   | kΩ     | Note 3                   |

| Aux synthesiser input -FIA         |      |     |       |        |                          |

| Input frequency - Fia              | 20   |     | 125   | MHz    | sinewave input, Note 1   |

|                                    | 1    |     | 125   | MHz    | pulse input, Note 1      |

| Rise time                          |      |     | 10    | ns     |                          |

| Fall time                          |      |     | 10    | ns     |                          |

| Input voltage                      | 0.35 |     | 1     | Vpk-pk | Fia = 20-49MHz, Note 1   |

|                                    | 0.1  |     | 1     | Vpk-pk | Fia = 50-99MHz, Note 1   |

|                                    | 0.35 |     | 1     | Vpk-pk | Fia = 100-125MHz, Note 1 |

| Input capacitance                  |      |     | 10    | pF     |                          |

| Large signal input impedance       | 200  |     |       | kΩ     | Note 2                   |

| Source impedance                   |      |     | 1.5   | kΩ     | Note 3                   |

| Main synthesiser input -FIM        |      |     |       |        |                          |

| Input frequency - Fim              | 10   |     | 30    | MHz    | sinewave input           |

|                                    | 1    |     | 30    | MHz    | pulse input              |

| Rise time                          |      |     | 50    | ns     |                          |

| Fall time                          |      |     | 50    | ns     |                          |

| Input voltage                      | 0.2  |     | 1     | Vpk-pk | Single ended input       |

| Common mode input DC voltage range | 2.8  |     | Vdd-1 | V      |                          |

| Input capacitance                  |      |     | 10    | pF     |                          |

| Input impedance                    | 100  |     |       | MΩ     |                          |

| Input Current                      |      |     | 10    | μΑ     |                          |

## Notes

1. Source impedance =  $50\Omega$

- 2. Virtual earth input amplifier, therfore low impedance for small signals. Impedance is high once signal amplitude exceeds typically ±0.125V.

- 3. Input amplifier may become unstable for higher values of Z.

# DYNAMIC

# **AC Characteristics**

$V_{dd}$  = 5V  $\pm$  10%, Tamb = -40 to +85°C

#### Input signals - Logic and current defining pins

| Parameter                                                                                                                           | Min                       | Тур              | Max                                      | Unit                      | Condition                              |

|-------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------------------|------------------------------------------|---------------------------|----------------------------------------|

| Data and strobe<br>Input voltage high<br>Input voltage low<br>Input capacitance<br>Input current                                    | V <sub>dd</sub> -0.8<br>0 |                  | V <sub>dd</sub><br>0.8<br>10<br>10       | V<br>V<br>pF<br>μA        |                                        |

| Clock<br>Input voltage high<br>Input voltage low<br>Input capacitance<br>Input current<br>Input frequency                           | V <sub>dd</sub> -0.8<br>0 |                  | V <sub>dd</sub><br>0.8<br>10<br>10<br>10 | V<br>V<br>pF<br>μA<br>MHz |                                        |

| Current setting pins<br>Input Signal RSA<br>Input current<br>Input Signal RSM<br>Input current<br>Input Signal RSC<br>Input current |                           | 80<br>32<br>12.8 |                                          | μΑ<br>μΑ<br>μΑ            | Notes 1, 4<br>Notes 2, 4<br>Notes 3, 4 |

#### Notes

- 1. The current set on pin RSA will be scaled up on chip by a factor of 3 to give the value of the auxiliary phase detector output.

- The current set on pin RSM will be scaled down on chip by a factor of 32 to provide the current *I<sub>bo</sub>* to the main phase detector which gives the outputs *I<sub>prop</sub>* and *I<sub>int</sub>*.

- 3. The current set on pin RSC will be scaled down on chip by a factor of 128 to provide the current *I<sub>co</sub>* to the main phase detector which gives the outputs *I<sub>comp</sub>* and *I<sub>comp</sub>* 2.

- The voltage on each of the three current setting pins (RSA, RSM, RSC) is approximately 4V. Therefore to give a typical current of 32µA on RSM for example, a 125kΩ resistor connected between the pin and GND would be required.

# DYNAMIC

$V_{dd} = 5V \pm 10\%$ ,  $T_{amb} = -40$  to  $+85^{\circ}C$

# Output signals

| Parameter                                                                | Min                       | Тур | Max                    | Unit   | Condition                                      |

|--------------------------------------------------------------------------|---------------------------|-----|------------------------|--------|------------------------------------------------|

| Modulus control - MOD1 MOD2<br>Output voltage high<br>Output voltage low | V <sub>dd-</sub> 0.4<br>0 |     | V <sub>dd</sub><br>0.4 | V<br>V | Push-Pull output<br>Іон = 0.5mA<br>Іо∟ = 0.5mA |

## Modulus output truth table

| MOD2 | MOD1 | Prescaler modulus |

|------|------|-------------------|

| 0    | 1    | R1                |

| 0    | 0    | R2                |

| 1    | 0    | R3                |

| 1    | 1    | R4                |

# DYNAMIC

$V_{dd}$  = 5V,  $T_{amb}$  = -40 to +85°C

**Output signals - Auxiliary synthesiser**

| Parameter                                             | Min  | Тур              | Max  | Unit | Condition                         |

|-------------------------------------------------------|------|------------------|------|------|-----------------------------------|

| <b>Output signal - PDA</b><br>Up current - See Note 5 | -10% | I <sub>pda</sub> | +10% | μΑ   | 0 <vpd<4.35v< td=""></vpd<4.35v<> |

| Down current - See Note 5                             | -10% | Ipda             | +10% | μA   | 0.65 <vpd<5v< td=""></vpd<5v<>    |

| Tristate                                              |      | poa              | 10   | nA   |                                   |

# DYNAMIC

$V_{dd} = 5V$ ,  $T_{amb} = -40$  to  $+85^{\circ}C$

#### Output signals - Main synthesiser, proportional output

| Parameter                        | Min  | Тур                       | Max  | Unit | Condition                                      |

|----------------------------------|------|---------------------------|------|------|------------------------------------------------|

| Output signal - PDP              |      |                           |      |      |                                                |

| Iprop(0) Up see notes 1, 3 & 4   | -10% | +I <sub>bo</sub> .CN      | +10% | μA   | 0 <vpd<4.55v, strobe="0V&lt;/td"></vpd<4.55v,> |

| lprop(0) Down see notes 1, 3 & 4 | -10% | -I <sub>bo</sub> .CN      | +10% | μA   | 0.45 <vpd<5v, strobe="0V&lt;/td"></vpd<5v,>    |

| lprop(1) Up see notes 2&3        | -10% | +I <sub>bo</sub> .CN.2L+1 | +10% | μA   | 0 <vpd<4.55v, strobe="5V&lt;/td"></vpd<4.55v,> |

| lprop(1) Down see notes 2&3      | -10% | -I <sub>bo</sub> .CN.2∟+1 | +10% | μA   | 0.45 <vpd<5v, strobe="5V&lt;/td"></vpd<5v,>    |

| Tristate                         |      |                           | 50   | nA   |                                                |

## Notes

The typical value of *Iprop(0)* is set by the programmed value of *CN* and the current *I<sub>rsm</sub>* set by the external resistor RSM, where *I<sub>bo</sub>=I<sub>rsm</sub>* / 32. *I<sub>rsm</sub>* is typically 32μA.

- 2. The typical value of IPROP(1) is set by the value of IPROP(0) and the programmed value of L.

- 3. The current output *IPROP* is specified between  $100\mu A$  and 1mA.

- 4. The output current is monotonic over the CN range 128-255. In standard operation CN is set at a value > 128.

- 5. Where  $I_{pda}$  depends on the value of current setting resistor on RSA pin (9).  $I_{pda}$  max = 250µA

# DYNAMIC

$V_{dd} = 5V$ ,  $T_{amb} = -40$  to  $+85^{\circ}C$

Output signals - Main synthesiser, integral output

| Parameter                                          | Min  | Тур                         | Max  | Unit | Condition                                      |

|----------------------------------------------------|------|-----------------------------|------|------|------------------------------------------------|

| Output signal - PDI                                |      |                             |      |      |                                                |

| Iілт Up<br>(1mA - 5mA) <i>see notes 1&amp;2</i>    | -10% | +l <sub>bo</sub> .CN.2∟+1.K | +10% | mA   | 0 <vpd<4.45v, strobe="5V&lt;/td"></vpd<4.45v,> |

| lілт Down<br>(1mA - 5mA) <i>see notes 1&amp;2</i>  | -10% | -I <sub>bo</sub> .CN.2∟+1.K | +10% | mA   | 0.35 <vpd<5v, strobe="5V&lt;/td"></vpd<5v,>    |

| lınт Up<br>(5mA - 10mA) <i>see notes 1&amp;2</i>   | -10% | +I <sub>bo</sub> .CN.2L+1.K | +10% | mA   | 0 <vpd<4.3v, strobe="5V&lt;/td"></vpd<4.3v,>   |

| Iınт Down<br>(5mA - 10mA) <i>see notes 1&amp;2</i> | -10% | -I <sub>bo</sub> .CN.2∟+1.K | +10% | mA   | 0.5 <vpd<5v, strobe="5V&lt;/td"></vpd<5v,>     |

| Tristate                                           |      |                             | 50   | nA   |                                                |

#### Notes

1. The typical value of *lint* is set by the value of *lprop(1)* and the programmed value of K.

2. The current output *lint* is specified between 1mA and 10mA.

# DYNAMIC

$V_{dd} = 5V$ ,  $T_{amb} = -40$  to  $+85^{\circ}C$

Output signals - Main synthesiser, under Fractional-N control

| Parameter                  | Min  | Тур                         | Max  | Unit | Condition                                      |

|----------------------------|------|-----------------------------|------|------|------------------------------------------------|

| Output signal - PDP        |      |                             |      |      |                                                |

| Icomp(0)<br>see notes 1&3  | -10% | I <sub>CO</sub> .Acc.       | +10% | μA   | 0 <vpd<4.55v, strobe="0V&lt;/td"></vpd<4.55v,> |

| ICOMP (1)<br>see notes 2&3 | -10% | I <sub>CO</sub> .Acc.2∟+1.  | +10% | μA   | 0 <vpd<4.55v, strobe="5V&lt;/td"></vpd<4.55v,> |

| Output signal - PDI        |      |                             |      |      |                                                |

| ICOMP2<br>see notes 4&5    | -10% | I <sub>CO</sub> .Acc.2∟+1.K | +10% | μA   | 0 <vpd<4.55v, strobe="5V&lt;/td"></vpd<4.55v,> |

#### Notes

- The typical value of *IcomP(0)* is set by the fractional-N accumulator value Acc and the current *I<sub>rsc</sub>* set by the external resistor RSC, where *I<sub>co</sub>=I<sub>rsc</sub>*/128. *I<sub>rsc</sub>* is typically 12.8µA.

- 2. The typical value of *lcomp(1)* is set by the value of *lcomp(0)* and the programmed value of *L*.

- 3. The current output *lcomp* is specified up to  $12\mu$ A.

- 4. The typical value of Icomp2 is set by the value of Icomp(1) and the programmed value of K.

- 5. The current output Icomp2 is specified up to 180µA.

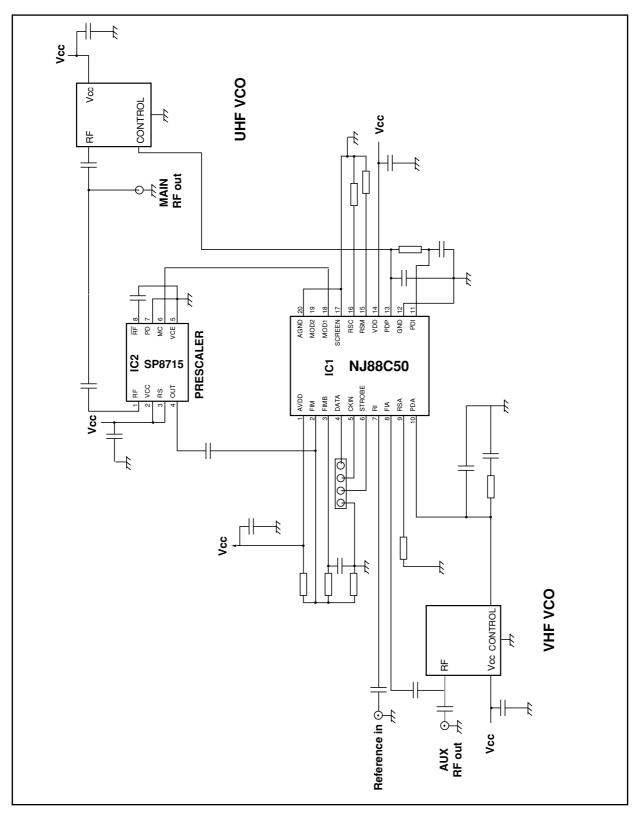

Figure 8 - Typical application

Fig.8 shows a typical application, using the NJ88C50 to generate both VHF and UHF signals. External components are kept to a minimum, requiring only bias, loop filter and decoupling components. In many applications the UHF VCO is a pre-assembled and tested module to suit the end equipment use, whereas the VHF design is likely to be discrete. The circuit shown is suitable for operation up to 1.1GHz and uses

a low power prescaler, the SP8715, feeding the NJ88C50 in single ended mode. This requires a biasing network around the differential input of the NJ88C50 to be used (pins 2 and 3).

Power supply and ground rails must have adequate decoupling otherwise overall performance may be impaired.

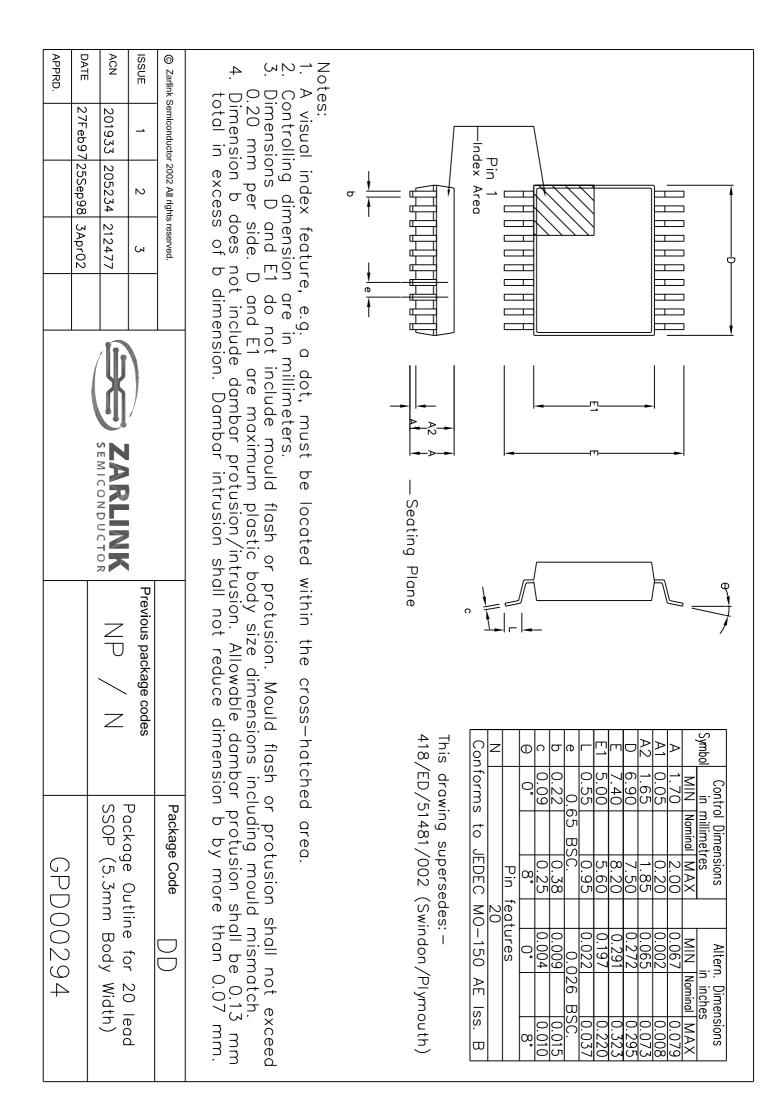

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Control Dimensions         Altern. Dimensions           in millimetres         MIN         Nominal         MAX           MIN         Nominal         MAX         0.079           0.05         0.200         0.0067         0.073           0.05         1.85         0.065         0.073           0.05         1.85         0.065         0.073           0.05         1.85         0.065         0.073           0.05         0.020         0.003         0.033           5.00         5.00         0.197         0.323           6.90         7.50         0.272         0.323           0.055         0.05         0.033         0.033           0.65         0.020         0.0010         0.015           0.09         0.25         0.0004         0.010           0.9         8'         0'         8'           0.09         0.25         0.010         0.010           0'         8'         0'         8'           7.16         0.001         0'         8'           0.09         0.25         0'         8'           0'         8'         0'         8' |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1 <sup>1</sup> - Seating Plane                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | This drawing supersedes:—<br>418/ED/51481/002 (Swindon/Roborough)<br>TD/D 991 (Oldham)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Notes:<br>1. A visual index feature, e.g. a dot, must be located within the cross-hatched area.<br>2. Controlling dimension are in millimeters.<br>3. Dimensions D and E1 do not include mould flash or protusion. Mould flash or protusion shall not exceed<br>0.20 mm per side. D and E1 are maximum plastic body size dimensions including mould mismatch.<br>4. Dimension b does not include dambar protusion/intrusion. Allowable dambar protusion shall be 0.13 mm<br>total in excess of b dimension. Dambar intrusion shall not reduce dimension b by more than 0.07 mm.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ORIGINATING SITE: SWINDON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ISSUE 1 2 2 ACM 2010 A | Title: Package Outline Drawing for<br>20 Ids SSOP-5.3 mm Body Width (NP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 27FEB972                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Drawing Number<br>GPD00294                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

# For more information about all Zarlink products visit our Web Site at

# www.zarlink.com

Information relating to products and services furnished herein by Zarlink Semiconductor Inc. trading as Zarlink Semiconductor or its subsidiaries (collectively "Zarlink") is believed to be reliable. However, Zarlink assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Zarlink or licensed from third parties by Zarlink, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Zarlink, or non-Zarlink furnished goods or services may infringe patents or other intellectual property rights owned by Zarlink owned by Zarlink.

This publication is issued to provide information only and (unless agreed by Zarlink in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Zarlink without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Zarlink's conditions of sale which are available on request.

Purchase of Zarlink s I<sup>2</sup>C components conveys a licence under the Philips I<sup>2</sup>C Patent rights to use these components in and I<sup>2</sup>C System, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

Zarlink and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright 2001, Zarlink Semiconductor Inc. All Rights Reserved.

# TECHNICAL DOCUMENTATION - NOT FOR RESALE

# For more information about all Zarlink products visit our Web Site at

# www.zarlink.com

Information relating to products and services furnished herein by Zarlink Semiconductor Inc. or its subsidiaries (collectively "Zarlink") is believed to be reliable. However, Zarlink assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Zarlink or licensed from third parties by Zarlink, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Zarlink, or non-Zarlink furnished goods or services may infringe patents or other intellectual property rights owned by Zarlink or licensed from third parties by Zarlink.

This publication is issued to provide information only and (unless agreed by Zarlink in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Zarlink without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Zarlink's conditions of sale which are available on request.

Purchase of Zarlink's I<sup>2</sup>C components conveys a licence under the Philips I<sup>2</sup>C Patent rights to use these components in and I<sup>2</sup>C System, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright Zarlink Semiconductor Inc. All Rights Reserved.

#### TECHNICAL DOCUMENTATION - NOT FOR RESALE