# 12 BIT HYBRID A/D CONVERTER 2.0 $\mu$ s Conversion Time; $\pm$ 0.012% F.S. Range Linearity Error

### **FEATURES**

- VERY FAST HYBRID A/D WITH 3-STATE OUTPUTS

- CODING:

Binary, Offset Binary, and Two's

Complement

- VOLTAGE RANGES:

±2.5V, ±5V, ±10V, 0-5V, 0-10V,

0-20V

- BOTH SERIAL AND PARALLEL OUTPUT

- INTERNAL OR EXTERNAL CLOCK

- POWER CONSUMPTION 1.8W TYP

### **DESCRIPTION**

Complete in a 36 pin DIP package. the ADH-8516 is the smallest 12 bit 2.0 µsec analog to digital converter available. With a suitable track and hold amplifier such as Data Device Corporation's ADH-050, it can achieve word rates of 450 kHz. Conversion time may be reduced below 2.0 usec by pin programmable short cycling if less resolution is acceptable. Gain and offset can be trimmed to zero, making the accuracy equal to the  $\pm 1/2$  LSB linearity. The ADH-8516 can be pin programmed to automatically ignore a new start command until internal conversion is completed, or to start a new cycle at once and abort any conversion in process, or to cycle continuously. The internal reference voltage is externally accessible.

### **APPLICATIONS**

Because of its high speed and 3-state outputs, the ADH-8516 is especially suited for multiplexing and for interfacing with microprocessors. Applications include high-speed data acquisition systems, autocorrelation computers, PCM communications systems, radar signal processors, moving target indicators, and electronic countermeasures systems. Utilizing the advantages of thin film and MSI technologies, the ADH-8516 has very high reliability and is ideal for remotely located and hard to access equipment where small size and high MTBF are critical.

| PARAMETER                                                                                                                                                                                                | UNIT                                                              | VALUE                                                                                                                                         |                                                                                                          | PARAMETER                                                                                                                                                                                                   | UNIT               | 1                                                                                                                                                                                                                                                                                                                                                                                     | VALUE           |                           |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------------------|--|

| RESOLUTION                                                                                                                                                                                               | Bits                                                              | 12                                                                                                                                            |                                                                                                          | DIGITAL INPUT/OUTPUT (DTL/TTL COMPATIBLE) (Cont'd)                                                                                                                                                          |                    |                                                                                                                                                                                                                                                                                                                                                                                       |                 |                           |  |

| ACCURACY AND DYNAMICS Linearity Error Linearity Error Tempco Gain Error (Trimmable to zero) Gain Error Tempco Offset (Trimmable to zero) Unipolar Bipolar Offset Tempco Unipolar Bipolar Conversion Time | % F.S. Range ppm/°C % F.S. Range ppm/°C mV mV ppm/°C ppm/°C  µsec | ADH-8516-11<br>±0.024 Max.<br>4 Max.<br>0.2 Typ.<br>30 Max.<br>10 Typ.<br>30 Typ.<br>10 Typ.<br>25 Typ.<br>2.0 Max. for 12<br>Programmable to | ADH-8516-12 ±0.012 Max. 2 Max. 0.2 Typ. 20 Max. 5 Typ. 10 Typ. 5 Typ. 10 Typ. bits 0.1.2 Typ, for 8 bits | Short Cycle  Retrigger Input (\$\overline{S}\$)  GI Digital Outputs (Buffered) Loading  12 Parallel Output Lines Serial Output (SO) Clock Out (CO)  Conversion Complete (CC) B1 (MSB) and \$\overline{B1}\$ |                    | Programs reduction in bits to obtain faster conversion Determines whether conversion can be initiated before end of cycle Programs MSB inversion  5 Std. TTL loads, except CO = 2 Std. TTL loads GO, and B2 through B12; three-state Non-return to zero (NRZ) 13 negative 50 nsec. typ. pulses; period = 150 nsec typ. Logic "0" during conversion For pin-programmable MSB inversion |                 |                           |  |

| Cycle Time                                                                                                                                                                                               | μsec                                                              | 2.0 Typ.; 2.2 Max.                                                                                                                            |                                                                                                          | INTERNAL REF. OUTPUT                                                                                                                                                                                        |                    |                                                                                                                                                                                                                                                                                                                                                                                       |                 |                           |  |

| ANALOG INPUT Input Ranges Unipolar Bipolar                                                                                                                                                               | V                                                                 | Pin-Programmable<br>0 to +5; 0 to +10; 0 to +20                                                                                               |                                                                                                          | + Ref Out Voltage<br>+ Ref External Current Load<br>Ref Out Voltage<br>( Ref for Trimming Only)                                                                                                             | V<br>mA<br>V       | 10.0 ±0.2<br>±2 Max.<br>—4.3 Nominal                                                                                                                                                                                                                                                                                                                                                  |                 |                           |  |

| Max Voltage Without Damage<br>Input Impedance<br>0 to +5V and +2.5V Ranges<br>0 to +10V and ±5.0V Ranges<br>0 to +20V and ±10.0V Ranges                                                                  | V<br>kΩ<br>kΩ                                                     | ±2.5; ±5.0; ±10.0<br>1.5 times F.S. input range<br>0.625<br>1.25<br>2.5                                                                       |                                                                                                          | POWER REQUIREMENTS Supply Voltages Max. Voltage Without Damage Current Typ. Max.                                                                                                                            | V<br>V<br>mA<br>mA | +15±3%<br>+18<br>50<br>65                                                                                                                                                                                                                                                                                                                                                             | 15±3%<br>18<br> | +5±5%<br>+7<br>135<br>250 |  |

| DIGITAL INPUT/OUTPUT (DTL/TTL COMPATIBLE)                                                                                                                                                                |                                                                   |                                                                                                                                               | TEMPERATURE RANGE (CASE)                                                                                 |                                                                                                                                                                                                             |                    |                                                                                                                                                                                                                                                                                                                                                                                       |                 |                           |  |

| Digital Inputs<br>Loading<br>Start Conversion (SC)                                                                                                                                                       |                                                                   | 1 Std. TTL load Positive pulse; 20 nsec min., 1.5 µsec max.; Triggers on leading edge                                                         |                                                                                                          | Operating1 Option3 Option Storage                                                                                                                                                                           | °C<br>°C<br>°C     | - 55 to +125<br>0 to +70<br>55 to +125                                                                                                                                                                                                                                                                                                                                                |                 |                           |  |

| Clock Input (CI)  3-State Enable Lines                                                                                                                                                                   |                                                                   |                                                                                                                                               |                                                                                                          | PHYSICAL DATA Type of Package Size                                                                                                                                                                          | Inch               | 36-Pin Double DIP<br>0.78 x 1.9 x .21<br>(1.98 x 4.83 x 0.53 cm)                                                                                                                                                                                                                                                                                                                      |                 |                           |  |

### TECHNICAL INFORMATION

### 1. INTRODUCTION

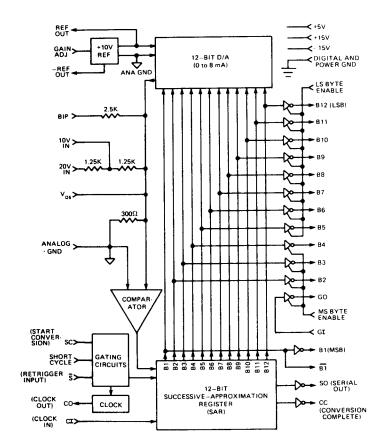

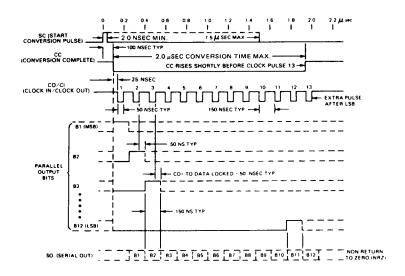

The major elements of the ADH-8516 analog to digital converter, as shown in Figure 1, are an analog voltage comparator, a 12 bit successive approximation register (SAR), and a 12 bit digital to analog converter. These elements are connected in a closed loop so as to perform A/D conversion by successive approximation. The clock and gating circuits control the SAR and the timing, as shown in the timing diagram, Figure 2.

The successive approximation process operates as follows. First bit 1 (the MSB) is set to 1, and its analog equivalent (1/2 F.S.) is produced by the D/A and compared with the input voltage  $V_{\sc IN}$  by the comparator. If  $V_{\sc IN}$  is greater than bit 1, the bit remains at 1 and bit 2 is tried next. If  $V_{\sc IN}$  is less than bit 1, the bit is set to 0 before bit 2 is tried. Any succeeding bit that does not cause the combined bit weight to exceed  $V_{\sc IN}$  remains set at 1, and any bit that causes the combined weight to exceed  $V_{\sc IN}$  is set to 0. When the LSB has been tried, the control logic transmits a conversion complete (CC) signal. The output of the register at that time is a digital number representing the quantized analog voltage  $V_{\sc IN}$  as a fraction of the D/A internal reference voltage.

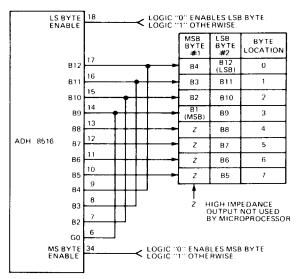

In the ADH-8516, output digital data is gated by two enable lines so that two 8 line bytes for microprocessor interfacing can be generated. If the MS and LS Byte Enable lines are grounded, as explained below, the gates will transmit logic 1 and 0 data normally.

### 2. PIN FUNCTIONS

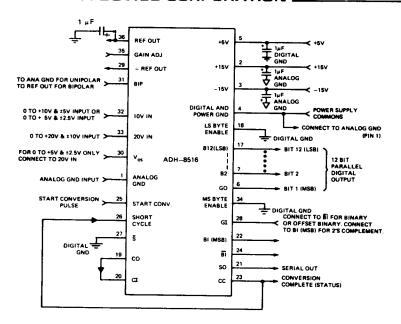

The versatility of the ADH-8516 has been maximized by making the fullest use of all 36 output pins. Figure 3 shows pin connections for normal, untrimmed, operation when 3-state output is not required.

The REF OUT, GAIN ADJ, and —REF OUT pins are used for trimming. The BIP pin connection determines whether the input accepted is unipolar (0 to +5V, 0 to +10V, or 0 to +20V) or bipolar (±2.5V, ±5V, or ±10V). Pins 10V IN and 20V IN accommodate all input ranges as shown in the connection table, Figure 3.

There are two ground pins, an ANALOG GND and a DIGITAL AND POWER GND. These grounds should be connected together at one and only one point by the user, as indicated at pin 4 in Figure 3. The ANALOG GND is represented by  $\checkmark$ , and the DIGITAL AND POWER GND is represented by  $\stackrel{1}{--}$  in Figure 3.

Conversions are initiated by a logic high pulse at the START pin. SHORT CYCLE and S are used to initiate special retriggerable and shorter cycle operating modes. Conversion status is indicated by the conversion complete logic signal, CC.

CO and CI are clock output and clock input, respectively. These pins are connected together when the internal clock is used. If an external clock is used, it is connected to CI. The internal clock is automatically disabled so long as CO remains disconnected.

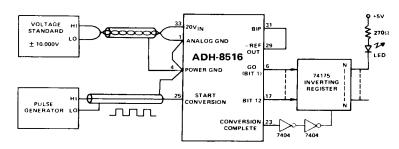

FIGURE 1. ADH-8516 BLOCK DIAGRAM

FIGURE 2. ADH—8516 TIMING DIAGRAM Non-Retriggerable Mode; Internal Clock

### ILC DATA DEVICE CORPORATION

FIGURE 3. INPUT/OUTPUT CONNECTIONS FOR NORMAL OPERATION (NON-RETRIGGERABLE)

|          | ABSOLUTE<br>MAX INPUT | INPUT<br>IMPEDANCE | INPUT<br>TERMINAL | JUMPER CONNECTIONS (Pin Numbers are given in parentheses) |

|----------|-----------------------|--------------------|-------------------|-----------------------------------------------------------|

| ±2.5∨    | ±3.75V                | 0.625kΩ            |                   | BIP (31) to REF OUT (36);                                 |

| 0 to 5V  | +7.5V                 | 0.625kΩ            |                   | 20V IN (33) to V <sub>os</sub> (30)                       |

|          | 177.50                | U.625K12           | 10V IN (32)       | BIP (31) to ANALOG GND (1)<br>20V IN (33) to Vos (30)     |

| ±5.0∨    | ±7.5∨                 | 1.25kΩ             | 10V IN (32)       | BIP (31) to REF OUT (36)                                  |

| 0 to 10V | +15V                  | 1.25kΩ             | 10V IN (32)       | BIP (31) to ANALOG GND (1)                                |

| ±10.0∨   | ±15V                  | 2.5kΩ              |                   | BIP (31) to REF OUT (36)                                  |

| 0 to 20V | +30V                  | 2.5kΩ              | 20V IN (33)       | BIP (31) to ANALOG GND (1)                                |

## FIGURE 4. INPUT VOLTAGE RANGES AND CONNECTIONS (PIN NUMBERS ARE GIVEN IN PARENTHESES)

Buffered parallel digital output is available at pin GO and pins B2, B3, ... B11, B12 (LSB). The gate output GO is either the MSB (for binary and offset binary coding) or its complement,  $\overline{\text{MSB}}$  (for 2's complement coding). The gate GI must be connected to B1 for MSB output, or to  $\overline{\text{B1}}$  (MSB) for  $\overline{\text{MSB}}$  output. The complement  $\overline{\text{MSB}}$  is available for both bipolar and unipolar operation. Bit transitions are given in Figure 5.

Pin SO provides serial digital output. Timing for the serial output is depicted in Figure 2. The Serial Out is a non return to zero type (NRZ).

### 3. POWER SUPPLIES

As shown in Figure 3, the +15V, -15V, and +5V power inputs must be bypassed by capacitors of  $1\mu F$  or greater. Note that the +5V input terminal is bypassed to Power and Digital Ground, while the +15V and -15V input terminals are bypassed to Analog Ground.

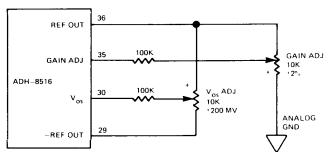

### 4. GAIN AND OFFSET TRIM ADJUSTMENTS

The gain and offset of the ADH-8516 are factory trimmed to the tolerances listed in the specifications table. Both errors can be trimmed to zero using the trim adjustment circuits shown in Figure 8.

### 5. 3-STATE PARALLEL DIGITAL OUTPUT

The parallel digital outputs are gated to provide two 8 line bytes for microprocessor interfacing. When the Enables for the gates in Figure 1 are at logic 0, the gate outputs are at normal logic 1 or 0, depending on the bit state. When the Enables are at logic 1, the gate output is high impedance (Z), and the microprocessor sees an essentially open line.

Connections for 3-state output are shown in Figure 9. The first byte is enabled by the MS Byte Enable, and transmits bits 1 to 4 only. Byte locations 4, 5, 6, 7 are connected only to high impedance outputs, and are not used. Note that bits 5 through 12 are not transmitted in byte 1 because the LS Byte Enable is at logic 1, so its gates have a high impedance output. During the second byte, only the LS Byte Enable is low, so bits 5 to 12 are transmitted and the gates for bits 1 to 4 have a high impedance output.

| TRANSITION VALUE    |                          | DIGITAL BIT OUTPUTS |    |    |    |    |    |    |    |    |     |     |            |

|---------------------|--------------------------|---------------------|----|----|----|----|----|----|----|----|-----|-----|------------|

| UNIPOLAR<br>BINARY  | BIPOLAR<br>OFFSET BINARY | MSB<br>B1           | B2 | В3 | B4 | 85 | В6 | B7 | B8 | В9 | B10 | B11 | LSB<br>B12 |

| +F.S 3/2 LSB        | +F.S. – 3/2 LSB          | 1                   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1   | 1   | 1          |

| +3/4 F.S 1/2 LSB    | +1/2 F.S 1/2 LSB         | 1                   | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0   | 0          |

| +1/2 F.S. + 1/2 LSB | +1/2 LSB                 | 1                   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0   | 1<br>0     |

| +1/2 F.S 1/2 LSB    | -1/2 LSB                 | 1 0                 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0   | 0          |

| +1/4 F.S. + 1/2 LSB | -1/2 F.S. + 1/2 LSB      | 0                   | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | Ö   | 0   | 1 0        |

| +3/2 LSB            | -F.S. + 3/2 LSB          | 0                   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 1 0 | 0          |

| +1/2 LSB            | -F.S. + 1/2 LSB          | 0                   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0   | 1 0        |

For Two's Complement coding, all values are the same as those listed above for Offset Binary coding, except that the MSB is reversed (MSB bits "0" becomes "1" and "1" becomes "0"). See Figure 6 for F.S. and 1/2 LSB values.

FIGURE 5. THEORETICAL TRANSITION VALUES

### DDC

### 6. RETRIGGERABLE MODE

When  $\overline{S}$  is grounded as in Figure 3, the ADH-8516 is considered to be in a non-retriggerable mode. A start conversion pulse at the START pin is ignored, and a new cycle cannot begin, until the CC output indicates that conversion is complete. If the START input is still high when conversion is complete, a new cycle will begin when the CC output rises (see Figure 2).

In the retriggerable mode, on the other hand, a new conversion will begin as soon as a pulse is received at the START input. If a previous conversion is in progress, it will be aborted. Programming the ADH-8516 for the retriggerable mode requires only that the Spin be connected to START instead of to digital ground.

### 7. CONTINUOUS CONVERSION

The ADH-8516 can be programmed to cycle continuously, beginning another conversion cycle as soon as the previous one has been completed. Continuous conversion will take place if the START input is maintained at logic 1, with pin  $\overline{S}$  at digital ground.

### 8. SHORT CYCLING

It is possible to reduce the number of bits tested by the SAR during the successive approximation process (see Figure 1), and thereby shorten the conversion time without sacrificing linearity. The resolution will then correspond to the actual number of bits tested. The tradeoff between conversion time and accuracy is made by connecting the SHORT CYCLE pin to one of the digital outputs bits instead of to CC. 3-state outputs cannot be used because the byte enable lines must be continuously enabled by grounding them in order to detect the short cycle condition. The following table lists the SHORT CYCLE connections for several possible conversion times and accuracies:

| RESOLUTION | SHORT CYCLE<br>CONNECTION TO | CONVERSION<br>TIME (TYP.) |  |  |

|------------|------------------------------|---------------------------|--|--|

| 11 BITS    | B12                          | 1.65 µs                   |  |  |

| 10 BITS    | B11                          | 1.50 μs                   |  |  |

| 9 BITS     | B10                          | 1.35 µs                   |  |  |

| 8 BITS     | B9                           | 1.20 μs                   |  |  |

### **DIGITAL CODING AND ACCURACY TESTS**

The digital coding is described by the transition table in Figure 5. Coding is straight binary for unipolar ranges  $(0-5V,\,0-10V,\,\text{and}\,0-20V)$  and offset binary for bipolar ranges  $(\pm 2.5V,\,\pm 5V,\,\text{and}\,\pm 10V)$ . The analog input voltage levels listed in the left hand columns of Figure 5 should correspond to the transition points between the digital codes shown at the right. The voltages for Full Scale (F.S.) and 1/2 LSB for each input voltage range are listed in Figure 6.

The accuracy of the ADH-8516 is specified by its linearity error, gain, and offset. The relationships between these terms and the measured bit transitions listed in Figure 5 are discussed in the Background Information section for A/D converters in this catalog.

| VOLTAGE<br>RANGE | FULL SCALE<br>(VOLTS) | 1/2 LSB<br>(VOLTS) |

|------------------|-----------------------|--------------------|

| ±2.5V            | 2.50000               | 0.00061            |

| ±5V              | 5.00000               | 0.00122            |

| ±10V             | 10.00000              | 0.00244            |

| 0 – 5V           | 5.00000               | 0.00061            |

| 0 – 10V          | 10.00000              | 0.00122            |

| 0 – 20V          | 20.00000              | 0.00244            |

FIGURE 6. FULL SCALE (F.S.) and 1/2 LSB VALUES

FIGURE 7. CIRCUIT FOR TESTING ACCURACY

FIGURE 8. GAIN AND OFFSET TRIM ADJUSTMENTS

FIGURE 9. CONNECTIONS FOR COMBINING

MS BYTE AND LS BYTE ON EIGHT LINES FOR

INTERFACING WITH MICROPROCESSORS

### ILC DATA DEVICE CORPORATION

### ORDERING INFORMATION ADH-8516 -11 - 1 -883B Reliability Grade: 883B = Fully compliant with MIL-STD-883. —B = Screened to MIL-STD-883 but without QCI testing. Blank = Screened to MIL-STD-883 but without pre burn-in testing, burn-in, and QCI testing. Operating Temperature Ranges (Case): $1 = -55^{\circ} \text{ C to } +125^{\circ} \text{ C}$ $3 = 0^{\circ} \text{C to } +70^{\circ} \text{C}$ Linearity: 11 = 11 bits (±0.024% F.S. range) 12 = 12 bits (±0.012% F.S. range)

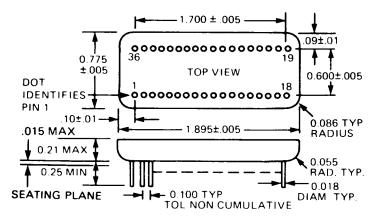

### MECHANICAL OUTLINE 36 PIN DOUBLE DIP

### NOTES:

- 1. Dimensions shown are in inches

- 2. Lead identification numbers are for reference only

- 3. Pin material meets solderability requirements of MIL-STD-202E, Method 208C

- Package is Kovar with electroless nickel plating.

- 5. Case is grounded through pin 1 (analog ground)

The arrangement shown in Figure 7 may be used to measure the bit transitions. Offset trim, gain trim, and other standard connections are not shown. Shielded twisted pair cable is used to connect the Voltage Standard, and each of the twelve bits requires its own LED indicator. Readings should be taken with the converter energized, in thermal equilibrium at 25°, and after a warm-up time of 5 minutes. The Pulse Generator can be set at any frequency up to the maximum specified for the ADH-8516. The power supply voltages should be at their nominal values.

The suggested test procedure is as follows:

- (1) Trim the offset by sweeping the input through the transition at all bits off in Figure 5 (-F.S. + 1/2 LSB for bipolar coding). Adjust the offset potentiometer until there is a 50% dither of the LSB.

- (2) Trim the gain by sweeping the input through the transition at +F.S. 3/2 LSB. Adjust the gain potentiometer for a 50% dither of the LSB.

- (3) Repeat steps (1) and (2) because there might be a slight interaction between the offset and gain adjustments.

- (4) Measure the input voltage levels at which other transitions occur. The differences between these voltages and the theoretical transition values will be within ±1/2 LSB.

### RELIABILITY

The use of MSI and thin film resistance networks, as well as careful thermal design, results in very high MTBF values. Summaries of MTBF calculations are available on request.

All ADH-8516's are built in accordance with requirements of MIL-STD-883.

### PIN CONNECTION TABLE

| PIN | FUNCTION              | PIN | FUNCTION       |

|-----|-----------------------|-----|----------------|

| 1   | Analog Gnd            | 19  | co             |

| 2   | +15V                  | 20  | l CI           |

| 3   | -15V                  | 21  | so             |

| 4   | Power and Digital Gnd | 22  | B1 (MSB)       |

| 5   | +5V                   | 23  | cc             |

| 6   | G0                    | 24  | B1             |

| 7   | B2                    | 25  | Start          |

| 8   | B3                    | 26  | Short Cycle    |

| 9   | B4                    | 27  | Ī              |

| 10  | B5                    | 28  | GI             |

| 11  | B6                    | 29  | -Ref Out       |

| 12  | B7                    | 30  | Vos            |

| 13  | B8                    | 31  | BIP            |

| 14  | B9                    | 32  | 10V IN         |

| 15  | B10                   | 33  | 20V IN         |

| 16  | B11                   | 34  | MS BYTE Enable |

| 17  | B12 (LSB)             | 35  | Gain Adj       |

| 18  | LS BYTE Enable        | 36  | Ref Out        |

C-4/86