CS5501 CS5503

# Low-Cost, 16 & 20-Bit Measurement A/D Converter

## **Features**

- Monolithic CMOS ADC with Filtering

- 6-Pole, Low-Pass Gaussian Filter

- Up to 4 kHz Output Word Rates

- On Chip Self-Calibration Circuitry

- Linearity Error: ±0.0003%

- Differential Nonlinearity:

CS5501: 16-Bit No Missing Codes

(DNL ±1/8 LSB)

CS5503: 20-Bit No Missing Codes

- System Calibration Capability

- Flexible Serial Communications Port

- μC-Compatible Formats

- 3-State Data and Clock Outputs

- UART Format (CS5501 only)

- Pin-Selectable Unipolar/Bipolar Ranges

- Low Power Consumption: 25 mW

- 10 µW Sleep Mode for Portable Applications

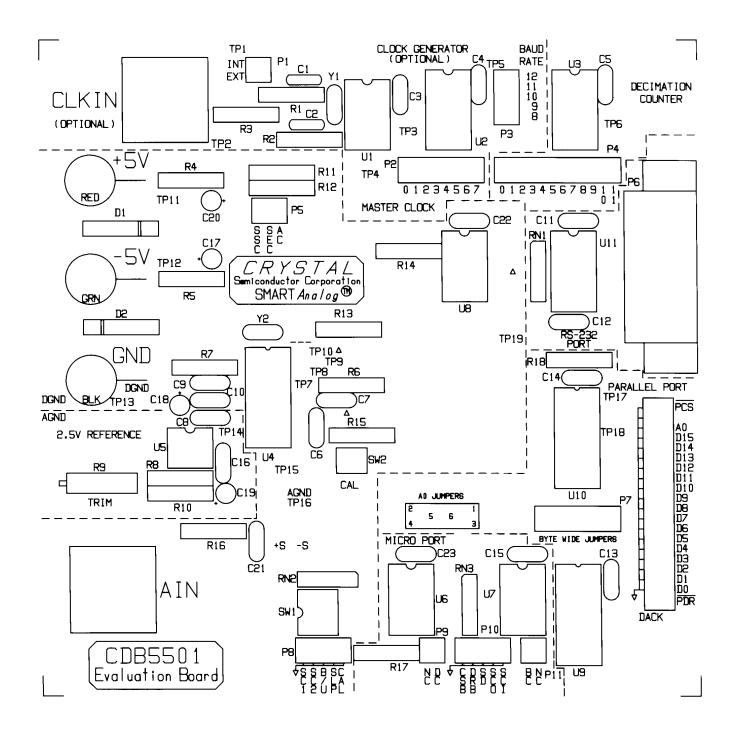

- Evaluation Boards Available

# **Description**

The CS5501 and CS5503 are low-cost CMOS A/D converters ideal for measuring low-frequency signals representing physical, chemical, and biological processes. They utilize charge-balance techniques to achieve 16-bit (CS5501) and 20-bit (CS5503) performance with up to 4 kHz word rates at very low cost.

The converters continuously sample at a rate set by the user in the form of either a CMOS clock or a crystal. On-chip digital filtering processes the data and updates the output register at up to a 4 kHz rate. The converters' low-pass, 6-pole Gaussian response filter is designed to allow corner frequency settings from 0.1 Hz to 10 Hz in the CS5501 and 0.5 Hz to 10 Hz in the CS5503. Thus, each converter rejects 50 Hz and 60 Hz line frequencies as well as any noise at spurious frequencies.

The CS5501 and CS5503 include on-chip self-calibration circuitry which can be initiated at any time or temperature to insure offset and full-scale errors of typically less than 1/2 LSB for the CS5501 and less than 4 LSB for the CS5503. The devices can also be applied in system calibration schemes to null offset and gain errors in the input channel.

Each device's serial port offers two general purpose modes of operation for direct interface to shift registers or synchronous serial ports of industry-standard microcontrollers. In addition, the CS5501's serial port offers a third, UART-compatible mode of asynchronous communication.

#### ORDERING INFORMATION

See page 33.

CS5501 ANALOG CHARACTERISTICS (TA = TMIN to TMAX; VA+, VD+ = 5V;

VA-, VD- = -5V; VREF = 2.5V; CLKIN = 4.096MHz; Bipolar Mode; MODE = +5V; R<sub>Source</sub> =  $750\Omega$  with a 1nF to AGND at AIN (see Note 1); Digital Inputs: Logic 0 = GND; Logic 1 = VD+; unless otherwise specified.)

|                                  |                                      | CS5501-A, B, C |                            |                           | CS5501-S,   | Т             |                 |                      |

|----------------------------------|--------------------------------------|----------------|----------------------------|---------------------------|-------------|---------------|-----------------|----------------------|

| Parameter*                       |                                      | Min            | Тур                        | Max                       | Min         | Тур           | Max             | Units                |

| Specified Temperature Range      |                                      | -40 to +85     |                            |                           | -55 to +125 |               |                 | °C                   |

| Accuracy                         |                                      |                |                            |                           |             |               |                 |                      |

| Linearity Error                  | -A, S<br>-B, T<br>-C                 | -<br>-<br>-    | 0.0015<br>0.0007<br>0.0003 | 0.003<br>0.0015<br>0.0012 | -           | 0.0007        | 0.003<br>0.0015 | ±%FS<br>±%FS<br>±%FS |

| Differential Nonlinearity        | T <sub>MIN</sub> to T <sub>MAX</sub> | -              | ±1/8                       | ±1/2                      | -           | ±1/8          | ±1/2            | LSB <sub>16</sub>    |

| Full Scale Error                 | (Note 2)                             | -              | ±0.13                      | ±0.5                      | -           | ±0.13         | ±0.5            | LSB <sub>16</sub>    |

| Full Scale Drift                 | (Note 3)                             | -              | ±1.2                       | 1                         | -           | ±2.3          | -               | LSB <sub>16</sub>    |

| Unipolar Offset                  | (Note 2)                             | -              | ±0.25                      | ±1                        | -           | ±0.25         | ±1              | LSB <sub>16</sub>    |

| Unipolar Offset Drift            | (Note 3)                             | -              | ±4.2                       | -                         | -           | +3.0<br>-25.0 | -               | LSB <sub>16</sub>    |

| Bipolar Offset                   | (Note 2)                             | -              | ±0.25                      | ±1                        | -           | ±0.25         | ±1              | LSB <sub>16</sub>    |

| Bipolar Offset Drift             | (Note 3)                             | -              | ±2.1                       | -                         | -           | +1.5<br>-12.5 | -               | LSB <sub>16</sub>    |

| Bipolar Negative Full Scale Erro | or (Note 2)                          | -              | ±0.5                       | ±2                        | -           | ±0.5          | ±2              | LSB <sub>16</sub>    |

| Bipolar Negative Full Scale Drif | t (Note 3)                           | -              | ±0.6                       | -                         | -           | ±1.2          | -               | LSB <sub>16</sub>    |

| Noise (Referred to Output)       |                                      | -              | 1/10                       | -                         | -           | 1/10          | -               | LSBrms               |

- Notes: 1. The AIN pin presents a very high input resistance at dc and a minor dynamic load which scales to the master clock frequency. Both source resistance and shunt capacitance are therefore critical in determining the CS5501's source impedance requirements. For more information refer the text section Analog Input Impedance Considerations.

- 2. Applies after calibration at the temperature of interest.

- 3. Total drift over the specified temperature range since calibration at power-up at 25°C (see Figure 11). This is guaranteed by design and /or characterization. Recalibration at any temperature will remove these errors.

|     | Un    | Unipolar Mode |        |       | Bipolar Mode |        |  |  |

|-----|-------|---------------|--------|-------|--------------|--------|--|--|

| μV  | LSB's | %FS           | ppm FS | LSB's | %FS          | ppm FS |  |  |

| 10  | 0.26  | 0.0004        | 4      | 0.13  | 0.0002       | 2      |  |  |

| 19  | 0.50  | 0.0008        | 8      | 0.26  | 0.0004       | 4      |  |  |

| 38  | 1.00  | 0.0015        | 15     | 0.50  | 0.0008       | 8      |  |  |

| 76  | 2.00  | 0.0030        | 30     | 1.00  | 0.0015       | 15     |  |  |

| 152 | 4.00  | 0.0061        | 61     | 2.00  | 0.0030       | 30     |  |  |

**CS5501 Unit Conversion Factors, VREF = 2.5V**

<sup>\*</sup> Refer to the Specification Definitions immediately following the Pin Description Section.

**CS5503 ANALOG CHARACTERISTICS** (TA = TMIN to TMAX; VA+, VD+ = 5V; VA-, VD- = -5V; VREF = 2.5V; CLKIN = 4.096MHz; Bipolar Mode; MODE = +5V; R<sub>source</sub> = 750 $\Omega$  with a 1nF to AGND at AIN (see Note 1): unless otherwise specified.)

|                                               |                         | CS5503-A, B, C |                            |                           | (           | CS5503-S,   | Т            |                      |

|-----------------------------------------------|-------------------------|----------------|----------------------------|---------------------------|-------------|-------------|--------------|----------------------|

| Parameter*                                    |                         | Min            | Тур                        | Max                       | Min         | Тур         | Max          | Units                |

| Specified Temperature Range                   |                         | -40 to +85     |                            |                           | -55 to +125 |             |              | °C                   |

| Accuracy                                      |                         |                |                            |                           |             |             |              |                      |

| Linearity Error                               | -A, S<br>-B, T<br>-C    | -<br>-<br>-    | 0.0015<br>0.0007<br>0.0003 | 0.003<br>0.0015<br>0.0012 |             | -<br>0.0007 | 0.003<br>TBD | ±%FS<br>±%FS<br>±%FS |

| Differential Nonlinearity (Not Missing Codes) | MIN to T <sub>MAX</sub> | -              | 20                         | -                         | -           | 20          | -            | Bits                 |

| Full Scale Error                              | (Note 2)                | -              | ±4                         | ±16                       | ı           | ±4          | ±16          | LSB <sub>20</sub>    |

| Full Scale Error Drift                        | (Note 3)                | -              | ±19                        | -                         | -           | ±37         | -            | LSB <sub>20</sub>    |

| Unipolar Offset                               | (Note 2)                | -              | ±4                         | ±16                       | 1           | ±4          | ±16          | LSB <sub>20</sub>    |

| Unipolar Offset Drift                         | (Note 3)                | -              | ±67                        | -                         |             | +48<br>-400 | -            | LSB <sub>20</sub>    |

| Bipolar Offset                                | (Note 2)                | -              | ±4                         | ±16                       | 1           | ±4          | ±16          | LSB <sub>20</sub>    |

| Bipolar Offset Drift                          | (Note 3)                | -              | ±34                        |                           | -           | +24<br>-200 | -            | LSB <sub>20</sub>    |

| Bipolar Negative Full Scale Erro              | r (Note 2)              | -              | ±8                         | ±32                       | -           | ±8          | ±32-         | LSB <sub>20</sub>    |

| Bipolar Negative Full Scale Drift             | (Note 3)                | -              | ±10                        | -                         | -           | ±20         | -            | LSB <sub>20</sub>    |

| Noise (Referred to Output)                    |                         | -              | 1.6                        | -                         | -           | 1.6         | -            | LSBrms<br>(20)       |

|       | Unipolar Mode |        |        | Bipolar Mode |           |        |  |  |

|-------|---------------|--------|--------|--------------|-----------|--------|--|--|

| μV    | LSB's         | %FS    | ppm Fs | LSB's        | %FS       | ppm FS |  |  |

| 0.596 | 0.25 0.0      | 000238 | 0.24   | 0.13         | 0.0000119 | 0.12   |  |  |

| 1.192 | 0.50 0.0      | 000477 | 0.47   | 0.26         | 0.0000238 | 0.24   |  |  |

| 2.384 | 1.00 0.0      | 000954 | 0.95   | 0.50         | 0.0000477 | 0.47   |  |  |

| 4.768 | 2.00 0.0      | 001907 | 1.91   | 1.00         | 0.0000954 | 0.95   |  |  |

| 9.537 | 4.000 0.0     | 003814 | 3.81   | 2.00         | 0.0001907 | 1.91   |  |  |

CS5503 Unit Conversion Factors, VREF = 2.5V

<sup>\*</sup> Refer to the Specification Definitions immediately following the Pin Description Section.

# **ANALOG CHARACTERISTICS** (Continued)

|                                              | CS5501/3-A, B, C |              | CS      | \$5501/3-S           | , T             |                     |                                                     |

|----------------------------------------------|------------------|--------------|---------|----------------------|-----------------|---------------------|-----------------------------------------------------|

|                                              | Min              | Тур          | Max     | Min                  | Тур             | Max                 | Units                                               |

|                                              |                  |              |         |                      |                 |                     |                                                     |

|                                              |                  |              |         |                      |                 |                     |                                                     |

|                                              | -                |              |         | -                    | 2               | 3.2                 | mA                                                  |

|                                              | -                |              |         | -                    |                 | -                   | mA                                                  |

|                                              | -                | •            |         | -                    | •               |                     | mΑ                                                  |

| (Note 4)                                     | -                | 0.03         | 0.1     | -                    | 0.03            | 0.1                 | mA                                                  |

|                                              |                  | 0.5          | 40      |                      | 0.5             | 40                  | 147                                                 |

| (N.L. ( 4)                                   | -                |              |         | -                    |                 | _                   | mW                                                  |

| (Note 4)                                     | -                | 10           | 20      | -                    | 10              | 40                  | μW                                                  |

|                                              |                  |              |         |                      |                 |                     |                                                     |

|                                              | -                | 70           | -       | -                    | 70              | -                   | dB                                                  |

| (Note 5)                                     | -                | 75           | -       | -                    | 75              | -                   | dB                                                  |

|                                              |                  |              |         |                      |                 |                     |                                                     |

|                                              |                  |              |         |                      |                 |                     |                                                     |

|                                              |                  | 0 to +2.5    |         |                      | 0 to +2.5       |                     | V                                                   |

|                                              | -                | ±2.5         | -       | -                    | ±2.5            | -                   | V                                                   |

|                                              | -                | 20           | -       | -                    | 20              | -                   | pF                                                  |

| (Note 1)                                     | -                | 1            | -       | -                    | 1               | -                   | nA                                                  |

| s                                            |                  |              |         |                      |                 |                     |                                                     |

| ge                                           |                  | VREF+0.1     | 1       | ,                    | VREF+0.1        | 1                   | V                                                   |

| )                                            |                  | VREF+0.1     | 1       | ,                    | VREF+0.1        | 1                   | V                                                   |

| е                                            | -                | (VREF+0.     | 1)      | -(                   | VREF+0.         | 1)                  | V                                                   |

|                                              |                  |              |         |                      |                 |                     |                                                     |

| lotes 6, 7)                                  |                  |              |         |                      |                 |                     |                                                     |

| Calibration Range (Notes 6, 7) Unipolar Mode |                  | -(VREF +0.1) |         | -(VREF +0.1)         |                 |                     | V                                                   |

|                                              | -40%VF           | REF to +40   | %VREF   | -40%VREF to +40%VREF |                 |                     | V                                                   |

| (Note 8)                                     | 80%              |              | 2VREF   | 80%                  |                 | 2VREF               |                                                     |

| (1.1010-0)                                   | VREF             |              | +0.2    | VREF                 |                 | +0.2                | V                                                   |

| (                                            |                  | Min   -      | Min Typ | Min Typ Max          | Min Typ Max Min | Min Typ Max Min Typ | Min   Typ   Max   Min   Typ   Max   Min   Typ   Max |

- Notes: 4. All outputs unloaded.

- 5. 0.1Hz to 10Hz. PSRR at 60 Hz will exceed 120 dB due to the benefit of the digital filter.

- 6. In unipolar mode the offset can have a negative value (-VREF) such that the unipolar mode can mimic bipolar mode operation.

- 7. The specifications for Input Overrange and for Input Span apply additional constraints on the offset calibration range.

- 8. For Unipolar mode, Input Span is the difference between full scale and zero scale. For Bipolar mode, Input Span is the difference between positive and negative full scale points. When using less than the maximum input span, the span range may be placed anywhere within the range of  $\pm$ (VREF + 0.1).

Specifications are subject to change without notice.

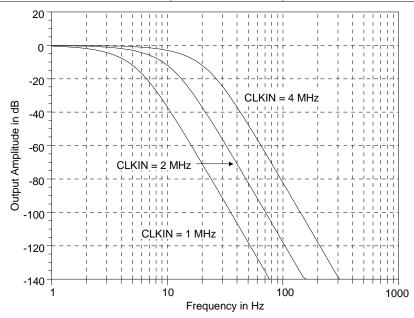

# **DYNAMIC CHARACTERISTICS**

| Parameter                              | Symbol            | Ratio          | Units |

|----------------------------------------|-------------------|----------------|-------|

| Sampling Frequency                     | f <sub>S</sub>    | CLKIN/ 256     | Hz    |

| Output Update Rate                     | fout              | CLKIN /1024    | Hz    |

| Filter Corner Frequency                | f <sub>-3dB</sub> | CLKIN /409,600 | Hz    |

| Settling Time to ±0.0007% FS (FS Step) | t <sub>s</sub>    | 506,880/CLKIN  | s     |

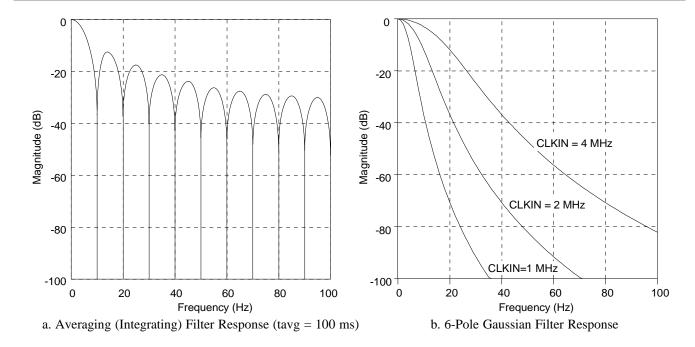

## **Frequency Response**

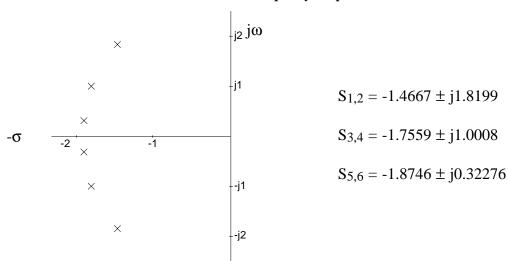

## S-Domain Pole/Zero Plot (Continuous-Time Representation)

$$\begin{split} H(x) &= [1 + 0.694x^2 + 0.241x^4 + 0.0557x^6 + 0.009664x^8 + 0.00134x^{10} + 0.000155x^{12}]^{-1/2} \\ &\text{where} \quad x = f/f_{\text{-3dB}}, \quad f_{\text{-3dB}} = CLKIN/409,600, \quad \text{and } f \text{ is the frequency of interest.} \end{split}$$

Continuous-Time Representation of 6-Pole Gaussian Filter

# **DIGITAL CHARACTERISTICS** (TA = $T_{min}$ to $T_{max}$ ; VA+, VD+ = 5V $\pm$ 10%; VA-, VD- = -5V $\pm$ 10%)

| Parameter                                                       | Symbol | Min        | Тур | Max | Units |

|-----------------------------------------------------------------|--------|------------|-----|-----|-------|

| Calibration Memory Retention Power Supply Voltage (VD+ and VA+) | VMR    | 2.0        | -   | -   | ٧     |

| High-Level Input Voltage All Except CLKIN                       | VIH    | 2.0        | -   | -   | V     |

| High-Level Input Voltage CLKIN                                  | VIH    | 3.5        | -   | -   | V     |

| Low-Level Input Voltage All Except CLKIN                        | VIL    | -          | -   | 0.8 | V     |

| Low-Level Input Voltage CLKIN                                   | VIL    | -          | -   | 1.5 | V     |

| High-Level Output Voltage (Note 9)                              | Vон    | (VD+)-1.0V | -   | -   | V     |

| Low-Level Output Voltage lout=1.6mA                             | Vol    | -          | -   | 0.4 | V     |

| Input Leakage Current                                           | lin    | -          | -   | 10  | μΑ    |

| 3-State Leakage Current                                         | loz    | -          | -   | ±10 | μΑ    |

| Digital Output Pin Capacitance                                  | Cout   | -          | 9   | -   | pF    |

Notes: 9.  $I_{out} = -100 \,\mu A$ . This guarantees the ability to drive one TTL load. ( $V_{OH} = 2.4V \, @ \, I_{out} = -40 \,\mu A$ ).

# **ABSOLUTE MAXIMUM RATINGS**

| Parameter                     |                                     | Symbol           | Min       | Max       | Units |

|-------------------------------|-------------------------------------|------------------|-----------|-----------|-------|

| DC Power Supplies:            | DC Power Supplies: Positive Digital |                  | -0.3      | (VA+)+0.3 | V     |

|                               | Negative Digital                    | VD-              | 0.3       | -6.0      | V     |

|                               | Positive Analog                     | VA+              | -0.3      | 6.0       | V     |

|                               | Negative Analog                     | VA-              | 0.3       | -6.0      | V     |

| Input Current, Any Pin Ex     | ccept Supplies (Notes 10, 11)       | lin              | -         | ±10       | mA    |

| Analog Input Voltage (AIN     | N and VREF pins)                    | VINA             | (VA-)-0.3 | (VA+)+0.3 | V     |

| Digital Input Voltage         |                                     | VIND             | -0.3      | (VA+)+0.3 | V     |

| Ambient Operating Temperature |                                     | TA               | -55       | 125       | C°    |

| Storage Temperature           |                                     | T <sub>stg</sub> | -65       | 150       | C°    |

Notes: 10. Applies to all pins including continuous overvoltage conditions at the analog input (AIN) pin.

<sup>11.</sup> Transient currents of up to 100mA will not cause SCR latch-up. Maximum input current for a power supply pin is  $\pm$  50 mA.

# RECOMMENDED OPERATING CONDITIONS (AGND, DGND = 0V) (Note 12)

|                        | Parameter        | Symbol | Min   | Тур  | Max  | Units |

|------------------------|------------------|--------|-------|------|------|-------|

| DC Power Supplies:     | Positive Digital | VD+    | 4.5   | 5.0  | VA+  | V     |

|                        | Negative Digital | VD-    | -4.5  | -5.0 | -5.5 | V     |

|                        | Positive Analog  | VA+    | 4.5   | 5.0  | 5.5  | V     |

|                        | Negative Analog  | VA-    | -4.5  | -5.0 | -5.5 | V     |

| Analog Reference Volta | ge               | VREF   | 1.0   | 2.5  | 3.0  | V     |

| Analog Input Voltage:  | (Note            | e 13)  |       |      |      |       |

|                        | Unipolar         | VAIN   | AGND  | -    | VREF | V     |

|                        | Bipolar          | VAIN   | -VREF | -    | VREF | V     |

Notes: 12. All voltages with respect to ground.

13. The CS5501 and CS5503 can accept input voltages up to the analog supplies (VA+ and VA-). They will accurately convert and filter signals with noise excursions up to 100mV beyond |VREF|. After filtering, the devices will output all 1's for any input above VREF and all 0's for any input below AGND in unipolar mode and -VREF in bipolar mode.

# **SWITCHING CHARACTERISTICS** ( $T_A = T_{min}$ to $T_{max}$ ; CLKIN=4.096 MHz; VA+, VD+ = 5V±10%; VA-, VD- = -5V ± 10%; Input Levels: Logic 0 = 0V, Logic 1 = VD+; CL = 50 pF; unless otherwise specified.)

|                        | Parameter                                       |             |                                      | Min      | Тур     | Max      | Units    |

|------------------------|-------------------------------------------------|-------------|--------------------------------------|----------|---------|----------|----------|

| Master Clock Frequency | /: Internal Gate Oscillator<br>(See Table 1)    |             | CLKIN                                | 200      | 4096    | 5000     | kHz      |

|                        | Externally Supplied: Maximum                    | (Note 14)   | CLKIN                                | -        | -       | 5000     | kHz      |

|                        | Minimum                                         | (Note 15)   | CLKIN                                | 200      | 40      | -        | kHz      |

| CLKIN Duty Cycle       |                                                 |             |                                      | 20       | -       | 80       | %        |

| Rise Times:            | Any Digital Input<br>Any Digital Output         | (Note 16)   | trise<br>trise                       | -        | -<br>20 | 1.0<br>- | μs<br>ns |

| Fall Times:            | Any Digital Input<br>Any Digital Output         | (Note 16)   | tfall<br>tfall                       | -        | -<br>20 | 1.0      | μs<br>ns |

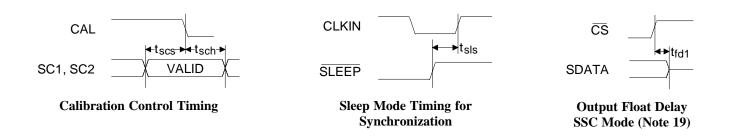

| Set Up Times:          | SC1, SC2 to CAL Low<br>SLEEP High to CLKIN High | n (Note 17) | t <sub>scs</sub><br>t <sub>sls</sub> | 100<br>1 | -       | -        | ns<br>μs |

| Hold Time:             | SC1, SC2 hold after CA                          | AL falls    | tsch                                 | 100      | -       | -        | ns       |

Notes: 14. CLKIN must be supplied whenever the CS5501 or CS5503 is not in SLEEP mode. If no clock is present when not in SLEEP mode, the device can draw higher current than specified and possibly become uncalibrated.

- 15. The CS5501/CS5503 is production tested at 4.096 MHz. It is guaranteed by characterization to operate at 200 kHz.

- 16. Specified using 10% and 90% points on waveform of interest.

- 17. In order to synchronize several CS5501's or CS5503's together using the SLEEP pin, this specification must be met.

**SWITCHING CHARACTERISTICS** (continued) (TA =  $T_{min}$  to  $T_{max}$ ; VA+, VD+ = 5V ± 10%; VA-, VD- = -5V ± 10%; Input Levels: Logic 0 = 0V, Logic 1 = VD+; CL = 50 pF)

|                                   | Parameter                                          | Symbol       | Min       | Тур              | Max              | Units |

|-----------------------------------|----------------------------------------------------|--------------|-----------|------------------|------------------|-------|

| SSC Mode (Mode = VL               | O+)                                                | 1            | I         |                  |                  |       |

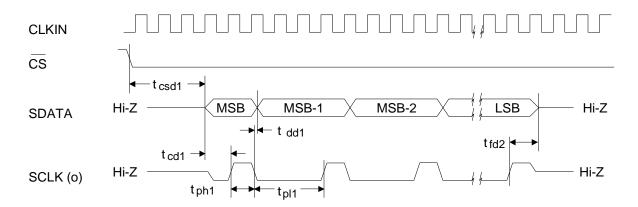

| Access Time                       | CS Low to SDATA Out                                | tcsd1        | 3/CLKIN   | -                | -                | ns    |

| SDATA Delay Time                  | SCLK Falling to New SDATA bit                      | tdd1         | -         | 25               | 100              | ns    |

| SCLK Delay Time<br>(at 4.096 MHz) | SDATA MSB bit to SCLK Rising                       | tcd1         | 250       | 380              | -                | ns    |

| Serial Clock<br>(Out)             | Pulse Width High (at 4.096 MHz)<br>Pulse Width Low | tph1<br>tpl1 | -<br>-    | 240<br>730       | 300<br>790       | ns    |

| Output Float Delay                | SCLK Rising to Hi-Z                                | tfd2         | -         | 1/CLKIN<br>+ 100 | 1/CLKIN<br>+ 200 | ns    |

| Output Float Delay                | CS High to Output Hi-Z (Note 18)                   | tfd1         | -         | -                | 4/CLKIN<br>+200  | ns    |

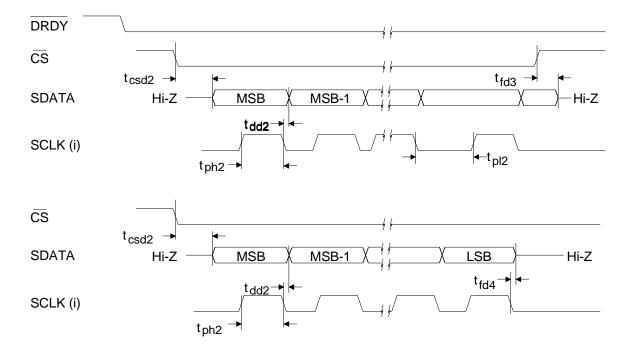

| SEC Mode (Mode = DC               | GND)                                               | •            |           |                  |                  |       |

| Serial Clock (In)                 |                                                    | fsclk        | dc        | -                | 4.2              | MHz   |

| Serial Clock (In)                 | Pulse Width High<br>Pulse Width Low                | tph2<br>tpl2 | 50<br>180 | -                | -                | ns    |

| Access Time                       | CS Low to Data Valid (Note 19)                     | tcsd2        | -         | 80               | 160              | ns    |

| Maximum Data Delay T              | ime (Note 20)<br>SCLK Falling to New SDATA bit     | tdd2         | -         | 75               | 150              | ns    |

| Output Float Delay                | CS High to Output Hi-Z                             | tfd3         | -         | -                | 250              | ns    |

| Output Float Delay                | SCLK Falling to Output Hi-Z                        | tfd4         | -         | 100              | 200              | ns    |

Notes: 18. If  $\overline{\text{CS}}$  is returned high before all data bits are output, the SDATA and SCLK outputs will complete the current data bit and then go to high impedance.

- 19. If  $\overline{CS}$  is activated asynchronously to  $\overline{DRDY}$ ,  $\overline{CS}$  will not be recognized if it occurs when  $\overline{DRDY}$  is high for 4 clock cycles. The propagation delay time may be as great as 4 CLKIN cycles plus 160 ns. To guarantee proper clocking of SDATA when using asychronous  $\overline{CS}$ , SCLK(i) should not be taken high sooner than 4 CLKIN cycles plus 160ns after  $\overline{CS}$  goes low.

- 20. SDATA transitions on the falling edge of SCLK(i).

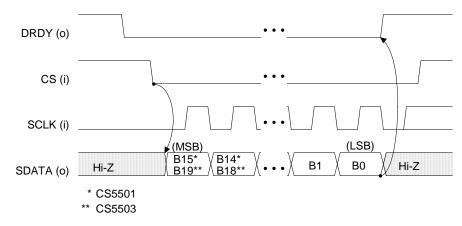

**SSC MODE Timing Relationships**

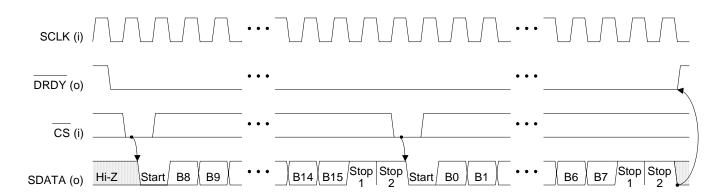

**SEC MODE Timing Relationships**

**SWITCHING CHARACTERISTICS** (continued) ( $T_A = T_{min}$  to  $T_{max}$ ;  $V_{A+}$ ,  $V_{D+} = 5V \pm 10\%$ ;  $V_{A-}$ ,  $V_{D-} = -5V \pm 10\%$ ; Input Levels: Logic  $V_{A-}$ ,  $V_{A-}$ ,

|                                                    | Parameter                           | Symbol           | Min       | Тур | Max | Units    |  |  |

|----------------------------------------------------|-------------------------------------|------------------|-----------|-----|-----|----------|--|--|

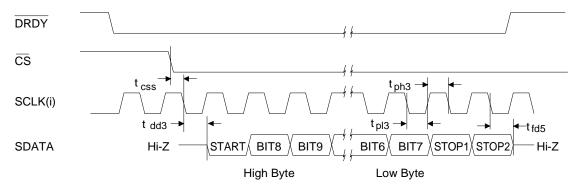

| AC Mode (Mode = VD-) CS5501 only                   |                                     |                  |           |     |     |          |  |  |

| Serial Clock (In)                                  |                                     | fsclk            | dc        | -   | 4.2 | MHz      |  |  |

| Serial Clock (In)                                  | Pulse Width High<br>Pulse Width Low | tph3<br>tpl3     | 50<br>180 | -   | -   | ns<br>ns |  |  |

| Set-up Time                                        | CS Low to SCLK Falling              | t <sub>CSS</sub> | -         | 20  | 40  | ns       |  |  |

| Maximum Data Delay Time SCLK Fall to New SDATA bit |                                     | tdd3             | -         | 90  | 180 | ns       |  |  |

| Output Float Delay                                 | CS High to Output Hi-Z (Note 21)    | tfd5             | -         | 100 | 200 | ns       |  |  |

Notes: 21. If  $\overline{\text{CS}}$  is returned high after an 11-bit data packet is started, the SDATA output will continue to output data until the end of the second stop bit. At that time the SDATA output will go to high impedance.

AC MODE Timing Relationships (CS5501 only)

## **GENERAL DESCRIPTION**

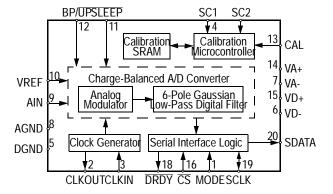

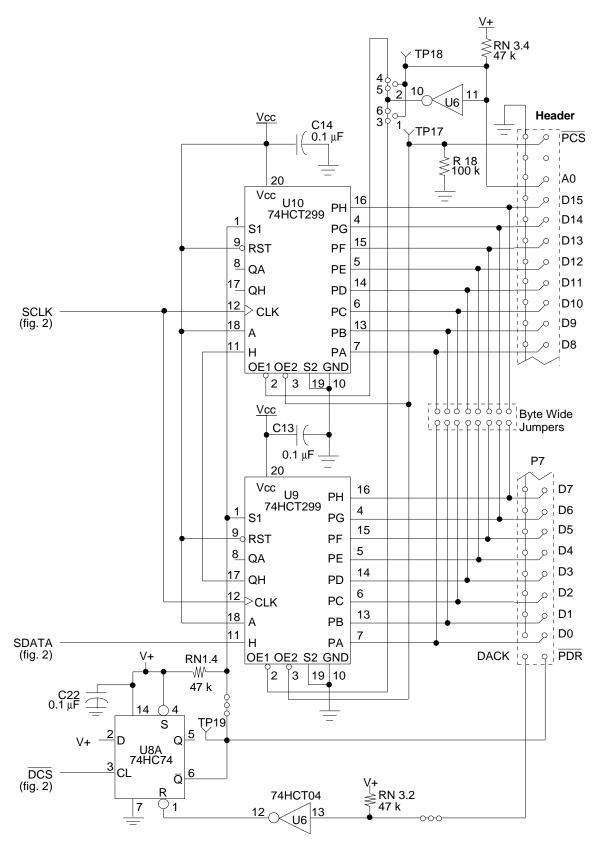

The CS5501/CS5503 are monolithic CMOS A/D converters designed specifically for high resolution measurement of low-frequency signals. Each device consists of a charge-balance converter (16-Bit for the CS5501, 20-Bit for the CS5503), calibration microcontroller with on-chip SRAM, and serial communications port.

The CS5501/CS5503 A/D converters perform conversions continuously and update their output ports after every conversion (unless the serial port is active). Conversions are performed and the serial port is updated independent of external control. Both devices are capable of measuring either unipolar or bipolar input signals, and calibration cycles may be initiated at any time to ensure measurement accuracy.

The CS5501/CS5503 perform conversions at a rate determined by the master clock signal. The master clock can be set by an external clock or with a crystal connected to the pins of the on-chip gate oscillator. The master clock frequency determines:

- 1. The sample rate of the analog input signal.

- 2. The corner frequency of the on-chip digital filter.

- 3. The output update rate of the serial output port.

The CS5501/CS5503 design includes several selfcalibration modes and several serial port interface modes to offer users maximum system design flexiblity.

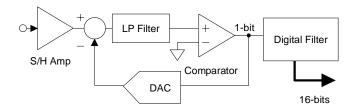

# The Delta-Sigma Conversion Method

The CS5501/CS5503 A/D converters use charge-balance techniques to achieve low cost, high resolution measurements. A charge-balance A/D converter consists of two basic blocks: an analog modulator and a digital filter. An elementary example of a charge-balance A/D converter is a conventional voltage-to-frequency converter and counter. The VFC's 1-bit output conveys infor-

mation in the form of frequency (or duty cycle), which is then filtered (averaged) by the counter for higher resolution.

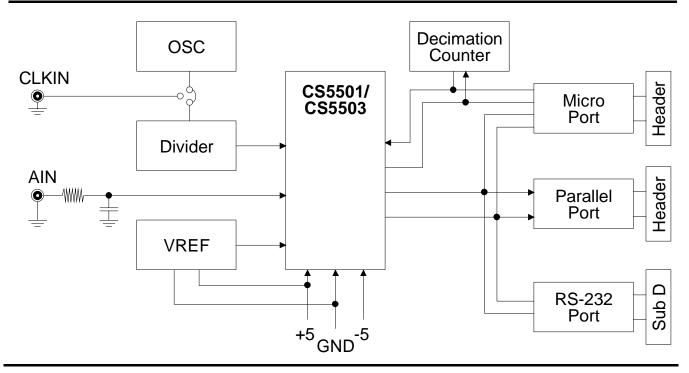

Figure 1. Charge Balance (Delta-Sigma) A/D Converter

The analog modulator of the CS5501/CS5503 is a multi-order delta-sigma modulator. The modulator consists of a 1-bit A/D converter (that is, a comparator) embedded in an analog feedback loop with high open loop gain (see Figure 1). The modulator samples and converts the input at a rate well above the bandwidth of interest. The 1-bit output of the comparator is sampled at intervals based on the clock rate of the part and this information (either a 1 or 0) is conveyed to the digital filter. The digital filter is much more sophisticated than a simple counter. The filter on the chip has a 6-pole low pass Gaussian response which rolls off at 120 dB/decade (36 dB/octave). The corner frequency of the digital filter scales with the master clock frequency. In comparison, VFC's and dual slope converters offer (sin x)/x filtering for high frequency rejection (see Figure 2 for a comparison of the characteristics of these two filter types). When operating from a 1 MHz master clock the digital filter in the CS5501/CS5503 offers better than 120 dB rejection of 50 and 60 Hz line frequencies and does not require any type of line synchronization to achieve this rejection. It should be noted that the CS5501/CS5503 will update its output port almost at 1000 times per second when operating from the 1 MHz clock. This is a much higher update rate (typically by a factor of at least 50 times) than either VFCs or dual-slope converters can offer.

For a more detailed discussion on the delta-sigma modulator see the Application note "Delta-Sigma

Figure 2. Filter Responses

A/D Conversion Technique Overview" in the application note section of the data book. The application note discusses the delta-sigma modulator and some aspects of digital filtering.

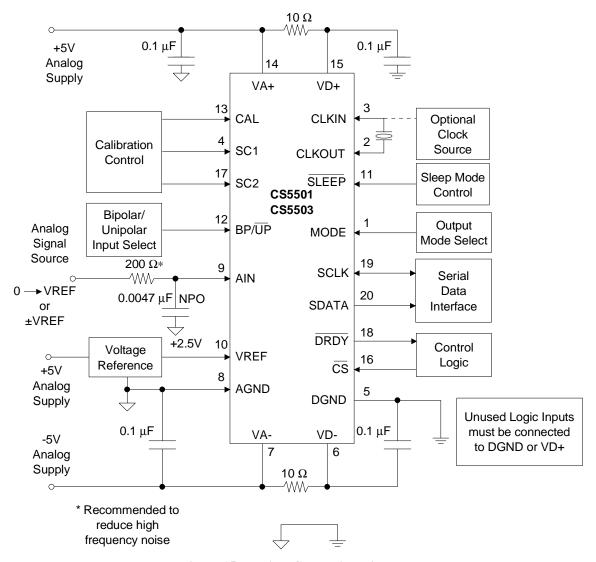

#### **OVERVIEW**

As shown in the block diagram on the front page of the data sheet, the CS5501/CS5503 can be segmented into five circuit functions. The heart of the chip is the charge balance A/D converter (16-bit for the CS5501, 20-bit for the CS5503). The converter and all of the other circuit functions on the chip must be driven by a clock signal from the clock generator. The serial interface logic outputs the converted data. The calibration microcontroller along with the calibration SRAM (static RAM), supervises the device calibration. Each segment of the chip has control lines associated with it. The function of each of the pins is described in the pin description section of the data sheet.

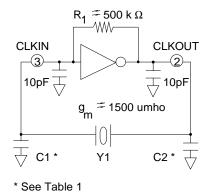

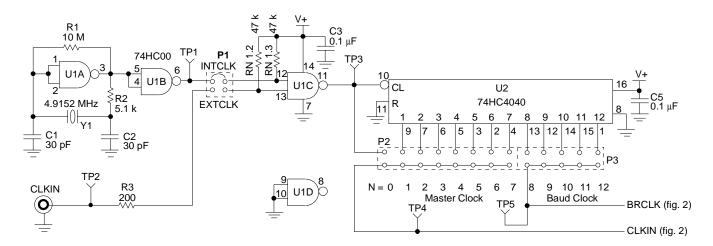

## Clock Generator

The CS5501/CS5503 both include gates which can be connected as a crystal oscillator to provide the master clock signal for the chip. Alternatively, an external (CMOS compatible) clock can be input to the CLKIN pin as the master clock for the device. Figure 3 illustrates a simple model of the on-chip gate oscillator. The gate has a typical transconductance of 1500 µmho. The gate model includes 10 pf capacitors at the input and output pins. These capacitances include the typical stray capacitance of the pins of the device. The on-chip

Figure 3. On-chip Gate Oscillator Model

gate oscillator is designed to properly operate without additional loading capacitors when using a 4.096 MHz (or 4 MHz) crystal. If other crystal frequencies or if ceramic resonators are used, loading capacitors may be necessary for reliable operation of the oscillator. Table 1 illustrates some typical capacitor values to be used with selected resonating elements.

| Resonators | C1    | C2    |

|------------|-------|-------|

| Ceramic    |       |       |

| 200 kHz    | 330pF | 470pF |

| 455 kHz    | 100pF | 100pF |

| 1.0 MHz    | 50pF  | 50pF  |

| 2.0 MHz    | 20pF  | 20pF  |

| Crystals   |       |       |

| 2.000 MHz  | 30pF  | 30pF  |

| 3.579 MHz  | 20pF  | 20pF  |

| 4.096 MHz  | None  | None  |

|            |       | I     |

**Table 1. Resonator Loading Capacitors**

CLKOUT (pin 2) can be used to drive one external CMOS gate for system clock requirements. In this case, the external gate capacitance must be taken into account when choosing the value of C2.

Caution: A clock signal should always be present whenever the  $\overline{SLEEP}$  is inactive ( $\overline{SLEEP} = VD+$ ). If no clock is provided to the part when not in  $\overline{SLEEP}$ , the part may draw excess current and possibly even lose its calibration data. This is because the device is built using dynamic logic.

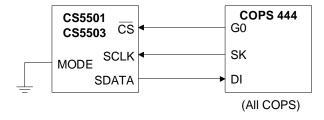

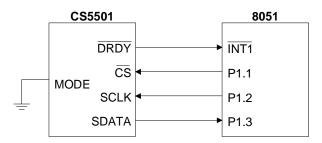

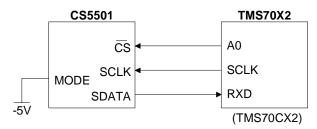

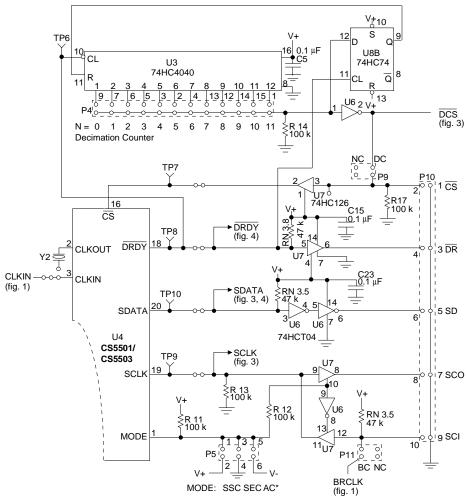

# Serial Interface Logic

The CS5501 serial data output can operate in any one of the following three different serial interface modes depending upon the MODE pin selection:

SSC (Synchronous Self-Clocking) mode; MODE pin tied to VD+ (+5V).

SEC (Synchronous External Clocking) mode; MODE pin tied to DGND.

and AC (Asynchronous Communication) mode; *CS5501 only* MODE pin tied to VD- (-5V)

The CS5503 can only operate in the first two modes, SEC and SSC.

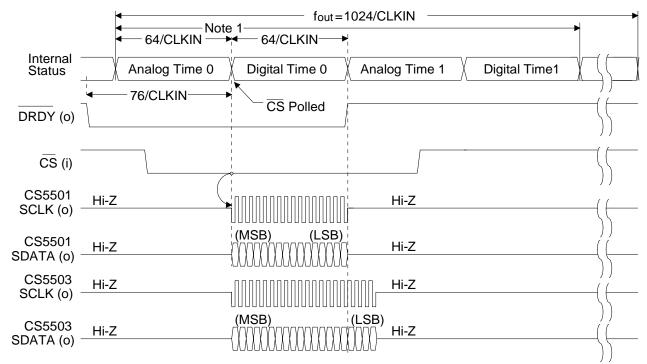

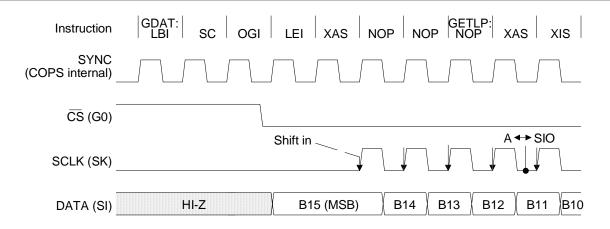

Synchronous Self-Clocking Mode

When operated in the SSC mode (MODE pin tied to VD+), the CS5501/CS5503 furnish both serial output data (SDATA) and an internally-generated serial clock (SCLK). Internal timing for the SSC mode is illustrated in Figure 4. Figure 5 shows detailed SSC mode timing for both the CS5501/CS5503. A filter cycle occurs every 1024 cycles of CLKIN. During each filter cycle, the status of CS is polled at eight specific times during the cycle. If  $\overline{CS}$  is low when it is polled, the CS5501/CS5503 begin clocking the data bits out, MSB first, at a SCLK output rate of CLKIN/4. Once transmission is complete,  $\overline{DRDY}$  rises and both SDATA and SCLK outputs go into a high impedance state. A filter cycle begins each time  $\overline{DRDY}$  falls. If the  $\overline{CS}$  line is not active,  $\overline{DRDY}$ will return high 1020 clock cycles after it falls. Four clock cycles later DRDY will fall to signal that the serial port has been updated with new data and that a new filter cycle has begun. The first  $\overline{\text{CS}}$  polling during a filter cycle occurs 76 clock cycles after  $\overline{DRDY}$  falls (the rising edge of CLKIN on which  $\overline{DRDY}$  falls is considered clock cycle number one). Subsequent pollings of  $\overline{CS}$  occur at intervals of 128 clock cycles thereafter (76, 204, 332, etc.). The  $\overline{\text{CS}}$  signal is polled at the beginning of each of eight data output windows which occur in a filter cycle. To transmit data during any one of the eight output windows,  $\overline{CS}$  must be low at least three CLKIN cycles before it is polled. If  $\overline{\text{CS}}$  does not meet this set-up time, data will not be transmitted during the window time. Furthermore,  $\overline{CS}$  is not latched internally and therefore must be held low during the entire data transmission to obtain all of the data bits.

Note: 1. There are 16 analog and digital settling periods per filter cycle (4 are shown). Data can be output in the SSC mode in only 1 of the 8 digital time periods in each filter cycle.

Figure 4. Internal Timing

Figure 5. Synchronous Self-Clocking (SSC) Mode Timing

The eighth output window time overlaps the time in which the serial output port is to be updated. If the  $\overline{CS}$  is recognized as being low when it is polled for the eighth window time, data will be output as normal, but the serial port will not be updated with new data until the next serial port update time. Under these conditions, the serial port will experience an update rate of only 2 kHz

(CLKIN = 4.096 MHz) instead of the normal 4 kHz serial port update rate.

Upon completion of transmission of all the data bits, the SCLK and SDATA outputs will go to a high impedance state even with  $\overline{CS}$  held low. In the event that  $\overline{CS}$  is taken high before all data bits are output, the SDATA and SCLK outputs will

complete the current data bit output and go to a high impedance state when SCLK goes low.

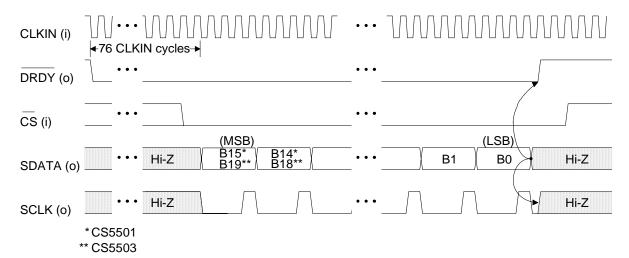

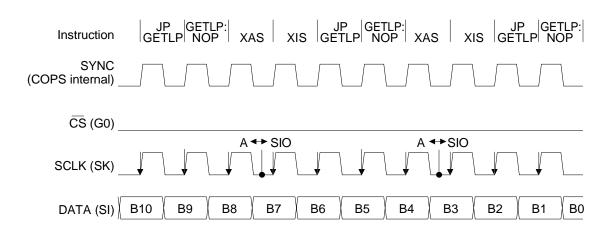

Synchronous External Clocking Mode

When operated in the SEC mode (MODE pin tied to DGND), the CS5501/CS5503 outputs the data in its serial port at a rate determined by an external clock which is input into the SCLK pin. In this mode the output port will be updated every 1024 CLKIN cycles. DRDY will go low when new data is loaded into the output port. If CS is not active, DRDY will return positive 1020 CLKIN cycles later and remain so for four CLKIN cycles. If  $\overline{CS}$  is taken low it will be recognized immediately unless it occurs while DRDY is high for the four clock cycles. As soon as CS is recognized, the SDATA output will come out of its high-impedance state and present the MSB data bit. The MSB data bit will remain present until a falling edge of SCLK occurs to advance the output to the MSB-1 bit. If the CS and external SCLK are operated asynchronously to CLKIN, errors can result in the output data unless certain precautions are taken. If  $\overline{CS}$  is activated asynchronously, it may occur during the four clock cycles when DRDY is high and therefore not be recognized immediately. To be certain that data misread errors will not result if CS occurs at this time, the SCLK input should not transition high to latch the MSB until four CLKIN cycles plus 160 ns after CS is taken low.

This insures that  $\overline{CS}$  will be recognized and the MSB bit will become stable before the SCLK transitions positive to latch the MSB data bit.

When SCLK returns low the serial port will present the MSB-1 data bit on its output. Subsequent cycles of SCLK will advance the data output. When all data bits are clocked out, DRDY will then go high and the SDATA output will go into a high impedance state. If the  $\overline{CS}$  input goes low and all of the data bits are not clocked out of the port, filter cycles will continue to occur but the output serial port will not be updated with new data ( $\overline{DRDY}$  will remain low). If  $\overline{CS}$  is taken high at any time, the SDATA output pin will go to a high impedance state. If any of the data bits in the serial port have not been clocked out, they will remain available until DRDY returns high for four clock cycles. After this DRDY will fall and the port will be updated with a new 16-bit word in the CS5501 or 20-bit word in the CS5503. It is acceptable to clock out less than all possible data bits if CS is returned high to allow the port to be updated. Figure 6 illustrates the serial port timing in the SEC mode.

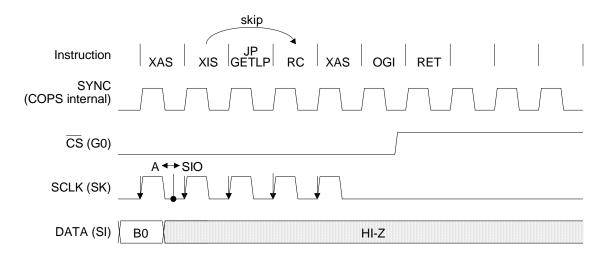

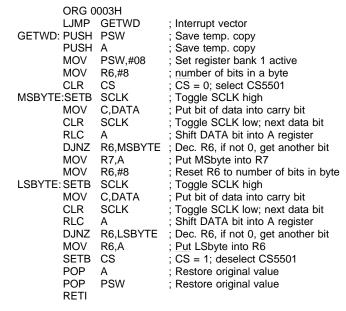

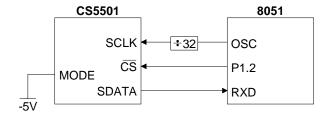

Asynchronous Communication Mode (CS5501 Only)

In the CS5501, the AC mode is activated when the MODE pin is tied to VD- (-5 V). When operating in the AC mode the CS5501 is designed to

Figure 6. Synchronous External-Clocking (SEC) Mode Timing

provide data output in UART compatible format. The baud rate of the SDATA output will be determined by the rate of the SCLK input. The data which is output of the SDATA pin will be formatted such that it will contain two 11 bit data packets. Each packet includes one start bit, eight data bits, and two stop bits. The packet which carries the most-significant-byte data will be output first, with its lsb being the first data bit output after the start bit.

In this mode, DRDY will occur every 1024 clock cycles. If the serial port is not outputting a data byte, DRDY will return high after 1020 clock cycles and remain high for 4 clock cycles. DRDY will then go low to indicate that an update to the serial output port with a new 16 bit word has occurred. To initiate a transmission from the port the CS line must be taken low. Then SCLK, which is an input in this mode, must transition from a high to a low to latch the state of  $\overline{CS}$  internal to the CS5501. Once  $\overline{CS}$  is recognized and latched as a low, the port will begin to output data. Figure 7 details the timing for this output. CS can be returned high before the end of the 11-bit transmission and the transmission will continue until the second stop bit of the first 11-bit packet is output. The SDATA output will go into a high impedance state after the second stop bit is output. To obtain the second 11-bit packet  $\overline{CS}$  must again be brought low before  $\overline{DRDY}$  goes high or the second 11-bit data packet will be overwritten with

a serial port update. For the second 11-bit packet,  $\overline{\text{CS}}$  need only to go low for 50 ns; it need not be latched by a falling edge of SCLK. Alternately, the  $\overline{\text{CS}}$  line can be taken low and held low until both 11-bit data packets are output. This is the preferred method of control as it will prevent losing the second 11-bit data packet if the port is updated. Some serial data rates can be quite slow compared to the rate at which the CS5501 can update its output port. A slow data rate will leave only a short period of time to start the second 11-bit packet if  $\overline{\text{CS}}$  is returned high momentarily. If  $\overline{\text{CS}}$  is held low continuously ( $\overline{\text{CS}}$  hard-wired to DGND), the serial port will be updated only after all 22 bits have been clocked out of the port.

Upon the completion of a transmission of the two 11-bit data packets the SDATA output will go into a high impedance state. If at any time during transmission the  $\overline{\text{CS}}$  is taken back high, the current 11-bit data packet will continue to be output. At the end of the second stop bit of the data packet, the SDATA output will go into a high impedance state.

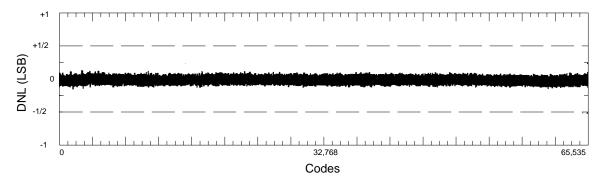

# Linearity Performance

The CS5501/CS5503 delta-sigma converters are like conventional charge-balance converters in that they have no source of nonmonotonicity. The devices therefore have no missing codes in their transfer functions. See Figure 8 for a plot of the

Figure 7. CS5501 Asynchronous (UART) Mode Timing

Figure 8. CS5501 Differential Nonlinearity Plot

excellent differential linearity achieved by the CS5501. The CS5501/CS5503 also have excellent integral linearity, which is accomplished with a well-designed charge-balance architecture. Each device also achieves low input drift through the use of chopper-stabilized techniques in its input stage. To assure that the CS5501/CS5503 achieves excellent performance over time and temperature, it uses digital calibration techniques to minimize offset and gain errors to typically within  $\pm 1/2$  LSB at 16 bits in the CS5501 and  $\pm 4$  LSB at 20 bits in the CS5503.

## **Converter Calibration**

The CS5501/CS5503 offer both self-calibration and system level calibration capability. To understand the calibration features, a basic comprehension of the internal workings of the converter are helpful. As mentioned previously in this data sheet, the converter consists of two sections. First is the analog modulator which is a delta-sigma type charge-balance converter. This is followed by a digital filter. The filter circuitry is actually an arithmetic logic unit (ALU) whose architecture and instructions execute the filter function. The modulator (explained in more detail in the applications note "Delta-Sigma Conversion Technique Overview") uses the VREF voltage connected to pin 10 to determine the magnitude of the voltages used in its feedback DAC. The modulator accepts an analog signal at its input and produces a data stream of 1's and 0's as its output. This data stream value can change

(from 1 to 0 or vice versa) every 256 CLKIN cycles. As the input voltage increases the ratio of 1's to 0's out of the modulator increases proportionally. The 1's density of the data stream out of the modulator therefore provides a digital representation of the analog input signal where the 1's density is defined as the ratio of the number of 1's to the number of 0's out of the modulator for a given period of time. The 1's density output of the modulator is also a function of the voltage on the VREF pin. If the voltage on the VREF pin increases in value (say, due to temperature drift), and the analog input voltage into the modulator remains constant, the 1's density output of the modulator will decrease (less 1's will occur). The analog input into the modulator which is necessary to produce a given binary output code from the converter is ratiometric to the voltage on the VREF pin. This means that if VREF increases by one per cent, the analog signal on AIN must also increase by one per cent to maintain the same binary output code from the converter.

For a complete calibration to occur, the calibration microcontroller inside the device needs to record the data stream 1's density out of the modulator for two different input conditions. First, a "zero scale" point must be presented to the modulator. Then a "full scale" point must be presented to the modulator. In unipolar self-cal mode the zero scale point is AGND and the full scale point is the voltage on the VREF pin. The calibration microcontroller then remembers the 1's density out of the modulator for each of these points and calculates a slope factor (LSB/ $\mu$ V). This slope factor

represents the gain slope for the input to output transfer function of the converter. In unipolar mode the calibration microcontroller determines the slope factor by dividing the span between the zero point and the full scale point by the total resolution of the converter (2<sup>16</sup> for the CS5501, resulting in 65,536 segments or 2<sup>20</sup> for the CS5503, resulting in 1,048,578 segments). In bipolar mode the calibration microcontroller divides the span between the zero point and the full scale point into 524,288 segments for the CS5503 and 32,768 segments for the CS5501. It then extends the measurement range 524,288 segments for the CS5503, 32,768 segments for the CS5501, below the zero scale point to achieve bipolar measurement capability. In either unipolar or bipolar modes the calculated slope factor is saved and later used to calculate the binary output code when an analog signal is present at the AIN pin during measurement conversions.

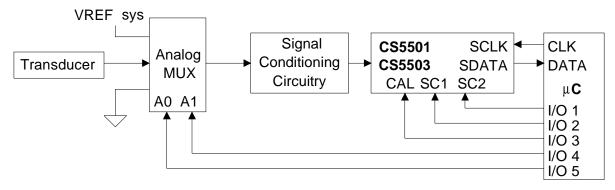

System calibration allows the A/D converter to compensate for system gain and offset errors (see

Figure 9). System calibration performs the same slope factor calculations as self-cal but uses voltage values presented by the system to the AIN pin for the zero scale point and for the full scale Table 2 depicts the calibration modes point. available. Two system calibration modes are listed. The first mode offers system level calibration for system offset and for system gain. This is a two-step calibration. The zero scale point (system offset) must be presented to the converter first. The voltage that represents zero scale point must be input to the converter before the calibration step is initiated and must remain stable until the step is complete. The DRDY output from the converter will signal when the step is complete by going low. After the zero scale point is calibrated, the voltage representing the full scale point is input to the converter and the second calibration step is initiated. Again the voltage must remain stable throughout the calibration step.

This two-step calibration mode offers another calibration feature. After a two-step calibration

Figure 9. System Calibration

| CAL | SC1 | SC2 | Cal Type      | ZS Cal | FS Cal | Sequence | Calibration Time           |

|-----|-----|-----|---------------|--------|--------|----------|----------------------------|

| 7   | 0   | 0   | Self-Cal      | AGND   | VREF   | One Step | 3,145,655/f <sub>clk</sub> |

| 7   | 1   | 1   | System Offset | AIN    | -      | 1st Step | 1,052,599/f <sub>clk</sub> |

| ¥   | 0   | 1   | & System Gain | -      | AIN    | 2nd Step | 1,068,813/f <sub>clk</sub> |

| 7_  | 1   | 0   | System Offset | AIN    | VREF   | One Step | 2,117,389/f <sub>clk</sub> |

<sup>\*</sup> DRDY remains high throughout the calibration sequence. In Self-Cal mode (SC1 and SC2 low) DRDY falls once the CS5501 or CS5503 has settled to the analog input. In all other modes DRDY falls immediately after the calibration term has been determined.

**Table 2. Calibration Control**

sequence (system offset and system gain) has been properly performed, additional offset calibrations can be performed by themselves to reposition the gain slope (the slope factor is not changed) to adjust its zero reference point to the new system zero reference value.

A second system calibration mode is available which uses an input voltage for the zero scale calibration point, but uses the VREF voltage as the full scale calibration point.

Whenever a system calibration mode is used, there are limits to the amount of offset and to the amount of span which can be accommodated. The range of input span which can be accommodated in either unipolar or bipolar mode is restricted to not less than 80% of the voltage on VREF and not more than 200% of (VREF + 0.1) V. The amount of offset which can be calibrated depends upon whether unipolar or bipolar mode is being used. In unipolar mode the system calibration modes can handle offsets as positive as 20% of VREF (this is restricted by the minimum span requirement of 80% VREF) or as negative as -(VREF + 0.1) V. This capability enables the unipolar mode of the CS5501/CS5503 to be calibrated to mimic bipolar mode operation.

In the bipolar mode the system offset calibration range is restricted to a maximum of ±40% of VREF. It should be noted that the span restrictions limit the amount of offset which can be calibrated. The span range of the converter in bipolar mode extends an equidistance (+ and -) from the voltage used for the zero scale point. When the zero scale point is calibrated it must not cause either of the two endpoints of the bipolar transfer function to exceed the positive or the negative input overrange points (+(VREF + 0.1) V or - (VREF +0.1) V). If the span range is set to a minimum (80% VREF) the offset voltage can move ±40% VREF without causing the end points of the transfer function to exceed the overrange points. Alternatively, if the span range is set to 200% of VREF, the input offset cannot move more than +0.1 or - 0.1 V before an endpoint of the transfer function exceeds the input overrange limit.

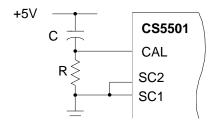

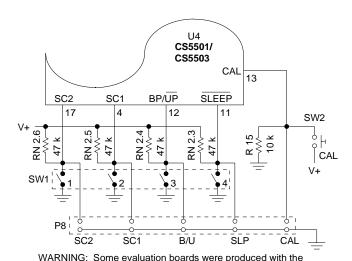

# Initiating Calibration

Table 2 illustrates the calibration modes available in the CS5501/CS5503. Not shown in the table is the function of the BP/UP pin which determines whether the converter is calibrated to measure bipolar or unipolar signals. A calibration step is initiated by bringing the CAL pin (13) high for at least 4 CLKIN cycles to reset the part and then bringing CAL low. The states of SC1 (pin 4) and SC2 (pin 17) along with the BP/UP (pin 12) will determine the type of calibration to be performed. The SC1 and SC2 inputs are latched when CAL goes low. The BP/UP input is not latched and therefore must remain in a fixed state throughout the calibration and measurement cycles. Any time the state of the BP/UP pin is changed, a new calibration cycle must be performed to enable the CS5501/CS5503 to properly function in the new mode.

When a calibration step is initiated, the DRDY signal will go high and remain high until the step is finished. Table 2 illustrates the number of clock cycles each calibration requires. Once a calibration step is initiated it must finish before a new calibration step can be executed. In the two step system calibration mode, the offset calibration step must be initiated before initiating the gain calibration step.

When a self-cal is completed  $\overline{DRDY}$  falls and the output port is updated with a data word that represents the analog input signal at the AIN pin. When a system calibration step is completed,  $\overline{DRDY}$  will fall and the output port will be updated with the appropriate data value (zero scale point, or full scale point). In the system calibration mode, the digital filter must settle before the output code will represent the value of the analog input signal.

|            |            |             | 1LSB            |            |               |               |  |

|------------|------------|-------------|-----------------|------------|---------------|---------------|--|

| Cal Mode   | Zero Scale | Gain Factor | Unipolar Bipola |            | olar          |               |  |

|            |            |             | CS5501          | CS5503     | CS5501        | CS5503        |  |

|            |            |             | VREF            | VREF       | 2VREF         | 2VREF         |  |

| Self-Cal   | AGND       | VREF        | 65,536          | 1,048,526  | 65,536        | 1,048,526     |  |

|            |            |             | SGAIN-SOFF      | SGAIN-SOFF | 2(SGAIN-SOFF) | 2(SGAIN-SOFF) |  |

| System Cal | SOFF       | SGAIN       | 65,536          | 1,048,526  | 65,536        | 1,048,526     |  |

Table 3. Output Code Size After Calibration

| Input Voltage              |                   | Input Voltage, Bipolar Mode |                |                   |                          |

|----------------------------|-------------------|-----------------------------|----------------|-------------------|--------------------------|

|                            |                   | Output Co                   | odes (Hex)     |                   |                          |

| System-Cal                 | Self-Cal          | CS5501                      | CS5503         | Self-Cal          | System Cal               |

| >(SGAIN - 1.5 LSB)         | >(VREF - 1.5 LSB) | FFFF                        | FFFFF          | >(VREF - 1.5 LSB) | >(SGAIN - 1.5 LSB)       |

| SGAIN - 1.5 LSB            | VREF - 1.5 LSB    | FFFF<br>FFFE                | FFFFF<br>FFFFE | VREF - 1.5 LSB    | SGAIN - 1.5 LSB          |

| (SGAIN - SOFF)/2 - 0.5 LSB | VREF/2 - 0.5 LSB  | 8000<br>7FFF                | 80000<br>7FFF  | AGND - 0.5 LSB    | SOFF -0.5 LSB            |

| SOFF + 0.5 LSB             | AGND + 0.5 LSB    | 0001<br>0000                | 00001<br>00000 | -VREF+ 0.5 LSB    | -SGAIN + 2SOFF + 0.5 LSB |

| <(SOFF + 0.5 LSB)          | <(AGND+0.5 LSB)   | 0000                        | 00000          | <(-VREF+0.5 LSB)  | <(-SGAIN+2SOFF+0.5 LSB)  |

**Table 4. Output Coding**

Tables 3 and 4 indicate the output code size and output coding of the CS5501/CS5503 in its various modes. The calibration equations which represent the CS5501/CS5503 transfer function are shown in Figure 10.

DOUT = Slope (AIN - Unipolar Offset) + 0.5 LSB

a. Unipolar Calibration

CS5501

DOUT = Slope (AIN - Bipolar Offset) + 2<sup>15</sup> + 0.5 LSB16

CS5503

DOUT = Slope(AIN - Bipolar Offset) + 2<sup>19</sup> + 0.5 LSB20

b. Bipolar Calibration

Figure 10. Calibration Equations

# **Underrange And Overrange Considerations**

The input signal range of the CS5501/CS5503 will be determined by the mode in which the part is calibrated. Table 4 indicates the input signal range in the various modes of operation. If the input signal exceeds the full scale point the converter will output all ones. If the signal is less than the zero scale point (in unipolar) or more negative in magnitude than minus the full scale point (in bipolar) it will output all zeroes.

Note that the modulator-filter combination in the chip CS5501/CS5503 is designed to accurately convert and filter input signals with noise excursions which extend up to 100 mV below the analog value which produces all zeros out or above the analog value which produces all ones out. Overrange noise excursions greater than 100 mV may increase output noise.

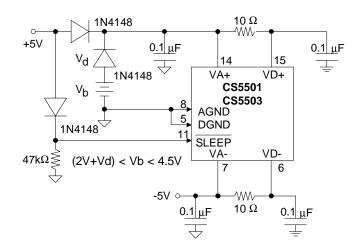

All pins of the CS5501/CS5503 include diodes which clamp the input signals to within the positive and negative supplies. If a signal on any pin (including AIN) exceeds the supply voltage (either

+ or -) a clamp diode will be forward-biased. Under these fault conditions the CS5501/CS5503 might be damaged. Under normal operating conditions (with the power supplies established), the device will survive transient currents through the clamp diodes up to 100 mA and continuous currents up to 10 mA. The drive current into the AIN pin should be limited to a safe value if an overvoltage condition is likely to occur. See the application note "Buffer Amplifiers for the CS501X Series of A/D Converters" for further discussion on the clamp diode input structure and on current limiting circuits.

# System Synchronization

If more than one CS5501/CS5503 is included in a system which is operating from a common clock, all of the devices can be synchronized to sample and output at exactly the same time. This can be accomplished in either of two ways. First, a single CAL signal can be issued to all the CS5501/CS5503's in the system. To insure synchronization on the same clock signal the CAL signal should go low on the falling edge of CLKIN. Or second, a common SLEEP control signal can be issued. If the SLEEP signal goes positive with the appropriate set up time to CLKIN, all parts will be synchronized on the same clock cycle.

# **Analog Input Impedance Considerations**

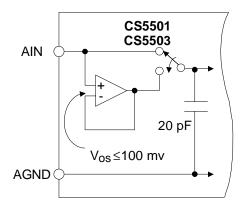

The analog input of the CS5501/CS5503 can be modeled as illustrated in Figure 11. A 20 pF capacitor is used to dynamically sample the input signal. Every 64 CLKIN cycles the switch alternately connects the capacitor to the output of the buffer and then directly to the AIN pin. Whenever the sample capacitor is switched from the output of the buffer to the AIN pin, a small packet of charge (a dynamic demand of current) will be required from the input source to settle the voltage on the sample capacitor to its final value. The voltage at the output of the buffer may differ up to 100 mV from the actual input voltage due to

Figure 11. Analog Input Model

the offset voltage of the buffer. Timing allows 64 cycles of master clock (CLKIN) for the voltage on the sample capacitor to settle to its final value. The equation which defines settling time is:

$$V_e = V_{max} e^{-t/RC}$$

Where Ve is the final settled value,  $V_{max}$  is the maximum error voltage value of the input signal, R is the value of the input source resistance, C is the 20 pF sample capacitor plus the value of any stray or additional capacitance at the input pin. The value of t is equal to 64/CLKIN.

$V_{max}$  occurs the instance when the sample capacitor is switched from the buffer output to the AIN pin. Prior to the switch, AIN has an error estimated as being less than or equal to  $V_e$ .  $V_{max}$  is equal to the prior error ( $V_e$ ) plus the additional error from the buffer offset. The estimate for  $V_{max}$  is:

$$V_{\text{max}} = V_e + 100 \text{mV} \frac{20 \text{pF}}{(20 \text{pF} + C_{\text{EXT}})}$$

Where C<sub>EXT</sub> is the combination of any external or stray capacitance.

From the equation which defines settling time, an equation for the maximum acceptable source resistance is derived

equation which defines settling time, an equation for the maximum acceptable source resistance is derived

$$Rs_{max} = \frac{-64}{CLKIN(20pF+C_{EXT}) \ln \left[ \frac{V_e}{V_e + \frac{20pF(100mv)}{(20pF+C_{EXT})}} \right]}$$

This equation assumes that the offset voltage of the buffer is 100 mV, which is the worst case. The value of Ve is the maximum error voltage which is acceptable.

For a maximum error voltage (Ve) of 10  $\mu$ V in the CS5501 (1/4LSB at 16-bits) and 600 nV in the CS5503 (1/4LSB at 20-bits), the above equation indicates that when operating from a 4.096 MHz CLKIN, source resistances up to 84 k $\Omega$  in the CS5501 or 64 k $\Omega$  in the CS5503 are acceptable in the absence of external capacitance (CEXT = 0). If higher input source resistances are desired the master clock rate can be reduced to yield a longer settling time for the 64 cycle period.

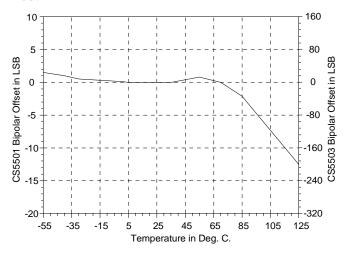

Figure 12. Typical Self-Cal Bipolar Offset vs. Temperature After Calibration at 25  $^{\circ}\mathrm{C}$

# Analog Input Drift Considerations

The CS5501/CS5503 analog input uses chopperstabilization techniques to minimize input offset drift. Charge injection in the analog switches and leakage currents at the sampling node are the primary sources of offset voltage drift in the converter. Figure 12 indicates the typical offset drift due to temperature changes experienced after calibration at 25 °C. Drift is relatively flat up to about 75 °C. Above 75 °C leakage current becomes the dominant source of offset drift. Leakage currents approximately double with each 10 °C of temperature increase. Therefore the offset drift due to leakage current increases as the temperature increases. The value of the voltage on the sample capacitor is updated at a rate determined by the master clock, therefore the amount of offset drift which occurs will be proportional to the elapsed time between samples. In conclusion, the offset drift increases with temperature and is inversely proportional to the CLKIN rate. minimize offset drift with increased temperature, higher CLKIN rates are desirable. At temperatures above 100 °C, a CLKIN rate above 1 MHz is recommended. The effects of offset drift due to temperature changes can be eliminated by recalibrating the CS5501/CS5503 whenever the temperature has changed.

Gain drift within the converter depends predominately upon the temperature tracking of internal capacitors. Gain drift is not affected by leakage currents, therefore gain drift is significantly less than comparable offset errors due to temperature increases. The typical gain drift over the specified temperature range is less than 2.5 LSBs for the CS5501 and less than 40 LSBs for the CS5503.

Measurement errors due to offset drift or gain drift can be eliminated at any time by recalibrating the converter. Using the system calibration mode can also minimize offset and gain errors in the signal conditioning circuitry. The CS5501/CS5503 can be recalibrated at any temperature to remove the effects of these errors.

Linearity and differential non linearity are not significantly affected by temperature changes.

#### **Filtering**

At the system level, the digital filter in the CS5501/CS5503 can be modeled exactly like an analog filter with a few minor differences. Digital filtering resides *behind* the A/D conversion and can thus reject noise injected during the conversion process (i.e. power supply ripple, voltage reference noise, or noise in the ADC itself). Analog filtering cannot.

Also, since digital filtering resides behind the A/D converter, noise riding unfiltered on a near-full-scale input could potentially overrange the ADC. In contrast, analog filtering removes the noise before it ever reaches the converter. To address this issue, the CS5501/CS5503 each contain an analog modulator and digital filter which reserve headroom such that the device can process signals with 100mV "excursions" above full-scale and still output accurately converted and filtered data. Filtered input signals above full-scale still result in an output of all ones.

The digital filter's corner frequency occurs at CLKIN/409,600, where CLKIN is the master clock frequency. With a 4.096MHz clock, the

filter corner is at 10Hz and the output register is updated at a 4kHz rate. CLKIN frequency can be reduced with a proportional reduction in the filter corner frequency and in the update rate to the output register. A plot of the filter response is shown in the specification tables section of this data sheet.

Both the CS5501/CS5503 employ internal digital filtering which creates a 6-pole Gaussian relationship. With the corner frequency set at 10Hz for minimized settling time, the CS5501/CS5503 offer approximately 55dB rejection at 60Hz to signals coming into either the AIN or VREF pins. With a 5Hz cut-off, 60Hz rejection increases to more than 90dB.

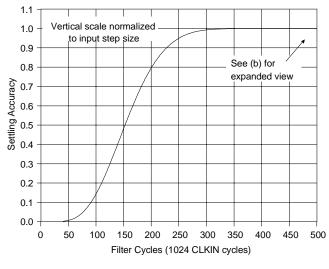

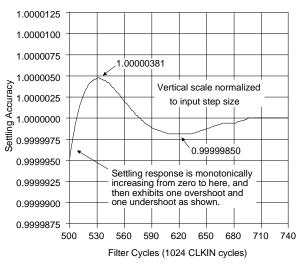

The digital filter (rather than the analog modulator) dominates the converters' settling for step-function inputs. Figure 13 illustrates the settling characteristics of the filter. The vertical axis is normalized to the input step size. The horizontal axis is in filter cycles. With a full scale input step (2.5 V in unipolar mode) the output will exhibit an overshoot of about 0.25 LSB<sub>16</sub> in the CS5501 and 4 LSB<sub>20</sub> in the CS5503.

(a) Settling Time Due to Input Step Change

(b) Expanded Version of (a)

#### Anti-Alias Considerations

The digital filter in the CS5501/CS5503 does not provide rejection around integer multiples of the oversampling rate [(N\*CLKIN)/256], where N=1,2,3,...]. That is, with a 4.096 MHz master clock the noise on the analog input signal within the narrow  $\pm 10$  Hz bands around the 16 kHz, 32 kHz, 48 kHz, etc., passes unfiltered to the digital output. Most broadband noise will be very well filtered because the CS5501/CS5503 use a very high oversampling ratio of 800 (16 kHz:  $2\times10$  Hz). Broadband noise is reduced by:

$$e_{out} = e_{in} \sqrt{2f_{-3dB}/f_s}$$

$$e_{out} = 0.035 e_{in}$$

where  $e_{in}$  and  $e_{out}$  are rms noise terms referred to the input. Since  $f_{-3dB}$  equals CLKIN/409,600 and  $f_s$  equals CLKIN/256, the digital filter reduces white, broadband noise by 96.5% independent of the CLKIN frequency. For example, a typical operational amplifier's  $50\mu V$  rms noise would be reduced to  $1.75\mu V$  rms (0.035 LSB's rms at the 16-bit level in the CS5501 and 0.4 LSB's rms at the 20-bit level in the CS5503).

Simple high frequency analog filtering in the signal conditioning circuitry can aid in removing energy at multiples of the sampling rate.

| Bits of<br>Output<br>Accuracy | Filter<br>Cycles | CLKIN<br>Cycles |

|-------------------------------|------------------|-----------------|

| 9                             | 340              | 348,160         |

| 10                            | 356              | 364,544         |

| 11                            | 389              | 398,336         |

| 12                            | 435              | 445,440         |

| 13                            | 459              | 470,016         |

| 14                            | 475              | 486,400         |

| 15                            | 486              | 497,664         |

| 16                            | 495              | 506,880         |

| 17                            | 500              | 512,000         |

| 18                            | 504              | 516,096         |

| 19                            | 506              | 518,144         |

| 20                            | 507              | 519,168         |

Table 5. Settling Time of the 6 Pole Low Pass Filter in the CS5501 to 1/2 LSB Accuracy with a Full Scale Step Input

## Post Filtering

Post filtering is useful to enhance the noise performance of the CS5503. With a constant input voltage the output codes from the CS5503 will exhibit some variation due to noise. The CS5503 has typically 1.6 LSB<sub>20</sub> rms noise in its output codes. Additional variation in the output codes can arise due to noise from the input signal source and from the voltage reference. Post filtering (digital averaging) will be necessary to achieve less than 1 LSB p-p noise at the 20-bit level. The CS5503 has peak noise less than the 18-bit level without additional filtering if care is exercised in the design of the voltage reference and the input signal condition circuitry. Noise in the bandwidth from dc to 10 Hz on both the AIN and VREF inputs should be minimized to ensure maximum performance. As the amount of noise will be highly system dependent, a specific recommendation for post filtering for all applications cannot be stated. The following guidelines are helpful. Realize that the digital filter in the CS5503, like any other low pass filter, acts as an information storage unit. The filter retains past information for a period of time even after the input signal has changed. The implication of this is that immediately sequential 20-bit updates to the serial port contain highly correlated information. To most efficiently post filter the CS5503 output data, uncorrelated samples should be used. Samples which have sufficiently reduced correlation can be obtained if the CS5503 is allowed to execute 200 filter cycles between each subsequent data word collected for post filtering.

The character of the noise in the data will influence the post filtering requirements. As a general rule, averaging N uncorrelated data samples will reduce noise by  $1/\sqrt{N}$ . While this rule assumes that the noise is white (which is true for the CS5503 but not true for all real system signals between dc and 10Hz), it does offer a starting point for developing a post filtering algorithm for removing the noise from the data. The algorithm

will have to be empirically tested to see if it meets the system requirements. It is recommended that any testing include input signals across the entire input span of the converter as the signal level will affect the amount of noise from the reference input which is transferred to the output data.

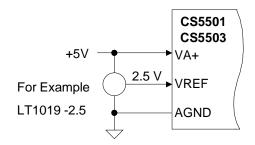

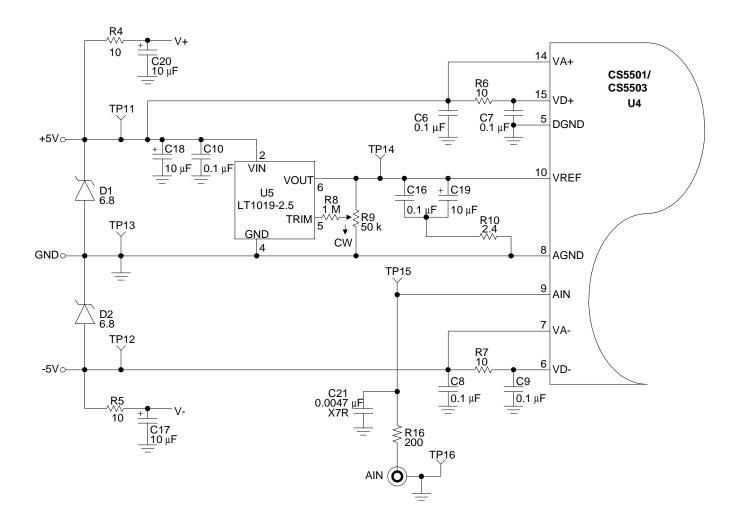

# Voltage Reference

The voltage reference applied to the VREF input pin defines the analog input range of the CS5501/CS5503. The preferred reference is 2.5V, but the device can typically accept references from 1V to 3V. Input signals which exceed 2.6V (+ or -) can cause some linearity degradation. Figure 14 illustrates the voltage reference connections to the CS5501/CS5503.

Figure 14. Voltage Reference Connections

The circuitry inside the VREF pin is identical to that as seen at the AIN pin. The sample capacitor (see Figure 12) requires packets of charge from the external reference just as the AIN pin does. Therefore the same settling time requirements apply. Most reference IC's can handle this dynamic load requirement without inducing errors. They exhibit sufficiently low output impedance and wide enough bandwidth to settle to within the necessary accuracy in the requisite 64 CLKIN cycles.

Noise from the reference is filtered by the digital filter, but the reference should be chosen to minimize noise below 10 Hz. The CS5501/CS5503 typically exhibit 0.1 LSB rms and 1.6 LSB rms noise respectively. This specification assumes a clean reference voltage. Many monolithic

band-gap references are available which can supply 2.5 V for use with the CS5501/CS5503. Many of these devices are not specified for noise, especially in the 0.1 to 10 Hz bandwidth. Some of these devices may exhibit noise characteristics which degrade the performance of the CS5501/CS5503.

# Power Supplies And Grounding

The CS5501/CS5503 use the analog ground connection, AGND, as a measurement reference node. It carries no power supply current. The AGND pin should be used as the reference node for both the analog input signal and for the reference voltage which is input into the VREF pin.

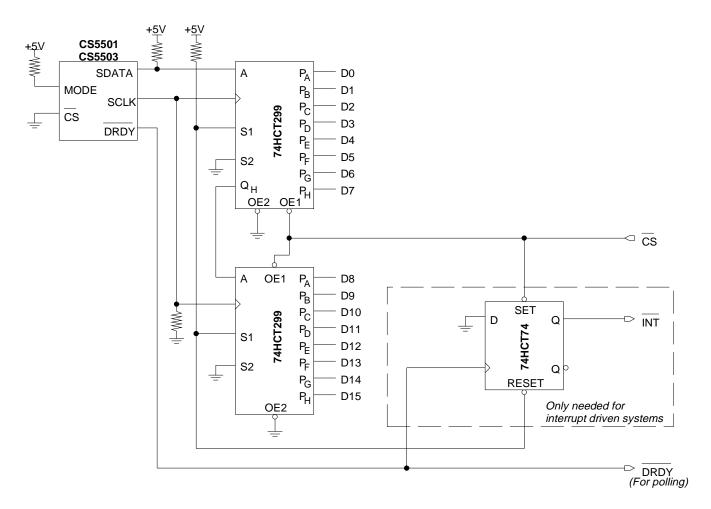

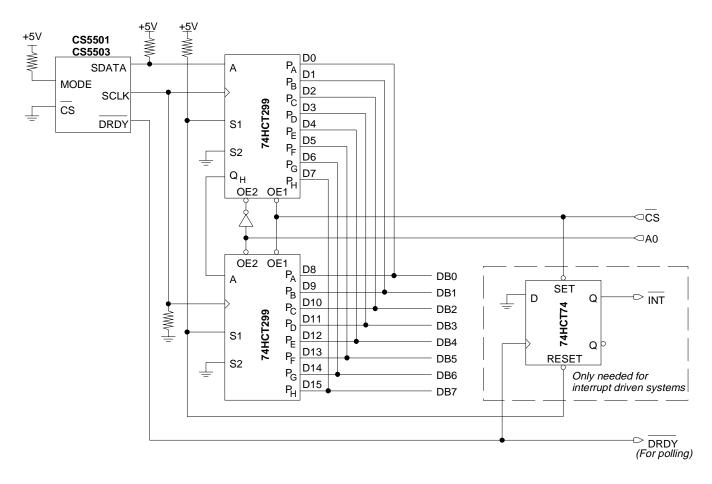

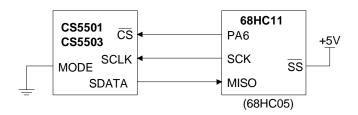

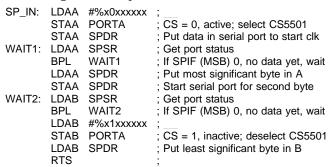

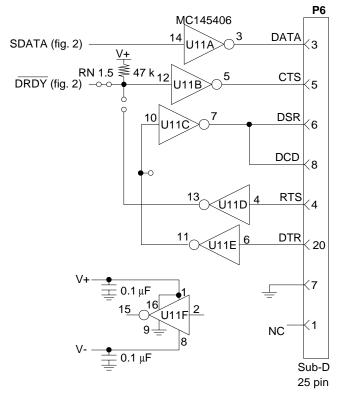

The analog and digital supply inputs are pinned out separately to minimize coupling between the analog and digital sections of the chip. To achieve maximum performance, all four supplies for the CS5501/CS5503 should be decoupled to their respective grounds using 0.1  $\mu$ F capacitors. This is illustrated in the System Connection Diagram, Figure 15, at the beginning of this data sheet.