# THIS DOCUMENT IS FOR MAINTENANCE PURPOSES ONLY AND IS NOT RECOMMENDED FOR NEW DESIGNS

## **SL2364**

### **VERY HIGH PERFORMANCE TRANSISTOR ARRAYS**

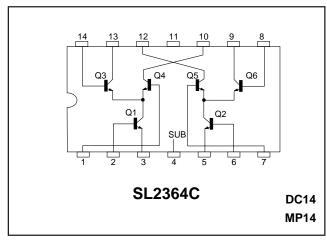

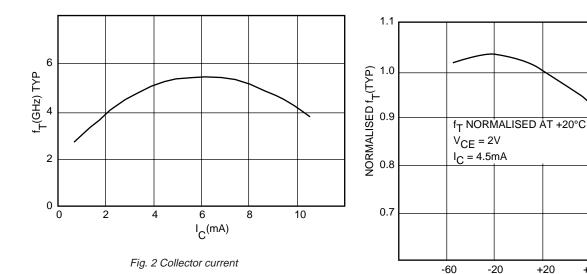

The SL2364 is an array of transistors internally connected to form a dual long-tailed pair with tail transistors. This is a monolithic integrated circuit manufactured on a very high speed bipolar process which has a minimum useable  $f_T$  of 2.5GHz, (typically 5GHz).

The SL2364 is in a 14 SO package and a high performance Dilmon encapsulation.

#### **FEATURES**

- Complete Dual Long-Tailed Pair in One Package

- Very High f⊤ Typically 5 GHz

- Very Good Matching Including Thermal Matching

#### **APPLICATIONS**

- Wide Band Amplification Stages

- 140 and 560 MBit PCM Systems

- Fibre Optic Systems

- High Performance Instrumentation

- Radio and Satellite Communications

Fig. 1 Pin connections (top view)

#### **ELECTRICAL CHARACTERISTICS**

These characteristics are guaranteed of the following conditions (unless otherwise stated):  $T_{amb} = 22^{\circ}C \pm 2^{\circ}C$

| Characteristics                                                                                                                                   | Value                             |                                                     |      | Units                             | Conditions                                                                                                                                                                                                                                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------------------------------------------------|------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                   | Min.                              | Тур.                                                | Max. | Oilles                            | Conditions                                                                                                                                                                                                                                                                                                             |

| $\begin{array}{c} BV_CBO \\ LV_CEO \\ BV_EBO \\ BV_CIO \\ h_FE \\ f_T \\ \Delta V_BE (See \ note \ 1) \\ \Delta V_BE / T_AMB \\ C_CB \end{array}$ | 10<br>6<br>2.5<br>16<br>50<br>2.5 | 20<br>9<br>5.0<br>40<br>80<br>5<br>2<br>-1.7<br>0.5 | 5    | V<br>V<br>V<br>GHz<br>mV<br>mV/°C | $I_{c} = 10\mu A$ $I_{c} = 5mA$ $I_{E} = 10\mu A$ $I_{C} = 10\mu A$ $I_{C} = 8mA, V_{CE} = 2V$ $I_{C} = 7mA, V_{CE} = 2V$ $I_{C} = 9mA, V_{CE} = 2V$ $I_{C} = 9mA, V_{CE} = 2V$ |

| C <sub>CI</sub>                                                                                                                                   |                                   | 1.0                                                 | 1.5  | pF                                | $V_{CI} = 0$                                                                                                                                                                                                                                                                                                           |

NOTE 1.  $\Delta V_{BE}$  applies to  $|V_{BEQ3} - V_{BEQ4}|$  and  $|V_{BEQ5} - V_{BEQ6}|$

#### **TYPICAL CHARACTERISTICS**

Fig. 3 Chip temperature

+20

TEMPERATURE (°C)

+60

+100

+140

#### **ABSOLUTE MAXIMUM RATINGS**

Maximum individual transistor dissipation 200mW

Storage temperature -55°C to + 150°C Maximum junction temperature + 150°C

Package thermal resistance (°C/W):

35 (DC14) Chip to case 45 (MP14) Chip to ambient 123 (MP14) 120 (DC14)

VCBO = 10V, VEBO = 2 5V VCEO = 6V. VCIO = 15V IC (any one transistor) = 20mA

The substrate should be connected to the most negative point of the circuit to maintain electrical isolation between the transistors.