# IP2012 / IP2022 Wireless Network Processors

Features and Performance Optimized for Network Connectivity

# 1.0 Product Highlights

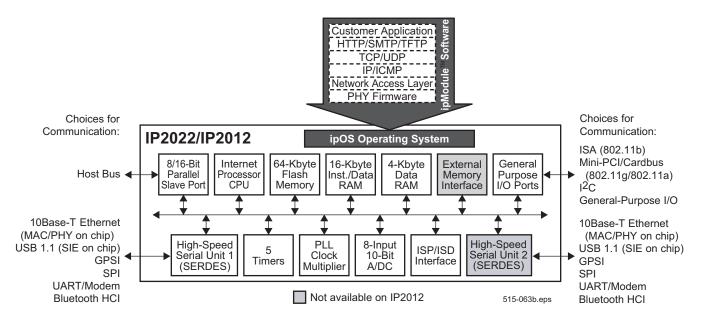

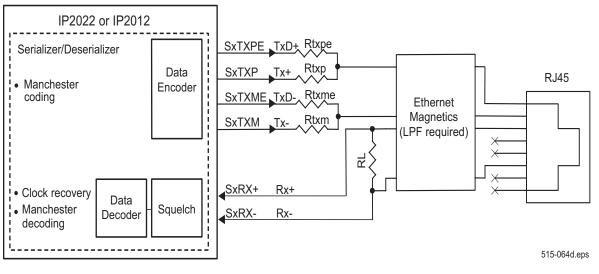

The Ubicom IP2012<sup>™</sup> and IP2022<sup>™</sup> Wireless Network Processors combine support for communication physical layer, Internet protocol stack, device-specific application, and device-specific peripheral software modules in a single chip, and are reconfigurable over the Internet. They can be programmed, and reprogrammed, using pre-built software modules and configuration tools to create true single-chip solutions for a wide range of device-to-device and device-to-human communication applications. High speed communication interfaces are available via on-chip hardware Serializer/Deserializer (SerDes) blocks. These full-duplex blocks allow the IP2022 or IP2012 to be used in a variety of communication bridging applications. Each SerDes block is capable of supporting 10Base-T Ethernet (MAC and PHY), USB, GPSI, SPI, or UART. The highspeed operating frequency, combined with most instructions executing in a single cycle, delivers the throughput needed for emerging network connectivity applications. A flash-based program memory allows both in-system and runtime reprogramming. The IP2022 and IP2012 implement most peripheral, communications and control functions via software modules (ipModule™ software), replacing traditional hardware for maximum system design flexibility. This approach allows rapid,

inexpensive product design and, when needed, quick and easy reconfiguration to accommodate changes in market needs or industry standards.

#### Key Features:

- Designed to support single-chip networked solutions

- Fast processor core

- 64kB Flash program memory

- 16kB SRAM data/program memory

- 4kB SRAM data memory

- Two SerDes communication blocks supporting common PHYs (Ethernet, USB, UARTs, etc.) and bridging applications (IP2012 has only one SerDes unit)

- Advanced RISC processors

- IP2022 120 and 160 MHz versions

- IP2012 120 MHz version

- · High speed packet processing

- · Instruction set optimized for communication functions

- Supports software implementation of traditional hardware functions

- In-system reprogrammable for highest flexibility

- Run time self-programmable

- Vpp = Vcc supply voltage

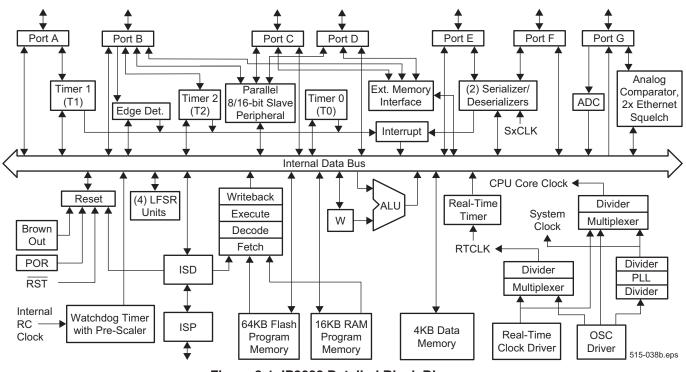

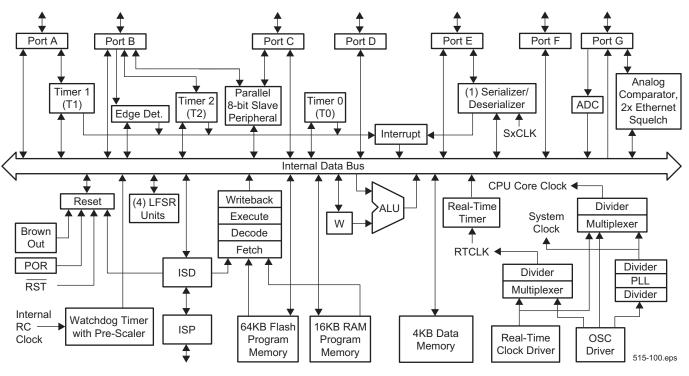

#### Figure 1-1 IP2012 / IP2022 Block Diagram

| 1.0 Pro        | duct Highlights                                                   | 1         |

|----------------|-------------------------------------------------------------------|-----------|

| 1.1            | Additional Features                                               | 3         |

| 1.2            | Architecture.                                                     |           |

| 1.2.1<br>1.2.2 | CPUSerializer/Deserializers                                       |           |

| 1.2.3          | Low-Power Support                                                 |           |

| 1.2.4          | Memory                                                            | 4         |

| 1.2.5<br>1.2.6 | Instruction Set Other Supported Functions                         | 4         |

| 1.2.7          | Programming and Debugging Support                                 | 5         |

| 2.0 Pin        | Definitions                                                       | 6         |

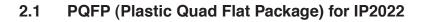

| 2.1            | PQFP (Plastic Quad Flat Package) for IP2022                       |           |

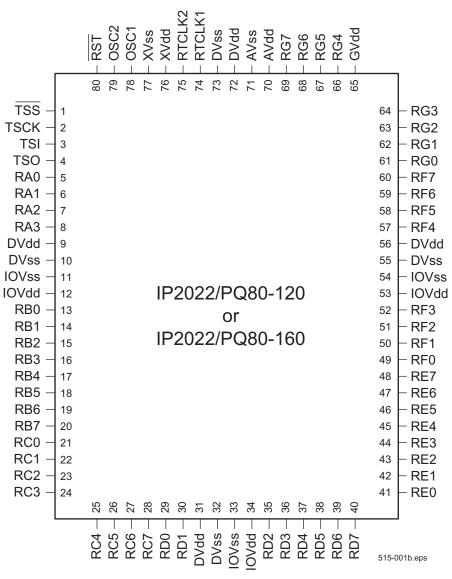

| 2.2            | PQFP (Plastic Quad Flat Package) for IP2012                       | 7         |

| 2.3            | µBGA (Micro Ball Grid Array) IP2022-120 Only                      | 8         |

| 2.4            | Signal Descriptions – IP2022                                      | 9         |

| 2.5            | Signal Descriptions – IP2012                                      |           |

| -              | tem Architecture                                                  | 15        |

| 3.1            | CPU Registers                                                     | .16       |

| 3.2            | Data Memory                                                       | .19       |

| 3.3<br>3.3.1   | Program Memory                                                    | .19<br>10 |

| 3.3.2          | Program Counter                                                   | .20       |

| 3.4            | Low Power Support                                                 | .20       |

| 3.4.1          | Clock Stop Mode (SLEEP)                                           |           |

| 3.4.2<br>3.5   | Wakeup                                                            | .21<br>21 |

| 3.6            | Instruction Timing                                                |           |

| 3.7            | Interrupt Support.                                                |           |

| 3.7.1          | Interrupt Processing                                              | .22       |

| 3.7.2          | Global Interrupt Enable Bit                                       |           |

| 3.7.3<br>3.7.4 | Interrupt Latency                                                 | .25       |

| 3.7.5          | Return From Interrupt<br>Disabled Interrupt Resources             | .26       |

| 3.8            | Reset                                                             |           |

| 3.8.1<br>3.8.2 | Brown-Out Detector                                                |           |

| 3.8.3          | Register States Following Reset                                   | .28       |

| 3.9            | Clock Oscillator.                                                 | .29       |

| 3.9.1          | External Connections                                              |           |

| 3.10<br>3.10.1 | Configuration Block<br>FUSE0 Register (not run-time programmable) | .31       |

| 3.10.1         | FUSE1 Register (not run-time programmable)                        |           |

| 3.10.3         | TRIM0 Register                                                    | .34       |

| 4.0 Inst       | ruction Set Architecture                                          | 35        |

| 4.1            | Addressing Modes                                                  | .35       |

| 4.1.1          | Pointer Registers                                                 | .35       |

| 4.1.2<br>4.1.3 | Direct Addressing Mode                                            | .36       |

| 4.1.3          | Indirect-with-Offset Addressing Mode                              | .37       |

| 4.2            | Instruction Set.                                                  | .38       |

| 4.2.1          | Instruction Formats                                               | .38       |

| 4.2.2<br>4.3   | Instruction Types                                                 | .38       |

| 4.4            | Subroutine Call/Return Stack                                      | .40<br>41 |

| 4.5            | Key to Abbreviations and Symbols                                  |           |

| 4.6            | Instruction Set Summary Tables.                                   | .42       |

| 4.7            | Program Memory Instructions                                       | .47       |

| 4.7.1          | Flash Timing Control Interrupts During Flash Operations           | .48       |

| 4.7.2          | ipherals                                                          | .40<br>49 |

|                | -                                                                 |           |

| 5.1<br>5.1.1   | I/O Ports                                                         | .49<br>49 |

| 5.1.2          | Reading and Writing the Ports                                     | .50       |

| 5.1.3          | RxIN Registers                                                    | .50       |

| 5.1.4<br>5.1.5 | RxOUT Registers                                                   |           |

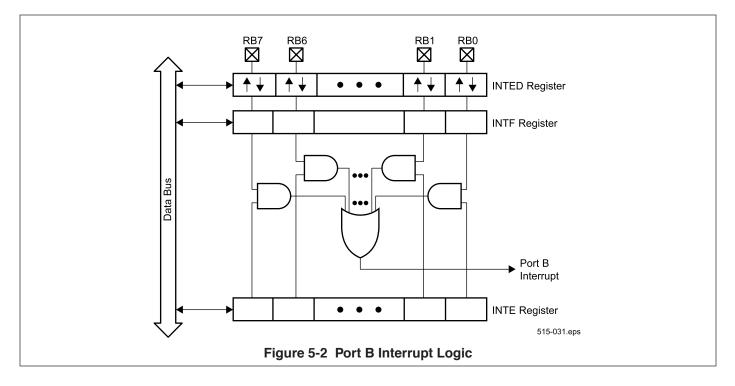

| 5.1.5          | INTED Register                                                    |           |

| 5.1.7          | INTF Regišter                                                     | .51       |

| 5.1.8          | INTE Register Port Configuration Upon Power-Up                    | .51       |

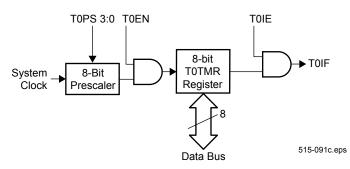

| 5.1.9<br>5.2   | Timer 0                                                           |           |

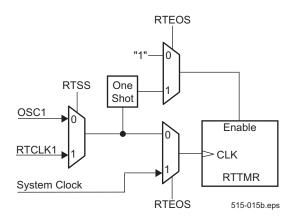

| 5.3            | Real-Time Timer (RTTMR)                                           | .52       |

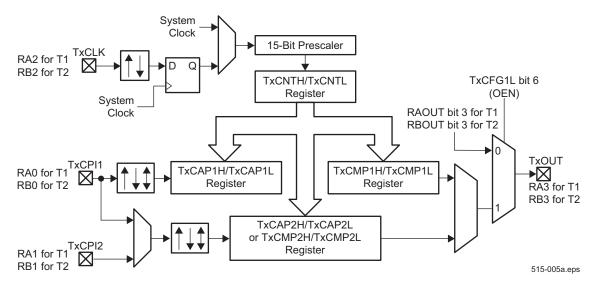

| 5.4            | Multi-Function Timers (T1 and T2)                                 | .54       |

| 5.4.1          | Timers T1, T2 Operating Modes                                     | .54       |

| 5.4.2          | T1 and T2 Timer Pin Assignments                                   | . 30      |

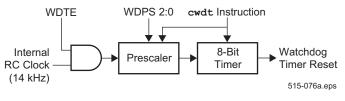

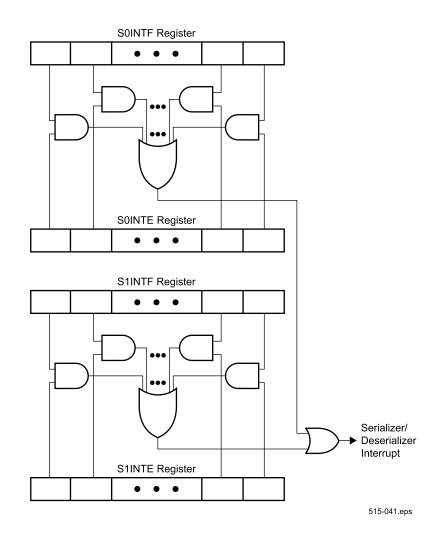

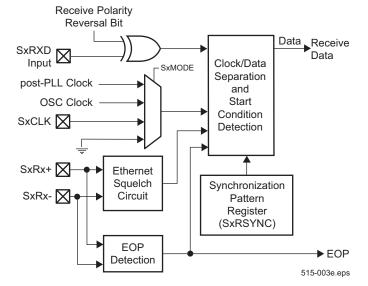

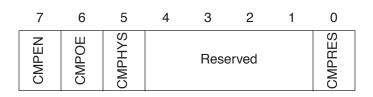

| 5.4.3<br>5.5<br>5.6<br>5.6.1<br>5.6.2<br>5.6.3<br>5.6.5<br>5.6.5<br>5.6.6<br>5.6.7<br>5.6.8<br>5.7<br>5.7.1<br>5.7.2<br>5.7.3<br>5.7.4<br>5.7.3<br>5.7.4<br>5.8.1<br>5.9<br>5.10.1<br>5.11<br>5.11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | T1 and T2 Timer Registers<br>Watchdog Timer (WDT)<br>Serializer/Deserializer (SERDES).<br>SERDES TX/RX Buffers<br>SERDES Configuration.<br>SERDES Interrupts<br>Protocol Modes<br>10base-T Ethernet.<br>USB.<br>UART.<br>SPI.<br>GPSI<br>Analog to Digital Converter (ADC)<br>ADC Reference Voltage<br>A/D Converter Registers.<br>Using the A/D Converter.<br>ADC Result Justification<br>Comparator.<br>CMPCFG Register<br>Linear Feedback Shift Register (LFSR)<br>Parallel Slave Peripheral (PSP)<br>PSPCFG Register<br>External Memory Interface (IP2022 only).<br>EMCFG Register (IP2022 only).                                                                                                              | 57<br>58<br>58<br>59<br>60<br>61<br>64<br>67<br>64<br>67<br>72<br>72<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>73<br>79<br>80                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.0 In-S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | System Programming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | mory Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 7.0.1<br>7.0.2<br>7.1<br>7.1.1<br>7.1.2<br>7.1.3<br>7.1.4<br>7.1.5<br>7.1.6<br>7.1.7<br>7.1.6<br>7.1.7<br>7.1.6<br>7.1.7<br>7.1.10<br>7.1.11<br>7.1.12<br>7.1.13<br>7.1.14<br>7.1.15<br>7.1.16<br>7.1.11<br>7.1.12<br>7.1.13<br>7.1.14<br>7.1.15<br>7.1.10<br>7.1.11<br>7.1.12<br>7.1.10<br>7.1.11<br>7.1.22<br>7.1.23<br>7.1.20<br>7.1.21<br>7.1.22<br>7.1.23<br>7.1.22<br>7.1.23<br>7.1.24<br>7.1.22<br>7.1.22<br>7.1.23<br>7.1.24<br>7.1.22<br>7.1.22<br>7.1.24<br>7.1.22<br>7.1.24<br>7.1.22<br>7.1.20<br>7.1.21<br>7.1.22<br>7.1.21<br>7.1.22<br>7.1.21<br>7.1.22<br>7.1.21<br>7.1.22<br>7.1.21<br>7.1.22<br>7.1.21<br>7.1.22<br>7.1.21<br>7.1.22<br>7.1.21<br>7.1.22<br>7.1.21<br>7.1.22<br>7.1.21<br>7.1.22<br>7.1.21<br>7.1.22<br>7.1.21<br>7.1.22<br>7.1.22<br>7.1.22<br>7.1.22<br>7.1.22<br>7.1.22<br>7.1.22<br>7.1.22<br>7.1.22<br>7.1.22<br>7.1.22<br>7.1.22<br>7.1.22<br>7.1.22<br>7.1.22<br>7.1.22<br>7.1.22<br>7.1.22<br>7.1.22<br>7.1.22<br>7.1.22<br>7.1.22<br>7.1.22<br>7.1.22<br>7.1.22<br>7.1.22<br>7.1.22<br>7.1.22<br>7.1.22<br>7.1.22<br>7.1.22<br>7.1.22<br>7.1.22<br>7.1.22<br>7.1.22<br>7.1.22<br>7.1.22<br>7.1.22<br>7.1.22<br>7.1.22<br>7.1.22<br>7.1.22<br>7.1.22<br>7.1.22<br>7.1.22<br>7.1.22<br>7.1.22<br>7.1.22<br>7.1.22<br>7.1.22<br>7.1.22<br>7.1.22<br>7.1.22<br>7.1.22 | Registers (sorted by address)<br>Program Memory .<br>Register Bit Definitions .<br>ADCCFG Register .<br>ADCTMR Register .<br>CMPCFG Register .<br>EMCFG Register (IP2022 only) .<br>FCFG Register .<br>INTSPD Register .<br>LFSRA Register .<br>SYNTE/SRA Register .<br>SXINTE/SRA Register .<br>SXINTF Register .<br>SXINTF Register .<br>SXRCFG Register .<br>SXRCFG Register .<br>SXRCTG Register .<br>SXRCTG Register .<br>SXRCTG Register .<br>SXRCTG Register .<br>SXTCFG Register .<br>SXTCFG Register .<br>SXTCFG Register .<br>SXTCFG Register .<br>SXTMRH/SXTMRL Register .<br>STATUS Register .<br>TATUS Register .<br>TXCFG1H Register .<br>TXCFG2L Register .<br>TCTRL Register .<br>TCTRL Register . | 88<br>89<br>89<br>90<br>91<br>93<br>93<br>94<br>93<br>93<br>94<br>95<br>96<br>96<br>97<br>97<br>98<br>98<br>99<br>99<br>99<br>99<br>99<br>91<br>91<br>92<br>93<br>94<br>94<br>95<br>95<br>96<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br>97<br> |

| 7.1.26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | XCFG Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | .104                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 8.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Absolute Maximum Ratings)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | DC Specifications: IP2022-120, IP2012-120<br>DC Specifications: IP2022-160.<br>AC Specifications: IP2022-120, IP2012-120<br>AC Specifications: IP2022-160.<br>Comparator DC and AC Specifications<br>ADC 10-bit Converter DC and AC Specifications.                                                                                                                                                                                                                                                                                                                                                                                                                                                                | .106<br>.108<br>.110<br>.111<br>.112                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

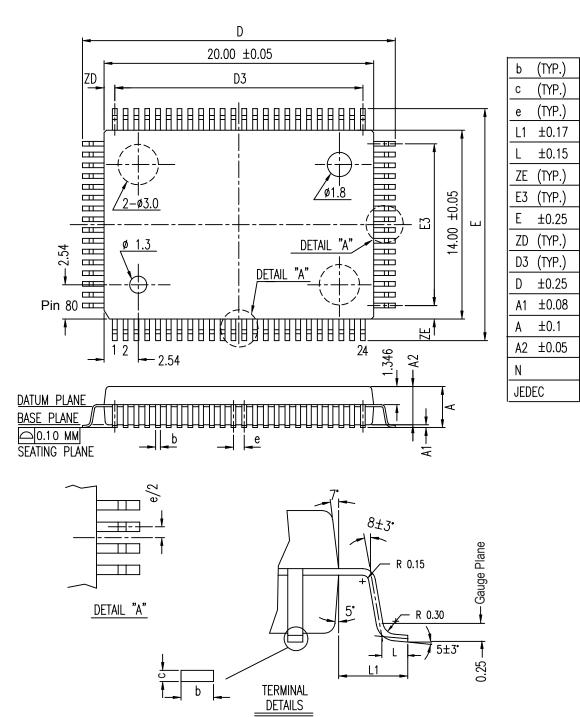

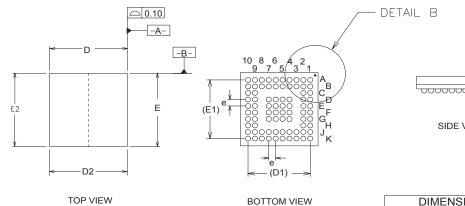

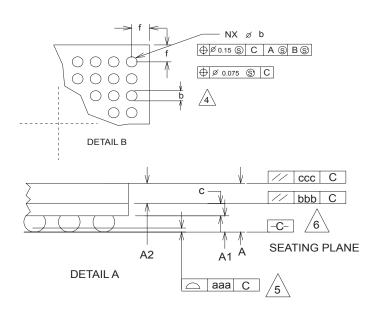

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | kage Dimensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 113                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 9.1<br>9.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | PQFP<br>µBGA (available for IP2022-120 only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | .113<br>.114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

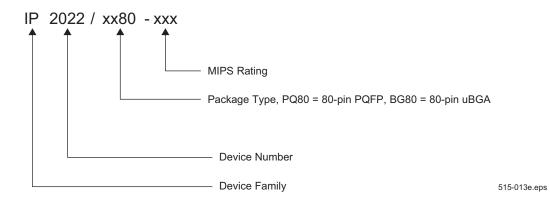

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | irt Numbering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 115                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

# 1.1 Additional Features

#### **Internet Processor Capabilities**

Foundation for Highly Flexible Connectivity Solution

- Performance: 120 MIPS @ 120 MHz, 160 MIPS @ 160 MHz

- Predictable execution for hard real-time applications

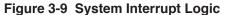

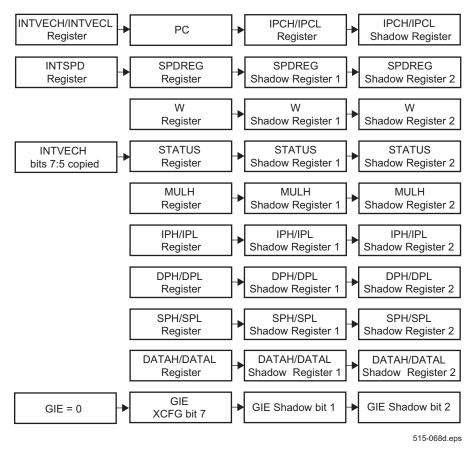

- Fast and deterministic 3-cycle (25ns @120MHz, 18.75ns @ 160 MHz) internal interrupt response

- Hardware save/store of key registers

- Functions implemented via software tightly coupled with hardware assist peripherals

# Multiple Networking Protocols and Physical Layer Support Hardware

- Two full-duplex serializer/deserializer (SERDES) channels (IP2022 has two, IP2012 has one)

- Flexible to support 10Base-T, GPSI, SPI, UART, USB protocols

- Two channels for protocol bridging

- On-chip squelch function for 10Base-T Ethernet on each SERDES

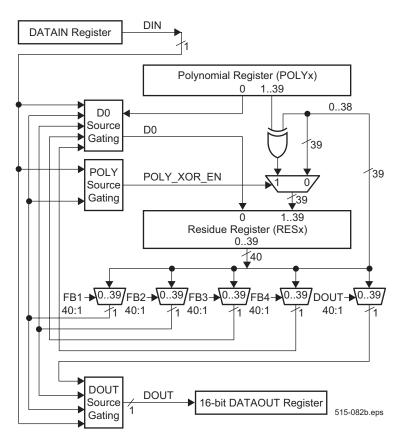

- Four hardware LFSR (Linear Feedback Shift Register) units

- CRC generation/checking

- Data whitening

- Encryption

#### Memory

- 64-Kbyte ( $32K \propto 16$ ) on-chip program flash memory

- 16-Kbyte (8K  $\infty$  16) on-chip program/data RAM

- 4-Kbyte on-chip linear-addressed data RAM

- Self-programming with built-in charge pump: instructions to read, write, and erase flash memory

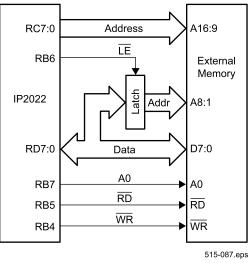

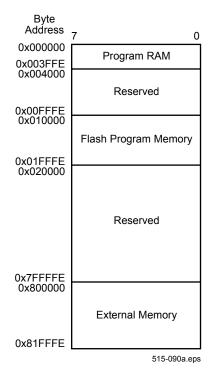

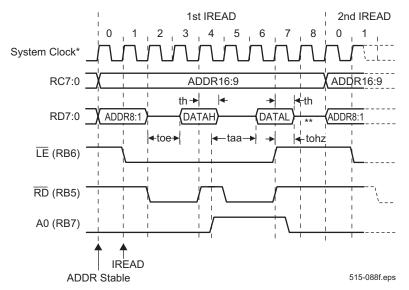

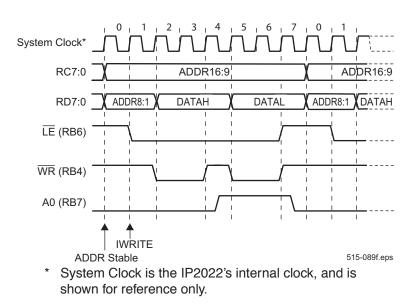

- Addresses up to 2 Mbytes of external memory (IP2022 only)

#### **CPU Features**

- RISC engine core

- IP2022-120, IP2012-120

- DC to 120 MHz operation

- 8.33 ns instruction cycle at max frequency

- IP2022-160

- DC to 120 MHz and 160 MHz operation only

- 6.25 ns instruction cycle at max frequency

- Compact 16-bit fixed-length instructions

- Single-cycle instruction execution on most instructions (3 cycles for jumps and calls)

- Sixteen-level hardware stack for high-performance subroutine linkage

- $8 \propto 8$  signed/unsigned single-cycle multiply

- · Pointers and stack operation optimized for C compiler

- Uniform, linear address space (no register banks)

#### **General-Purpose Hardware Peripherals**

- Two 16-bit timers with 8-bit prescalers supporting:

- Timer mode

- PWM mode

- Capture/Compare mode

- Parallel host interface, 8/16-bit selectable for use as a communications coprocessor (IP2012 supports 8-bit only)

- External memory interface (IP2022 only)

- One 8-bit timer with programmable 8-bit prescaler

- One 8-bit real-time clock/counter with programmable

15-bit prescaler and 32 kHz crystal input

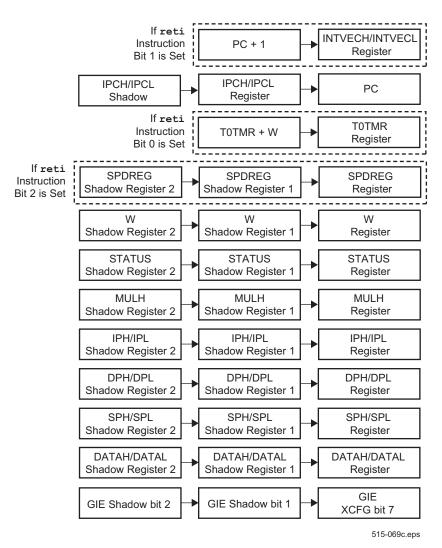

- Watchdog timer with prescaler

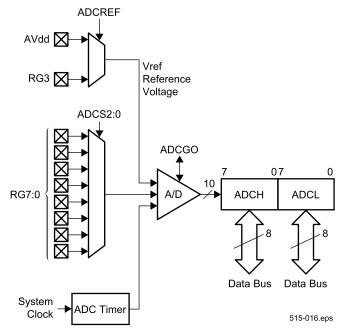

- 10-bit, 8-channel ADC with 1/2 LSB accuracy

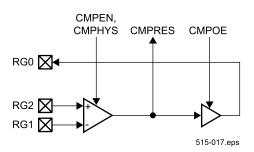

- Analog comparator with hysteresis enable/disable

- Brown-out minimum supply voltage detector

- External interrupt inputs on 8 pins (Port B)

#### Sophisticated Power and Frequency/Clock Management Support

- Operating voltage of 2.3V to 2.7V (120 MHz)

- Switching the system clock frequencies between different clock sources

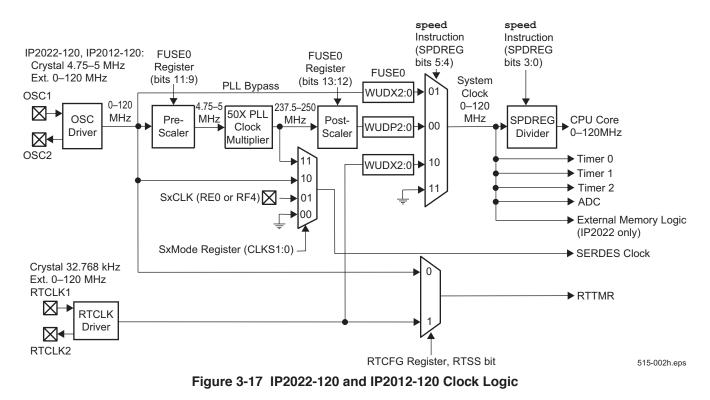

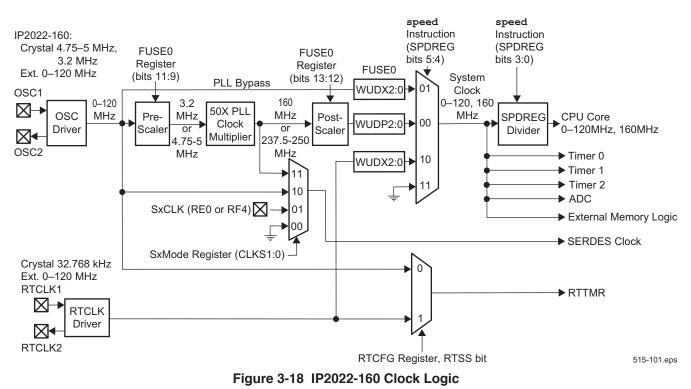

- On-chip PLL clock multiplier with pre- and post-divider

- 120 MHz on-chip clock from 4.8 MHz ext. crystal

- 160 MHz on-chip clock from 3.2 MHz ext. crystal

- Changing the core clock using a selectable divider

- Shutting down the PLL and/or the OSC input

- Dynamic CPU speed control with speed instruction

- Power-On-Reset (POR) logic

#### Flexible I/O

- 52 I/O Pins (48 on IP2012)

- 2.3V to 3.6V symmetric CMOS output drive (120MHz part)

- 5V-tolerant inputs

- Port A pins capable of sourcing/sinking 24 mA

- Optional I/O synchronization to CPU core clock

#### **Re-configurable Over The Internet**

- Customer application program updatable

Run-time self programming

- On-chip in-system programming interface

- On-chip in-system debugging support interface

- Debugging at full IP2022 operating speed

- Programming at device supply voltage level

- Real-time emulation, program debugging, and integrated software development environment offered by leading third-party tool vendors

# 1.2 Architecture

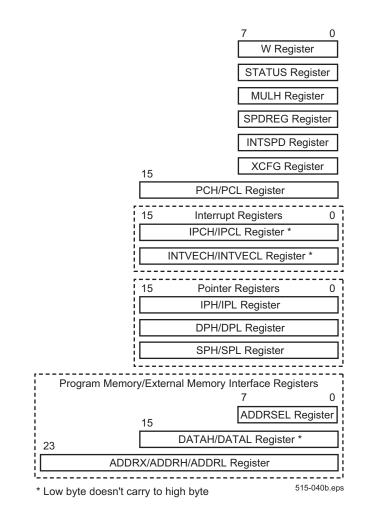

# 1.2.1 CPU

The IP2012 and IP2022 implement an enhanced Harvard architecture (i.e. separate instruction and data memories) with independent address and data buses. The 16-bit program memory and 8-bit dual-port data memory allow instruction fetch and data operations to occur in parallel. The advantage of this architecture is that instruction fetch and memory transfers can be overlapped by a multistage pipeline, so that the next instruction can be fetched from program memory while the current instruction is executed with data from the data memory.

Ubicom has developed a revolutionary RISC-based architecture that is deterministic, jitter free, and completely reprogrammable.

The architecture implements a four-stage pipeline (fetch, decode, execute, and write back). At the maximum operating frequency of 160 MHz, instructions are executed at the rate of one per 6.25 ns clock cycle.

#### 1.2.2 Serializer/Deserializers

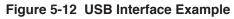

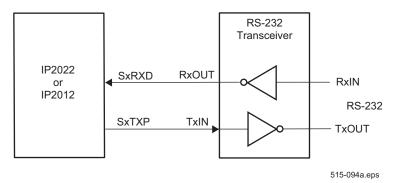

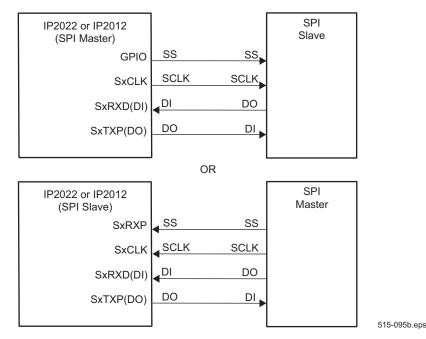

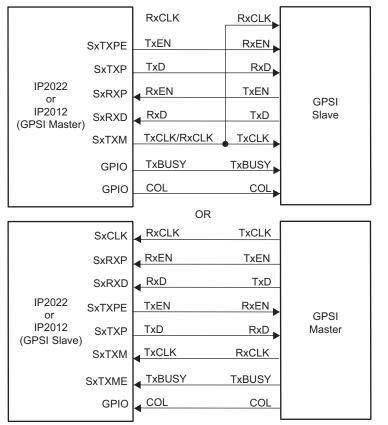

One of the key elements in optimizing the IP2012 and IP2022 for device-to-device and device-to-human communication is the inclusion of on-chip serializer/deserializer units. Each unit supports popular communication protocols such as GPSI, SPI, UART, USB, and 10Base-T Ethernet, allowing the IP2000 series devices to be used in bridge, access point and gateway applications.

By performing data serialization and deserialization in hardware, the CPU bandwidth needed to support serial communications is greatly reduced, especially at high baud rates. Providing two units (IP2022 only) allows easy implementation of protocol conversion or bridging functions between two fast serial devices, such as USBto-Ethernet, GPSI to ethernet, or Ethernet to Ethernet. A single SerDes unit (IP2012) provides the ability to bridge RS232, SPI, or WLAN (802.11b) to Ethernet.

# 1.2.3 Low-Power Support

Particular attention has been paid to minimizing power consumption. For example, an on-chip PLL allows use of a lower-frequency external source (e.g., an inexpensive 4.8MHz crystal can be used to produce a 120 MHz onchip clock; a 3.2 MHz crystal to produce a 160 MHz onchip clock), which reduces both power consumption and EMI. In addition, software can change the execution speed of the CPU to reduce power consumption, and a mechanism is provided for automatically changing the speed on entry and return from an interrupt service routine. The speed instruction specifies power-saving modes that include a clock divisor between 1 and 128. This divisor only affects the clock to the CPU core, not the timers. The **speed** instruction also specifies the clock source (OSC1 clock, RTCLK oscillator, or PLL clock multiplier), and whether to disable the OSC1 clock oscillator or the PLL. The speed instruction executes using the current clock divisor.

#### 1.2.4 Memory

The IP2012 / IP2022 CPU executes from a  $32K \propto 16$  flash memory. In addition, the ability to write into the program flash memory allows flexible non-volatile data storage. An interface is available (IP2022 only) for up to 128K bytes of linearly addressed external memory, which can be expanded to 2M bytes with additional software-based I/O addressing. At 120 MHz operation, the maximum execution rate is 40 MIPS from flash memory and 120 MIPS from RAM. At 160 MHz operation, the maximum execution rate is 53.33 MIPS from flash memory and 160 MIPS from RAM. Speed-critical routines can be copied from the flash memory to the RAM for faster execution. The IP2000 series devices have a mechanism for insystem programming of their flash and RAM program memories through a four-wire SPI interface, and software has the ability to reprogram the program memories at run time. This allows the functionality of a device to be changed in the field over the Internet.

#### 1.2.5 Instruction Set

The IP2000 series instruction set, using 16-bit words, implements a rich set of arithmetic and logical operations, including signed and unsigned 8-bit  $\infty$  8-bit integer multiply with a 16-bit product.

# 1.2.6 Other Supported Functions

On-chip dedicated hardware also includes a PLL, an 8channel 10-bit ADC, general-purpose timers, single-cycle multiplier, analog comparator, LFSR units, external memory interface (IP2022 only), parallel slave port, brown-out power voltage detector, watchdog timer, lowpower support, multi-source wakeup capability, userselectable clock modes, high-current outputs, and 52 general-purpose I/O pins (48 on IP2012).

# 1.2.7 Programming and Debugging Support

The IP2000 series has advanced in-system programming and debug support on-chip. This unobtrusive capability is provided through the ISP/ISD interface. There is no need for a bond-out chip for software development. This eliminates concerns about differences in electrical characteristics between a bond-out chip and the actual chip used in the target application. Designers can test and revise code on the same part used in the actual application.

Ubicom provides the complete Red Hat GNUPro tools, including C compiler, assembler, linker, utilities and GNU debugger. In addition, Ubicom offers an integrated graphical development environment which includes an editor, project manager, graphical user interface for the GNU debugger, device programmer, and ipModule<sup>™</sup> configuration tool.

# 2.0 Pin Definitions

Figure 2-1 IP2022 PQFP Pin Definition (Top View)

# 2.2 PQFP (Plastic Quad Flat Package) for IP2012

Figure 2-2 IP2012 PQFP Pin Definition (Top View)

# 2.3 µBGA (Micro Ball Grid Array Package) IP2022-120 Only

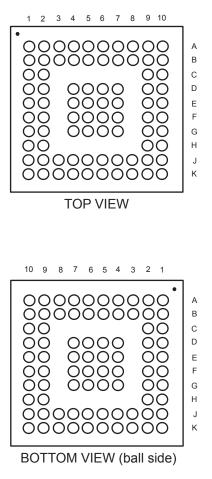

IP2022/BG80-120

515-092b.eps

Refer to Section 2.4 for signal names. Figure 2-3  $\mu$ BGA Pin Definition

#### 2.4 Signal Descriptions – IP2022

I = Digital Input, AI = Analog Input, O/DO = Digital Output, HiZ = High Impedance, P = Power, PLP = On-Chip Pullup, ST = Schmitt Trigger

| []     |                   |                  |              |                |                  |                                                                                                           |  |  |

|--------|-------------------|------------------|--------------|----------------|------------------|-----------------------------------------------------------------------------------------------------------|--|--|

| Name   |                   | in               | Туре         | Sink<br>@ 3.3V | Source<br>@ 3.3V | Function                                                                                                  |  |  |

|        | PQFP              | μBGA             | - 76*        | IOVDD          | IOVDD            |                                                                                                           |  |  |

| AVDD   | 70                | B6               | Р            |                |                  | Analog Supply                                                                                             |  |  |

| AVSS   | 71                | A6               | Р            |                |                  | Analog Ground                                                                                             |  |  |

| DVDD   | 9, 31,<br>56, 72  | D1,D6,<br>E9,G5  | Р            |                |                  | Logic Supply                                                                                              |  |  |

| DVSS   | 10, 32,<br>55, 73 | E1,K5,<br>E10,D5 | Р            |                |                  | Logic Ground                                                                                              |  |  |

| GVDD   | 65                | A8               | Р            |                |                  | I/O Port G supply                                                                                         |  |  |

| IOVDD  | 12, 34,<br>53     | E5,G6,<br>E6     | Р            |                |                  | I/O Supply (except Port G)                                                                                |  |  |

| IOVSS  | 11, 33,<br>54     | E2,K6,<br>E7     | Р            |                |                  | I/O Ground (all ports)                                                                                    |  |  |

| XVDD   | 76                | A4               | Р            |                |                  | PLL Supply                                                                                                |  |  |

| XVSS   | 77                | D4               | Р            |                |                  | PLL Ground                                                                                                |  |  |

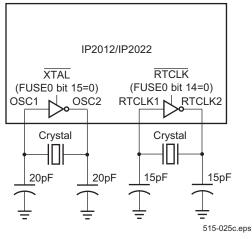

| OSC1   | 78                | B4               | I/ST         |                |                  | Clock/Crystal Input                                                                                       |  |  |

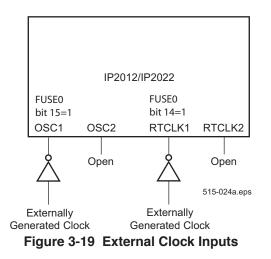

| OSC2   | 79                | A3               | O/HiZ        |                |                  | Crystal Output (tri-state if FUSE0 bit 15 = 1)                                                            |  |  |

| RST    | 80                | A2               | I/ST/<br>PLP |                |                  | Reset Input. There is a weak pull-up on this pin, but floating this pin does not guarantee Vih.           |  |  |

| RTCLK1 | 74                | A5               | I            |                |                  | Real-Time Clock/Crystal Input                                                                             |  |  |

| RTCLK2 | 75                | B5               | O/HiZ        |                |                  | Real-Time Crystal Output (tri-state if FUSE0 bit 14 = 1)                                                  |  |  |

| TSS    | 1                 | A1               | I/ST/<br>PLP |                |                  | Target SPI Slave Select (used only for in-system pro-<br>gramming and debug)                              |  |  |

| TSCK   | 2                 | C2               | I/ST/<br>PLP |                |                  | Target SPI Clock (used only for in-system program-<br>ming and debug)                                     |  |  |

| TSI    | 3                 | B1               | I/ST<br>/PLP |                |                  | Target SPI Serial Data Input (used only for in-system programming and debug)                              |  |  |

| TSO    | 4                 | B2               | O/HiZ        |                |                  | Target SPI Serial Data output (used only for in-sys-<br>tem programming and debug; high Z unless TSS low) |  |  |

| RA0    | 5                 | D2               | I/O          | 24 mA          | 24 mA            | I/O Port, High Power Output, Timer 1 Capture 1 Input                                                      |  |  |

| RA1    | 6                 | C1               | I/O          | 24 mA          | 24 mA            | I/O Port, High Power Output, Timer 1 Capture 2 Input                                                      |  |  |

| RA2    | 7                 | B3               | I/O          | 24 mA          | 24 mA            | I/O Port, High Power Output, Timer 1 Clock Input                                                          |  |  |

| RA3    | 8                 | E4               | I/O          | 24 mA          | 24 mA            | I/O Port, High Power Output, Timer 1 Output                                                               |  |  |

| RB0    | 13                | F5               | I/O          | 8 mA           | 8 mA             | I/O Port, External Interrupt, Timer 2 Capture 1 Input                                                     |  |  |

| RB1    | 14                | F1               | I/O          | 8 mA           | 8 mA             | I/O Port, External Interrupt, Timer 2 Capture 2 Input                                                     |  |  |

| RB2    | 15                | F2               | I/O          | 8 mA           | 8 mA             | I/O Port, External Interrupt, Timer 2 Clock Input                                                         |  |  |

#### Table 2-1 Signal Descriptions

| Table 2-1 Signal Descriptions (continued) |           |            |      |                         |                           |                                                                                             |  |  |

|-------------------------------------------|-----------|------------|------|-------------------------|---------------------------|---------------------------------------------------------------------------------------------|--|--|

| Name                                      | P<br>PQFP | in<br>μBGA | Туре | Sink<br>@ 3.3V<br>IOVDD | Source<br>@ 3.3V<br>IOVDD | Function                                                                                    |  |  |

| RB3                                       | 16        | G1         | I/O  | 8 mA                    | 8 mA                      | I/O Port, External Interrupt, Timer 2 Output                                                |  |  |

| RB4                                       | 17        | F4         | I/O  | 8 mA                    | 8 mA                      | I/O Port, External Interrupt, External Memory WR                                            |  |  |

| RB5                                       | 18        | J3         | I/O  | 8 mA                    | 8 mA                      | I/O Port, External Interrupt, Parallel Slave Peripheral<br>HOLD, External Memory RD         |  |  |

| RB6                                       | 19        | G2         | I/O  | 8 mA                    | 8 mA                      | I/O Port, External Interrupt, Parallel Slave Peripheral R/W, External Memory LE             |  |  |

| RB7                                       | 20        | H1         | I/O  | 8 mA                    | 8 mA                      | I/O Port, External Interrupt, Parallel Slave Peripheral CS, External Memory A0              |  |  |

| RC0                                       | 21        | J2         | I/O  | 4 mA                    | 4 mA                      | I/O Port, Parallel Slave Peripheral Data D8, External Memory A9                             |  |  |

| RC1                                       | 22        | H2         | I/O  | 4 mA                    | 4 mA                      | I/O Port, Parallel Slave Peripheral Data D9, External Memory A10                            |  |  |

| RC2                                       | 23        | J1         | I/O  | 4 mA                    | 4 mA                      | I/O Port, Parallel Slave Peripheral Data D10, External Memory A11                           |  |  |

| RC3                                       | 24        | K1         | I/O  | 4 mA                    | 4 mA                      | I/O Port, Parallel Slave Peripheral Data D11, External Memory A12                           |  |  |

| RC4                                       | 25        | K2         | I/O  | 4 mA                    | 4 mA                      | I/O Port, Parallel Slave Peripheral Data D12, External Memory A13                           |  |  |

| RC5                                       | 26        | K3         | I/O  | 4 mA                    | 4 mA                      | I/O Port, Parallel Slave Peripheral Data D13, External Memory A14                           |  |  |

| RC6                                       | 27        | J4         | I/O  | 4 mA                    | 4 mA                      | I/O Port, Parallel Slave Peripheral Data D14, External<br>Memory A15                        |  |  |

| RC7                                       | 28        | K4         | I/O  | 4 mA                    | 4 mA                      | I/O Port, Parallel Slave Peripheral Data D15, External Memory A16                           |  |  |

| RD0                                       | 29        | G4         | I/O  | 4 mA                    | 4 mA                      | I/O Port, Parallel Slave Peripheral Data D0, External Memory shared A1/D0                   |  |  |

| RD1                                       | 30        | J5         | I/O  | 4 mA                    | 4 mA                      | I/O Port, Parallel Slave Peripheral Data D1, External Memory shared A2/D1                   |  |  |

| RD2                                       | 35        | J6         | I/O  | 4 mA                    | 4 mA                      | I/O Port, Parallel Slave Peripheral Data D2, External Memory shared A3/D2                   |  |  |

| RD3                                       | 36        | G7         | I/O  | 4 mA                    | 4 mA                      | I/O Port, Parallel Slave Peripheral Data D3, External Memory shared A4/D3                   |  |  |

| RD4                                       | 37        | K7         | I/O  | 4 mA                    | 4 mA                      | I/O Port, Parallel Slave Peripheral Data D4, External Memory shared A5/D4                   |  |  |

| RD5                                       | 38        | J7         | I/O  | 4 mA                    | 4 mA                      | I/O Port, Parallel Slave Peripheral Data D5, External Memory shared A6/D5                   |  |  |

| RD6                                       | 39        | K8         | I/O  | 4 mA                    | 4 mA                      | I/O Port, Parallel Slave Peripheral Data D6, External Memory shared A7/D6                   |  |  |

| RD7                                       | 40        | K9         | I/O  | 4 mA                    | 4 mA                      | I/O Port, Parallel Slave Peripheral Data D7, External Memory shared A8/D7                   |  |  |

| RE0                                       | 41        | K10        | I/O  | 8 mA                    | 8 mA                      | I/O Port, S1CLK - SCLK (SPI), RxCLK (GPSI),<br>optional SERDES clock input for UART or USB. |  |  |

Table 2-1

Signal Descriptions (continued)

| Table 2-1 | Signal | Descriptions | (continued) |  |

|-----------|--------|--------------|-------------|--|

|-----------|--------|--------------|-------------|--|

|      | Pin  |      |       | Sink            | Source          |                                                                                                                                 |

|------|------|------|-------|-----------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------|

| Name | PQFP | μBGA | Туре  | @ 3.3V<br>IOVDD | @ 3.3V<br>IOVDD | Function                                                                                                                        |

| RE1  | 42   | H9   | I/O   | 8 mA            | 8 mA            | I/O Port, S1RXP - VP (USB), SS (SPI Slave), TxEN<br>(GPSI Master), RxEN (GPSI Slave)                                            |

| RE2  | 43   | J10  | I/O   | 8 mA            | 8 mA            | I/O Port, S1RXM - VM (USB)                                                                                                      |

| RE3  | 44   | J9   | I/O   | 8 mA            | 8 mA            | I/O Port, S1RXD - RCV (USB), RXD (UART), DI<br>(SPI), TxD (GPSI Master), RxD (GPSI Slave)                                       |

| RE4  | 45   | H10  | I/O   | 8 mA            | 8 mA            | I/O Port, S1TXPE/S1OE - TxD+ (Ethernet), OE<br>(USB), RxEN (GPSI Master), TxEN (GPSI Slave)                                     |

| RE5  | 46   | G9   | I/O   | 24 mA           | 24 mA           | I/O Port, High Power Output, S1TXP - Tx+ (Ethernet),<br>VPO (USB), TXD (UART), DO (SPI), RxD (GPSI<br>Master), TxD (GPSI Slave) |

| RE6  | 47   | G10  | I/O   | 24 mA           | 24 mA           | I/O Port, High Power Output, S1TXM - Tx- (Ethernet),<br>VMO (USB), TxCLK/RxCLK (GPSI Master), TxCLK<br>(GPSI Slave)             |

| RE7  | 48   | J8   | I/O   | 8 mA            | 8 mA            | I/O Port, S1TXME - TxD- (Ethernet), TxBUSY (GPSI)                                                                               |

| RF0  | 49   | F7   | I/O   | 8 mA            | 8 mA            | I/O Port, S2TXPE/S2OE - TxD+ (Ethernet), OE<br>(USB), RxEN (GPSI Master), TxEN (GPSI Slave)                                     |

| RF1  | 50   | F9   | I/O   | 24 mA           | 24 mA           | I/O Port, High Power Output, S2TXP - Tx+ (Ethernet),<br>VPO (USB), TXD (UART), DO (SPI), RxD (GPSI<br>Master), TxD (GPSI Slave) |

| RF2  | 51   | F10  | I/O   | 24 mA           | 24 mA           | I/O Port, High Power Output, S2TXM - Tx- (Ethernet),<br>VMO (USB), TxCLK/RxCLK (GPSI Master), TxCLK<br>(GPSI Slave)             |

| RF3  | 52   | F6   | I/O   | 8 mA            | 8 mA            | I/O Port, S2TXME - TxD- (Ethernet), TxBUSY (GPSI)                                                                               |

| RF4  | 57   | B9   | I/O   | 8 mA            | 8 mA            | I/O Port, S2CLK - SCLK (SPI), RxCLK (GPSI),<br>optional SERDES clock input for UART or USB.                                     |

| RF5  | 58   | A9   | I/O   | 8 mA            | 8 mA            | I/O Port, S2RXP - VP (USB), SS (SPI Slave), TxEN<br>(GPSI Master), RxEN (GPSI Slave)                                            |

| RF6  | 59   | D10  | I/O   | 8 mA            | 8 mA            | I/O Port, S2RXM - VM (USB)                                                                                                      |

| RF7  | 60   | D9   | I/O   | 8 mA            | 8 mA            | I/O Port, S2RXD - RCV (USB), RXD (UART), DI<br>(SPI), TxD (GPSI Master), RxD (GPSI Slave)                                       |

| RG0  | 61   | C10  | AI/DO | 4 mA*           | 4 mA*           | Output Port, ADC0 Input, Comparator Output                                                                                      |

| RG1  | 62   | C9   | AI/DO | 4 mA*           | 4 mA*           | Output Port, ADC1 Input, Comparator – Input                                                                                     |

| RG2  | 63   | B10  | AI/DO | 4 mA*           | 4 mA*           | Output Port, ADC2 Input, Comparator + Input                                                                                     |

| RG3  | 64   | A10  | AI/DO | 4 mA*           | 4 mA*           | Output Port, ADC3 Input, ADC reference Input                                                                                    |

| RG4  | 66   | B7   | AI/DO | 4 mA*           | 4 mA*           | Output Port, ADC4 Input, S1RX-                                                                                                  |

| RG5  | 67   | B8   | AI/DO | 4 mA*           | 4 mA*           | Output Port, ADC5 Input, S1RX+                                                                                                  |

| RG6  | 68   | A7   | AI/DO | 4 mA*           | 4 mA*           | Output Port, ADC6 Input, S2RX-                                                                                                  |

| RG7  | 69   | D7   | AI/DO | 4 mA*           | 4 mA*           | Output Port, ADC7 Input, S2RX+                                                                                                  |

\* GVDD = 2.5V

# 2.5 Signal Descriptions – IP2012

I = Digital Input, AI = Analog Input, O/DO = Digital Output, HiZ = High Impedance, P = Power, PLP = On-Chip Pullup, ST = Schmitt Trigger

|        | Pin               |                  | _            | Sink            | Source          |                                                                                                      |  |

|--------|-------------------|------------------|--------------|-----------------|-----------------|------------------------------------------------------------------------------------------------------|--|

| Name   | PQFP              | μBGA             | Туре         | @ 3.3V<br>IOVDD | @ 3.3V<br>IOVDD | Function                                                                                             |  |

| AVDD   | 70                | B6               | Р            |                 |                 | Analog Supply                                                                                        |  |

| AVSS   | 71                | A6               | Р            |                 |                 | Analog Ground                                                                                        |  |

| DVDD   | 9, 31,<br>56, 72  | D1,D6,<br>E9,G5  | Р            |                 |                 | Logic Supply                                                                                         |  |

| DVSS   | 10, 32,<br>55, 73 | E1,K5,<br>E10,D5 | Р            |                 |                 | Logic Ground                                                                                         |  |

| GVDD   | 65                | A8               | Р            |                 |                 | I/O Port G supply                                                                                    |  |

| IOVDD  | 12, 34,<br>53     | E5,G6,<br>E6     | Р            |                 |                 | I/O Supply (except Port G)                                                                           |  |

| IOVSS  | 11, 33,<br>54     | E2,K6,<br>E7     | Р            |                 |                 | I/O Ground (all ports)                                                                               |  |

| XVDD   | 76                | A4               | Р            |                 |                 | PLL Supply                                                                                           |  |

| XVSS   | 77                | D4               | Р            |                 |                 | PLL Ground                                                                                           |  |

| OSC1   | 78                | B4               | I/ST         |                 |                 | Clock/Crystal Input                                                                                  |  |

| OSC2   | 79                | A3               | O/HiZ        |                 |                 | Crystal Output (tri-state if FUSE0 bit 15 = 1)                                                       |  |

| RST    | 80                | A2               | I/ST/<br>PLP |                 |                 | Reset Input. There is a weak pull-up on this pin, but floating this pin does not guarantee Vih.      |  |

| RTCLK1 | 74                | A5               | I            |                 |                 | Real-Time Clock/Crystal Input                                                                        |  |

| RTCLK2 | 75                | B5               | O/HiZ        |                 |                 | Real-Time Crystal Output (tri-state if FUSE0 bit 14 = 1)                                             |  |

| TSS    | 1                 | A1               | I/ST/<br>PLP |                 |                 | Target SPI Slave Select (used only for in-system pro-<br>gramming and debug)                         |  |

| TSCK   | 2                 | C2               | I/ST/<br>PLP |                 |                 | Target SPI Clock (used only for in-system program-<br>ming and debug)                                |  |

| TSI    | 3                 | B1               | I/ST<br>/PLP |                 |                 | Target SPI Serial Data Input (used only for in-system programming and debug)                         |  |

| TSO    | 4                 | B2               | O/HiZ        |                 |                 | Target SPI Serial Data output (used only for in-system programming and debug; high Z unless TSS low) |  |

| RA0    | 5                 | D2               | I/O          | 24 mA           | 24 mA           | I/O Port, High Power Output, Timer 1 Capture 1 Input                                                 |  |

| RA1    | 6                 | C1               | I/O          | 24 mA           | 24 mA           | I/O Port, High Power Output, Timer 1 Capture 2 Input                                                 |  |

| RA2    | 7                 | B3               | I/O          | 24 mA           | 24 mA           | I/O Port, High Power Output, Timer 1 Clock Input                                                     |  |

| RA3    | 8                 | E4               | I/O          | 24 mA           | 24 mA           | I/O Port, High Power Output, Timer 1 Output                                                          |  |

| RB0    | 13                | F5               | I/O          | 8 mA            | 8 mA            | I/O Port, External Interrupt, Timer 2 Capture 1 Input                                                |  |

| RB1    | 14                | F1               | I/O          | 8 mA            | 8 mA            | I/O Port, External Interrupt, Timer 2 Capture 2 Input                                                |  |

| RB2    | 15                | F2               | I/O          | 8 mA            | 8 mA            | I/O Port, External Interrupt, Timer 2 Clock Input                                                    |  |

#### Table 2-2 Signal Descriptions

| Table 2-2 | Signal  | Descri | otions | (continued) | ) |

|-----------|---------|--------|--------|-------------|---|

|           | orginar | Deseri |        | (continucu) | / |

|      | P    | Pin Sink Source |      |                 |                 |                                                                                                                                 |  |  |

|------|------|-----------------|------|-----------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------|--|--|

| Name | PQFP | μBGA            | Туре | @ 3.3V<br>IOVDD | @ 3.3V<br>IOVDD | Function                                                                                                                        |  |  |

| RB3  | 16   | G1              | I/O  | 8 mA            | 8 mA            | I/O Port, External Interrupt, Timer 2 Output                                                                                    |  |  |

| RB4  | 17   | F4              | I/O  | 8 mA            | 8 mA            | I/O Port, External Interrupt                                                                                                    |  |  |

| RB5  | 18   | J3              | I/O  | 8 mA            | 8 mA            | I/O Port, External Interrupt, Parallel Slave Peripheral HOLD                                                                    |  |  |

| RB6  | 19   | G2              | I/O  | 8 mA            | 8 mA            | I/O Port, External Interrupt, Parallel Slave Peripheral R/W                                                                     |  |  |

| RB7  | 20   | H1              | I/O  | 8 mA            | 8 mA            | $I/O$ Port, External Interrupt, Parallel Slave Peripheral $\overline{CS}$                                                       |  |  |

| RC0  | 21   | J2              | I/O  | 4 mA            | 4 mA            | I/O Port, Parallel Slave Peripheral Data D8                                                                                     |  |  |

| RC1  | 22   | H2              | I/O  | 4 mA            | 4 mA            | I/O Port, Parallel Slave Peripheral Data D9                                                                                     |  |  |

| RC2  | 23   | J1              | I/O  | 4 mA            | 4 mA            | I/O Port, Parallel Slave Peripheral Data D10                                                                                    |  |  |

| RC3  | 24   | K1              | I/O  | 4 mA            | 4 mA            | I/O Port, Parallel Slave Peripheral Data D11                                                                                    |  |  |

| RC4  | 25   | K2              | I/O  | 4 mA            | 4 mA            | I/O Port, Parallel Slave Peripheral Data D12                                                                                    |  |  |

| RC5  | 26   | K3              | I/O  | 4 mA            | 4 mA            | I/O Port, Parallel Slave Peripheral Data D13                                                                                    |  |  |

| RC6  | 27   | J4              | I/O  | 4 mA            | 4 mA            | I/O Port, Parallel Slave Peripheral Data D14                                                                                    |  |  |

| RC7  | 28   | K4              | I/O  | 4 mA            | 4 mA            | I/O Port, Parallel Slave Peripheral Data D15                                                                                    |  |  |

| RD2  | 35   | J6              | I/O  | 4 mA            | 4 mA            | I/O Port                                                                                                                        |  |  |

| RD3  | 36   | G7              | I/O  | 4 mA            | 4 mA            | I/O Port                                                                                                                        |  |  |

| RD4  | 37   | K7              | I/O  | 4 mA            | 4 mA            | I/O Port                                                                                                                        |  |  |

| RD5  | 38   | J7              | I/O  | 4 mA            | 4 mA            | I/O Port                                                                                                                        |  |  |

| RD6  | 39   | K8              | I/O  | 4 mA            | 4 mA            | I/O Port                                                                                                                        |  |  |

| RD7  | 40   | K9              | I/O  | 4 mA            | 4 mA            | I/O Port                                                                                                                        |  |  |

| RE0  | 41   | K10             | I/O  | 8 mA            | 8 mA            | I/O Port, S1CLK - SCLK (SPI), RxCLK (GPSI),<br>optional SERDES clock input for UART or USB.                                     |  |  |

| RE1  | 42   | H9              | I/O  | 8 mA            | 8 mA            | I/O Port, S1RXP - VP (USB), SS (SPI Slave), TxEN<br>(GPSI Master), RxEN (GPSI Slave)                                            |  |  |

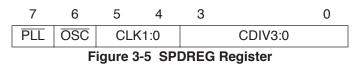

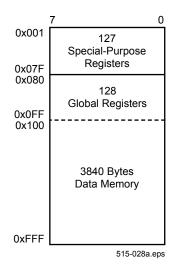

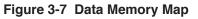

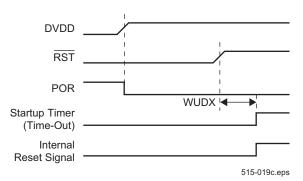

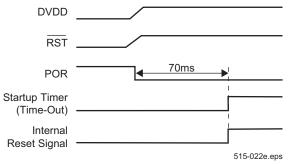

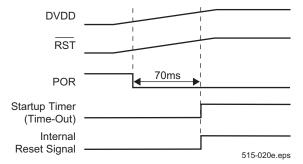

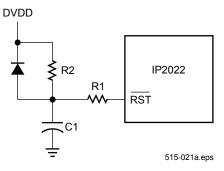

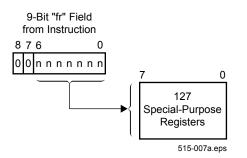

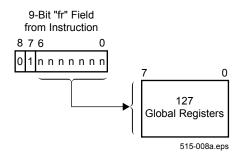

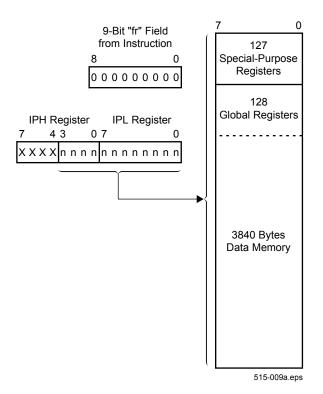

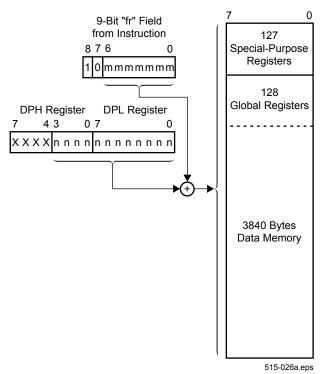

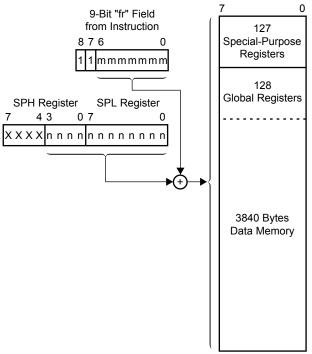

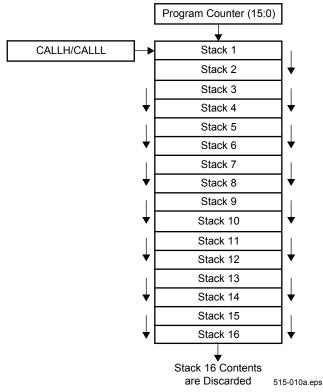

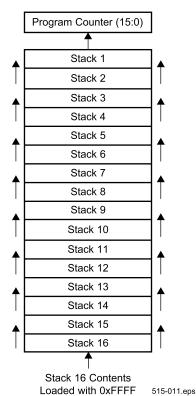

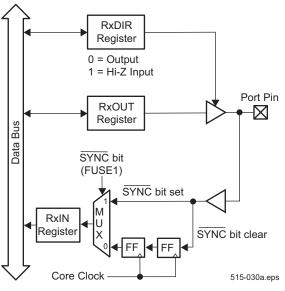

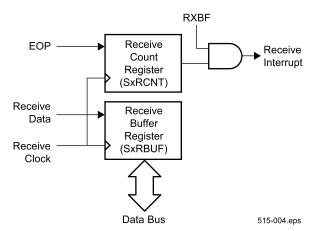

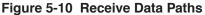

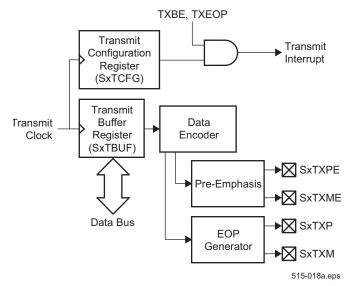

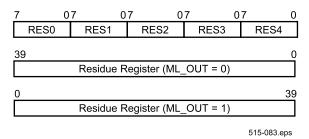

| RE2  | 43   | J10             | I/O  | 8 mA            | 8 mA            | I/O Port, S1RXM - VM (USB)                                                                                                      |  |  |