普誠科技股份有限公司 Princeton Technology Corp.

**Remote Control Receiver IC**

### PT2249A\_PT2250A

## DESCRIPTION

The PT2249A\_PT2250A Series are infra-red remote control receivers utilizing CMOS Technology. Remote Control System can be constructed together with the PT2248 remote control encoder. The PT2249A Series are packaged in 16 pins DIP (PT2249A version is also available in SOP package) and are capable of controlling 10 functions while the PT2250A Series are packaged in 24 pins DIP and are capable of controlling 18 functions. Several options, inverting/non-inverting IR signal input and/or dependent/independent cyclic (toggle) outputs, are provided to fit different application needs.

## **FEATURES**

- CMOS technology

- Low power consumption

- Very high noise immunity

- Able to output parallel multiple keying signals sent from the transmitter (PT2249A is able to output up to 5 functions simultaneously while PT2250A is able to output up to 6 functions simultaneously)

- Outputs for single pulse, hold pulse and cyclic pulse are provided

- A single terminal type oscillator by means of RC is provided

- Code detection circuit prevents interference from various types of machines and apparatus

- Digital filtering and code checking prevent interference from light sources such as PL lamp without sacrificing the receiving sensitivity

## **APPLICATIONS**

- Audio equipment remote control

- Television (TV) remote control

- Video Cassette Recorder (VCR) remote control

PT2249A\_PT2250A

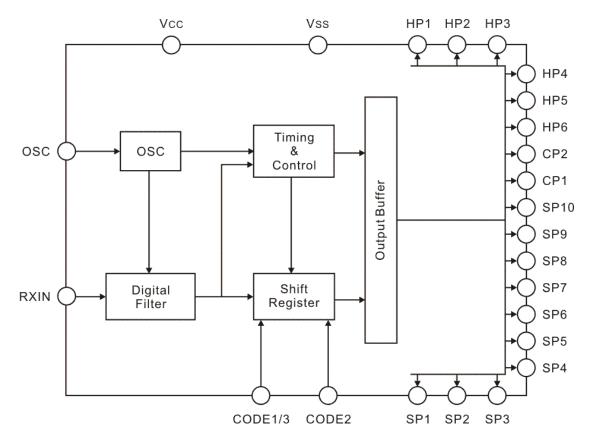

## **BLOCK DIAGRAM**

普誠科技股份有限公司

Princeton Technology Corp.

**Remote Control Receiver IC**

PT2249A\_PT2250A

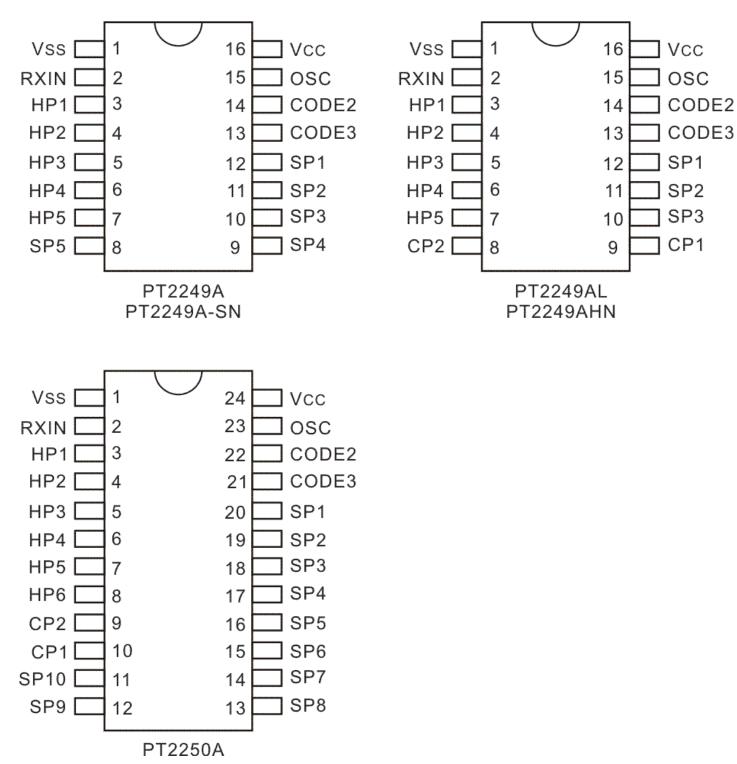

**PIN CONFIGURATIONS**

PT2249A\_PT2250A

## **PIN DESCRIPTION**

|            | Pin No.               |                       |         |     |                                                                                                                                                                                                   |  |

|------------|-----------------------|-----------------------|---------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin Name   | PT2249A<br>PT2249A-SN | PT2249AL<br>PT2249AHN | PT2250A | I/O | Description                                                                                                                                                                                       |  |

| Vss        | 1                     | 1                     | 1       | -   | Negative Power Supply                                                                                                                                                                             |  |

| RXIN       | 2                     | 2                     | 2       | I   | Receiver Input.<br>Instruction signal with carrier wave<br>eliminated should be inputted to<br>this pin. Input signal may be<br>optionally inverted before fed into<br>internal decoding circuit. |  |

| HP1 ~ HP5  | 3 ~ 7                 | 3 ~ 7                 | 3 ~ 7   | 0   | Hold Pulse.                                                                                                                                                                                       |  |

| HP6        | -                     | -                     | 8       | 0   | As long as proper signal is<br>received, this output is held at "H"<br>level. (approximately 160ms will<br>be "0" after key is released.)                                                         |  |

| CP1        | -                     | 9                     | 10      | 0   | Cyclic Pulse.                                                                                                                                                                                     |  |

| CP2        | -                     | 8                     | 9       | 0   | When receiving signal is inputted,<br>CP1/CP2 is inversed. CP1 output<br>may be optionally governed by<br>(dependent to) the output state of<br>CP2. See Functional Description<br>for details.   |  |

| SP1 ~ SP3  | 12 ~ 10               | 12 ~ 10               | 20 ~ 18 | 0   | Single Pulse.                                                                                                                                                                                     |  |

| SP4        | 9                     | -                     | 17      | 0   | When the receiving signal is                                                                                                                                                                      |  |

| SP5        | 8                     | -                     | 16      | 0   | inputted, the active output will be                                                                                                                                                               |  |

| SP6 ~ SP10 | -                     | -                     | 15 ~ 11 | 0   | at "H" level only for a fixed<br>duration of time (approximately<br>107 msec), then it will return to "L"<br>level.                                                                               |  |

| CODE1      | -                     | -                     | 22      | I   | Tx/Rx Matching Code.                                                                                                                                                                              |  |

| CODE2      | 14                    | 14                    | 21      | I   | Transmitter Code is compared                                                                                                                                                                      |  |

| CODE3      | 13                    | 13                    | -       | I   | with a code set at this terminals and if matched, input is accepted.                                                                                                                              |  |

| OSC        | 15                    | 15                    | 23      | I/O | OSC Input/Output.<br>A resistor and a capacitor are in<br>parallel connection between this<br>terminal and Vss.                                                                                   |  |

| Vcc        | 16                    | 16                    | 24      | -   | Positive Power Supply                                                                                                                                                                             |  |

### PT2249A\_PT2250A

# **FUNCTIONAL DESCRIPTION**

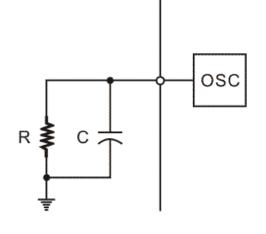

### **OSCILLATION CIRCUIT**

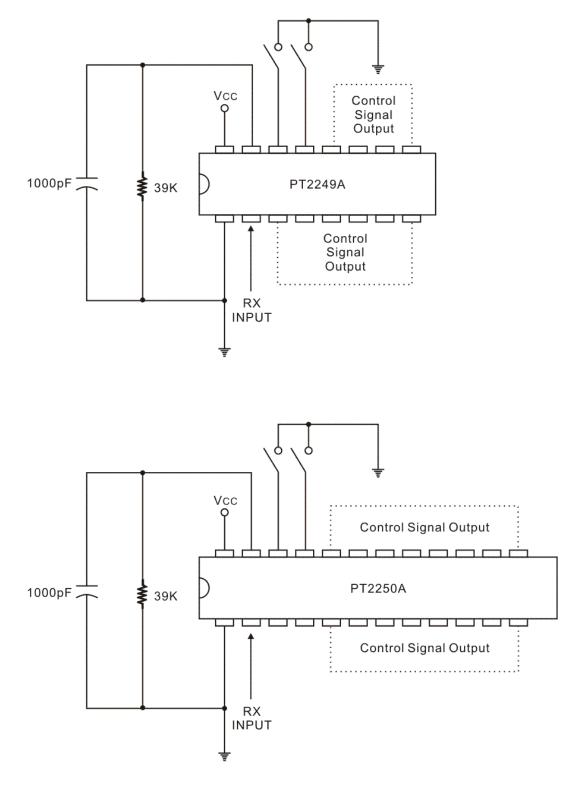

Timing with transmitter signal and internal operating clock are all decided by this oscillator. Using CMOS Technology, the oscillator of PT2248 transmitter is constructed through a combination of a linear amplifier by connecting C and R between the oscillator terminal and Vss.

Notes: 1. R=39K±5% 2. C=100pF±5%

## **RECEIVING SIGNAL INPUT CIRCUIT**

The signal is received by IR receiver module and the wave is infused into the IC.

The RXIN has a built-in Schmitt trigger circuit for shaping received signal waveform to eliminate rounding. PTC has made available various options to suit IR receiving module with positive or negative output. PT2249A Series / PT2250A Series with "N" Option was specially designed for IR modules with negative output. PT2249A Series / PT2250A Series without the "N" Option were specially designed for IR receiving modules with positive output. In these two options, IR signals without external inversion can be fed into the RXIN directly.

PT2249A\_PT2250A

### **RECEIVING SIGNAL CHECK**

The receiving signal check is used to check 2 cycle transmitting signals sent from the transmitter to determine if it is a normal signal.

|           | 12 BITS                             | 12 BITS                             |

|-----------|-------------------------------------|-------------------------------------|

| Receiving | C1 C2 C3 T1 T2 T3 K1 K2 K3 K4 K5 K6 | C1 C2 C3 T1 T2 T3 K1 K2 K3 K4 K5 K6 |

| Signal    | First Data                          | Secondt Data                        |

First, the data is stored in the 12-bit shift register. Then, when the second data is pushed into the shift register, the data is forced out of the shift register by one bit where the first data has been stored. The "pushed out" data and the incoming data are checked to see if they match. If there is an error in the receiving signal of the 12-bit data check, the system is reset at that point. Conversely, when all receiving data are checked OK, (HP1 ~ HP6 signals) outputs are raised from "L" level to "H" level.

### CODE COMPARISON

To prevent interference with other models: C1, C2, and C3 code bits are provided to check whether the transmitter and receiver codes match.

It is only when both codes match that the internal latch strobe pulse is generated to latch the receiving data. The output is then raised from "L" level to "H" level. If both codes do not match, no latch strobe pulse is generated and the output remains at "L" level (HPs and SPs) or unchanged (CPs).

The Code Bits used differ depending on the receiver. Please refer below.

| Rx PT2248 Code Pin | PT2249A | PT2250A |

|--------------------|---------|---------|

| T1 (C1 Code)       | Diode   | C1      |

| T2 (C2 Code)       | C2      | C2      |

| T3 (C3 Code)       | C3      | Diode   |

Note: where C1, C2, C3 will be "1" if one diode is connected between CODE and Tn pins; n=1 to 3 in PT2248; otherwise will be set to "0".

PT2249A\_PT2250A

## CODING

CODE1, CODE2 and CODE3 are internally pulled up to Vcc by pull-up resistors.

To encode each code bit to "1":

Open the corresponding CODE pin, or Insert a capacitor between CODE pin and Vss.

To encode each Code bit to "0": Connect the corresponding CODE pin to Vss.

## EXPLANATION OF OUTPUT TYPES: SP, HP AND CP

| SINGLE PULSE (SP1~SP10)          | r       |             |

|----------------------------------|---------|-------------|

| PT2248-Key On                    |         |             |

| PT2249A/PT2250A RXIN             | 12 BITS | 12 BITS     |

| Latch Strobe Pulse               |         |             |

| Single Shot Output<br>(SP1~SP10) |         | About 107ms |

If there is no error in the receiving signal of the 12-bit data check, it will generate a single pulse output.

PT2249A PT2250A

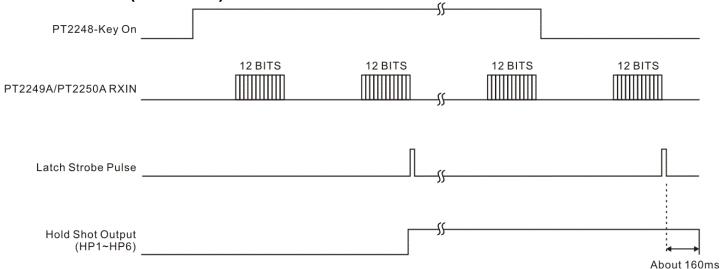

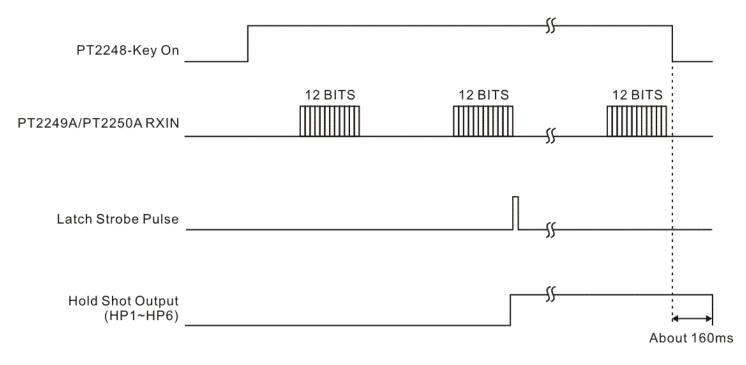

### HOLD PULSE (HP1~HP6)

Normally, after two matched code words (12-bit per word) transmitted from PT2248 is detected, the latch strobe is generated, thereby producing a latch strobe pulse. This causes an "H" state output and this output is sustained at "H" level as long as the continuous signal received. Approximately 160ms after the key is released and the continuous signal is stopped, the output is reversed to "L" level by above the last latch strobe pulse. Please refer to the diagram

普誠科技股份有限公司 Princeton Technology Corp.

#### Remote Control Receiver IC

### PT2249A\_PT2250A

Under abnormal conditions where intolerable interference of any kind would cause the receiver to receive only one matched code word during the last transmission (please refer to the diagram above), then approximately 160ms after the key is released and the hold shot output (continuous signal) is stopped, the output is reversed to "L" level.

Under any condition, the HP1 ~ HP6 are able to drive simultaneously a maximum of six outputs at "H" Level by the continuous signals sent from the transmitter. These functions are most applicable for REC-PLAY, REC-PAUSE and CUE/REVIEW of the Tape Deck.

普誠科技股份有限公司 Princeton Technology Corp.

#### **Remote Control Receiver IC**

### PT2249A\_PT2250A

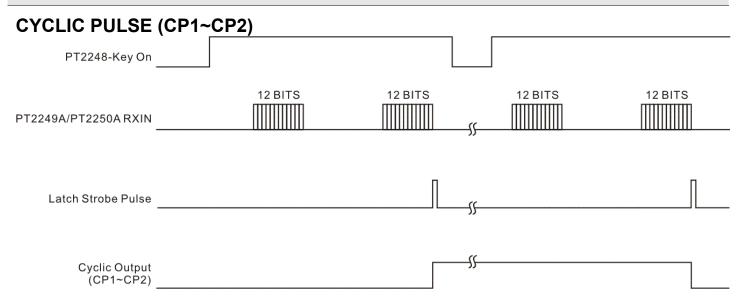

When signal is received, the cyclic pulse output is reversed. This cyclic pulse is used for Power ON/OFF, MUTE, etc.

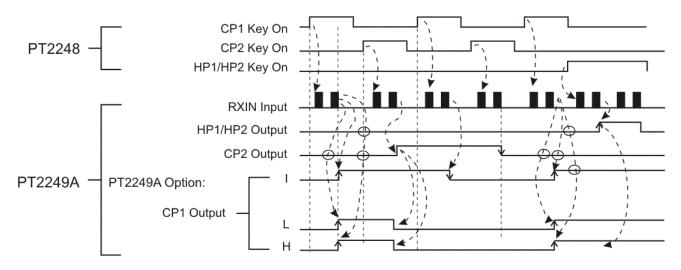

The relationship between CP1 and CP2 (in the PT2249A Series) is shown in the diagram below:

PT2249AL:

- CP1 may not be set to "H" level when CP2 is in "H" Level.

- CP1 is reset to "L" level whenever CP2 is set to "H" level.

#### PT2249AHN:

- CP1 may not be set to "H" Level when CP2 or HP1 or HP2 is in "H" Level.

- CP1 is reset to "L" Level whenever CP2 or HP1 or HP2 is set to "H" Level.

### PT2249A\_PT2250A

### **CODE ALLOCATION\***

### \* NOTE: KEY NO. IS OF PT2248

|         |    |    | F  | PT224     | 48 Da | ata Bi | t  |    |    | Function of Instruction  |      |  |

|---------|----|----|----|-----------|-------|--------|----|----|----|--------------------------|------|--|

| Key No. | Н  | S1 | S2 | D1        | D2    | D3     | D4 | D5 | D6 |                          |      |  |

|         | T1 | T2 | Т3 | <b>K1</b> | K2    | K3     | K4 | K5 | K6 | (PT2249A or PT2250A O/P) |      |  |

| 1       | 1  | 0  | 0  | 1         | 0     | 0      | 0  | 0  | 0  | Continuous Signal        | HP1  |  |

| 2       | 1  | 0  | 0  | 0         | 1     | 0      | 0  | 0  | 0  | Continuous Signal        | HP2  |  |

| 3       | 1  | 0  | 0  | 0         | 0     | 1      | 0  | 0  | 0  | Continuous Signal        | HP3  |  |

| 4       | 1  | 0  | 0  | 0         | 0     | 0      | 1  | 0  | 0  | Continuous Signal        | HP4  |  |

| 5       | 1  | 0  | 0  | 0         | 0     | 0      | 0  | 1  | 0  | Continuous Signal        | HP5  |  |

| 6       | 1  | 0  | 0  | 0         | 0     | 0      | 0  | 0  | 1  | Continuous Signal        | HP6  |  |

| 7       | 0  | 1  | 0  | 1         | 0     | 0      | 0  | 0  | 0  | Single-Shot Signal       | SP1  |  |

| 8       | 0  | 1  | 0  | 0         | 1     | 0      | 0  | 0  | 0  | Single-Shot Signal       | SP2  |  |

| 9       | 0  | 1  | 0  | 0         | 0     | 1      | 0  | 0  | 0  | Single-Shot Signal       | SP3  |  |

| 10      | 0  | 1  | 0  | 0         | 0     | 0      | 1  | 0  | 0  | Single-Shot Signal       | SP4  |  |

| 11      | 0  | 1  | 0  | 0         | 0     | 0      | 0  | 1  | 0  | Single-Shot Signal       | SP5  |  |

| 12      | 0  | 1  | 0  | 0         | 0     | 0      | 0  | 0  | 1  | Single-Shot Signal       | SP6  |  |

| 13      | 0  | 0  | 1  | 1         | 0     | 0      | 0  | 0  | 0  | Single-Shot Signal       | SP7  |  |

| 14      | 0  | 0  | 1  | 0         | 1     | 0      | 0  | 0  | 0  | Single-Shot Signal       | SP8  |  |

| 15      | 0  | 0  | 1  | 0         | 0     | 1      | 0  | 0  | 0  | Single-Shot Signal       | SP9  |  |

| 16      | 0  | 0  | 1  | 0         | 0     | 0      | 1  | 0  | 0  | Single-Shot Signal       | SP10 |  |

| 17      | 0  | 0  | 1  | 0         | 0     | 0      | 0  | 1  | 0  | Cyclic Signal            | CP1  |  |

| 18      | 0  | 0  | 1  | 0         | 0     | 0      | 0  | 0  | 1  | Cyclic Signal            | CP2  |  |

C1 ~ C3 Code Bits are available in addition to the above data bits for optional Code Selection.

PT2250A can use all keys.

PT2249A are able to use Key No. 1 ~ 5 and Key No. 7 ~ 11.

PT2249A/AL/AHN can use Key No. 1 ~ 5, Key No. 7 ~ 9, and Key No. 17 ~ 18.

PT2249A\_PT2250A

# **ABSOLUTE MAXIMUM RATING**

(Ta=25℃)

| Parameter             | Symbol          | Rating             | Unit |

|-----------------------|-----------------|--------------------|------|

| Supply voltage        | V <sub>CC</sub> | 5.5                | V    |

| Input/Output voltage  | V <sub>IN</sub> | Vss-0.5 to Vcc+0.5 | V    |

| Power dissipation     | Pd              | 200                | mW   |

| Operating temperature | Topr            | -40 ~ +85          | °C   |

| Storage temperature   | Tstg            | -65 ~ +150         | °C   |

Note: Exceeding the maximum rating may cause permanent damage to devices.

## **ELECTRICAL CHARACTERISTICS**

(Unless otherwise specified,  $V_{CC}$ =5V and Ta=25 °C)

| Pa          | rameter                               | Symbol           | Conditions                 | Min. | Тур. | Max. | Unit |

|-------------|---------------------------------------|------------------|----------------------------|------|------|------|------|

| Operating   | supply voltage                        | Vcc              | All Function<br>Operations | 2.3  | -    | 5.0  | V    |

| Operating   | supply current                        | lcc              | Key on without Load        | -    | -    | 1.0  | mA   |

| Oscillation | frequency                             | fosc             | Vcc=5 V                    | 25   | 34   | 41   | KHz  |

| Output      | "H" level                             | I <sub>OH</sub>  | Vo=4V                      | -1.0 | -    | -    | mA   |

| Current     | "L" level                             | I <sub>OL</sub>  | Vo=1 V                     | 1.0  | -    | -    | mA   |

| Pull-up res | istor                                 | Rup              |                            | 150  | 300  | 450  | KΩ   |

|             | Input current                         | I <sub>IH</sub>  | V <sub>I</sub> =5V         | -1.0 | -    | 1.0  | μA   |

| RXIN        | Input circuit<br>threshold<br>voltage | VI               |                            | 2.0  | 2.5  | 3.0  | V    |

|             | Input<br>hysterestic<br>voltage       | V <sub>HIS</sub> |                            | -    | 0.6  | -    | V    |

| Stand-by    | PT2249/50A                            |                  | RXIN=0V                    | -    | -    | 200  |      |

| current     | PT2249AL                              | I <sub>SB</sub>  | OSC=5V                     | -    | -    | 300  | μA   |

| current     | PT2249AHN                             |                  | (All Outputs floating)     | -    | -    | 300  |      |

PT2249A\_PT2250A

# **APPLICATION CIRCUIT**

PT2249A\_PT2250A

### **APPLICATION NOTE:**

- 1. Combination of PT2248/PT2249A Series Code Bits

- a) PT2249A Series Code Bit C1 is internally pulled high and thereby set at a default value of "1". Thus, PT2248 Code Bit C1 must be set at "1".

- b) PT2249A Series Code Bits C2 and C3 may be programmed as follows:

- 1) "0", "0" (This combination is not available with TC9149.)

- 2) "0", "1"

- 3) "1", "0"

- 4) "1", "1"

- c) To set Code Bit to "1" on PT2248, diodes must be connected to Code Terminal from the T1 ~ T3 terminals.

- d) To set Code Bit to "0" on PT2248, the terminals must be kept floating, except C1 add one diode.

|    | PT224 | 8  | PT2249A | Series |

|----|-------|----|---------|--------|

| C1 | C2    | C3 | C2      | C3     |

| 1  | 0     | 0  | 0       | 0      |

| 1  | 0     | 1  | 0       | 1      |

| 1  | 1     | 0  | 1       | 0      |

| 1  | 1     | 1  | 1       | 1      |

e) The Code Bits Combinations of PT2248 and PT2249A Series are shown below:

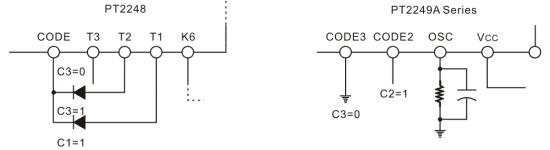

f) Example: (Refer to Example 1 diagram)

The following example shows the case when PT2248 Code Bits C1=1, C2=1, and C3=0. The CODE2 Pin of the PT2249A Series is programmed in floating state and CODE3 pin is connected to Vss (C2=1, C3=0.) In this way, the PT2249A Series can match the C2, C3 Code Bits of PT2248 and correctly decode the remote commands.

Example 1 Circuit Diagram when Code Bit C2 = 1 and C3 = 0

普誠科技股份有限公司 Princeton Technology Corp.

#### Remote Control Receiver IC

PT2249A\_PT2250A

- 2. Combination of PT2248/PT2250A Series Code Bits

- a) PT2250A Series Code Bit C3 is internally pulled high and thereby set at a default value of "1". Thus, PT2248 Code Bit C3 must be set at "1".

- b) PT2250A Series Code Bits C2 and C3 may be programmed as follows:

- 1) "0", "0" (This combination is not available with TC9150.)

- 2) "0", "1"

- 3) "1", "0"

- 4) "1", "1"

- c) To set Code Bit to "1" on PT2248, diodes must be connected to Code Terminal from the T1 ~ T3 terminals.

- d) To set Code Bit to "0" on PT2248, the terminals must be kept floating.

- e) The Code Bits Combinations of PT2248 and PT2250A Series are shown below:

|    | PT2248 | 3  | PT2250/ | A Series |

|----|--------|----|---------|----------|

| C1 | C2     | C3 | C1      | C2       |

| 0  | 0      | 1  | 0       | 0        |

| 0  | 1      | 1  | 0       | 1        |

| 1  | 0      | 1  | 1       | 0        |

| 1  | 1      | 1  | 1       | 1        |

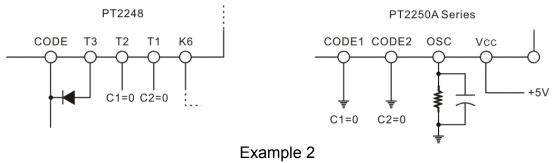

f) Example: (Refer to Example 2 diagram)

The following example shows the case when PT2248 Code Bits C1=0, C2=0, and C3=1. The CODE1 and CODE2 pins of the PT2250A Series are connected to the  $V_{SS}$  (C1=0 and C2=0). In this way, the PT2250A or any of its series matches the C1 and C2 Code Bits of PT2248; thus, the remote commands are correctly decoded.

Circuit Diagram when Code Bit C1=0 and C2=0

#### PT2249A\_PT2250A

## **ORDER INFORMATION**

| Valid Part Number | Package Type         | Top Code   |

|-------------------|----------------------|------------|

| PT2249A           | 16 Pins, DIP, 300mil | PT2249A    |

| PT2249AHN         | 16 Pins, DIP, 300mil | PT2249AHN  |

| PT2249AL          | 16 Pins, DIP, 300mil | PT2249AL   |

| PT2249A-SN        | 16 Pins, SOP, 150mil | PT2249A-SN |

| PT2250A           | 24 Pins, DIP, 600mil | PT2250A    |

Functions:

1. A – Advanced Version

2. N – Inversed RXIN Input

3. L – Advanced Dependent Cyclic (Toggle) Outputs

4. H – Output Format same as "L", except that when HP1 or HP2 is active, it will clear CP1.

PT2249A\_PT2250A

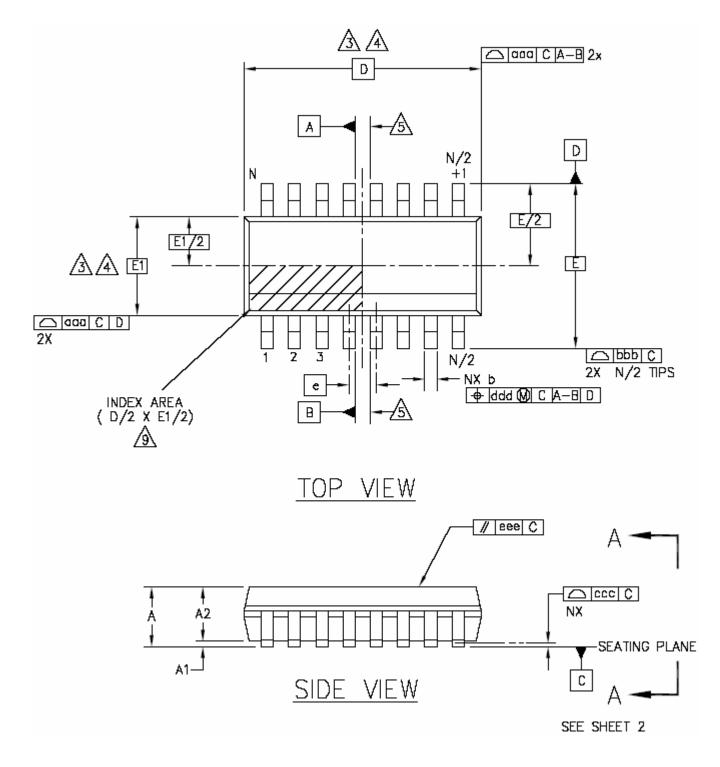

# PACKAGE INFORMATION

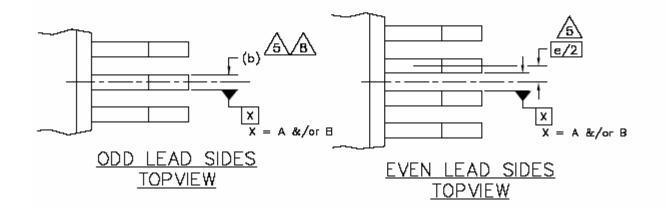

### 16 PINS, SOP, 150 MIL

#### PT2249A\_PT2250A

SEE VIEW C

### PT2249A\_PT2250A

| Symbol | Min. | Тур.      | Max. |

|--------|------|-----------|------|

| A      | 1.35 | -         | 1.75 |

| A1     | 0.10 | -         | 0.25 |

| A2     | 1.25 | -         | 1.65 |

| b      | 0.31 | -         | 0.51 |

| b1     | 0.28 | -         | 0.48 |

| С      | 0.17 | -         | 0.25 |

| c1     | 0.17 | -         | 0.23 |

| D      |      | 9.90 BSC. |      |

| E      |      | 6.00 BSC. |      |

| E1     |      | 3.90 BSC. |      |

| е      |      | 1.27 BSC. |      |

| L      | 0.40 | -         | 1.27 |

| L1     |      | 1.04 REF. |      |

| L2     |      | 0.25 BSC. |      |

| R      | 0.07 | -         | -    |

| R1     | 0.07 |           | -    |

| h      | 0.25 | -         | 0.50 |

| θ      | 0°   | -         | 8°   |

| θ1     | 5°   | -         | 15°  |

| θ2     | 0°   | -         | -    |

Notes:

- 1. Dimensioning and tolerancing per ANSI Y 14.5M-1994

- 2. Controlling Dimension: MILLIMETERS.

- Dimension D does not include mold flash protrusions or gate burrs. Mold flash, protrusions or gate burrs shall not exceed 0.15 mm (0.006 in) per end. Dimension E1 does not include interlead flash or protrusion. Interlead flash or protrusion shall not exceed 0.25mm per side. D and E1 dimensions are determined at datum H.

- 4. The package top may be smaller than the package bottom. Dimensions D and E1 are determined at the outermost extremes of the plastic body exclusive of mold flash, tie bar burrs, gate burrs and interlead flash, but including any mismatch between the top and bottom of the plastic body.

- 5. Datums A & B to be determined at datum H.

- 6. N is the number of terminal positions. (N=16)

- 7. The dimensions apply to the flat section of the lead between 0.10 to 0.25mm from the lead tip.

- 8. Dimension "b" does not include dambar protrusion. Allowable dambar protrusion shall be 0.10mm total in excess of the "b" dimension at maximum material condition. The dambar cannot be located on the lower radius of the foot.

- 9. This chamfer feature is optional. If it is not present, then a pin 1 identifier must be located within the index area indicated.

- 10. Refer to JEDEC MS-012, Variation AC.

- JEDEC is the registered trademark of JEDEC SOLID STATE TECHNOLOGY ASSOCIATION

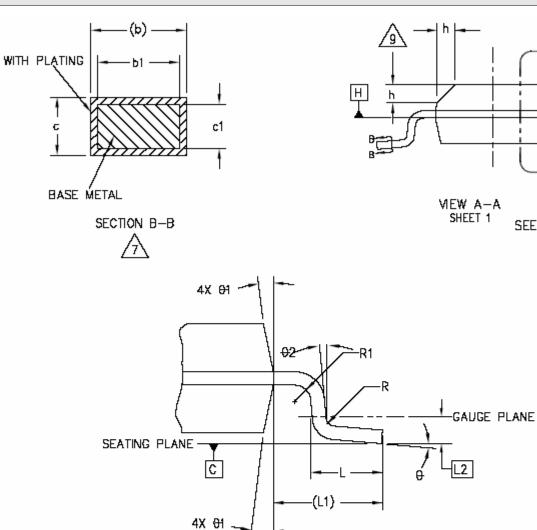

PT2249A\_PT2250A

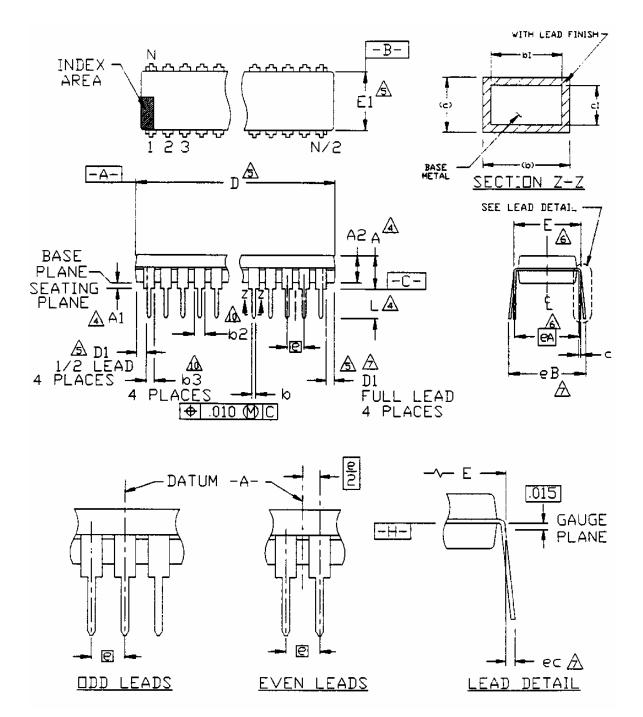

### 16 PINS, DIP, 300 MIL

CTC

### Remote Control Receiver IC

### PT2249A\_PT2250A

| Symbol | Min.  | Nom.      | Max.  |

|--------|-------|-----------|-------|

| A      | -     | -         | 0.210 |

| A1     | 0.015 | -         | -     |

| A2     | 0.115 | 0.130     | 0.195 |

| b      | 0.014 | 0.018     | 0.022 |

| b1     | 0.014 | 0.018     | 0.020 |

| b2     | 0.045 | 0.060     | 0.070 |

| b3     | 0.030 | 0.039     | 0.045 |

| С      | 0.008 | 0.010     | 0.014 |

| c1     | 0.008 | 0.010     | 0.011 |

| D      | 0.780 | 0.790     | 0.800 |

| D1     | 0.005 | -         | -     |

| E      | 0.300 | 0.310     | 0.325 |

| E1     | 0.240 | 0.250     | 0.280 |

| е      |       | 0.100 bsc |       |

| eA     |       | 0.300 bsc |       |

| eB     | -     | -         | 0.430 |

| eC     | 0.000 | -         | 0.060 |

| L      | 0.115 | 0.130     | 0.150 |

Notes:

- 1. Controlling Dimension: INCHES.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- 3. Dimensions A, A1 and L are measured with the package seated in JEDEC Seating Plane Gauge GS-3.

- 4. D, D1 and E1 dimensions do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.010 inch.

- 5. E and eA measured with the leads constrained to be perpendicular to datum -C-.

- 6. eB and eA are measured at the lead tips with the leads unconstrained.

- 7. N is the maximum number of terminal positions (N=16).

- 8. Pointed or rounded lead tips are preferred to ease insertion.

- 9. b2 and b3 maximum dimensions do not include dambar protrusions. Dambar protrusions shall not exceed 0.010 (0.25mm).

- 10. Variation AB is a full lead package.

- 11. Distance between leads including dambar protrusions to be 0.005 in minimum.

- 12. Datum plane -H- coincident with the bottom of lead where lead exits body.

- 13. Refer to JEDEC MS-001 Variation AB.

JEDEC is the registered trademark of JEDEC SOLID STATE TECHNOLOGY ASSOCIATION.

PT2249A\_PT2250A

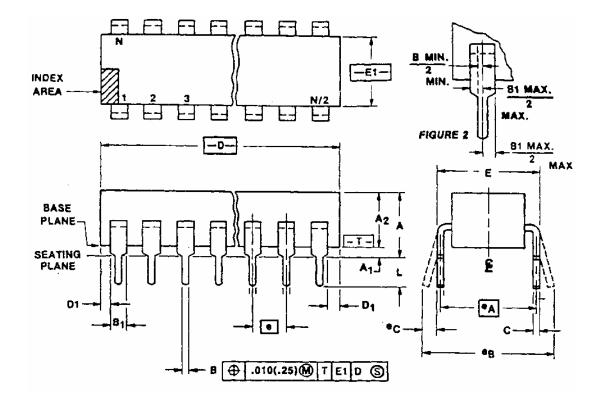

### 24 PINS, DIP, 600 MIL

| Symbol | Min.      | Max.  |

|--------|-----------|-------|

| A      | -         | 0.250 |

| A1     | 0.015     | -     |

| A2     | 0.125     | 0.195 |

| В      | 0.014     | 0.022 |

| B1     | 0.030     | 0.070 |

| С      | 0.008     | 0.015 |

| D      | 1.150     | 1.290 |

| D1     | 0.005     | -     |

| E      | 0.600     | 0.625 |

| E1     | 0.485     | 0.580 |

| e      | 0.100 bsc |       |

| eA     | 0.600 bsc |       |

| eB     | -         | 0.700 |

| Ĺ      | 0.115     | 0.200 |

### PT2249A\_PT2250A

#### Notes:

- 1. Controlling Dimensions: INCH

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- 3. Dimension A, A1 and L are measured with the package seated in JEDEC Seating Plane Gauge GS-3

- 4. D and E1 dimensions, for ceramic packages, include allowance for glass overrun and meniscus and lid to base mismatch.

- 5. D and E1 dimensions for plastic packages, do not include mold, flash to protrusions. Mold flash or protrusions shall not exceed 0.010 inch (0.25mm)

- 6. E and eA measured with the leads constrained to be perpendicular to plane T.

- 7. eB and eC are measured at the lead tips with the leads unconstrained. eC must be zero or greater.

- 8. N is the maximum number of terminal positions. (N=24).

- 9. Refer to JEDEC MS-011 Variation AA.

JEDEC is the registered trademark of JEDEC SOLID STATE TECHNOLOGY ASSOCIATION.