Document Number: MC33970

Rev. 3.0, 1/2007

# Dual Gauge Driver Integrated Circuit with Improved Damping Algorithms

This 33970 is a single-packaged, Serial Peripheral Interface (SPI) controlled, dual step motor gauge driver integrated circuit (IC). This monolithic IC consists of four dual output H-Bridge coil drivers and the associated control logic. Each pair of H-Bridge drivers is used to automatically control the speed, direction, and magnitude of current through the two coils of a two-phase instrumentation step motor, similar to an MMT-licensed AFIC 6405.

The 33970 is ideal for use in automotive instrumentation systems requiring distributed and flexible step motor gauge driving. The device also eases the transition to step motors from air core motors by emulating the air core pointer movement with little additional processor bandwidth utilization.

#### **Features**

- MMT-Licensed Two-Phase Step Motor Compatible

- Minimal Processor Overhead Required

- Fully Integrated Pointer Movement and Position State Machine with Air Core Movement Emulation

- 4096 Possible Steady State Pointer Positions

- 340° Maximum Pointer Sweep

- Fixed Maximum Acceleration and Deceleration of 4500°/s<sup>2</sup>

- Maximum Pointer Velocity of 400°/s

- · Analog Microstepping (12 Steps/Degree of Pointer Movement)

- · Pointer Calibration and Return to Zero

- SPI-Controlled 16-Bit Word

- Calibratable Internal Clock

- Low Sleep Mode Current

- Backward Compatible with MC33991

- Improved Pointer Movement, Diagnostics, and Return to Zero (RTZ)

- · Pb-Free Packaging Designated by Suffix Code EG

### 33970

### IMPROVED GAUGE DRIVER INTEGRATED CIRCUIT

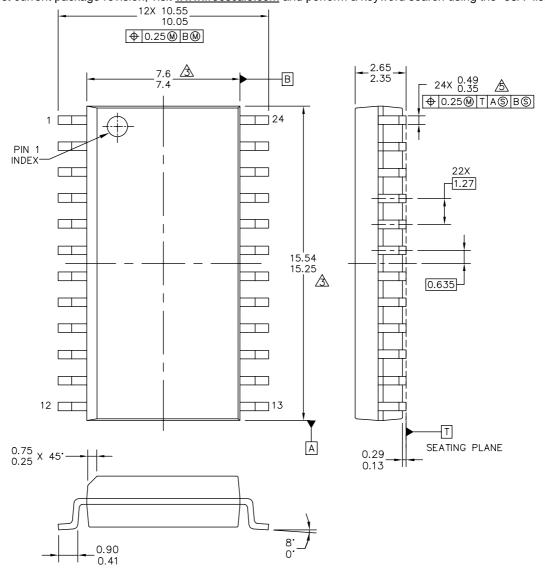

DW SUFFIX EG SUFFIX (Pb-FREE) 98ASB42344B 24-PIN SOICW

| ORDERING INFORMATION                               |                |           |  |  |  |  |  |  |  |

|----------------------------------------------------|----------------|-----------|--|--|--|--|--|--|--|

| Device Temperature Range (T <sub>A</sub> ) Package |                |           |  |  |  |  |  |  |  |

| MC33970DW/R2                                       | -40°C to 125°C | 24 SOICW  |  |  |  |  |  |  |  |

| MCZ33970EG/R2                                      | -40 C to 125 C | 24 301000 |  |  |  |  |  |  |  |

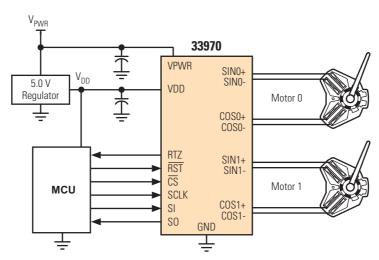

Figure 1. 33970 Simplified Application Diagram

<sup>\*</sup> This document contains certain information on a new product. Specifications and information herein are subject to change without notice.

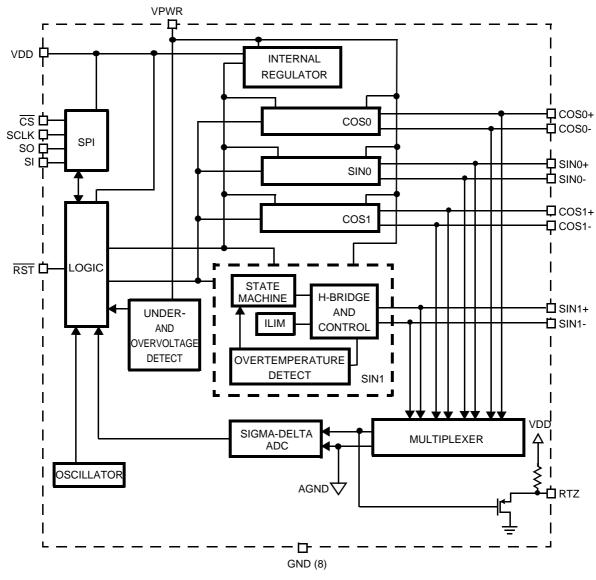

### INTERNAL BLOCK DIAGRAM

Figure 2. 33970 Simplified Internal Block Diagram

### **PIN CONNECTIONS**

| COS0+           | 1 ● | 24 | COS1+    |

|-----------------|-----|----|----------|

| COS0- I         | 2   | 23 | COS1-    |

| SIN0+ □□        | 3   | 22 | □□ SIN1+ |

| SIN0- □□        | 4   | 21 | □□ SIN1- |

| GND □□          | 5   | 20 | □□ GND   |

| GND □□          | 6   | 19 | □ GND    |

| GND □□          | 7   | 18 | □ GND    |

| GND □□          | 8   | 17 | □ GND    |

| <del>cs</del> □ | 9   | 16 | UPWR     |

| SCLK □□         | 10  | 15 | □□ RST   |

| so □□           | 11  | 14 | UDV U    |

| SI 🖂            | 12  | 13 | RTZ      |

|                 |     |    |          |

Figure 3. 33970 Pin Connections

Table 1. 33970 Pin Definitions

A functional description of each pin can be found in the Functional Pin Description section beginning on page 10.

| Pin Number           | Pin Name                         | Pin Function | Formal Name        | Definition                                                                                                                         |

|----------------------|----------------------------------|--------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>2<br>3<br>4     | COS0+<br>COS0-<br>SIN0+<br>SIN0- | Output       | H-Bridge Outputs 0 | Each pin is the output pin of a half bridge, designed to source or sink current.                                                   |

| 5–8,<br>17–20        | GND                              | Ground       | Ground             | These pins serve as the ground for the source of the low-side output transistors as well as the logic portion of the device.       |

| 9                    | CS                               | Input        | Chip Select        | This pin is connected to a chip select output of a LSI IC.                                                                         |

| 10                   | SCLK                             | Input        | Serial Clock       | This pin is connected to the SCLK pin of the master device and acts as a bit clock for the SPI port.                               |

| 11                   | SO                               | Output       | Serial Output      | This pin is connected to the SPI Serial Data Input pin of the master device, or to the SI pin of the next device in a daisy chain. |

| 12                   | SI                               | Input        | Serial Input       | This pin is connected to the SPI Serial Data Output pin of the master device from which it receives output command data.           |

| 13                   | RTZ                              | Output       | Multiplexed Output | This is a multiplexed output pin, for the non-driven coil, during a Return to Zero (RTZ) event.                                    |

| 14                   | VDD                              | Input        | Voltage            | This SPI and logic power supply input will work with 5.0 V supplies.                                                               |

| 15                   | RST                              | Input        | Reset              | This input has an internal active pull-up.                                                                                         |

| 16                   | VPWR                             | Input        | Battery Voltage    | Power supply.                                                                                                                      |

| 21<br>22<br>23<br>24 | SIN1-<br>SIN1+<br>COS1-<br>COS1+ | Output       | H-Bridge Outputs 1 | Each of these pins are the output pin of a half bridge, designed to source or sink current.                                        |

### **ELECTRICAL CHARACTERISTICS**

### **MAXIMUM RATINGS**

### **Table 2. Maximum Ratings**

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Ratings                                                | Symbol                | Value       | Unit |

|--------------------------------------------------------|-----------------------|-------------|------|

| ELECTRICAL RATINGS                                     | 1                     |             | 1    |

| Power Supply Voltage                                   | V <sub>PWR(SUS)</sub> |             | V    |

| Steady State                                           |                       | -0.3 to 41  |      |

| Input Pin Voltage (1)                                  | V <sub>IN</sub>       | -0.3 to 7.0 | V    |

| SIN+/- COS+/- Continuous Per Output Current (2)        | I <sub>OUTMAX</sub>   | 40          | mA   |

| ESD Voltage (3)                                        |                       |             | V    |

| Human Body Model                                       | V <sub>ESD1</sub>     | ±2000       |      |

| Machine Model                                          | V <sub>ESD2</sub>     | ±200        |      |

| THERMAL RATINGS                                        |                       |             | -    |

| Storage Temperature                                    | T <sub>STG</sub>      | -55 to 150  | °C   |

| Operating Junction Temperature                         | T <sub>J</sub>        | -40 to 150  | °C   |

| Thermal Resistance                                     |                       |             | °C/W |

| Junction to Ambient                                    | $R_{	heta JA}$        | 60          |      |

| Junction to Lead                                       | $R_{\theta JL}$       | 20          |      |

| THERMAL RESISTANCE                                     | ,                     |             | •    |

| Peak Package Reflow Temperature During Reflow (4), (5) | T <sub>PPRT</sub>     | Note 5      | °C   |

- 1. Exceeding voltage limits on Input pins may cause permanent damage to the device.

- 2. Output continuous output rating so long as maximum junction temperature is not exceeded. Operation at 125°C ambient temperature will require maximum output current computation using package thermal resistances.

- 3. ESD1 testing is performed in accordance with the Human Body Model ( $C_{ZAP}$  = 100 pF,  $R_{ZAP}$  = 1500  $\Omega$ ), ESD2 testing is performed in accordance with the Machine Model ( $C_{ZAP}$  = 200 pF,  $R_{ZAP}$  = 0  $\Omega$ ).

- 4. Pin soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.

- Freescale's Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For Peak Package Reflow Temperature and Moisture Sensitivity Levels (MSL),

Go to www.freescale.com, search by part number [e.g. remove prefixes/suffixes and enter the core ID to view all orderable parts. (i.e. MC33xxxD enter 33xxx), and review parametrics.

### STATIC ELECTRICAL CHARACTERISTICS

### **Table 3. Static Electrical Characteristics**

Characteristics noted under conditions  $4.75~\text{V} \le \text{V}_{DD} \le 5.25~\text{V}$ ,  $-40^{\circ}\text{C} \le \text{T}_{A} \le 125^{\circ}\text{C}$ , GND = 0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at  $\text{T}_{A} = 25^{\circ}\text{C}$  under nominal conditions unless otherwise noted.

| Characteristic                                                                                         | Symbol               | Min                   | Тур                   | Max                   | Unit |

|--------------------------------------------------------------------------------------------------------|----------------------|-----------------------|-----------------------|-----------------------|------|

| POWER INPUT                                                                                            |                      |                       | I.                    | l                     |      |

| Supply Voltage Range                                                                                   | V <sub>PWR</sub>     |                       |                       |                       | V    |

| Fully Operational                                                                                      |                      | 6.5                   | -                     | 26                    |      |

| Limited Operational <sup>(6)</sup> , <sup>(7)</sup>                                                    |                      | 4.0                   | -                     | 26                    |      |

| VPWR Supply Current                                                                                    | I <sub>PWR(ON)</sub> |                       |                       |                       | mA   |

| Gauge 1 and 2 Outputs ON, No Output Loads                                                              | , ,                  | _                     | 4.0                   | 6.0                   |      |

| VPWR Supply Current (All Outputs Disabled)                                                             |                      |                       |                       |                       | μА   |

| Reset = Logic [0], $V_{DD} = 5.0 \text{ V}$                                                            | I <sub>PWSLP1</sub>  | _                     | 42                    | 60                    |      |

| Reset = Logic [0], $V_{DD} = 0 V$                                                                      | I <sub>PWRSLP2</sub> | _                     | 15                    | 25                    |      |

| Overvoltage Detection Level <sup>(8)</sup>                                                             | V <sub>PWROV</sub>   | 26                    | 32                    | 38                    | V    |

| Undervoltage Detection Level (9)                                                                       | V <sub>PWRUV</sub>   | 5.0                   | 5.6                   | 6.2                   | V    |

| Logic Supply Voltage Range (5.0 V Nominal Supply)                                                      | $V_{DD}$             | 4.5                   | 5.0                   | 5.5                   | V    |

| Under VDD Logic Reset                                                                                  | V <sub>DDUV</sub>    | _                     | -                     | 4.5                   | V    |

| VDD Supply Current                                                                                     |                      |                       |                       |                       |      |

| Sleep: Reset Logic [0]                                                                                 | I <sub>DD(OFF)</sub> | _                     | 40                    | 65                    | μΑ   |

| Outputs Enabled                                                                                        | I <sub>DD(ON)</sub>  | _                     | 1.0                   | 1.8                   | mA   |

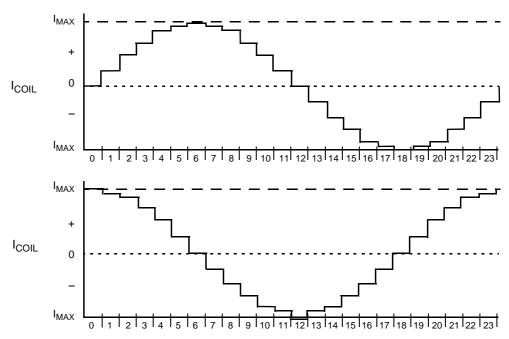

| POWER OUTPUTS                                                                                          | 1                    | •                     | •                     |                       |      |

| Microstep Output (Measured Across Coil Outputs) SIN0,1, ± (COS0,1, ±) (refer to <b>Table 1</b> )       |                      |                       |                       |                       | V    |

| $R_{OUT} = 200 \Omega$                                                                                 |                      |                       |                       |                       |      |

| Steps 6, 18 (0, 12)                                                                                    | V <sub>ST6</sub>     | 4.82                  | 5.3                   | 6.0                   |      |

| Steps 5, 7, 17, 19 (1, 11, 13, 23)                                                                     | V <sub>ST5</sub>     | 0.94 V <sub>ST6</sub> | 0.97 V <sub>ST6</sub> | 1.0 V <sub>ST6</sub>  |      |

| Steps 4, 8, 16, 20 (2, 10, 14, 22)                                                                     | V <sub>ST4</sub>     | 0.84 V <sub>ST6</sub> | 0.87 V <sub>ST6</sub> | 0.96 V <sub>ST6</sub> |      |

| Steps 3, 9, 15, 21 (3, 9, 15, 21)                                                                      | V <sub>ST3</sub>     | 0.68 V <sub>ST6</sub> | 0.71 V <sub>ST6</sub> | 0.8 V <sub>ST6</sub>  |      |

| Steps 2, 10, 14, 22 (4, 8,16, 20)                                                                      | V <sub>ST2</sub>     | 0.47 V <sub>ST6</sub> | 0.50 V <sub>ST6</sub> | 0.57 V <sub>ST6</sub> |      |

| Steps 1, 11, 13, 23 (5, 7, 17, 19)                                                                     | V <sub>ST1</sub>     | 0.23 V <sub>ST6</sub> | 0.26 V <sub>ST6</sub> | 0.31 V <sub>ST6</sub> |      |

| Steps 0, 12 (6, 18)                                                                                    | V <sub>ST0</sub>     | -0.1                  | 0.0                   | 0.1                   |      |

| Full Step Active Output (Measured Across Coil Outputs) SIN0, 1, ± (COS0, 1, ±) (see Figure 9, page 23) | V <sub>FS</sub>      |                       |                       |                       | V    |

| Steps 1, 3 (0, 2)                                                                                      |                      | 4.9                   | 5.3                   | 6.0                   |      |

| Microstep, Full Step Output (Measured from Coil Low Side to Ground)                                    | V <sub>LS</sub>      |                       |                       |                       | V    |

| SIN0, 1, $\pm$ (COS0, 1, $\pm$ ), $I_{OUT} = 30 \text{ mA}$                                            |                      | 0.0                   | 0.1                   | 0.3                   |      |

- 6. Outputs and logic remain active; however, the larger coil voltage levels may be clipped. The reduction in drive voltage may result in a loss of position control.

- 7. The logic will reset at some level below the specified Limited Operational minimum.

- 8. Outputs will disable and must be re-enabled via the PECCR command.

- 9. Outputs remain active; however, the reduction in drive voltage may result in a loss of position control.

### ELECTRICAL CHARACTERISTICS STATIC ELECTRICAL CHARACTERISTICS

### Table 3. Static Electrical Characteristics (continued)

Characteristics noted under conditions  $4.75~\text{V} \leq \text{V}_{DD} \leq 5.25~\text{V}$ ,  $-40^{\circ}\text{C} \leq \text{T}_{A} \leq 125^{\circ}\text{C}$ , GND = 0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at  $\text{T}_{A} = 25^{\circ}\text{C}$  under nominal conditions unless otherwise noted.

| Characteristic                                          | Symbol                | Min                 | Тур                    | Max                    | Unit      |

|---------------------------------------------------------|-----------------------|---------------------|------------------------|------------------------|-----------|

| POWER OUTPUTS (continued)                               | 1                     |                     |                        | l                      |           |

| Output Flyback Clamp (10)                               | $V_{FB}$              | _                   | V <sub>ST6</sub> + 0.5 | V <sub>ST6</sub> + 1.0 | V         |

| Output Current Limit (Output = VST6)                    | I <sub>LIM</sub>      | 40                  | 100                    | 170                    | mA        |

| Overtemperature Shutdown (10)                           | OT <sub>SD</sub>      | 155                 | -                      | 180                    | °C        |

| Overtemperature Hysteresis (10)                         | OT <sub>HYST</sub>    | 8.0                 | -                      | 16                     | °C        |

| CONTROL I/O                                             | •                     |                     |                        | •                      |           |

| Input Logic High Voltage (11)                           | V <sub>IH</sub>       | 2.0                 | _                      | _                      | V         |

| Input Logic Low Voltage (11)                            | V <sub>IL</sub>       | -                   | -                      | 0.8                    | V         |

| Input Logic Voltage Hysteresis (10)                     | V <sub>IN(HYST)</sub> | -                   | 100                    | -                      | mV        |

| Input Logic Pull Down Current (SI, SCLK)                | I <sub>DWN</sub>      | 3.0                 | -                      | 20                     | μА        |

| Input Logic Pull-Up Current (CS, RST)                   | I <sub>UP</sub>       | 5.0                 | -                      | 20                     | μА        |

| SO High-State Output Voltage (I <sub>OH</sub> = 1.0 mA) | V <sub>SOH</sub>      | 0.8 V <sub>DD</sub> | _                      | -                      | V         |

| SO Low-State Output Voltage (I <sub>OL</sub> = -1.6 mA) | V <sub>SOL</sub>      | -                   | 0.2                    | 0.4                    | V         |

| SO Tri-State Leakage Current (CS ≥ 3.5 V)               | I <sub>SOLK</sub>     | -5.0                | 0                      | 5.0                    | μА        |

| Input Capacitance (12)                                  | C <sub>IN</sub>       | _                   | 4.0                    | 12                     | pF        |

| SO Tri-State Capacitance (12)                           | C <sub>SO</sub>       | -                   | -                      | 20                     | pF        |

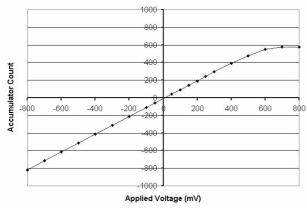

| ANALOG TO DIGITAL CONVERTER (RTZ ACCUMULATOR CO         | OUNT)                 | •                   | •                      |                        |           |

| ADC Gain <sup>(10)</sup> , <sup>(13)</sup>              | G <sub>ADC</sub>      | 100                 | 188                    | 270                    | Counts/V/ |

- 10. This parameter is guaranteed by design; however, it is not production tested.

- 11.  $V_{DD} = 5.0 \text{ V}.$

- 12. Capacitance not measured. This parameter is guaranteed by design; however, it is not production tested.

- 13. Reference Figure 8, RTZ Accumulator (Typical)

### **DYNAMIC ELECTRICAL CHARACTERISTICS**

### **Table 4. Dynamic Electrical Characteristics**

Characteristics noted under conditions  $4.75 \text{ V} \leq \text{V}_{DD} \leq 5.25 \text{ V}$ ,  $-40^{\circ}\text{C} \leq \text{T}_{A} \leq 125^{\circ}\text{C}$ , GND = 0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at  $\text{T}_{A} = 25^{\circ}\text{C}$  under nominal conditions unless otherwise noted.

| Characteristic                                                                                                                                | Symbol                | Min        | Тур        | Max        | Unit     |

|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------|------------|------------|----------|

| POWER OUTPUT AND CLOCK TIMINGS                                                                                                                |                       |            | l          | l          | I.       |

| SIN, COS Output Turn ON Delay Time (Time from Rising $\overline{\text{CS}}$ Enabling Outputs to Steady State Coil Voltages and Currents) (14) | t <sub>DLY(ON)</sub>  | _          | _          | 1.0        | ms       |

| SIN, COS Output Turn OFF Delay Time (Time from Rising CS Disables Outputs to Steady State Coil Voltages and Currents) (14)                    | t <sub>DLY(OFF)</sub> | _          | _          | 1.0        | ms       |

| Uncalibrated Oscillator Cycle Time                                                                                                            | t <sub>CLU</sub>      | 0.65       | 1.0        | 1.7        | μS       |

| Calibrated Oscillator Cycle Time  Cal Pulse = 8.0 μs, PECCR D4 = Logic [0]  Cal pulse = 8.0 μs, PECCR D4 = Logic [1]                          | t <sub>CLC</sub>      | 1.0<br>0.9 | 1.1<br>1.0 | 1.2<br>1.1 | μs       |

| Maximum Pointer Speed (15)                                                                                                                    | V <sub>MAX</sub>      | _          | _          | 400        | °/s      |

| Maximum Pointer Acceleration (15)                                                                                                             | A <sub>MAX</sub>      | _          | _          | 4500       | °/s²     |

| SPI INTERFACE TIMING (16)                                                                                                                     |                       |            | I          | I          | <u> </u> |

| Recommended Frequency of SPI Operation                                                                                                        | f <sub>SPI</sub>      | _          | 1.0        | 3.0        | MHz      |

| Falling Edge of CS to Rising Edge of SCLK (Required Setup Time) (17)                                                                          | t <sub>LEAD</sub>     | _          | 50         | 167        | ns       |

| Falling Edge of SCLK to Rising Edge of CS (Required Setup Time) (17)                                                                          | t <sub>LAG</sub>      | -          | 50         | 167        | ns       |

| SI to Falling Edge of SCLK (Required Setup Time) (17)                                                                                         | t <sub>SISU</sub>     | -          | 25         | 83         | ns       |

| Required High State Duration of SCLK (Required Setup Time) (17)                                                                               | twsclkh               | _          | -          | 167        | ns       |

| Required Low State Duration of SCLK (Required Setup Time) (17)                                                                                | twsclkl               | -          | -          | 167        | ns       |

| Falling Edge of SCLK to SI (Required Hold Time) (17)                                                                                          | t <sub>SI(HOLD)</sub> | -          | 25         | 83         | ns       |

| SO Rise Time $C_L = 200 \text{ pF}$                                                                                                           | t <sub>RSO</sub>      | -          | 25         | 50         | ns       |

| SO Fall Time $C_L = 200 \text{ pF}$                                                                                                           | t <sub>FSO</sub>      | -          | 25         | 50         | ns       |

| SI, CS, SCLK, Incoming Signal Rise Time (18)                                                                                                  | t <sub>RSI</sub>      | -          | -          | 50         | ns       |

| SI, CS, SCLK, Incoming Signal Fall Time (18)                                                                                                  | t <sub>FSI</sub>      | _          | -          | 50         | ns       |

| Falling Edge of RST to Rising Edge of RST (Required Setup Time) (17)                                                                          | twRST                 | -          | -          | 3.0        | μS       |

| Rising Edge of CS to Falling Edge of CS (Required Setup Time) (17), (19)                                                                      | tCS                   | _          | -          | 5.0        | μS       |

| Rising Edge of RST to Falling Edge of CS (Required Setup Time) (17)                                                                           | t <sub>EN</sub>       | _          | -          | 5.0        | μS       |

- 14. Maximum specified time for the 33970 is the minimum guaranteed time needed from the microcontroller.

- 15. The minimum and maximum value will vary proportionally to the internal clock tolerance. These numbers are based on an ideally calibrated clock frequency of 1.0 MHz. These are not 100 percent tested.

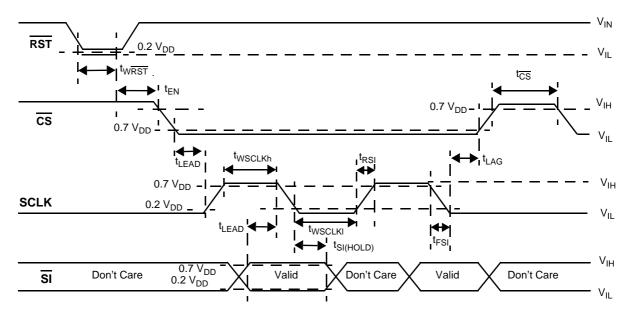

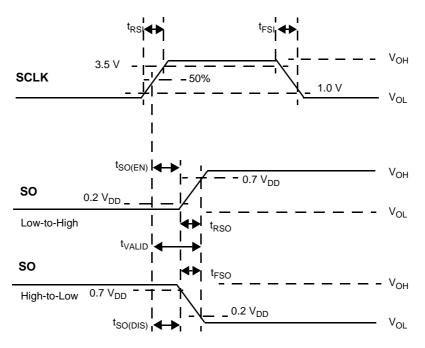

- 16. The device shall meet all SPI interface timing requirements specified in the SPI Interface Timing section of this table, over the temperature range specified. Digital interface timing is based on a symmetrical 50 percent duty cycle SCLK Clock Period of 333 ns. The device shall be fully functional for slower clock speeds. See Figure 4 and 5.

- 17. The maximum setup time specified for the 33970 is the minimum time needed from the microcontroller to guarantee correct operation.

- 18. Rise and Fall time of incoming SI,  $\overline{CS}$ , and SCLK signals suggested for design consideration to prevent the occurrence of double pulsing.

- 19. The value is for a 1.0 MHz calibrated internal clock. The value will change proportionally as the internal clock frequency changes

### ELECTRICAL CHARACTERISTICS DYNAMIC ELECTRICAL CHARACTERISTICS

### **Table 4. Dynamic Electrical Characteristics**

Characteristics noted under conditions  $4.75~\text{V} \leq \text{V}_{DD} \leq 5.25~\text{V}$ ,  $-40^{\circ}\text{C} \leq \text{T}_{A} \leq 125^{\circ}\text{C}$ , GND = 0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at  $\text{T}_{A} = 25^{\circ}\text{C}$  under nominal conditions unless otherwise noted.

| Characteristic                                                                  | Symbol               | Min | Тур | Max | Unit |

|---------------------------------------------------------------------------------|----------------------|-----|-----|-----|------|

| Time from Falling Edge of CS to SO Low Impedance (20)                           | t <sub>SO(EN)</sub>  | -   | _   | 145 | ns   |

| Time from Rising Edge of $\overline{\text{CS}}$ to SO High Impedance (21)       | t <sub>SO(DIS)</sub> | -   | 1.3 | 4.0 | μS   |

| Time from Rising Edge of SCLK to SO Data Valid (22)                             | t <sub>VALID</sub>   |     |     |     | ns   |

| $0.2 \text{ V}_{DD} \le \text{SO} \ge 0.8 \text{ V}_{DD}, C_L = 200 \text{ pF}$ |                      | -   | 65  | 105 |      |

- 20. Time required for output status data to be terminated at SO. 1.0 k $\Omega$  load on SO

- 21. Time required for output status data to be available for use at SO. 1.0 k $\Omega$  load on SO.

- 22. Time required to obtain valid data out from SO following the rise of SCLK.

### **TIMING DIAGRAMS**

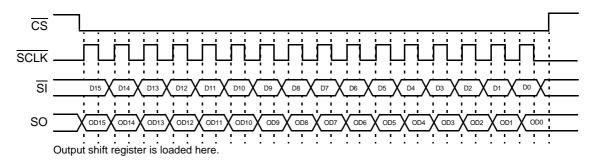

Figure 4. Input Timing Switching Characteristics

Figure 5. Valid Data Delay Time and Valid Time Waveforms

### **FUNCTIONAL DESCRIPTION**

#### INTRODUCTION

This 33970 is a single-packaged, Serial Peripheral Interface (SPI) controlled, dual step motor gauge driver integrated circuit (IC). This monolithic IC consists of four dual output H-Bridge coil drivers and the associated control logic. Each pair of H-Bridge drivers is used to automatically control the speed, direction, and magnitude of current through the two coils of a two-phase instrumentation step motor, similar to an MMT-licensed AFIC 6405.

The 33970 is ideal for use in automotive instrumentation systems requiring distributed and flexible step motor gauge driving. The device also eases the transition to step motors from air core motors by emulating the air core pointer movement with little additional processor bandwidth utilization.

### **FUNCTIONAL PIN DESCRIPTION**

### H-Bridge Outputs 0 (COSO+, COSO-, SINO+, SINO-)

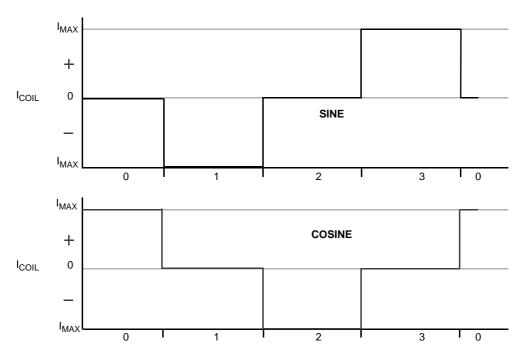

Each pin is the output pin of a half bridge, designed to source or sink current. The H-Bridge pins linearly drive the sine and cosine coils of two separate step motors to provide four-quadrant operation.

### **GROUND (GND)**

These pins serve as the ground for the source of the lowside output transistors as well as the logic portion of the device. They also help dissipate heat from the device.

### CHIP SELECT (CS)

The  $\overline{\text{CS}}$  pin enables communication with the master device. When this pin is in a logic [0] state, the 33970 is capable of transferring information to, and receiving information from, the master. The 33970 latches data in from the Input Shift registers to the addressed registers on the rising edge of  $\overline{\text{CS}}$ . The output driver on the SO pin is enabled when  $\overline{\text{CS}}$  is logic [0]. When  $\overline{\text{CS}}$  is logic high, signals at the SCLK and SI pins are ignored and the SO pin is tri-stated (high impedance).  $\overline{\text{CS}}$  will only be transitioned from a logic [1] state to a logic [0] state when SCLK is a logic [0].  $\overline{\text{CS}}$  has an internal pull-up ( $I_{\text{UP}}$ ) connected to the pin, as specified in the section of the Static Electrical Characteristics table entitled  $\overline{\text{CONTROL I/O}}$ , which is found on page  $\underline{6}$ .

### **SERIAL CLOCK (SCLK)**

SCLK clocks the Internal Shift registers of the 33970 device. The Serial Input (SI) pin accepts data into the Input Shift register on the falling edge of the SCLK signal, while the Serial Output pin (SO) shifts data information out of the SO Line Driver on the rising edge of the SCLK signal. It is important that the SCLK pin be in a logic [0] state whenever the  $\overline{\text{CS}}$  makes any transition. SCLK has an internal pull down ( $I_{\text{DWN}}$ ), as specified in the section of the Static Electrical Characteristics table entitled  $\underline{\text{CONTROL I/O}}$ , which is found on page  $\underline{\textbf{6}}$ . When  $\overline{\text{CS}}$  is logic [1], signals at the SCLK and SI pins are ignored and SO is tri-stated (high impedance). Refer to the data transfer timing diagrams in  $\underline{\text{Figure 6}}$  and  $\underline{\text{Figure 7}}$  on page  $\underline{\textbf{12}}$ .

### **SERIAL OUTPUT (SO)**

The SO data pin is a tri-stateable output from the Shift register. The Status register bits are the first 16 bits shifted out. Those bits are followed by the message bits clocked in FIFO, when the device is in a daisy chain connection or being sent words that are multiples of 16 bits. Data is shifted on the rising edge of the SCLK signal. The SO pin will remain in a high impedance state until the  $\overline{\text{CS}}$  pin is put into a logic low state.

### **SERIAL INPUT (SI)**

The SI pin is the input of the Serial Peripheral Interface (SPI). Serial Input (SI) information is read on the falling edge of SCLK. A 16-bit stream of serial data is required on the SI pin, beginning with the most significant bit (MSB). Messages that are not multiples of 16 bits (e.g., daisy chained device messages) are ignored. After transmitting a 16-bit word, the  $\overline{\text{CS}}$  pin must be de-asserted (logic [1]) before transmitting a new word. SI information is ignored when  $\overline{\text{CS}}$  is in a logic high state.

### **Multiplexed Output (RTZ)**

This is a multiplexed output pin, for the non-driven coil, during a Return to Zero (RTZ) event.

### Voltage (VDD)

This SPI and logic power supply input will work with  $5.0\ V$  supplies.

### **RESET (RST)**

If the master decides to reset the device, or place it into a sleep state, the RST pin is driven to a logic [0]. A logic [0] on the RST pin will force all internal logic to the known default state. This input has an internal active pull-up.

### **BATTERY VOLTAGE (VPWR)**

Power supply.

# H-BRIDGE OUTPUTS 1 (SIN1-, SIN1+, COS1-, COS1+)

Each of this pins is the output pin of a half bridge, designed to source or sink current. The H-Bridge pins linearly drive the

sine and cosine coils of two separate step motors to provide four-quadrant operation.

### **FUNCTIONAL DEVICE OPERATION**

### **OPERATIONAL MODES**

### SPI PROTOCOL DESCRIPTION

The SPI interface has a full-duplex, three-wire synchronous, 16-bit serial synchronous interface data transfer and four I/O lines associated with it: Chip Select (CS), Serial Clock (SCLK), Serial Input (SI), and Serial Output

(SO). The SI/SO pins of the 33970 follow a first in/first out (D15/D0) protocol with both input and output words transferring the most significant bit first. All inputs are compatible with 5.0 V CMOS logic levels.

### LOGIC COMMANDS AND REGISTERS

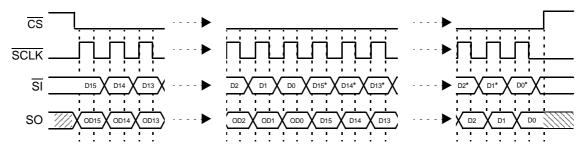

This section provides a description of the 33970 SPI behavior. To follow the explanations below, refer to Table 5 and to the timing diagrams shown in Figure 6 and Figure 7.

**Table 5. Data Transfer Timing**

| Pin         | Description                                                                                                              |

|-------------|--------------------------------------------------------------------------------------------------------------------------|

| CS (1-to-0) | SO pin is enabled.                                                                                                       |

| CS (0-to-1) | 33970 configuration and desired output states are transferred and executed according to the data in the Shift registers. |

| SO          | Will change state on the rising edge of the SCLK pin signal.                                                             |

| SI          | Will accept data on the falling edge of the SCLK pin signal.                                                             |

**Note** SO is tri-stated when  $\overline{CS}$  is logic [1].

Figure 6. Single 16-Bit Word SPI Communication

- **Notes** 1. SO is tri-stated when  $\overline{CS}$  is logic [1].

- 2. D15, D14, D13, ..., and D0 refer to the first 16 bits of data into the 33970.

3. D15\*, D14\*, D13\*, ..., and D0\* refer to the most recent entry of program data into the 33970.

- 4. OD15, OD14, OD13, ..., and OD0 refer to the first 16 bits of fault and status data out of the 33970.

Figure 7. Multiple 16-Bit Word SPI Communication

### **DATA INPUT**

The Input Shift register captures data at the falling edge of the SCLK clock. The SCLK clock pulses exactly 16 times only inside the transmission windows ( $\overline{\text{CS}}$  in a logic [0] state). By the time the  $\overline{\text{CS}}$  signal goes to logic [1] again, the contents of the Input Shift register are transferred to the appropriate internal register, to the address contained in bits 15:13. The minimum time  $\overline{\text{CS}}$  should be kept high depends on the internal clock speed. That data is specified in the SPI INTERFACE TIMING section of the Static Electrical Characteristics, which is found on page  $\underline{\textit{T}}$ . It must be long enough so the internal clock is able to capture the data from the Input Shift register and transfer it to the internal registers.

#### **DATA OUTPUT**

At the first rising edge of the SCLK clock, with the  $\overline{\text{CS}}$  at logic [0], the contents of the selected Status Word register are transferred to the Output Shift register. The first 16 bits clocked out are the status bits. If data continues to clock in before the  $\overline{\text{CS}}$  transitions to a logic [1], the device begins to shift out the data previously clocked in FIFO after the  $\overline{\text{CS}}$  first transitioned to logic [0].

### COMMUNICATION MEMORY MAPS AND REGISTER DESCRIPTIONS

The 33970 device is capable of interfacing directly with a microcontroller via the 16-bit SPI protocol described and specified below. The device is controlled by the microprocessor and reports back status information via the SPI. This section provides a detailed description of all registers accessible via serial interface. The various registers control the behavior of this device.

A message is transmitted by the master beginning with the MSB (D15) and ending with the LSB (D0). Multiple messages can be transmitted in succession to accommodate those applications where daisy chaining is desirable, or to confirm transmitted data, as long as the messages are all multiples of 16 bits. Data is transferred through daisy-chained devices, as illustrated in Figure 7, page 12. If an attempt is made to latch in a message smaller than 16 bits wide, it is ignored.

The 33970 uses six registers to configure the device, control the state of the four H-bridge outputs, and determine the type of status information that is clocked back to the master. The registers are addressed via D15:D13 of the incoming SPI word (refer to **Table 6**).

### **MODULE MEMORY MAP**

Various registers of the 33970 SPI module are addressed by the three MSBs of the 16-bit word received serially. Functions to be controlled include:

- · Individual gauge drive enabling

- Power-up/down

- · Internal clock calibration

- Gauge pointer position and velocity

- · Gauge pointer zeroing

- · Air core motor movement emulation

· Status information

Status reporting includes:

- Individual gauge overtemperature condition

- · Battery overvoltage

- · Battery undervoltage

- Pointer zeroing status

- Internal clock status

- Confirmation of coil output changes that should result in pointer movement

- Real time pointer position information

- · Real time pointer velocity step information

- · Pointer movement direction

- · Command pointer position status

- · RTZ accumulator value

**Table 6** provides the registers available to control the above functions.

Table 6. Module Memory Map

| Address<br>[15:13] | Register                                               | Name  | See Page |

|--------------------|--------------------------------------------------------|-------|----------|

| 000                | Power, Enable, Calibration, and Configuration Register | PECCR | Page 13  |

| 001                | Maximum Velocity Register                              | VELR  | Page 15  |

| 010                | Gauge 0 Position Register                              | POS0R | Page 15  |

| 011                | Gauge 1 Position Register                              | POS1R | Page 15  |

| 100                | Gauge Return to 0 Register                             | RTZR  | Page 16  |

| 101                | Gauge Return to 0<br>Configuration Register            | RTZCR | Page 17  |

| 110                | Not Used                                               | -     | _        |

| 111                | Reserved for Test                                      | -     | _        |

### **REGISTER DESCRIPTIONS**

The following section describes the registers, their addresses, and their impact on device operation.

### Address 000—Power, Enable, Calibration, and Configuration Register (PECCR)

The Power, Enable, Calibration, and Configuration Register is illustrated in **Table 7**, page <u>14</u>. A write to the 33970 using this register allows the master to

- (1) independently enable or disable the output drivers of the two-gauge controllers, (2) calibrate the internal clock,

- (3) disable the air core emulation, (4) select the direction of the pointer movement during pointer positioning and zeroing,

- (5) configure the device for the desired status information to be clocked out into the SO pin, or (6) send a null command for the purpose of reading the status bits. This register is also used to place the 33970 into a low current consumption mode.

Each of the gauge drivers can be enabled by writing a logic [1] to their assigned address bits, PE0 and PE1 respectively. This feature could be used to disable a driver if

33970

### FUNCTIONAL DEVICE OPERATION LOGIC COMMANDS AND REGISTERS

it is failing or is not being used. The device can be placed into a standby current mode by writing a logic [0] to both PE0 and PE1. During this state, most current consuming circuits are biased off. When in the Standby mode, the internal clock will remain ON.

The internal state machine utilizes a ROM table of step times defining the duration that the motor will spend at each microstep as it accelerates or decelerates to a commanded position. The accuracy of the acceleration and velocity of the motor is directly related to the accuracy of the internal clock. Although the accuracy of the internal clock is temperature independent, the non-calibrated tolerance is +70% to -35%. The 33970 was designed with a feature allowing the internal clock to be software calibrated to a tighter tolerance of  $\pm 10\%$ , using the  $\overline{CS}$  pin and a reference time pulse provided by the microcontroller.

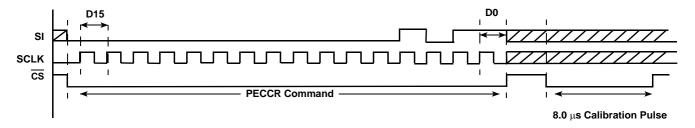

Calibration of the internal clock is initiated by writing a logic [1] to PE3. The calibration pulse, which must be  $8.0\,\mu s$  for an internal clock speed of 1.0 MHz, will be sent on the CS pin immediately after the SPI word is sent. No other SPI lines will be toggled. A clock calibration will be allowed only if the gauges are disabled or the pointers are not moving, as indicated by status bits MOV0 and MOV1. Additional details are provided in the INTERNAL CLOCK CALIBRATION section, beginning on page 26.

Some applications may require a guaranteed maximum pointer velocity and acceleration. Guaranteeing these maximums requires that the nominal internal clock frequency fall below 1.0 MHz. The frequency range of the calibrated clock will always be below 1.0 MHz if bit PE4 is logic [0] when initiating a calibration command, followed by an 8.0  $\mu s$  reference pulse. The frequency will be centered at 1.0 MHz if bit PE4 is logic [1].

Some applications may require a slower calibrated clock due to a lower motor gear reduction ratio. Writing a logic [1] to bit PE2 will slow the internal oscillator by one-third. Slowing the clock accommodates a longer calibration pulse without overrunning the internal counter—a condition designed to generate a CAL fault indication. For example, calibration for

a clock frequency of 667 kHz would require a calibration pulse of 12  $\mu s.$  Unless the internal oscillator is slowed by writing PE2 to logic [1], a 12  $\mu s$  calibration pulse may overrun the counter and generate a CAL fault indication.

Some applications may require faster pointer positioning than is provided with the air core motor emulation feature. This feature is enabled with the device that is in the default mode. Writing logic [1] to bit PE5 will disable the air core emulation and provide a constant acceleration and deceleration at the maximum rate.

Bit D6 is logic [0] during a PECCR commands.

The default Pointer Position 0 (PE7 = 0) will be the farthest counter-clockwise position. A logic [1] written to bit PE7 will change the location of the position 0, for the Gauge selected by bit PE8, to the farthest clockwise position. A change in position 0 of only one, or both, of the two coils can be accomplished by using bits PE8 and PE7. Performing an RTZ will always move the pointer to position 0. Exercise care when writing to PECCR bits PE8 and PE7 in order to prevent accidental changes of the position 0 locations.

Bits PE11:PE8 determine the content of the bits clocked out of the SO pin. When bit PE11 is at logic [0], the clocked out bits will provide device status. If a logic [1] is written to bit PE11, the bits clocked out of the SO pin, depending upon the state of bits PE10:PE8, provides either:

- Accumulator information and detection status during the RTZ (PE10 logic [0])

- Real time pointer position location at the time CS goes low (PE10 logic [1] and PE9 logic [0]), or

- The real time step position of the pointer as described in the velocity Table 21, page 24 (PE10, PE9, and PE8 logic [1]).

Additional details are provided in the <u>SO Communication</u> section beginning on page <u>18</u>.

If bit PE12 is logic [1] during a PECCR command, the state of PE11:PE0 is ignored. This is referred to as the null command and can be used to read device status without affecting device operation.

Table 7. Power, Enable, Calibration, and Configuration Register (PECCR)

|       | Address 000 |      |      |     |     |     |    |     |     |     |     |     |     |

|-------|-------------|------|------|-----|-----|-----|----|-----|-----|-----|-----|-----|-----|

| Bits  | D12         | D11  | D10  | D9  | D8  | D7  | D6 | D5  | D4  | D3  | D2  | D1  | D0  |

| Read  | -           | _    | -    | _   | _   | -   | _  | -   | -   | -   | -   | _   | _   |

| Write | PE12        | PE11 | PE10 | PE9 | PE8 | PE7 | 0  | PE5 | PE4 | PE3 | PE2 | PE1 | PE0 |

The bits in Table 7 are write-only.

PE12 (D12)—Null Command for Status Read

- 0 = Disable

- 1 = Enable

PE11 (D11) — Status Select bit. This bit selects the information clocked out of the SO pin.

0 = Device Status (the logic states of PE10, PE9, and PE8 don't cares)  1 = RTZ Accumulator Value, Gauge 0 or 1 Pointer position, or Gauge 0 and 1 Velocity ramp position (depending upon the logic states of PE10, PE9, and PE8)

PE10 (D10)—RTZ Accumulator or Pointer Status Select bit. This bit is recognized only when PE11 = 1.

- 0 = RTZ Accumulator Value and status

- 1 = Pointer Position or Speed

PE9 (D9)—Pointer Position or Pointer Speed Select bit. This bit is recognized only if PE11 and PE10 = 1.

- 0 = Gauge 0 or Gauge 1 Pointer Position

- 1 = Gauge 0 and Gauge 1 Pointer Speed

PE8 (D8)—Pointer Position Gauge Select bit. Also the Position 0 of the selected gauge is determined by the PE7 selection. This bit is recognized only if PE11 and PE10 = 1 and PE9 = 0.

- 0 = Gauge 0 position

- 1 = Gauge 1 position

PE7 (D7)—Position 0 Location Select bit. This bit determines the Position 0 of the gauge selected by PE8. RTZ direction will always be to the position 0.

- 0 = Position 0 is the most CCW (counterclockwise) position

- 1 = Position 0 is the most CW (clockwise) position

PE6 (D6)—This bit must be transmitted as logic [0] for valid PECCR commands.

PE5 (D5)—Air Core Motor Emulation bit. This bit is enabled or disabled (acceleration and deceleration is constant if disabled).

- 0 = Enable

- 1 = Disable

PE4 (D4)—Clock Calibration Frequency Selector

- 0 = Maximum f =1.0 MHz (for 8.0 μs calibration pulse)

- 1 = Nominal f =1.0 MHz (for 8.0 μs calibration pulse)

PE3 (D3)—Clock Calibration Enable bit. This bit enables or disables the clock calibration.

- 0 = Disable

- 1 = Enable

PE2 (D2)—Oscillator Adjustment

- 0 = t<sub>CLU</sub>

- $1 = 0.66 \times t_{CLU}$

PE1 (D1)—Gauge 1 Enable bit. This bit enables or disables the output driver of Gauge 1.

- 0 = Disable

- 1 = Enable

PE0 (D0)—Gauge 0 Enable bit. This bit enables or disables the output driver of Gauge 0.

- 0 = Disable

- 1 = Enable

#### Address 001—Maximum Velocity Register (VELR)

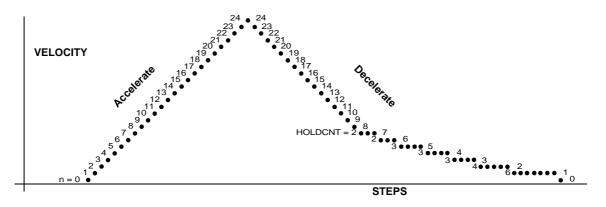

The Gauge Maximum Velocity Register is used to set a maximum velocity for each gauge (refer to **Table 8**). Bits V7:V0 contain a position value from 1–225 that is representative of the velocity position value described in **Table 21**, page 24. The table value becomes the maximum velocity until it is changed to another value. If a maximum value is chosen greater than the maximum velocity in the acceleration table, the maximum table value becomes the maximum velocity. If the motor is turning at a speed greater than the new maximum, the motor immediately moves down the velocity ramp until the speed falls equal to or below it. Velocity for each motor can be changed simultaneously or independently by writing V8 and/or V9 to a logic [1]. Bits V12:V10 must be at logic [0] for valid VELR commands.

Table 8. Maximum Velocity Register (VELR)

|       | Address 001 |     |     |    |    |    |    |    |    |    |    |    |    |

|-------|-------------|-----|-----|----|----|----|----|----|----|----|----|----|----|

| Bits  | D12         | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| Read  | _           | -   | _   | -  | _  | _  | -  | _  | _  | -  | _  | 1  | _  |

| Write | 0           | 0   | 0   | V9 | V8 | V7 | V6 | V5 | V4 | V3 | V2 | V1 | V0 |

The bits in Table 8 are write-only.

V12:V10 (D12:D10)—These bits must be transmitted as logic [0] for valid VELR commands

V9 (D9) — Gauge 1 Velocity. Specifies whether the maximum velocity determined in the V7: V0 field will apply to Gauge 1.

- 0 = Velocity does not apply to Gauge 1

- 1 = Velocity applies to Gauge 1

V8 (D8) — Gauge 0 Velocity. Specifies whether the maximum velocity specified in the V7: V0 field will apply to Gauge 0.

- 0 = Velocity does not apply to Gauge 0

- 1 = Velocity applies to Gauge 0

V7:V0 (D7:D0)—Maximum Velocity. Specifies the maximum velocity position from **Table 21**. This velocity will remain the maximum of the intended gauge until changed by command. Velocities can range from position 1 (00000001) to position 225 (11111111).

### Addresses 010 and 011—Gauge 0/1 Position Registers (POS0R, POS1R)

Gauge 0 Position Register (SI Addresses 010) bits P011:P00 are written to when communicating the desired pointer positions, and Gauge 1 Position Register (SI Address 011) bits P111:P10 are written to when communicating the desired pointer positions. Commanded positions can range from 0 to 4095. The D12 bit must be at logic [0] for valid POS0R and POS1R commands.

Table 9. Gauge 0 Position Register (POS0R)

|       |                                                |      |      |     |     | Addr | ess 010 |     |     |     |     |     |     |  |

|-------|------------------------------------------------|------|------|-----|-----|------|---------|-----|-----|-----|-----|-----|-----|--|

| Bits  | Bits D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 |      |      |     |     |      |         |     |     |     |     |     |     |  |

| Read  | -                                              | -    | -    | -   | _   | _    | -       | _   | _   | -   | -   | -   | -   |  |

| Write | 0                                              | P011 | P010 | P09 | P08 | P07  | P06     | P05 | P04 | P03 | P02 | P01 | P00 |  |

The bits in Table 9 are write-only.

P012 (D12)—This bit must be transmitted as logic [0] for valid commands.

P011:P00 (D11:D0)—Desired pointer position of Gauge 0. Pointer positions can range from 0 (00000000000) to position 4095 (11111111111). For a step motor requiring 12 microsteps per degree of pointer movement, the maximum pointer sweep is 341.25°.

Table 10. Gauge 1 Position Register (POS1R)

|       |                                                |      |      |     |     | Addr | ess 011 |     |     |     |     |     |     |  |

|-------|------------------------------------------------|------|------|-----|-----|------|---------|-----|-----|-----|-----|-----|-----|--|

| Bits  | Bits D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 |      |      |     |     |      |         |     |     |     |     |     |     |  |

| Read  | -                                              | -    | -    | -   | -   | -    | -       | -   | -   | -   | -   | -   | -   |  |

| Write | 0                                              | P111 | P110 | P19 | P18 | P17  | P16     | P15 | P14 | P13 | P12 | P11 | P10 |  |

The bits in **Table 10** are write-only.

P1 12 (D12)—This bit must be transmitted as logic [0] for valid commands.

P111:P10 (D11:D0)—Desired pointer position of Gauge 1. Pointer positions can range from 0 (00000000000) to position 4095 (111111111111). For a step motor requiring 12 microsteps per degree of pointer movement, the maximum pointer sweep is 341.25° (4095  $\div$  12).

### Address 100—Gauge Return to Zero Register (RTZR)

Gauge Return to Zero Register (RTZR) (refer to **Table 11**) is written to return the gauge pointers to the zero position. During an RTZ event, the pointer is returned to zero using full steps, where only one coil is driven at any point in time. The back electromotive force (EMF) signal present on the non-

driven coil is integrated and its results are stored in an accumulator.

A logic [1] written to bit RZ1 enables a Return to Zero for Gauge 0 if RZ0 is logic [0], and Gauge 1 if RZ0 is logic [1], respectively. Similarly, a logic [0] written to bit RZ1 disables a Return to Zero for Gauge 0 when RZ0 is logic [0], and Gauge 1 when RZ0 is logic [1], respectively.

Bits D12:D5 and D3:D2 must be at logic [0] for valid RTZR commands.

Bit RZ4 is used to enable an unconditional RTZ event. A logic [0] results in a typical RTZ event, automatically providing a Stop when a stall condition is detected. A logic [1] will result in RTZ movement, causing a Stop if a logic [0] is written to bit RZ0. This feature is useful during development and characterization of RTZ requirements.

Table 11. Return to Zero Register (RTZR)

|       |                                                |   |   |   |   | Addr | ess 100 |   |     |   |     |     |     |  |

|-------|------------------------------------------------|---|---|---|---|------|---------|---|-----|---|-----|-----|-----|--|

| Bits  | Bits D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 |   |   |   |   |      |         |   |     |   |     |     |     |  |

| Read  | _                                              | _ | _ | _ | _ | _    | _       | _ | _   | _ | _   | _   | _   |  |

| Write | 0                                              | 0 | 0 | 0 | 0 | 0    | 0       | 0 | RZ4 | 0 | RZ2 | RZ1 | RZ0 |  |

The register bits in **Table 11** are *write-only*.

RZ12:RZ5 (D12:D5)—These bits must be transmitted as logic [0] for valid commands.

RZ4 (D4)—This bit is used to enable an unconditional RTZ event.

- 0 = Automatic Return to Zero

- 1 = Unconditional Return to Zero

RZ3 (D3)—This bit must be transmitted as logic [0] for valid commands.

RZ2 (D2)—Return to Zero Direction bit. This bit is used to properly sequence the integrator, depending upon the desired zeroing direction.

- 0 = Return to Zero will occur in the CCW direction (PE7 = 0)

- 1 = Return to Zero will occur in the CW direction (PE7 = 1)

RZ1 (D1)—Return to Zero Direction. This bit commands the selected gauge to return the pointer to zero position.

- 0 = Return to Zero Disabled

- 1 = Return to Zero Enabled

RZ0 (D0)—Gauge Select: Gauge 0/Gauge 1. This bit selects the gauge to be commanded.

- 0 = Selects Gauge 0

- 1 = Selects Gauge 1

### Address 101—Gauge Return to Zero Configuration Register

Gauge Return to Zero Configuration Register (RTZCR) is used to configure the Return to Zero Event (refer to Table 12). It is written to modify the step time, or rate; at which the pointer moves during an RTZ event. Also, the integration blanking time, which is the time immediately following the transition of a coil from a driven state to an open state in the RTZ mode, is adjustable with this command. Finally, this command is used to adjust the threshold of the RTZ integration register.

The values used for this register should be selected during development to optimize the RTZ for each application. Selecting an RTZ step rate resulting in consistently successful zero detections depends on a clear understanding of the motor characteristics. Specifically, resonant frequencies exist due to the interaction between the motor and the pointer. This command allows movement of the RTZ pointer speed away from these frequencies. Also, some motors require a significant amount of time for the pointer to settle to a steady state position when moving from one full step position to the next. Consistent and accurate integration values require the pointer be stationary at the end of the full step time.

Bits RC3:RC0, RC12:RC11, and RC4 determine the time spent at each full step during an RTZ event. Bits RC3:RC0 are used to select a  $\Delta t$  ranging from 0 ms (0000) to 61.44 ms (1111) in increments of 4.096 ms (refer to **Table 13**). The  $\Delta t$  is multiplied by the factor M, which is defined by bits RC12:RC11. The product is then added to the blanking time, selected using bit RC4, to generate the full step time. The multiplier selected with RC12:RC11 will be 1 (00), 2 (01), or 4 (10) as illustrated in the equations below. Note that the RC12:RC11 value of 8 (11) is not recommended for use in a product design application, because of the potential for an RTZ accumulator internal overflow, due to the long time step. The blanking time is either 512  $\mu s$  when RC4 is logic [0], or

768  $\mu s$  when it is logic [1].The full step time is generated using the following equations:

When D3:D0 (RC3:RC0) ≠ 0000

Full Step  $(t) = \Delta t \times M + blanking (t)(1)$

When D3:D0 (RC3:RC0) = 0000

Full Step (t) = blanking (t) + 2.048 ms(2)

**Note** In equation (2), a 2.048 ms offset is added to the full step time when the RC:3:RC0 = 0000. The full step time default value after a logic reset is 12.80 ms (RC12:RC11 = 00, RC4 = 0, and RC3:RC0 = 0011).

If there are two full steps per degree of pointer movement, the pointer speed is 1/(FullStep x 2) deg/s.

Detecting pointer movement is accomplished by integrating the EMF present in the non-driven coil during the RTZ event. The integration circuitry is implemented using a Sigma-Delta converter resulting in the placement of a value in the 15-bit RTZ accumulator at the end of each full step. The value in the RTZ accumulator represents the change in flux and is compared to a threshold. Values above the threshold indicate a pointer is moving. Values below the threshold indicate a stalled pointer, thereby resulting in the cessation of the RTZ event.

The RTZ accumulator bits are signed and represented in two's complement. After a full step of integration, a sign bit of 0 is the indicator of an accumulator exceeding the decision threshold of 0, and the pointer is assumed to still be moving. Similarly, if the sign bit is logic [1] after a full step of integration, the accumulator value is negative and the pointer is assumed to be stopped. The integrator and accumulator are initialized after each full step. If the PECCR command is written to clock out the RTZ accumulator values via the SO, the OD14 bit corresponds to the sign bit of the RTZ accumulator.

Accurate pointer stall detection depends on a correctly preloaded accumulator for specific gauge, pointer, and full step combinations. Bits RC10:RC5 are used to offset the initial RTZ accumulator value, properly detecting a stalled motor. The initial accumulator value at the start of a full step of integration is negative. If the accumulator was correctly preloaded, a free-moving pointer will result in a positive value at the end of the integration time, and a stalled pointer will result in a negative value. The preloaded values associated with each combination of bits RC10:RC5 are illustrated in Table 14. The accumulator should be loaded with a value resulting in an accumulator MSB to a logic [1] when the motor is stalled. For the default mode, after a power-up or any reset, the 33970 device sets the accumulator value to -1.

Table 12. RTZCR SI Register Assignment

|       | Address 101                                                                                                                                                          |  |  |  |  |  |  |  |  |  |  |  |     |  |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|-----|--|--|

| Bits  | Bits D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0                                                                                                                       |  |  |  |  |  |  |  |  |  |  |  |     |  |  |

| Read  | Read                                                                                                                                                                 |  |  |  |  |  |  |  |  |  |  |  |     |  |  |

| Write | Write         RC12         RC11         RC10         RC9         RC8         RC7         RC6         RC5         RC4         RC3         RC2         RC1         RC0 |  |  |  |  |  |  |  |  |  |  |  | RC0 |  |  |

33970

The bits in Table 12 are write-only.

RC12:RC11 (D12:D11) — These bits, along with RC3:RC0 (D3:D0) and RC4 (D4), determine the full step time and, therefore, the rate at which the pointer will move during an RTZ event. The values of D12:D11 determine the multiplier (M) is used in equation (1) (refer to page 17).

RC12:RC11 = M

- 00 = 1

- 01 = 2

- 10 = 4

- 11 = 8 (Not to be used for design)

RC10:RC5 (D10:D5)—These bits determine the value preloaded into the RTZ integration accumulator to adjust the detection threshold. Values range from -1 (00000000) to -1099 (11111111) as shown in **Table 14**.

RC4 (D4)—This bit determines the RTZ blanking time (*blanking* (*t*)).

- $0 = 512 \,\mu s$

- $1 = 768 \mu s$

RC3:RC0 (D3:D0)—These bits, along with RC12:RC11 (D12:D11) and RC4 (D4), determine the time variables used to calculate the full step times with equations (1) or (2) illustrated above. RC3:RC0 determines the  $\Delta t$  time. The  $\Delta t$  values range from 0 (0000) to 61.440 ms (1111) and are shown in **Table 13**. The default  $\Delta t$  is 0 (0011).

**Note** Equation (2) (refer to page <u>17</u>) is only used to calculate the full step time if RC3:RC0 = 0000. Use equation (1) for all other combinations of RC3:RC0.

Table 13. RTZCR Full Step Time

| RC3 | RC2 | RC1 | RC0 | ∆t (ms) |

|-----|-----|-----|-----|---------|

| 0   | 0   | 0   | 0   | 0       |

| 0   | 0   | 0   | 1   | 4.096   |

| 0   | 0   | 1   | 0   | 8.192   |

| 0   | 0   | 1   | 1   | 12.288  |

| 0   | 1   | 0   | 0   | 16.384  |

| 0   | 1   | 0   | 1   | 20.480  |

| 0   | 1   | 1   | 0   | 24.576  |

| 0   | 1   | 1   | 1   | 28.672  |

| 1   | 0   | 0   | 0   | 32.768  |

| 1   | 0   | 0   | 1   | 36.864  |

| 1   | 0   | 1   | 0   | 40.960  |

| 1   | 0   | 1   | 1   | 45.056  |

| 1   | 1   | 0   | 0   | 49.152  |

| 1   | 1   | 0   | 1   | 53.248  |

| 1   | 1   | 1   | 0   | 57.344  |

| 1   | 1   | 1   | 1   | 61.440  |

**Table 14. RTZCR Accumulator Offset**

| RC10 | RC9 | RC8 | RC7 | RC6 | RC5 | Preload Value<br>(PV) | Initial Accumulator<br>Value = (-16xPV) -1 |

|------|-----|-----|-----|-----|-----|-----------------------|--------------------------------------------|

| 0    | 0   | 0   | 0   | 0   | 0   | 0                     | -1                                         |

| 0    | 0   | 0   | 0   | 0   | 1   | 1                     | -17                                        |

| 0    | 0   | 0   | 0   | 1   | 0   | 2                     | -33                                        |

| 0    | 0   | 0   | 0   | 1   | 1   | 3                     | -49                                        |

| 0    | 0   | 0   | 1   | 0   | 0   | 4                     | -65                                        |

|      |     |     |     |     |     |                       |                                            |

|      |     |     |     |     |     |                       | ·                                          |

| 1    | 1   | 1   | 1   | 1   | 1   | 63                    | -1009                                      |

### **SO Communication**

When the  $\overline{\text{CS}}$  pin is pulled low, the internal status register, as configured with the PECCR command bits PE11:PE8, is loaded into the output register and the data is clocked out MSB (OD15) first. Following a  $\overline{\text{CS}}$  transition 0 to 1, the device determines if the shifted-in message was of a valid length (a valid message length is one that is greater than 0 bits and a multiple of 16 bits), and if so, latches the incoming data into the appropriate registers.

At this time, the SO pin is tri-stated and the status register is now able to accept new status information. Fault status information will be latched and held until the Device Status Output register is selected and it is clocked out via the SO. If the message length was determined to be invalid, the fault information will not be cleared and will be transmitted again during the next valid SPI message. Pointer status information bits (e.g., pointer position, velocity, and commanded position status) will always reflect the real time state of the pointer.

Any bits clocked out of the SO pin after the first 16 are representative of the initial message bits clocked into the SI pin since the  $\overline{\text{CS}}$  pin first transitioned to a logic [0]. This feature is useful for daisy-chaining devices as well as message verification.

As described above, the last valid write to bits PE11:PE8 of the PECCR command determines the nature of the status data that is clocked out of the SO pin.

There are five different types of status information available:

- 1. Device Status (refer to Table 15 below)

- 2. RTZ Accumulator Status (refer to Table 16, page 20)

- Gauge 0 Pointer Position Status (refer to <u>Table 17</u>, page <u>21</u>)

- Gauge 1 Pointer Position Status (refer to <u>Table 18</u>, page <u>21</u>)

5. Gauge 1 and 2 Pointer Velocity Status (refer to Table 19, page 22)

Once a specific status type is selected, it will not change until either the PECCR command bits PE11:PE8 (D11:D8) are written to select another or the device is reset. Each of the Status types and the PECCR bit necessary to select them are described below.

#### **Device Status Information**

Most recent valid PECCR command resulting in the Device Status output:

| D11 | D10 | D9 | D8 |

|-----|-----|----|----|

| 0   | х   | Х  | х  |

x = Don't care.

Table 15. Device Status Output Register

| Bits  | OD15 | OD14 | OD13  | OD12  | OD11 | OD10 | OD9 | OD8 | OD7 | OD6  | OD5  | OD4  | OD3  | OD2  | OD1 | OD0 |

|-------|------|------|-------|-------|------|------|-----|-----|-----|------|------|------|------|------|-----|-----|

| Read  | DIR1 | DIR0 | 0POS1 | 0POS0 | CMD1 | CMD0 | OV  | UV  | CAL | OVUV | MOV1 | MOV0 | RTZ1 | RTZ0 | OT1 | ОТ0 |

| Write | _    | _    | _     | _     | _    | _    | _   | _   | -   | _    | _    | _    | _    | -    | _   | -   |

The bits in Table 15 are read-only bits.

DIR1 (OD15)—This bit indicates the direction Gauge 1 pointer is moving.

- 0 = Toward position 0

- 1 = Away from position 0

DIR0 (OD14)—This bit indicates the direction Gauge 0 pointer is moving.

- 0 = Toward position 0

- 1 = Away from position 0

0POS1 (OD13)—This bit indicates the configured Position 0 for Gauge 1.

- 0 = Farthest CCW

- 1 = Farthest CW

0POS0 (OD12)—This bit indicates the configured Position 0 for Gauge 0.

- 0 = Farthest CCW

- 1 = Farthest CW

CMD1 (OD11)—This bit indicates whether Gauge 1 is at the most recently commanded position.

- 0 = At commanded position

- 1 = Not at commanded position

CMD0 (OD10)—This bit indicates whether Gauge 0 is at the most recently commanded position.

- 0 = At commanded position

- 1 = Not at commanded position

OV (OD9)—Overvoltage Indication. A logic [1] on this bit indicates  $V_{PWR}$  voltage exceeded the upper limit of  $V_{PWROV}$  since the last SPI communication (refer to the Static Electrical Characteristics table under <u>POWER INPUT</u>, page <u>5</u>). An

overvoltage event will automatically disable the driver outputs. Because the pointer may not be in the expected position, the master may want to re-calibrate the pointer position with an RTZ command after the voltage returns to a normal level. For an overvoltage event, both gauges must be re-enabled as quickly as this flag returns to logic [0]. The state machine will continue to operate properly as long as  $V_{\text{DD}}$  is within the normal range.

- 0 = Normal range

- 1 = Battery voltage exceeded V<sub>PWROV</sub>

UV (OD8) —Undervoltage Indication. A logic 1] on this bit indicates the  $V_{PWR}$  voltage fell below  $V_{PWRUV}$  since the last SPI communication (refer to the Static Electrical Characteristics table under <u>POWER INPUT</u>, page <u>5</u>). An undervoltage event is just flagged; however, at some voltage level below 4.0 V, the outputs turn OFF and the state machine resets. Because the pointer may not be in the expected position, the master may want to re-calibrate the pointer position with an RTZ command after the voltage returns to a normal level. For an undervoltage event, both gauges may need to be re-enabled as quickly as this flag returns to logic [0]. The state machine will continue to operate properly as long as  $V_{\rm DD}$  is within the normal range.

- 0 = Normal range

- 1 = Battery voltage fell below V<sub>PWRUV</sub>

CAL (OD7)—Calibrated Clock out of Specification. A logic [1] on this bit indicates the clock count calibrated to a value outside the expected range given the tolerance specified by  $t_{CLC}$  in the Dynamic Electrical Characteristics

33970

table under <u>POWER OUTPUT AND CLOCK TIMINGS</u>, page <u>7</u>.

- 0 = Clock within spec

- 1 = Clock out of spec

OVUV (OD6) — Undervoltage or Overvoltage Indication. A logic [1] on this bit indicates the  $V_{PWR}$  voltage fell to a level below the  $V_{PWRUV}$  since the last SPI communication (refer to the Static Electrical Characteristics table under  $\underbrace{POWER}$  INPUT, page 5). An undervoltage event is just flagged, while an overvoltage event automatically disables the drive outputs. Because the pointer may not be in the expected position, the master may want to re-calibrate the pointer with an RTZ command after the voltage returns to normal level. For an overvoltage event, both gauges must be re-enabled as soon as this flag returns to logic [0]. The state machine will continue to operate properly as long as  $V_{DD}$  is within the normal range.

- 0 = Normal range

- 1 = Battery voltage fell below V<sub>PWRUV</sub> or exceeded V<sub>PWROV</sub>

MOV1 (OD5) — This bit identifies Gauge 1 Movement since last SPI communication. A logic [1] on this bit indicates the Gauge 1 pointer position changed since the last SPI command. This information allows the master to confirm the pointer is moving as commanded.

- 0 = Gauge 1 position has not changed since the last SPI command

- 1 = Gauge 1 pointer position has changed since the last SPI command

MOV0 (OD4)—Gauge 0 Movement Since last SPI Communication. A logic [1] on this bit indicates the Gauge 0 pointer position has changed since the last SPI command. This information allows the master to confirm the pointer is moving as commanded.

- 0 = Gauge 0 position has not changed since the last SPI command

- 1 = Gauge 0 pointer position has changed since the last SPI command

RTZ1 (OD3)—RTZ1 Is Enabled or Disabled. A logic [1] on this bit indicates Gauge 1 is in the process of returning to the zero position as requested with the RTZ command. This bit will continue to indicate a logic [1] until the SPI message following a detection of the zero position, or the RTZ feature is commanded OFF using the RTZ message.

- 0 = Return to Zero disabled

- 1 = Return to Zero enabled successfully

RTZ0 (OD2) —RTZ0 Is Enabled or Disabled. A logic [1] on this bit indicates Gauge 0 is in the process of returning to the zero position as requested with the RTZ command. This bit continues to indicate a logic [1] until the SPI message following a detection of the zero position, or the RTZ feature is commanded OFF using the RTZ message.

- 0 = Return to Zero disabled

- 1 = Return to Zero enabled successfully

OT1 (OD1)—Gauge 1 Junction Overtemperature. A logic [1] on this bit indicates that the coil drive circuitry dedicated to drive Gauge 1 has exceeded the maximum allowable junction temperature since the last SPI communication and that Gauge 1 has been disabled. It is recommended that the pointer be re-calibrated using the RTZ command after re-enabling the gauge using the PECCR command. This bit remains logic [1] until the gauge is enabled.

- 0 = Temperature within range

- 1 = Gauge 1 maximum allowable junction temperature condition has been reached

OT0 (OD0)—Gauge 0 Junction Overtemperature. A logic [1] on this bit indicates that the coil drive circuitry dedicated to drive Gauge 0 has exceeded the maximum allowable junction temperature since the last SPI communication and that Gauge 0 has been disabled. It is recommended that the pointer be re-calibrated using the RTZ command after re-enabling the gauge using the PECCR command. This bit remains logic [1] until the gauge is reenabled.

- 0 = Temperature within range

- 1 = Gauge 0 maximum allowable junction temperature condition is reached

### **RTZ Accumulator Status Information**

Most recent valid PECCR command resulting in the RTZ Accumulator status output:

| D11 | D10 | D9 | D8 |

|-----|-----|----|----|

| 1   | 0   | Х  | Х  |

x = Don't care.

Table 16. RTZ Accumulator Status Output Register

| Bits  | OD15 | OD14  | OD13  | OD12  | OD11  | OD10  | OD9  | OD8  | OD7  | OD6  | OD5  | OD4  | OD3  | OD2  | OD1  | OD0  |

|-------|------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|------|------|

| Read  | RTZ  | ACC14 | ACC13 | ACC12 | ACC11 | ACC10 | ACC9 | ACC8 | ACC7 | ACC6 | ACC5 | ACC4 | ACC3 | AC2C | ACC1 | ACC0 |

| Write | -    | -     | -     | -     | -     | _     | -    | -    | -    | -    | -    | -    | -    | -    | -    | -    |

The bits in Table 16 are read-only bits.

RTZ (OD15)—RTZ Bit Is Enabled or Disabled. A logic [1] on this bit indicates that the Gauge is in the process of returning to the zero position as requested with the RTZ

command. This bit will continue to indicate a logic [1] until the SPI message following a detection of the zero position, or the RTZ feature is commanded OFF using the RTZ message.

• 0 = Return to Zero disabled

• 1 = Return to Zero enabled successfully

ACC14:ACC0 (OD14:OD0)—These 15 bits are from the RTZ accumulator. They represent the integrated signal present on the non-driven coil during an RTZ event. These bits are logic [0] after power-on reset, or after the RST pin transitions from logic [0] to [1]. After an RTZ event, they will represent the last RTZ accumulator result before the RTZ was stopped. ACC14 is the MSB and is the sign bit used for zero detection.

Figure 8. RTZ Accumulator (Typical)