**Features**

### 106.25MHz/212.5MHz/425MHz **Clock Oscillators**

#### **General Description**

The DS4106, DS4212, and DS4425 ceramic surfacemount crystal oscillators are part of Maxim's DS4-XO series crystal oscillators family. These devices offer output frequencies at 106.25MHz, 212.5MHz, and 425MHz. The clock oscillators are suited for systems with tight tolerances because of the litter, phase noise, and stability performance. The small package provides a format made for applications where PCB space is critical.

These clock oscillators are crystal based and use a fundamental crystal with PLL technology to provide the final output frequencies. Each device is offered with LVDS or LVPECL output types. The output enable pin is active-high logic.

These clock oscillators have very low phase jitter and phase noise. Typical phase jitter is < 0.9psRMS from 12kHz to 20MHz. The devices are designed to operate with a 3.3V ±5% supply voltage, and are available in a 5.0mm x 3.2mm x 1.49mm, 10-pin LCCC surface-mount ceramic package.

### **Applications**

Fibre Channel Hard Disk Drives

Host Bus Adapters

Raid Controllers

Fibre Channel Switches

**♦ Clock Output Frequencies:**

DS4106: 106.25MHz DS4212: 212.50MHz DS4425: 425.00MHz

- ♦ Phase Jitter (RMS): 0.9ps Typical

- **♦ LVPECL or LVDS Output**

- **♦ Supply Current:**

50mA (Typical, Unloaded) at +3.3V Supply (LVPECL)

53mA (Typical) at +3.3V Supply (LVDS)

- ♦ -40°C to +85°C Temperature Range

- ♦ Output Disable

### **Ordering Information**

| PART              | TEMP RANGE     | PIN-PACKAGE |

|-------------------|----------------|-------------|

| <b>DS4106</b> AN+ | -40°C to +85°C | 10 LCCC     |

| DS4106BN+         | -40°C to +85°C | 10 LCCC     |

| <b>DS4212</b> AN+ | -40°C to +85°C | 10 LCCC     |

| DS4212BN+         | -40°C to +85°C | 10 LCCC     |

| <b>DS4425</b> AN+ | -40°C to +85°C | 10 LCCC     |

| DS4425BN+         | -40°C to +85°C | 10 LCCC     |

+Denotes a lead-free package. The lead finish is JESD97 category e4 (Au over Ni) and is compatible with both lead-based and lead-free soldering processes.

Pin Configuration and Selector Guide appear at end of data sheet.

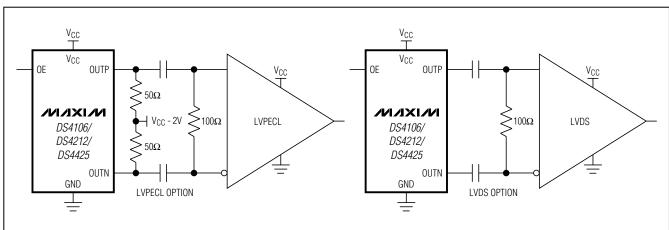

### **Typical Operating Circuits**

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> , GND, OE, OUTP, OUTN0.3V, +4V | Storage Temperature Range40°C to +125°C |

|------------------------------------------------|-----------------------------------------|

| Operating Temperature Range40°C to +85°C       | Soldering Temperature Profile           |

| Junction Temperature+150°C                     | (3 passes max)See IPC/JEDEC J-STD-020   |

|                                                | Specification                           |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = 3.0 \text{V to } 3.6 \text{V}, T_A = -40 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}, \text{ typical values are at } V_{CC} = +3.3 \text{V} \text{ and } T_A = +25 ^{\circ}\text{C}, \text{ unless otherwise noted.})$  (Note 1)

| PARAMETER                                                  | SYMBOL          | CONDITIONS           | MIN                     | TYP | MAX                    | UNITS |

|------------------------------------------------------------|-----------------|----------------------|-------------------------|-----|------------------------|-------|

| Supply Voltage                                             | Vcc             | (Note 2)             | 3.0                     | 3.3 | 3.6                    | V     |

| Cumply Cumpet                                              |                 | LVPECL (Note 3)      |                         | 50  | 65                     | Л     |

| Supply Current                                             | Icc             | LVDS                 | 53 67                   |     | mA                     |       |

| TTL Control Input-Voltage High (OE)                        | VIH             | (Note 2)             | 2                       |     |                        | V     |

| TTL Control Input-Voltage Low (OE)                         | VIL             | (Note 2)             |                         |     | 0.8                    | V     |

| Input Leakage Current                                      | lıL             |                      | -50                     |     | +10                    | μΑ    |

| LVPECL OUTPUTS (Note 4)                                    |                 |                      | <u> </u>                |     |                        |       |

| Output High Voltage                                        | VoH             | (Note 2)             | V <sub>CC</sub> - 1.085 |     | V <sub>CC</sub> - 0.88 | V     |

| Output Low Voltage                                         | V <sub>OL</sub> | (Note 2)             | V <sub>CC</sub> - 1.825 |     | V <sub>CC</sub> - 1.62 | V     |

| Output Leakage Current (Absolute)                          | I <sub>OL</sub> | OE = V <sub>IL</sub> |                         | 100 |                        | μA    |

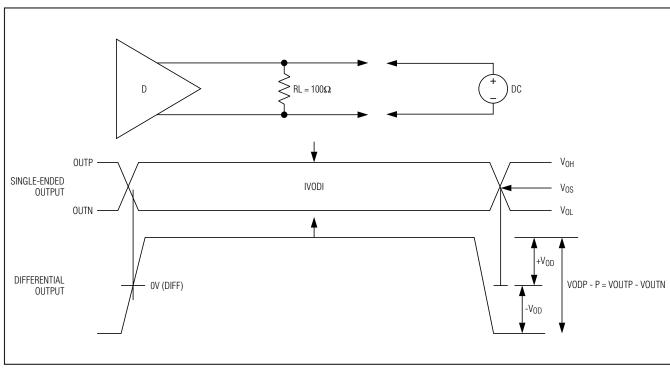

| LVDS OUTPUTS (Figure 2)                                    |                 |                      |                         |     |                        | •     |

| LVDS Output High Voltage                                   | V <sub>OH</sub> | (Note 2)             |                         |     | 1.475                  | V     |

| LVDS Output Low Voltage                                    | V <sub>OL</sub> | (Note 2)             | 0.925                   |     |                        | V     |

| LVDS Differential Output Voltage                           | V <sub>OD</sub> |                      | 250                     |     | 400                    |       |

| LVDS Change in V <sub>OD</sub> for Complementary States    | ΔIVODI          |                      |                         |     | 25                     | mV    |

| LVDS Offset Output Voltage<br>(Output Common-Mode Voltage) | Vos             | (Note 5)             | 1.125                   |     | 1.275                  | V     |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = 3.0 \text{V to } 3.6 \text{V}, T_A = -40 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}, \text{ typical values are at } V_{CC} = +3.3 \text{V} \text{ and } T_A = +25 ^{\circ}\text{C}, \text{ unless otherwise noted.})$  (Note 1)

| PARAMETER                                                     | SYMBOL                          | CONDITION                                | NS             | MIN | TYP   | MAX | UNITS |  |

|---------------------------------------------------------------|---------------------------------|------------------------------------------|----------------|-----|-------|-----|-------|--|

| LVDS Change in V <sub>OS</sub> for Complementary States       | Δ V <sub>OS</sub>               |                                          |                |     |       | 150 | mV    |  |

| LVDS Differential Output Impedance                            | Rolvdso                         |                                          |                | 80  |       | 140 | Ω     |  |

| LVDS Output Current                                           | ILVDSO                          | Outputs shorted together                 | er             |     | 12    |     | mA    |  |

| Output Current                                                | Ivsslvdso                       | Short to ground                          |                |     |       | 40  | mA    |  |

| CLOCK OUTPUT                                                  |                                 |                                          |                |     |       |     |       |  |

|                                                               |                                 | DS4106                                   |                |     | 106.2 |     |       |  |

| Clock Output Frequency                                        | fO                              | DS4212                                   |                |     | 212.5 |     | MHz   |  |

|                                                               |                                 | DS4425                                   |                |     | 425.0 |     |       |  |

| Frequency Stability Total                                     | Δf / f <sub>O</sub>             | Temperature, aging, loa                  | ad, and supply | -39 |       | +39 | ppm   |  |

| Initial Frequency Tolerance                                   | f_TOL                           | +25°C, ±3°C, V <sub>C</sub> C = 3.3      | BV             |     | ±20   |     | ppm   |  |

| Frequency Stability vs.<br>Temperature                        | Δf / fo  TA                     |                                          |                | -30 |       | +30 | ppm   |  |

| Frequency Stability vs. V <sub>CC</sub>                       | Δf / f <sub>O</sub>  v          | V <sub>CC</sub> = 3.3V ±10%              |                | -3  |       | +3  | ppm/V |  |

| Frequency Stability vs. Load                                  | Δf / f <sub>O</sub>             | ±10% variation in termination resistance |                |     | ±1    |     | ppm   |  |

| Aging (15 Years)                                              | faging                          |                                          |                | -7  |       | +7  | ppm   |  |

| Phase Jitter (RMS)                                            | PJRMS                           | 12kHz to 20MHz                           |                |     | 0.9   |     | ps    |  |

|                                                               |                                 | 10kHz                                    |                |     | 3     |     |       |  |

| Accumulated Deterministic Jitter Due to Reference Spurs (P-P) |                                 | 100kHz<br>200kHz                         |                |     | 27    |     | ps    |  |

|                                                               |                                 |                                          |                |     | 15    |     |       |  |

|                                                               |                                 | 1MHz                                     |                |     | 7     |     |       |  |

| Clock Output Edge Speeds                                      | t <sub>R</sub> , t <sub>F</sub> | 20% to 80%                               | LVPECL         |     | 200   |     |       |  |

| Clock Output Edge Speeds                                      | IK, IF                          | 20 /0 10 00 /0                           | LVDS           |     | 175   |     | ps    |  |

| Clock Output Duty Cycle                                       |                                 | +25°C                                    |                | 45  |       | 55  | %     |  |

| Oscillation Startup Time                                      |                                 | (Note 6)                                 |                |     | 10    |     | ms    |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = 3.0 \text{V to } 3.6 \text{V}, T_A = -40 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}, \text{ typical values are at } V_{CC} = +3.3 \text{V} \text{ and } T_A = +25 ^{\circ}\text{C}, \text{ unless otherwise noted.})$  (Note 1)

| PARAMETER                     | SYMBOL | CONDITIONS          |        | MIN | TYP  | MAX | UNITS  |

|-------------------------------|--------|---------------------|--------|-----|------|-----|--------|

|                               |        | DS4106 at 106.25MHz | 100Hz  |     | -90  |     | dBC/Hz |

|                               |        |                     | 1kHz   |     | -112 |     |        |

|                               |        |                     | 10kHz  |     | -115 |     |        |

|                               |        |                     | 100kHz |     | -123 |     |        |

|                               |        |                     | 1MHz   |     | -142 |     |        |

|                               |        |                     | 10MHz  |     | -147 |     |        |

|                               | _      | DS4212 at 212.50MHz | 100Hz  |     | -82  |     |        |

|                               |        |                     | 1kHz   |     | -106 |     |        |

| Clock Output SSB Phase Noise  |        |                     | 10kHz  |     | -109 |     |        |

| Clock Output 33B Fliase Noise |        |                     | 100kHz |     | -117 |     |        |

|                               |        |                     | 1MHz   |     | -136 |     |        |

|                               |        |                     | 10MHz  |     | -141 |     |        |

|                               |        | DS4425 at 425.00MHz | 100Hz  |     | -76  |     |        |

|                               |        |                     | 1kHz   |     | -100 |     |        |

|                               |        |                     | 10kHz  |     | -103 |     |        |

|                               |        |                     | 100kHz |     | -111 |     |        |

|                               |        |                     | 1MHz   |     | -130 |     |        |

|                               |        |                     | 10MHz  |     | -135 |     |        |

- **Note 1:** Limits at -40°C are guaranteed by design and are not production tested.

- Note 2: Voltage referenced to ground.

- Note 3: Outputs are enabled and unloaded.

- Note 4: When the LVPECL output is disabled, the typical output off current is < 100μA for nominal LVPECL signal levels at the output.

- **Note 5:** AC parameters are guaranteed by design and characterization.

- Note 6: Including oscillator startup time and PLL acquisition time, measured after VCC reaches 3.0V from power-on.

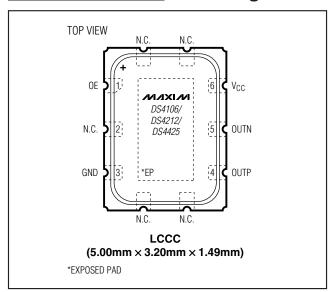

### **Pin Description**

| PIN     | NAME | FUNCTION                                                                                                                                                                                                                                                                                                                         |

|---------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | OE   | Output Enable. On-chip pullup resistor. Connect OE to logic-high, V <sub>CC</sub> , or leave open to enable the output clock. Connect OE to logic-low or GND to disable the output clock. The LVPECL output clock is set to high impedance when disabled. The LVDS output clock is latched to a differential high when disabled. |

| 2, 7–10 | N.C. | No Connection                                                                                                                                                                                                                                                                                                                    |

| 3       | GND  | Ground                                                                                                                                                                                                                                                                                                                           |

| 4       | OUTP | Positive Clock Output, LVPECL or LVDS                                                                                                                                                                                                                                                                                            |

| 5       | OUTN | Negative Clock Output, LVPECL or LVDS                                                                                                                                                                                                                                                                                            |

| 6       | Vcc  | +3.3V Supply                                                                                                                                                                                                                                                                                                                     |

| _       | EP   | Exposed Paddle. The exposed pad must be used for thermal relief. This pad can be connected to ground.                                                                                                                                                                                                                            |

### **Detailed Description**

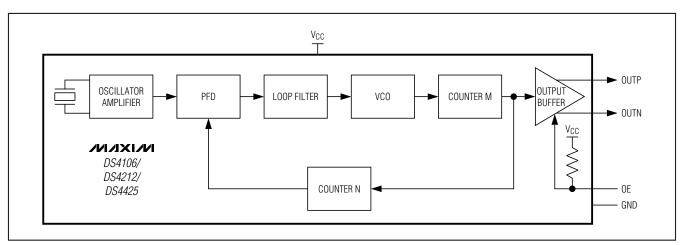

The DS4106/DS4212/DS4425 combine a crystal and an IC to form a precision clock. Figure 1 shows a functional diagram of the devices. The IC consists of a crystal oscillator, a low-noise PLL, selectable clock-divider circuitry, and an output buffer. The PLL consists of a digital phase/frequency detector (PFD) and low-jitter generation VCO. The VCO signal is scaled by a clock-divider circuit and applied to the output buffer.

#### **Output Drivers**

All devices are available with either LVPECL (DS4106A/DS4212A/DS4425A) or LVDS (DS4106B/DS4212B/DS4425B) output buffers. When not needed, the output buffers can be disabled. When disabled, the LVPECL output buffer goes to a high-impedance state. However, the LVDS outputs go to a differential logic one (OUTP latched high and OUTN latched low) when the outputs are disabled.

### **Additional Information**

For more available frequencies, refer to the DS4125 data sheet at **www.maxim-ic.com/DS4125**.

Figure 1. Functional Diagram

Figure 2. LVDS Level Definitions

### **Selector Guide**

| PART              | OUTPUTS | FREQUENCY (MHz) | TOP MARK |

|-------------------|---------|-----------------|----------|

| <b>DS4106</b> AN+ | LVPECL  | 106.25          | 06A      |

| DS4106BN+         | LVDS    | 106.25          | 06B      |

| <b>DS4212</b> AN+ | LVPECL  | 212.50          | 12A      |

| DS4212BN+         | LVDS    | 212.50          | 12B      |

| <b>DS4425</b> AN+ | LVPECL  | 425.00          | 42A      |

| DS4425BN+         | LVDS    | 425.00          | 42B      |

<sup>+</sup>Denotes a lead-free package. The lead finish is JESD97 category e4 (Au over Ni) and is compatible with both lead-based and lead-free soldering processes.

NIXI/N \_\_\_\_\_\_

### **Pin Configuration**

### Thermal Information

| THET | A-JA (°C/W) |

|------|-------------|

|      | 90          |

### **Package Information**

(For the latest package outline information go to <a href="https://www.maxim-ic.com/DallasPackInfo">www.maxim-ic.com/DallasPackInfo</a>.)

| PACKAGE TYPE | DOCUMENT NO. |

|--------------|--------------|

| 10 LCCC      | 56-G5032-002 |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.