# Advance Data Sheet March 1997

# microelectronics group

# L8575 Dual-Resistive, Low-Cost Subscriber Line Interface Circuit (SLIC)

# Features

- Two channels in a single package

- Serial data interface

- Per-channel powerdown

- Low standby power (≤65 mW per channel)

- Integrated protection

- No external protection device required

- Battery noise cancellation

- Switchhook detector

- Ring-trip detector

- Switchhook and ring-trip detector self-test

- Fault detector

- Zero ring voltage cross detection

- Three relay drivers per channel

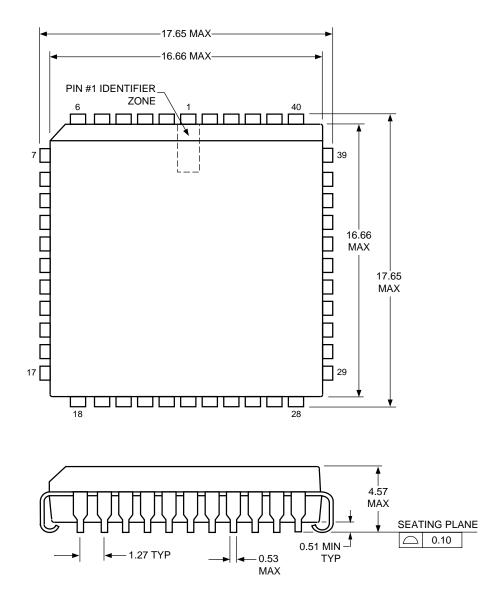

- 44-pin, surface-mount, plastic package (PLCC)

# Description

The L8575 is a dual-resistive, low-cost subscriber line interface circuit (SLIC) that is optimized to meet both ITU-T recommendations and LSSGR requirements for 600  $\Omega$ /900  $\Omega$  resistive and complex impedance termination applications. It interfaces the low-voltage circuits on an analog line card to the Tip and Ring of two subscriber loops. The L8575 does not supply dc current to the subscriber loops—external resistors are used for this purpose. The device is built using a 90 V complementary bipolar (CBIC) process and is available in a 44-pin PLCC package.

# **Table of Contents**

#### Contents

# Page

| Features                                       | 1    |

|------------------------------------------------|------|

| Description                                    | 1    |

| Preliminary Pin Information                    | 5    |

| Absolute Maximum Ratings (@ TA = 25 °C)        |      |

| Electrical Characteristics                     |      |

| Relay Drivers                                  | . 11 |

| Transmission                                   |      |

| Serial Interface and Logic                     | . 14 |

| Applications                                   |      |

| General                                        | . 16 |

| Resistor Module                                | . 16 |

| Protection                                     | . 18 |

| Tip/Ring Drivers                               | . 20 |

| Receive Interface                              | . 20 |

| Transmit Interface                             | . 20 |

| Battery Noise Cancellation                     | . 20 |

| On-Hook Transmission                           | . 21 |

| Self-Test                                      | . 21 |

| Serial Data Interface                          | . 21 |

| Operating States                               |      |

| Active State                                   | . 24 |

| Test State                                     | . 24 |

| Powerdown State with Relay Driver RDD Operated | . 24 |

| Powerdown State                                |      |

| Ringing State (D2 = 1)                         | . 24 |

| Supervision                                    | . 25 |

| Off-Hook Detection                             | . 25 |

| Ring-Trip Threshold                            |      |

| Ring-Trip Requirements                         |      |

| Fault Detection                                |      |

| Zero Voltage Current Cross                     |      |

| Relay Drivers                                  |      |

| dc Characteristics                             |      |

| I/V Characteristics                            |      |

| Loop Length                                    |      |

| ac Design                                      |      |

| Codec Features and Selection Summary           |      |

| Design Equations                               |      |

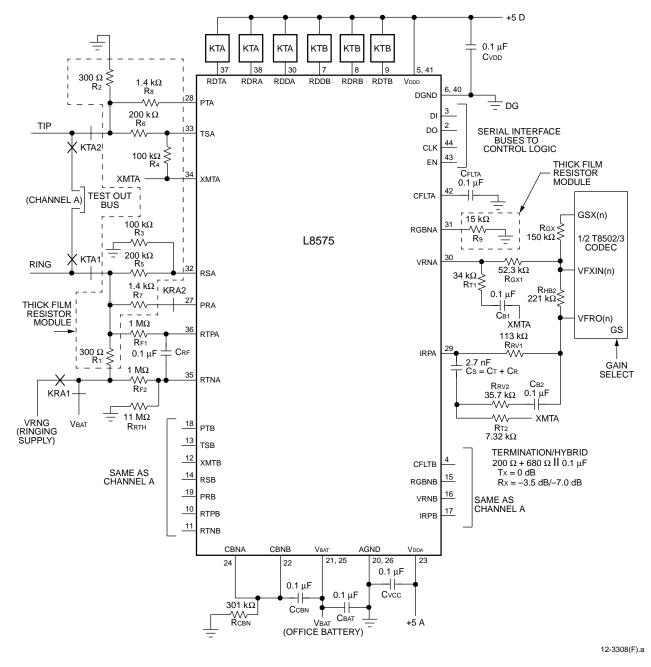

| Application Diagram                            |      |

| Outline Diagram                                |      |

| 44-Pin PLCC                                    |      |

| Ordering Information                           | 36   |

# Table of Contents (continued)

#### **Tables**

| Table 1. Pin Descriptions         Table 2. Operating Conditions and Powering                   | 5  |

|------------------------------------------------------------------------------------------------|----|

| Table 3. Battery Feed, Switchhook Detectors (LCA and LCB), and Fault Detectors (FLTA and FLTB) |    |

| Table 4. Ring-Trip Detectors (RTA, RTB, RZA, and RZB)                                          |    |

| Table 5. Relay Drivers (RDRA, RDTA, RDRB, RDTB, RDDA, and RDDB)                                |    |

| Table 6. Analog Signal Pins                                                                    |    |

| Table 7. Transmission Characteristics                                                          | 13 |

| Table 8. Logic Inputs (CLK, EN, and DI) and Outputs (DO)                                       | 14 |

| Table 9. Timing Requirements for CLK, EN, DI, and DO                                           | 14 |

| Table 10. MMC* A31A8575AA Thick Film Resistor Module                                           |    |

| Table 11. Total Module Power Dissipation                                                       | 19 |

| Table 12. Truth Table for EN and CLK                                                           | 22 |

| Table 13. Output DATA Bit Definition                                                           | 22 |

| Table 14. Input DATA Bit Definition                                                            | 23 |

| Table 15. Truth Table for D1 and D0                                                            |    |

| Table 16. External Components Required                                                         | 33 |

## Figures

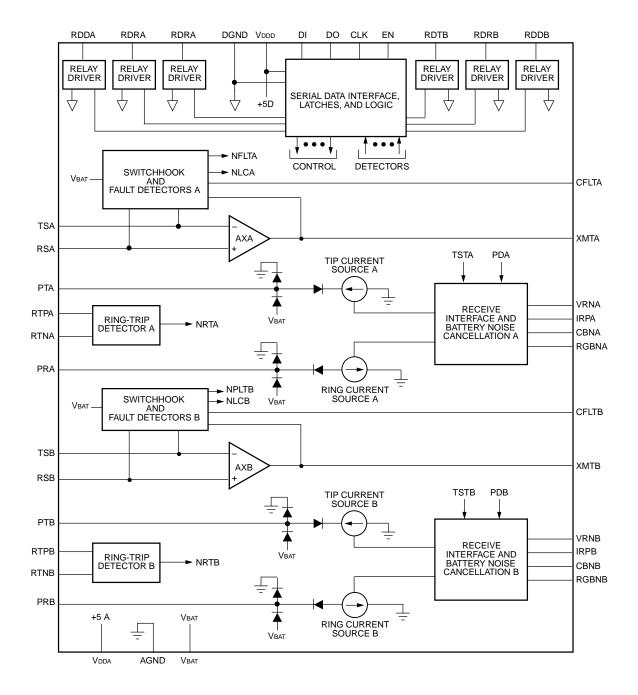

| Figure 1. Functional Diagram                                                               | 4  |

|--------------------------------------------------------------------------------------------|----|

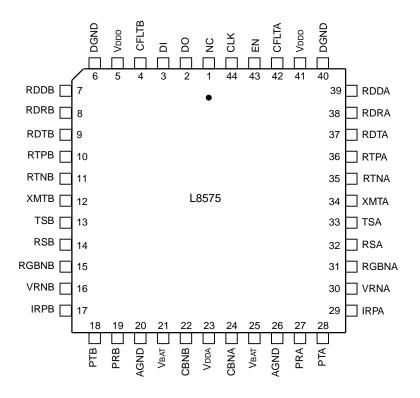

| Figure 2. 44-Pin PLCC Pinout                                                               |    |

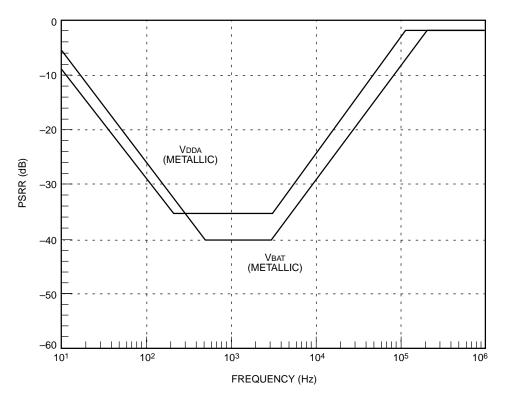

| Figure 3. Power Supply Rejection vs. Frequency Diagram                                     | 15 |

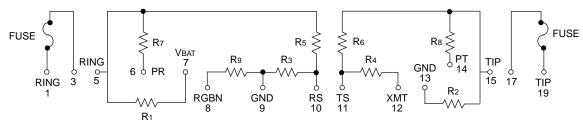

| Figure 4. L8575 SLIC Resistor Module                                                       | 17 |

| Figure 5. L8575 SLIC Dual-Resistive Matching Requirements                                  | 18 |

| Figure 6. Self-Test Mode Circuit                                                           | 21 |

| Figure 7. Timing Requirements for CLK, EN, DI, and DO                                      | 22 |

| Figure 8. Logic Diagram (Positive Logic; Flip-Flops Clocked on High-to-Low Transition)     | 23 |

| Figure 9. Ring-Trip Threshold                                                              | 25 |

| Figure 10. Ring-Trip Circuits                                                              |    |

| Figure 11. L8575 SLIC I/V Template                                                         | 27 |

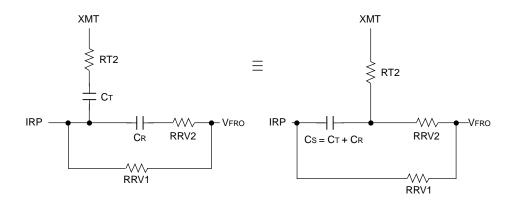

| Figure 12. Equivalent Complex Terminations                                                 | 29 |

| Figure 13. Initial ac Interface for Complex Termination Between L8575 SLIC and T7504 Codec | 30 |

| Figure 14. Revised ac Interface CT and CR Combined into a Single Capacitor Cs              | 31 |

| Figure 15. Addition of Resistor Rsc from XMT to IRP                                        | 32 |

| Figure 16. Typical Application Diagram with Blocking Capacitors (CB) Included              | 34 |

|                                                                                            |    |

\* MMC is a registered trademark of Microelectronic Modules Corporation.

### Page

#### Page

## Description (continued)

12-3304(F).ar1

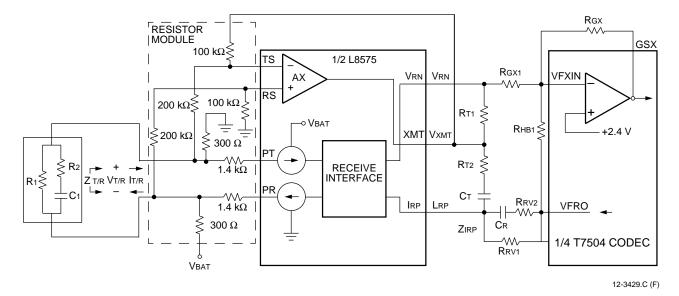

Figure 1. Functional Diagram

# **Preliminary Pin Information**

12-3364(F)

#### Figure 2. 44-Pin PLCC Pinout

#### **Table 1. Pin Descriptions**

| Pin | Symbol | Туре | Name/Function                                                                                                                                               |

|-----|--------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | NC     | —    | No Connect. Unused pin (no internal connection).                                                                                                            |

| 2   | DO     | 0    | <b>Serial Data Output.</b> Data in the internal 8-bit serial shift register is shifted out on this logic output with the clock signal on pin CLK.           |

| 3   | DI     | Ι    | <b>Serial Data Input.</b> Data on this logic input is shifted into the 8-bit serial shift register with the clock signal on pin CLK.                        |

| 4   | CFLTB  | I/O  | Fault Filter (Channel B). Connect a 0.1 $\mu$ F capacitor from CFLTB to AGND. This capacitor filters Tip/Ring transients from the channel B fault detector. |

| 5   | Vddd   | —    | 5 V Digital dc Supply. 5 V supply for logic and relay driver flyback diodes.                                                                                |

| 6   | DGND   | —    | Digital Ground. Ground for channel B relay drivers.                                                                                                         |

| 7   | RDDB   | 0    | Disconnect Relay Driver (Channel B). This output drives the external relay.                                                                                 |

| 8   | RDRB   | 0    | Ringing Relay Driver (Channel B). This output drives an external ringing relay.                                                                             |

| 9   | RDTB   | 0    | Test Relay Driver (Channel B). This output drives an external test relay.                                                                                   |

| 10  | RTPB   | I    | Ring-Trip Positive (Channel B). Positive sense input for the ring-trip detector.                                                                            |

## Preliminary Pin Information (continued)

Table 1. Pin Descriptions (continued)

| Pin | Symbol | mbol Type Name/Function |                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|-----|--------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 11  | RTNB   |                         | Ring-Trip Negative (Channel B). Negative sense input for the ring-trip detector.                                                                                                                                                                                                                      |  |  |  |  |

| 12  | XMTB   | 0                       | Transmit Signal Output (Channel B). Channel B transmit amplifier output.                                                                                                                                                                                                                              |  |  |  |  |

| 13  | TSB    | I                       | <b>Tip Sense (Channel B).</b> Negative input of channel B transmit op amp. Connect one high-<br>value resistor between TSB and the Tip of loop B and another high-value resistor between<br>TSB and XMTB.                                                                                             |  |  |  |  |

| 14  | RSB    | Ι                       | <b>Ring Sense (Channel B).</b> Positive input of channel B transmit op amp. Connect one high-<br>value resistor between RSB and the Ring of loop B and another high-value resistor between<br>RSB and AGND.                                                                                           |  |  |  |  |

| 15  | RGBNB  | Ι                       | <b>Battery Noise Gain Resistor (Channel B).</b> The current flowing out of PRB is 50 times the current flowing into RGBNB. Connect a resistor from RGBNB to AGND to set the gain of the channel B battery noise cancellation circuit.                                                                 |  |  |  |  |

| 16  | VRNB   | Ι                       | <b>Receive Voltage Negative Input (Channel B).</b> The differential current flowing from PTB to PRB is –200 times the voltage applied to VRNB, divided by the impedance connected between IRPB and AGND.                                                                                              |  |  |  |  |

| 17  | IRPB   | Ι                       | <b>Receive Current Positive Input (Channel B).</b> The differential current flowing from PTB to PRB is 200 times the current flowing into IRPB.                                                                                                                                                       |  |  |  |  |

| 18  | PTB    | 0                       | <b>Protected Tip (Channel B).</b> Output of the Tip current drive amplifier B. Connect PTB to the Tip of loop B through an overvoltage protection resistor (1.4 k $\Omega$ minimum).                                                                                                                  |  |  |  |  |

| 19  | PRB    | 0                       | <b>rotected Ring (Channel B).</b> Output of the Ring current drive amplifier B. Connect PRB to e Ring of loop B through an overvoltage protection resistor (1.4 k $\Omega$ minimum).                                                                                                                  |  |  |  |  |

| 20  | AGND   | —                       | Analog Signal Ground. Signal ground for channel B.                                                                                                                                                                                                                                                    |  |  |  |  |

| 21  | Vbat   | _                       | Office Battery Supply. Negative office battery supply for channel B.                                                                                                                                                                                                                                  |  |  |  |  |

| 22  | CBNB   | Ι                       | <b>Battery Noise Capacitor (Channel B).</b> The current flowing out of PRB is –50 times the voltage applied to CBNB, divided by the impedance connected between RGBNB and AGND. Couple V <sub>BAT</sub> to CBNB through a high-pass filter to eliminate battery noise from the Tip/Ring of channel B. |  |  |  |  |

| 23  | Vdda   | _                       | 5 V Analog dc Supply.                                                                                                                                                                                                                                                                                 |  |  |  |  |

| 24  | CBNA   | Ι                       | <b>Battery Noise Capacitor (Channel A).</b> The current flowing out of PRA is –50 times the voltage applied to CBNA, divided by the impedance connected between RGBNA and AGND. Couple VBAT to CBNA through a high-pass filter to eliminate battery noise from the Tip/Ring of channel A.             |  |  |  |  |

| 25  | VBAT   | —                       | Office Battery Supply. Negative office battery supply for channel A.                                                                                                                                                                                                                                  |  |  |  |  |

| 26  | AGND   | _                       | Analog Signal Ground. Signal ground for channel A.                                                                                                                                                                                                                                                    |  |  |  |  |

| 27  | PRA    | 0                       | <b>Protected Ring (Channel A).</b> Output of the Ring current drive amplifier A. Connect PRA to the Ring of loop A through an overvoltage protection resistor (1.4 k $\Omega$ minimum).                                                                                                               |  |  |  |  |

| 28  | PTA    | 0                       | <b>Protected Tip (Channel A).</b> Output of the Tip current drive amplifier A. Connect PTA to the Tip of loop A through an overvoltage protection resistor (1.4 k $\Omega$ minimum).                                                                                                                  |  |  |  |  |

| 29  | IRPA   | I                       | <b>Receive Current Positive Input (Channel A).</b> The differential current flowing from PTA to PRA is 200 times the current flowing into IRPA.                                                                                                                                                       |  |  |  |  |

| 30  | VRNA   | I                       | <b>Receive Voltage Negative Input (Channel A).</b> The differential current flowing from PTA to PRA is –200 times the voltage applied to VRNA, divided by the impedance connected between IRPA and AGND.                                                                                              |  |  |  |  |

# Preliminary Pin Information (continued)

| Table 1. | Pin D | Descriptions | (continued) |

|----------|-------|--------------|-------------|

|----------|-------|--------------|-------------|

| Pin | Symbol | Туре | Name/Function                                                                                                                                                                                                                                                                                                              |  |  |  |

|-----|--------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 31  | RGBNA  | I    | <b>Battery Noise Gain Resistor (Channel A).</b> The current flowing out of PRA is 50 times the current flowing into RGBNA. Connect a resistor from RGBNA to AGND to set the gain of the channel A battery noise cancellation circuit.                                                                                      |  |  |  |

| 32  | RSA    | Ι    | <b>Ring Sense (Channel A).</b> Positive input of channel A transmit op amp. Connect one high-value resistor between RSA and the Ring of loop A and another high-value resistor between RSA and AGND.                                                                                                                       |  |  |  |

| 33  | TSA    | I    | <b>Tip Sense (Channel A).</b> Negative input of channel A transmit op amp. Connect one high-value resistor between TSA and the Tip of loop A and another high-value resistor between TSA and XMTA.                                                                                                                         |  |  |  |

| 34  | XMTA   | 0    | Transmit Signal Output (Channel A). Channel A transmit amplifier output.                                                                                                                                                                                                                                                   |  |  |  |

| 35  | RTNA   | I    | ng-Trip Negative (Channel A). Negative sense input for the ring-trip detector.                                                                                                                                                                                                                                             |  |  |  |

| 36  | RTPA   | I    | Ring-Trip Positive (Channel A). Positive sense input for the ring-trip detector.                                                                                                                                                                                                                                           |  |  |  |

| 37  | RDTA   | 0    | Test Relay Driver (Channel A). This output drives an external test relay.                                                                                                                                                                                                                                                  |  |  |  |

| 38  | RDRA   | 0    | Ringing Relay Driver (Channel A). This output drives the external ringing relay.                                                                                                                                                                                                                                           |  |  |  |

| 39  | RDDA   | 0    | Disconnect Relay Driver (Channel A). This output drives an external relay.                                                                                                                                                                                                                                                 |  |  |  |

| 40  | DGND   | —    | Digital Ground. Ground for channel A relay drivers.                                                                                                                                                                                                                                                                        |  |  |  |

| 41  | Vddd   | —    | 5 V Digital dc Supply. 5 V supply for logic and relay driver flyback diodes.                                                                                                                                                                                                                                               |  |  |  |

| 42  | CFLTA  | I/O  | Fault Filter (Channel A). Connect a 0.1 $\mu$ F capacitor from CFLTA to AGND. This capacitor filters Tip/Ring transients from the channel A fault detector.                                                                                                                                                                |  |  |  |

| 43  | EN     | Ι    | <b>Enable.</b> A high-to-low transition on this logic input latches the data in the 8-bit serial shift register into the output latches. The logic level of EN also controls which data is shifted into the 8-bit serial shift register (refer to CLK pin description).                                                    |  |  |  |

| 44  | CLK    | Ι    | <b>Clock.</b> When the enable input (EN) is high, a low-to-high transition on this logic input shifts data at the data input pin (DI) into the 8-bit serial shift register. When the enable input (EN) is low, a low-to-high transition latches the states of the internal detectors into the 8-bit serial shift register. |  |  |  |

## Absolute Maximum Ratings (@ TA = 25 °C)

Stresses in excess of the absolute maximum ratings can cause permanent damage to the device. These are absolute stress ratings only. Functional operation of the device is not implied at these or any other conditions in excess of those given in the operational sections of this data sheet. Exposure to absolute maximum ratings for extended periods can adversely affect device reliability.

| Parameter                                               | Symbol | Min  | Value | Max        | Unit |

|---------------------------------------------------------|--------|------|-------|------------|------|

| 5 V Analog dc Supply                                    | Vdda   | -0.5 |       | +7.0       | V    |

| 5 V Digital dc Supply                                   | Vddd   | -0.5 | _     | +7.0       | V    |

| Office Battery Supply                                   | Vbat   | -65  |       | +0.5       | V    |

| Logic Input Voltage                                     | —      | -0.5 | _     | VDDD + 0.5 | V    |

| Logic Input Clamp Diode Current, per Pin                |        | _    | ±20   | —          | mA   |

| Logic Output Voltage                                    | —      | -0.5 | —     | VDDD + 0.5 | V    |

| Logic Output Current, per Pin (excluding relay drivers) |        | _    | ±35   | —          | mA   |

| Maximum Junction Temperature                            | —      | —    | 150   | —          | °C   |

| Operating Temperature Range                             | —      | -40  | _     | +125       | °C   |

| Storage Temperature Range                               | Tstg   | -40  |       | +125       | °C   |

| Relative Humidity Range                                 | —      | 5    | —     | 95         | %    |

| Ground Potential Difference (DGND to AGND)              |        | +0.5 |       | -0.5       | V    |

Notes:

Analog and battery voltages are referenced to AGND; digital (logic) voltages are referenced to DGND.

The IC can be damaged unless all ground connections are applied before, and removed after, all other connections. Furthermore, when powering the device, the user must guarantee that no external potential creates a voltage on any pin of the device that exceeds the device ratings. Some of the known examples of conditions that cause such potentials during powering are (1) an inductor connected to Tip and Ring that can force an overvoltage on VBAT through external components if the VBAT connection chatters, and (2) inductance in the VBAT lead that could resonate with the VBAT filter capacitor to cause a destructive overvoltage.

# **Electrical Characteristics**

Generally, minimum and maximum values are testing requirements. However, some parameters may not be tested in production because they are guaranteed by design and device characterization. Typical values reflect the design center or nominal value of the parameter; they are for information only and are not a requirement. Minimum and maximum values apply across the entire temperature range ( $-40 \degree C$  to  $+85 \degree C$ ) and entire battery range ( $-42 \degree V$  to  $-58 \degree V$ ). Unless otherwise specified, typical values are defined as 25 °C,  $V_{DDA} = 5 \degree V$ ,  $V_{BAT} = -48 \degree V$ . Positive currents flow into the device.

| Table 2. | Operating | Conditions | and Powering |

|----------|-----------|------------|--------------|

|----------|-----------|------------|--------------|

| Parameter                                                                                                  | Min  | Тур      | Max             | Unit       |

|------------------------------------------------------------------------------------------------------------|------|----------|-----------------|------------|

| Temperature Range                                                                                          | -40  | —        | 85              | °C         |

| Humidity Range                                                                                             | 5    | _        | 95 <sup>1</sup> | %RH        |

| Supply Voltage:                                                                                            |      |          |                 |            |

| VDDA                                                                                                       | 4.75 | _        | 5.5             | V          |

| Vddd                                                                                                       | 4.75 |          | 5.5             | V          |

| VBAT                                                                                                       | -42  | -48      | -58             | V          |

| Vdda – Vddd                                                                                                | -    |          | ±0.5            | V          |

| Supply Currents (both channels active):<br>IVDDA + IVDDD (5 V)<br>IVBAT (-48 V) <sup>2</sup>               | _    | _        | 19.0<br>–27.5   | mA<br>mA   |

| Supply Currents (both channels powerdown):<br>IVDDA + IVDDD (5 V)<br>IVBAT (-48 V) <sup>2</sup>            | _    | _        | 18.0<br>2.0     | mA<br>mA   |

| Total Power Dissipation (5 V; –48 V) <sup>3</sup> :<br>Active (both channels)<br>Powerdown (both channels) |      | _        | 1.40<br>185     | W<br>mW    |

| Power-supply Rejection <sup>4, 5</sup> (50 mVrms ripple):<br>Tip/Ring and XMT                              |      | Refer to | Figure 3.       |            |

| Thermal <sup>5</sup> :<br>Thermal Resistance (still air)<br>Operating Tjc                                  |      |          | 47<br>155       | °C/W<br>°C |

1. Not to exceed 26 grams of water per kilogram of dry air.

2. Includes VBAT current through the external dc feed resistors, assuming the loop is open.

3. Includes power dissipation in the external dc feed resistors per application diagram, assuming the loop is open.

4. VBAT power supply rejection depends on the battery noise cancellation circuit. The performance stated here applies only during the active state and assumes proper battery noise cancellation, i.e., a high-pass filter from VBAT to CBN and a resistor from RGBN to AGND which is 50 times the dc feed resistor connecting VBAT to Ring (refer to the application diagram).

5. This parameter is not tested in production. It is guaranteed by design and device characterization.

#### Table 3. Battery Feed, Switchhook Detectors (LCA and LCB), and Fault Detectors (FLTA and FLTB)

| Parameter                                                                                                                                                                                                                                                                                                                                                        | Min                      | Тур           | Max                      | Unit               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|---------------|--------------------------|--------------------|

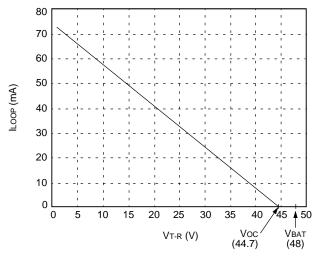

| Loop Resistance Range <sup>1</sup> :<br>(3.17 dBm overload into 600 Ω)<br>ILOOP = 18 mA at VBAT = -48 V                                                                                                                                                                                                                                                          | 1800                     |               |                          | Ω                  |

| Longitudinal Current Capability per Wire                                                                                                                                                                                                                                                                                                                         | 8.5                      | _             |                          | mArms              |

| Switchhook Detector Loop Resistance <sup>2</sup> :<br>Off-hook (LC = 1)<br>On-hook (LC = 0)                                                                                                                                                                                                                                                                      | 4800                     | 4000<br>      | 3200<br>—                | Ω<br>Ω<br>Ω        |

| $ \begin{array}{l} \mbox{Fault Detector}^{2,\ 3}: \\  V_{\text{TIP}}  \ or \  V_{\text{RING}} - V_{\text{BAT}}  \\ \ No \ Fault \ (FLT = 0) \\ \ Fault \ (FLT = 1) \\ \ Detection \ Delay \ t_{\text{DET}} \ (no \ fault \ to \ fault; \ CFLT = 0.1 \ \mu\text{F}) \\ \ Release \ Delay \ (fault \ to \ no \ fault; \ CFLT = 0.1 \ \mu\text{F}) \\ \end{array} $ | <br>39<br>10<br>1.6 tdet | 36<br>36<br>— | 33<br><br>30<br>2.5 tdet | V<br>V<br>ms<br>ms |

1. Assumes 2 x 300  $\Omega$  external dc feed resistors.

2. Detector values are independent of office battery and are valid over the entire range of VBAT.

3. Fault voltage is defined as the absolute value of the dc voltage across either dc feed resistor. If the voltage across either feed resistor exceeds this value, a fault is determined to be present. FLT is forced to a 0 when D2 = 1 (ringing state).

#### Table 4. Ring-Trip Detectors (RTA, RTB, RZA, and RZB)

| Parameter                                                                                                                      | Min               | Тур    | Max             | Unit            |

|--------------------------------------------------------------------------------------------------------------------------------|-------------------|--------|-----------------|-----------------|

| Ringing Source <sup>1</sup> :<br>Frequency ( <i>f</i> )<br>dc Voltage<br>ac Voltage                                            | 19<br>–39.5<br>60 | 20<br> | 28<br>57<br>105 | Hz<br>V<br>Vrms |

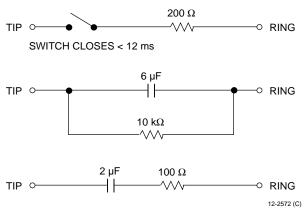

| Ring Trip <sup>2, 3</sup> (RT = 1):<br>Loop Resistance<br>Trip Time ( $f$ = 20 Hz)<br>RT Valid                                 | 2000<br>          |        | <br>200<br>80   | Ω<br>ms<br>ms   |

| Ringing Source Zero Crossing (referenced to VBAT/2):<br>Ringing Voltage Positive (RZ = 1)<br>Ringing Voltage Negative (RZ = 0) | 3Vbat/4           |        | <br>Vbat/4      | V<br>V          |

1. The ringing source consists of the ac and dc voltages added together (battery-backed ringing); the ringing return is ground.

2. RT must also indicate ring-trip when the ac ringing voltage is absent (<5 Vrms) from the ringing source.

3. Pretrip: Ringing must not be tripped by a 10 k $\Omega$  resistor in parallel with an 8  $\mu$ F capacitor applied across Tip and Ring.

### **Relay Drivers**

The relay drivers operate using the VDDD supply. When VDDD is first applied to the device, the relay drivers must power up and remain in the off-state until the SLIC is configured via the serial data interface. The table below summarizes their parameter requirements.

#### Table 5. Relay Drivers (RDRA, RDTA, RDRB, RDTB, RDDA, and RDDB)

| Parameter <sup>1</sup>                 | Symbol | Min        | Мах        | Unit |

|----------------------------------------|--------|------------|------------|------|

| Off-state Output Current (Vout = VDDD) | IOFF   | —          | ±10        | μΑ   |

| On-state Output Voltage (Iout = 40 mA) | Von    | 0          | 0.60       | V    |

| On-state Output Voltage (Iout = 20 mA) | Von    | 0          | 0.40       | V    |

| Clamp Diode Reverse Current (Vout = 0) | IR     | —          | ±10        | μΑ   |

| Clamp Diode On Voltage (Iout = 80 mA)  | Voc    | VDDD + 0.5 | Vddd + 3.0 | V    |

| Turn-on Time <sup>2</sup>              | ton    | —          | 10         | μs   |

| Turn-off Time <sup>2</sup>             | toff   | —          | 10         | μs   |

1. Unless otherwise specified, all logic voltages are referenced to DGND.

2. This parameter is not tested in production. It is guaranteed by design and device characterization.

#### Table 6. Analog Signal Pins

| Parameter                                      | Min      | Тур  | Max      | Unit  |

|------------------------------------------------|----------|------|----------|-------|

| PTA, PTB, PRA, and PRB:                        |          |      |          |       |

| Surge Current (from external source):          |          |      |          |       |

| Continuous                                     | _        | _    | ±50      | mAdc  |

| 1 ms Exponential Pulse (50 repetitions)        | _        | _    | ±750     | mA    |

| 1 second, 60 Hz (60 repetitions)               | _        | _    | ±175     | mArms |

| 10 $\mu$ s Rectangular Pulse (10 repetitions)  | _        | _    | ±1.25    | A     |

| Output Drive (PTA and PTB):                    |          |      |          |       |

| Drive Current (sink only)                      | 0.1      | _    | 15       | mA    |

| Voltage Swing (lout = 15 mA)                   | VBAT + 4 | _    | AGND     | V     |

| dc Bias Current (active state only)            | 5.3      | 5.6  | 5.9      | mA    |

| Output Drive (PRA and PRB):                    |          |      |          |       |

| Drive Current (source only)                    | -15      | _    | -0.1     | mA    |

| Voltage Swing (lout = 15 mA)                   | VBAT     | _    | AGND – 4 | V     |

| dc Bias Current (active state only)            | -5.3     | -5.6 | -5.9     | mA    |

| Output Impedance (60 Hz—3.4 kHz) <sup>1</sup>  | 1        | _    | _        | MΩ    |

| Output Load Resistance (dc or ac) <sup>1</sup> | 0        | —    | 100      | kΩ    |

1. This parameter is not tested in production. It is guaranteed by design and device characterization.

#### Relay Drivers (continued)

#### Table 6. Analog Signal Pins (continued)

| Parameter                                                          | Min       | Тур | Max  | Unit |

|--------------------------------------------------------------------|-----------|-----|------|------|

| XMTA and XMTB:                                                     |           |     |      |      |

| Output Drive Current                                               | ±3        | _   | _    | mA   |

| Output Voltage Swing (3 mA load):                                  |           |     |      |      |

| Maximum                                                            | VBAT      | _   | Vdda | V    |

| Minimum                                                            | VBAT + 10 |     | +2.5 | V    |

| Output Short-circuit Current <sup>2</sup>                          | _         | _   | ±30  | mA   |

| Output Impedance (60 Hz—3.4 kHz)                                   | _         | —   | 10   | Ω    |

| Output Load dc Resistance                                          | 20        | _   |      | kΩ   |

| Output Load ac Impedance <sup>1</sup>                              | 2         |     |      | kΩ   |

| Output Load Capacitance <sup>1</sup>                               | _         | —   | 50   | pF   |

| VRNA and VRNB:                                                     |           |     |      |      |

| Input Voltage Range                                                | -1.75     | —   | 3.5  | V    |

| Input Bias Current                                                 | _         | —   | ±1   | μA   |

| Input Impedance <sup>1</sup>                                       | 20        | —   | —    | MΩ   |

| IRPA and IRPB:                                                     |           |     |      |      |

| Input Offset Voltage (to respective VRN)                           | _         | —   | ±10  | mV   |

| Input Impedance                                                    | _         | —   | 5    | Ω    |

| CBNA and CBNB:                                                     |           |     |      |      |

| Input Voltage Range                                                | -1.75     | —   | 3.5  | V    |

| Input Bias Current                                                 | _         | —   | ±250 | nA   |

| Input Impedance                                                    | 50        |     |      | MΩ   |

| RGBNA and RGBNB:                                                   |           |     |      |      |

| Input Offset Voltage (to respective CBN)                           | _         | —   | ±10  | mV   |

| Input Impedance                                                    | — —       | —   | 5    | Ω    |

| TSA, TSB, RSA, and RSB:                                            |           |     |      |      |

| Surge Current (from external source)                               | —         | —   | ±25  | mAdc |

| Input Voltage Range                                                | Vbat + 3  | —   | AGND | V    |

| Input Bias Current                                                 | _         | —   | ±1   | μA   |

| Differential Input Impedance <sup>1</sup>                          | 50        | —   | —    | kΩ   |

| Common-mode Input Impedance <sup>1</sup>                           | 50        | —   | _    | MΩ   |

| External Capacitance (67 k $\Omega$ source impedance) <sup>1</sup> |           |     | 10   | pF   |

1. This parameter is not tested in production. It is guaranteed by design and device characterization.

2.A VBAT or ground short on XMTA or XMTB will not cause a device failure.

#### Transmission

Transmit direction is Tip/Ring to XMT. Receive direction is IRP/VRN to Tip/Ring.

#### **Table 7. Transmission Characteristics**

| Parameter                                                               | Min    | Тур      | Max    | Unit   |

|-------------------------------------------------------------------------|--------|----------|--------|--------|

| Longitudinal Balance (IEEE <sup>1</sup> Std. 455—1976) <sup>2</sup> :   |        |          |        |        |

| 50 Hz—1 kHz                                                             | 54     | 70       | _      | dB     |

| 1 kHz—3 kHz                                                             | 50     | 66       | —      | dB     |

| Metallic to Longitudinal Balance <sup>2</sup> :                         |        |          |        |        |

| 200 Hz—4 kHz                                                            | 30     |          | _      | dB     |

| RFI Rejection <sup>3</sup> :                                            |        |          |        |        |

| (0.5 Vrms, 50 $\Omega$ source, 30% AM Mod. 1 kHz)                       |        |          |        |        |

| 500 kHz—10 MHz                                                          | _      |          | -65    | dBV    |

| 10 MHz—100 MHz                                                          | —      | —        | -45    | dBV    |

| Tip/Ring Signal Level                                                   |        |          | 3.17   | dBm    |

| ac Termination Impedance <sup>4</sup>                                   | _      | 600      | —      | Ω      |

| Total Harmonic Distortion (200 Hz—4 kHz) <sup>3</sup>                   | _      | _        | 0.3    | %      |

| Transmit Gain ( $f = 1 \text{ kHz}$ ) <sup>5</sup> :                    |        |          |        |        |

| Tip/Ring to XMT                                                         | -0.486 | -0.500   | -0.514 | _      |

| Receive Gain ( $f = 1$ kHz):                                            |        |          |        |        |

| IRP Current to Differential Current Flowing from PT to PR               | 195    | 200      | 205    | _      |

| VRV to IRP                                                              | 0.995  | 1        | 1.005  | _      |

| CBN Gain ( $f = 1 \text{ kHz}$ ):                                       |        |          |        |        |

| 1 RGBN Current to Current Flowing                                       | -49.5  | -50      | -50.5  |        |

| CBN to RGBN                                                             | 0.995  | 1        | 1.005  |        |

| Gain vs. Frequency (transmit & receive; 1 kHz reference) <sup>3</sup> : |        |          |        |        |

| 200 Hz—3.4 kHz                                                          | -0.1   | 0        | 0.1    | dB     |

| Gain vs. Level (transmit & receive; 0 dBV reference) <sup>3</sup> :     |        |          |        |        |

| –50 dB to +3 dB                                                         | -0.05  | 0        | 0.05   | dB     |

| Interchannel Crosstalk <sup>3</sup> :                                   |        |          |        |        |

| 200 Hz—3.4 kHz                                                          | _      |          | 77     | dB     |

| Idle-channel Noise (Tip/Ring; 600 $\Omega$ termination):                |        |          |        |        |

| Psophometric <sup>3</sup>                                               | -      | —        | -77    | dBmp   |

| C-message                                                               | -      | —        | 12     | dBrnC  |

| 3 kHz flat <sup>3</sup>                                                 | -      | <u> </u> | 20     | dBrn   |

| Idle-channel Noise (XMT; 600 $\Omega$ termination):                     |        |          |        |        |

| Psophometric <sup>3</sup>                                               | -      | -        | -77    | dBmp0  |

| C-message                                                               | -      | -        | 12     | dBrnC0 |

| 3 kHz flat <sup>3</sup>                                                 |        |          | 20     | dBrn0  |

1. IEEE is a registered trademark of The Institute of Electrical and Electronics Engineers, Inc.

2. Assumes ideal external components.

3. This parameter is not tested in production. It is guaranteed by design and device characterization.

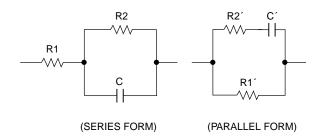

4. Transmission characteristics are specified assuming a 600 Ω resistive termination; however, feedback using external components allows the user to adjust the termination impedance from the intrinsic 600 Ω of the feed resistors to most ITU-T recommended complex termination impedances.

5. Measured with the L8575 SLIC connected per application diagram with ideal external components.

#### Serial Interface and Logic

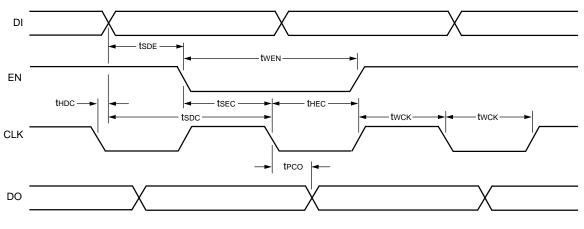

The tables below summarize the parameter and timing requirements for logic inputs CLK, EN, DI, and DO.

#### Table 8. Logic Inputs (CLK, EN, and DI) and Outputs (DO)

| Parameter <sup>1</sup>                           | Symbol | Min        | Max  | Unit |

|--------------------------------------------------|--------|------------|------|------|

| High-level Input Voltage                         | Viн    | 2          | Vddd | V    |

| Low-level Input Voltage                          | VIL    | 0          | 0.8  | V    |

| Input Bias Current (high and low)                | lin    | —          | ±50  | μΑ   |

| High-level Output Voltage (Iout = $-100 \mu A$ ) | Voн    | Vddd - 1.5 | Vddd | V    |

| Low-level Output Voltage (Iout = 180 µA)         | Vol    | 0          | 0.4  | V    |

| Output Short-circuit Current (Vout = VDDD)       | loss   | 1          | 35   | mA   |

| Output Load Capacitance <sup>2</sup>             | Col    | 0          | 50   | pF   |

1. Unless otherwise specified, all logic voltages are referenced to DGND.

2. This parameter is not tested in production. It is guaranteed by design and device characterization.

#### Table 9. Timing Requirements for CLK, EN, DI, and DO

| Parameter <sup>1</sup>                                       | Symbol       | Min | Max  | Unit |

|--------------------------------------------------------------|--------------|-----|------|------|

| Input Rise and Fall Time, CLK & EN (10% to 90%) <sup>2</sup> | tR, tF       | 0   | 70   | ns   |

| Maximum Input Capacitance <sup>2</sup>                       | CIN          | —   | 5    | pF   |

| Maximum CLK Frequency (50% duty cycle)                       | fмах         |     | 1.25 | MHz  |

| Propagation Delay, CLK to DO <sup>2</sup>                    | tPCO         | 0   | 350  | ns   |

| Propagation Delay, EN to RD Outputs <sup>2</sup>             | <b>t</b> PCR | 0   | 10   | μs   |

| Minimum Setup Time from DI to CLK <sup>2</sup>               | tspc         | 150 | _    | ns   |

| Minimum Setup Time from DI to EN <sup>2</sup>                | tsde         | 150 | _    | ns   |

| Minimum Setup Time from EN to CLK <sup>2</sup>               | tsec         | 150 | _    | ns   |

| Minimum Hold Time from CLK to DI <sup>2</sup>                | thdc         | 50  | _    | ns   |

| Minimum Hold Time from EN to CLK <sup>2</sup>                | thec         | 50  |      | ns   |

| Minimum Pulse Width of CLK                                   | twcĸ         | 400 |      | ns   |

| Minimum Pulse Width of EN                                    | twen         | 800 |      | ns   |

1. Unless otherwise specified, all times are measured from the 50% point of logic transitions.

2. This parameter is not tested in production. It is guaranteed by design and device characterization.

## Serial Interface and Logic (continued)

12-3307(F)

Figure 3. Power Supply Rejection vs. Frequency Diagram

# Applications

## General

The L8575 is a dual (channels A and B) subscriber line interface circuit (SLIC). Each channel operates independently such that no interaction occurs between the channels. The following description applies to both channels though the description may refer to only a single channel. Some circuits, such as reference circuits which do not impact interchannel crosstalk, are common to both channels.

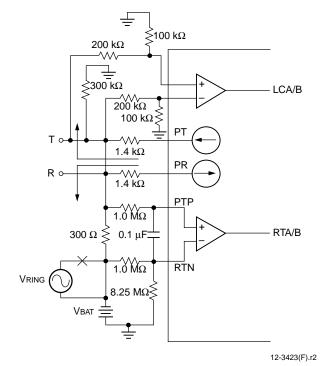

The L8575 device supplies a precise differential current to the Tip/Ring pair (via PT and PR) as a function of analog signal voltages on IRP and VRN. However, the current drivers connected to PT and PR are not designed to supply dc feed current to the loop. Two external resistors (typically 300  $\Omega$ ), connected to office battery and ground, must be used in conjunction with the L8575 SLIC to provide dc loop current. These resistors will primarily determine the longitudinal balance of the line feed; thus, they must be matched appropriately to meet the longitudinal balance requirements (0.4% for 50 dB balance).

These resistors also have a significant impact on the termination impedance of the SLIC. Feedback, using external components, allows the user to adjust the termination impedance from the intrinsic 600  $\Omega$  of the feed resistors to most ITU-T recommended complex termination impedances. Since the L8575 does not supply dc to the loop, outputs PT and PR can be coupled to the Tip and Ring through a resistance high enough to allow for simple lightning protection of the drivers. However, the resistance must be low enough to achieve the coupling of sufficient ac signals to the Tip and Ring from the available power supply. Since the Tip and Ring drivers are current sources, the value of the resistance is arbitrary and does not affect the performance of the SLIC. A minimum value of 1400  $\Omega$  (1.4 k $\Omega$ ) is required for protection purposes.

The L8575 also senses the Tip voltage, Ring voltage, and differential Tip/Ring voltage via the TS and RS sense inputs. The differential dc voltage is used internally for switchhook detection. The Tip and Ring voltages are also used internally to detect faults on Tip and Ring. Both detector thresholds are preset internally. The status of each detector is monitored at pin DO by reading the 8-bit serial shift register. The differential Tip/Ring ac signal appears on analog output XMT. The L8575 also includes:

- Per-channel ring-trip detectors, loop closure detectors.

- Six relay drivers (three per channel).

- 8-bit serial-to-parallel and parallel-to-serial logic interface.

- Per-channel circuits which eliminate the battery noise that is coupled to the Tip and Ring through the dc feed resistors.

- Fault detection.

- Zero ring voltage detection.

## **Resistor Module**

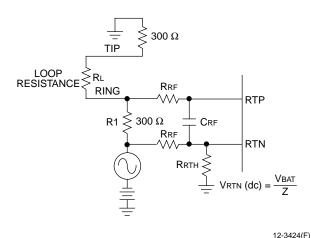

The L8575 requires certain external resistors at the Tip and Ring interface. Because of matching and protection requirements, one of the most economical options recommended to implement these registers is in a thick film resistor module. A schematic and a brief description of the function of each of these resistors is given in Figure 4. Note that Microelectronic Modules Corporation\* *MMC* A31A8575AA Thick Film resistor module is an application-specific resistor module designed for use with the L8575 SLIC. The values, tolerance, matching, and power rating of the *MMC* A31A8575AA module are given in Table 10.

Resistors R<sub>1</sub> and R<sub>2</sub> are the dc feed resistors. R<sub>1</sub> is connected from battery to Ring, and R<sub>2</sub> is connected from Tip to ground. The dc loop current is fed to the subscriber loop via these resistors. These resistors will set the dc I/V template of the line circuit with the I/V template being linear with a  $-1/600 \Omega$  slope. No constant current region at short dc loops is provided by resistors R<sub>1</sub> and R<sub>2</sub>, or the L8575 SLIC.

U.S.A: (414) 785-6506 FAX Number: (414) 785-6516

<sup>\*</sup> For additional information, contact Microelectronic Modules Corporation (*MMC*), 2601 S. Moorland Rd., New Berlin, WI 53151:

#### Resistor Module (continued)

5-3428(F)

Note: Pin numbers are *MMC* A31A8575AA pin numbers. Resistors are labeled per *MMC* A31A8575AA description. Nodes are L8575 SLIC package nodes.

#### Figure 4. L8575 SLIC Resistor Module

| Resistor            | Value  | Tolerance | Power  | Surge Rating           |

|---------------------|--------|-----------|--------|------------------------|

| R1                  | 300 Ω  | 1.0%      | 2.0 W  | Lightning: Power Cross |

| R2                  | 300 Ω  | 1.0%      | 2.0 W  | Lightning: Power Cross |

| R3                  | 100 kΩ | 1.0%      | 250 mW | None                   |

| R4                  | 100 kΩ | 1.0%      | 250 mW | None                   |

| R5                  | 200 kΩ | 1.0%      | 250 mW | Lightning: Power Cross |

| R6                  | 200 kΩ | 1.0%      | 250 mW | Lightning: Power Cross |

| R7                  | 1.4 kΩ | 2.0%      | 0.5 W  | Lightning: Power Cross |

| R8                  | 1.4 kΩ | 2.0%      | 0.5 W  | Lightning: Power Cross |

| R9                  | 15 kΩ  | _         | 10 mW  | None                   |

| R9/R1               | 50     | 1.0%      | —      | _                      |

| R1/R2               | 1      | 0.35%     | —      | _                      |

| (R3 + R6)/(R4 + R5) | 1      | 0.35%     | —      | —                      |

#### Table 10. MMC A31A8575AA Thick Film Resistor Module

Note: For 50 dB longitudinal balance, 0.2% for 58 dB balances. Continuous power (rms).

Resistors R<sub>1</sub> and R<sub>2</sub> also provide a common-mode impedance of (300 || 300) 150  $\Omega$ . These resistors will primarily determine the longitudinal balance of the line circuit; thus they must be matched appropriately to meet longitudinal balance requirements (0.35% for 50 dB and 0.2% for 58 dB). Also, they have a significant impact on the termination impedance of the SLIC. Feedback using external components (external components when a first- or second-generation codec is used) allows the user to set the termination impedance at 600  $\Omega$ , or most ITU-T recommended complex termination impedances.

Resistors R1 and R2, along with R3 and R7, are used in conjunction with the self-test feature of the L8575 SLIC. In this mode, the Ring current drive amplifier is saturated to ground, and the Tip amplifier is saturated to battery, which causes both the ring-trip and loop closure detectors to trip. Ring-trip and loop closure detector output are bits RT and LC, respectively, in the serial output stream. Under normal operating conditions, resistors  $R_1$  and  $R_2$ will see the battery voltage less the Tip/Ring voltage. Assuming a Tip/Ring voltage of 6 V (representative of a short into a handset), the nominal continuous operating power of  $R_1$  and  $R_2$  is given by:

$(48 V - 6 V)^2/600 \Omega = 2.94 W$ per R<sub>1</sub> and R<sub>2</sub> resistor pair

2.94 W/2 = 1.47 W per resistor

The operating power rating of R<sub>1</sub> and R<sub>2</sub> is 2 W. This is the steady-state power rating of R<sub>1</sub> and R<sub>2</sub>, and it is adequate for normal operating conditions. The ability of these resistors to withstand fault conditions depends on the power ratings of the individual resistors and on the power rating of the thick film resistor module itself. Obviously, the higher the power capabilities of the resistor module, the less susceptible the resistors are to damage during faults. The various fault conditions are discussed further in the Protection section of this data sheet.

Lucent Technologies Inc.

#### Resistor Module (continued)

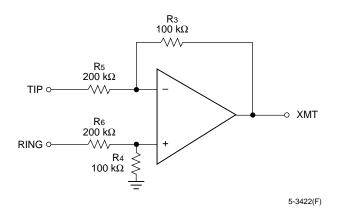

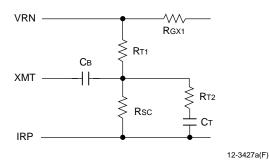

Resistors  $R_3$  through  $R_6$  set the gain of the SLIC in the transmit (2-wire to 4-wire) direction. This is shown in Figure 5.

Figure 5. L8575 SLIC Dual-Resistive Matching Requirements

The matching of resistors  $R_3$  through  $R_6$  will determine the gain accuracy of the SLIC; therefore, these resistors must also be matched accordingly. The matching requirements are given in Table 10.

Because of the high resistance values, the normal operating power of resistors R<sub>3</sub> through R<sub>6</sub> will be relatively low. Given design margin and thick film technology capabilities, a power rating of 250 mW for these resistors is not unreasonable.

Resistors R7 and R8 are used to couple the PT and PR current drive amplifiers to Tip and Ring. Since the PT and PR drive amplifiers are current sources, the value of the series resistance does not affect the loop length or other performance of the SLIC, and may be arbitrarily high for protection purposes. A value of 1.4 k $\Omega$  is adequate for protection purposes.

Under normal operating conditions, these resistors will see the battery voltage less the Tip/Ring voltage. Assuming a Tip/Ring voltage of 6 V (representative of a short into a handset), the nominal continuous operating power of  $R_7$  and  $R_8$  is given by:

$(48 V - 6 V)^2/2.8 k\Omega = 0.630 W$ per R7 and R8 resistor pair

630 mW/2 = 315 mWper resistor (R7 and R8) Hence, the operating power rating of 500 mW for  $R_7$  and  $R_8$ . This is the nominal rating for  $R_7$  and  $R_8$  under normal operating conditions. Again, the ability of these resistors to withstand fault conditions depends on the power rating.

Resistor  $R_{\vartheta}$  is also included on the thick film resistor module. This resistor is used to set the gain of the battery noise cancellation circuit. See the Battery Noise Cancellation section of this data sheet for design equations to set the value of  $R_{\vartheta}$ .

## Protection

Because of the resistive feed architecture, a simple inexpensive protection scheme that does not require a separate external protection device may be used. The *MMC* A31A8575AA resistor module has specifications which are qualified to Bellcore GR-CORE-1089, *UL*\*1459, *UL* 497A, FCC part 68.302 (d) & (e) and REA form 397G, ITU-T K20, and ITU-T K21.

Lightning and power cross protection are provided by the two dc feed resistors, R1 and R2, in the external resistor module. Under fault conditions, these resistors serve as fault current-limiting resistors. Fault current is steered to ground and to battery via resistors R2 and R1, respectively. Thus, the battery design must be such that the various specified faults can be applied to the battery through  $300 \Omega$ , without damaging the battery or the line circuit.

Resistors R<sub>1</sub> and R<sub>2</sub> need to be designed to survive lightning surges and to dissipate power associated with a Ring ground dc fault and specified ac power cross faults—both a sneak under and full surge type fault. Under certain sustained fault conditions, R<sub>1</sub> and R<sub>2</sub> could fail when they are required to survive. For this reason, a per-channel fault detector is included on the L8575 SLIC.

When the voltage across either R<sub>1</sub> and/or R<sub>2</sub> is greater than a nominal 36 V, the fault detect bit (FLT) in the serial data output will go high. The control logic on the line card detects FLT is high, and opens an external electromechanical relay (EMR) to isolate the resistors from the loop, enabling the resistors to service extended power cross. (Note the EMR is the test in or test out EMR, and this relay is driven by one of the internal relay drivers on the L8575 SLIC.)

A delay of 10 ms to 30 ms is provided (using an external capacitor on pin CFLT) in the fault detector. This prevents transients on the Tip and Ring from tripping the fault detector when a fault is not present.

\* UL is a registered trademark of Underwriters Laboratories, Inc.

#### Protection (continued)

The Tip/Ring drive amplifiers, which feed the ac signal to nodes PR and PT, are high-impedance current drivers. Since these nodes are current sources, the value of protection current-limiting series resistance does not affect the loop length or other SLIC performance, and may be arbitrarily high for protection purposes.

Resistors R7 and R8 in the resistor module are used for this purpose. These resistors have a value of 1.4 k $\Omega$  with a power rating 0.5 W. Internal diodes clamp nodes PR and PT to ground and battery.

The voltage sense leads, RS and TS, are also exposed to the outside plant. Current to these nodes is limited by resistors R<sub>3</sub> and R<sub>4</sub> in the resistor module. Resistors R<sub>3</sub> and R<sub>4</sub> are 100 k $\Omega$ , 250 mW resistors. Internal diodes also clamp nodes RS and TS to ground and battery.

The ability of the resistors to survive faults is a function of the power dissipated in the individual resistors and the total power dissipated on the entire thick film module. Fault conditions include:

- A continuous worst-case (fault detector) sneak under condition of 39 Vdc applied metallically to Ring in the case of a Ring ground fault, and

- A sneak under condition of 39 Vp (voltage peak) applied to Tip and Ring, as described in Bellcore 1089, ITU-T K20, etc., in the case of power cross.

Additionally, there is a transient fault condition, assuming full specified power cross fault voltages (Bellcore 1089, ITU-T K20, etc.,) for a time duration equal to the maximum response time that it will take to isolate the line circuit from the fault via the fault detector and EMR described above.

For example, a Ring ground fault assuming fault detector sneak under will result in a worst-case potential across the R<sub>1</sub> of 39 V. The power dissipated in R<sub>1</sub> under this condition is calculated as follows:

$(39 \vee 39 \vee)/300 \Omega = 5 \vee$

Since this is a sneak under condition, the fault detector will not trigger and the time duration of the fault can be infinite. In the case of a longitudinally applied sneak under power cross, the maximum voltage seen, this time by both  $R_1$  (Ring) and  $R_2$  (Tip), is 39 Vp (voltage peak). The power dissipation is given by:

Maximum Voltage = 39 Vp = 27.6 Vrms Maximum Power =  $(27.6 \text{ Vrms} * 27.6 \text{ Vrms})/(300 \Omega)$ = 2.54 W per resistor.

Thus, 2.54 W will be dissipated per resistor or a total of 5.1 W in a longitudinal sneak under condition.

If  $R_1$  and  $R_2$  are rated for 2 W, they can fail under these fault conditions. Also, the *MMC* A31A8575AA resistor module includes a fail-safe thermal fuse located at the Tip and Ring nodes (pin 1 and pin 19) of the module for this reason. A fail-safe fuse is recommended for any resistor module used with the L8575 SLIC.

With thick film technology, not only is the power capabilities of the individual resistors important, but also the power handling capabilities of the entire module. The total module power dissipation is calculated by summing the power dissipation for each of the resistors under a given condition.

For example, the module power dissipation for the above sneak under fault conditions is calculated in Table 11. Thus, the HIC will require a minimum power rating of 6 W continuous to survive these sneak under conditions.

| Resistor<br>(R) | Value<br>(Ω) | Ring Ground<br>Maximum dc<br>Fault Voltage (V) | Ring Ground<br>Maximum dc<br>Fault Power (W) | Longitudinal<br>Fault Maximum<br>Peak Voltage (Vp) | Longitudinal Fault<br>Maximum rms<br>Voltage (Vrms) | Longitudinal<br>Fault Maximum<br>rms Power (W) |

|-----------------|--------------|------------------------------------------------|----------------------------------------------|----------------------------------------------------|-----------------------------------------------------|------------------------------------------------|

| 1               | 300          | 39                                             | 5.07                                         | 39                                                 | 27.577                                              | 2.535                                          |

| 2               | 300          | 0                                              | 0                                            | 39                                                 | 27.577                                              | 2.535                                          |

| 3               | 100 k        | 29                                             | 0.015                                        | 39                                                 | 27.577                                              | 0.0076                                         |

| 4               | 100 k        | 0                                              | 0                                            | 39                                                 | 27.577                                              | 0.0076                                         |

| 5               | 200 k        | 39                                             | 0.0076                                       | 39                                                 | 27.577                                              | 0.0038                                         |

| 6               | 200 k        | 0                                              | 0                                            | 39                                                 | 27.577                                              | 0.0038                                         |

| 7               | 1.4 k        | 39                                             | 1.086                                        | 39                                                 | 27.577                                              | 0.543                                          |

| 8               | 1.4 k        | 0                                              | 0                                            | 39                                                 | 27.577                                              | 0.543                                          |

| Total HIC       | Power:       |                                                | 6.18                                         | —                                                  | —                                                   | 6.18                                           |

#### Table 11. Total Module Power Dissipation

## Protection (continued)

Similar consideration to the individual resistor and total module power capability should be given to full voltage power faults, but taking into account the fault detector will isolate the SLIC and resistor module after some finite period of time. The fault detector indicates a fault in the serial data output stream in 10 ns to 30 ms. Recognition and relay activation time need to be considered.

# Tip/Ring Drivers

Each channel of the L8575 utilizes a current source for the Tip/Ring driver. The driver is capable of sinking (but not sourcing) up to 15 mA from the Tip (PT) while swinging to within 4 V of office battery (VBAT), and sourcing (but not sinking) up to 15 mA to the Ring (PR) while swinging to within 4 V of ground (AGND). Since the current driver is not bidirectional, during transmission (powerup) each lead is biased at 5.6 mAdc.

# **Receive Interface**

The receive interface circuitry couples the differential signal on receive inputs IRP and VRN to the Tip/Ring drivers. Input IRP is a low-impedance (<5  $\Omega$ ) current input while VRN is a high-impedance voltage input. Internal feedback forces the voltage at IRP to be equal to VRN such that a voltage applied to VRN causes a current flow out of IRP, which equals that voltage divided by the impedance connected from IRP to AGND (assuming the input voltage is referenced to AGND).

The receive interface and Tip/Ring drivers provide a current gain of 200, i.e., a differential output current flows from PT to PR which is 200 times the current flowing into IRP. The receive interface also provides a level shift since the inputs, IRP and VRN, are referenced to analog ground, while the outputs, PT and PR, swing between AGND and VBAT. The receive interface ensures that the input current is not converted to a common-mode current at PT and PR.

# Transmit Interface

The transmit interface circuitry interfaces the differential voltage on Tip and Ring to transmit output XMT. The Tip/Ring differential voltage (both ac and dc) appears on output XMT with a gain of 0.5. The transmit interface uses an operational amplifier with four external resistors to perform a differential to single-ended conversion. Output XMT is referenced to ground (AGND). The longitudinal balance and gain accuracy at XMT depends on the matching of the external resistors.

Because a large dc potential exists at XMT, a capacitor must be used to couple the ac signal to the low-voltage codec circuitry. The operational amplifier inputs are TS and RS. These inputs are also used by the fault-detection circuitry to detect fault voltages on Tip or Ring. A fault is detected when the magnitude of the voltage across either dc feed resistor exceeds a nominal 36 V (equivalent to approximately 4 W dissipation in either resistor). A delay is provided (using an external capacitor on pin CFLT) in the fault detector. This prevents transients on Tip and Ring from tripping the fault detector when a fault is not actually present.

# **Battery Noise Cancellation**

The battery noise cancellation circuit senses the ac noise on the battery via the capacitor connected from input CBN to VBAT. It then couples this noise, 180 degrees out of phase, to the Ring current driver amplifier. This cancels the battery noise that is coupled to the Ring through the feed resistor connected to VBAT.

Additionally, it ensures longitudinal balance which depends only on the matching of the battery feed resistors by creating an ac ground at VBAT with respect to signals on the Ring lead.

For the cancellation to operate properly, both the phase and gain must be accurate. The battery noise cancellation gain is a transconductance that is equal to 50 divided by resistor R9 on the thick film resistor module connected from RGBN to ground (AGND). This value must be equal to the reciprocal of the dc feed resistor (1/300  $\Omega$ ), that is,

$$\frac{50}{R_9} = \frac{1}{300 \Omega}$$

$$R_9 = 15 k\Omega$$

It is advantageous if the two resistors are matched and tracked thermally, i.e., located on the same film integrated circuit (FIC).

#### **On-Hook Transmission**

In powerup mode, the L8575 SLIC provides a dc bias of 5.6 mA. The 5.6 mA bias is also present under onhook conditions. The L8575 SLIC is able to support onhook transmission because of this bias. It is sufficiently high to drive a 3.17 dBm signal into a 600  $\Omega$  or 900  $\Omega$  loop under open-circuit conditions. An internal current source provides a dc bias of 112  $\mu$ A. There is an internal current gain of 50; thus (50 \* 112  $\mu$ A) 5.6 mA flows from battery through R1 to PR, and 5.6 mA flows from PT through R2 to ground under on-hook conditions.

## Self-Test

The L8575 SLIC offers a self-test capability. This is set via logic inputs D1 and D0 in the serial input data stream. In this mode, shown in Figure 6, the Ring current drive amplifier is saturated to ground, and the Tip amplifier is saturated to battery, which causes both the ring-trip and loop closure detectors to indicate an off-hook condition. In this operation mode, the ring relay must not be active. The ring relay driver output in the L8575 is at package nodes RDR (A&B). These relay drivers are controlled by logic inputs D2 (A&B) in the serial input data stream. See Table 14 for details.

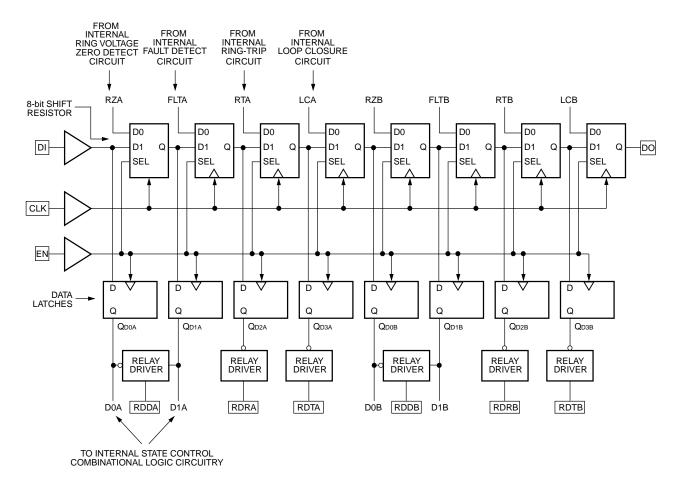

**Serial Data Interface**

A 4-wire serial interface (DI, DO, CLK, and EN) is used to pass data from the control logic on the line card to the L8575 SLIC, and to pass detector information from L8575 SLIC to the control logic on the line card. When enable input EN is high, data on input DI is clocked into an 8-bit shift register on a high-to-low transition of the clock input CLK.

Eight latches (four per channel) are provided to store the data. Data is loaded into the eight latches from input DI and the first 7 bits of the shift register on the high-to-low transition of EN. When EN is low, a high-tolow transition on CLK loads all of the detector information (loop closure, fault zero voltage, and ring-trip from the internal detector circuitry) into the 8-bit shift register. When EN is high, data in the 8-bit shift register is clocked out on output DO on the high-to-low transition of CLK.

Two latch outputs per channel drive relay drivers. The drivers are included on the L8575 SLIC. These are the relay drivers whose outputs are at external package nodes RDR (A&B) and RDT (A&B). The remaining two latch output power channels are internal control signals. These are logic data bits D0 (A&B) and D1 (A&B). These bits input to a combinational logic circuit that controls the operational state of each channel and also controls the state of the third relay driver. The third relay driver's output is at external package node RDD (A&B). Refer to the Truth Table (see Table 15) for more details.

Note that up to 16 channels may be daisy-chained together. The DO lead of package 1 (channels 1 and 2) may be tied to the DI lead of package 2 (channels 3 and 4), etc. All EN and CLK should also be tied together in this mode.

The L8575 SLIC device has an internal reset which guarantees that all relay drivers power up in the offstate when 5 V (VccD and VccA) is applied to the device. This reset operates properly only if input EN is held high (within 0.5 V of VccD) when the 5 V is applied. An external pull-up resistor from the EN bus to VccD satisfies this requirement, provided that the logic-driving EN does not pull the EN bus low during powerup.

Figure 6. Self-Test Mode Circuit

### Serial Data Interface (continued)

Figure 7 shows the timing characteristics and requirement definitions.

12-3305(F).ar2

Figure 7. Timing Requirements for CLK, EN, DI, and DO

#### Table 12. Truth Table for EN and CLK

| EN           | CLK          | Function                                                      |  |  |  |

|--------------|--------------|---------------------------------------------------------------|--|--|--|

| 1            | $\downarrow$ | Shift register clocked, $QN = QN - 1$ ; latches unaffected.   |  |  |  |

| 0            | $\downarrow$ | Channel data latched into shift register; latches unaffected. |  |  |  |

| $\downarrow$ | X            | Contents of shift register transferred to output latches.     |  |  |  |

#### Table 13. Output DATA Bit Definition

| DATA Bit | Output | Output Bit Definition                                                   |

|----------|--------|-------------------------------------------------------------------------|

| D0A      | D0A    | Latch output state D0A (refer to Operating States section).             |

| D1A      | D1A    | Latch output state D1A (refer to Operating States section).             |

| D2A      | RDRA   | Ringing relay driver A is on (RDRA low = relay energized) when D2A = 1. |

| D3A      | RDTA   | Test relay driver A is on (RDTA low = relay energized) when D3A = 1.    |

| D0B      | D0B    | Latch output state D0B (refer to Operating States section).             |

| D1B      | D1B    | Latch output state D1B (refer to Operating States section).             |

| D2B      | RDRB   | Ringing relay driver B is on (RDRB low = relay energized) when D2B = 1. |

| D3B      | RDTB   | Test relay driver B is on (RDTB low = relay energized) when D3B = 1.    |

#### Serial Data Interface (continued)

#### Table 14. Input DATA Bit Definition

| Input | DATA Bit | Input Bit Definition                                                    |

|-------|----------|-------------------------------------------------------------------------|

| RZA   | D0A      | Channel A ringing voltage zero crossing detector output (positive = 1). |

| FLTA  | D1A      | Channel A fault detector output (loop fault = 1).                       |

| RTA   | D2A      | Channel A ring-trip detector output (ring-trip = 1).                    |

| LCA   | D3A      | Channel A switchhook detector output (off-hook = 1).                    |