# MICRO NETWORKS

# MN7145 Series

8-CHANNEL, 12-Bit

DATA ACQUISITION SYSTEM

with μP INTERFACE

## **FEATURES**

- Complete, 8-Channel, 12-Bit DAS with MUX, T/H, ADC, Ref. and 3-State Output

- 25,000 Channels/sec Guaranteed Throughput

- Microprocessor Interface (3-State Output, Address Line, Read/Convert, etc.)

- Small 28-Pin Side-Brazed DIP

- 18 Models (3 Input Voltage Ranges)

- Fully Specified 0°C to +70°C (J and K Models) or -55°C to +125°C (S and T Models)

- MIL-H-38534 Screening Optional. MIL-STD-1772 Qualified Facility

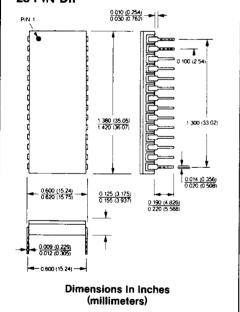

# 28 PIN DIP

# **DESCRIPTION**

The MN7145, MN7146 and MN7147 are complete, single-package, 8-channel, 12-bit, data acquisition systems with internal decoding logic and 3-state output buffers which greatly facilitate microprocessor control. Packing a lot of function into a 28-pin, side-brazed, ceramic DIP, MN7145 Series DAS's each contain an 8-channel, overvoltage protected ( $\pm 35V$ ) multiplexer; a high-speed ( $10\mu$ sec), high-impedance ( $10^{10}\Omega$ ), T/H amplifier; a high-speed ( $25\mu$ sec), 12-bit A/D with reference and clock; and all the timing and control logic (3-state buffer, address line, read/convert line) necessary for  $\mu$ P control. System throughput rate is guaranteed at 25,000 channels/sec for full rated accuracy.

These devices are manufactured using contemporary hybrid assembly techniques, and they illustrate the technology's ability to combine I.C.'s made with different processing technologies into a single functional design that takes advantage of the best aspects of each semiconductor technology. The overvoltage protected mux is CMOS. The T/H is high-speed bipolar with an npo hold cap. The A/D combines high-speed bipolar technology with state-of-the-art thin-film technology and TTL compatible CMOS. Active laser trimming of fully assembled devices compensates for summed accuracy and linearity errors to produce overall system linearity (±1/2LSB) and accuracy (±0.05%FSR offset error) that may not be achievable when assembling a similar system with individual components. Small size, low power (1 Watt max), high sampling rate and low cost may make the MN7145 Series the most economical way possible to achieve multichannel, 12-bit, data acquisition today.

MN7145 (0 to +10V input range), MN7146 ( $\pm$ 5V) and MN7147 ( $\pm$ 10V) are fully specified over both 0°C to +70°C (J and K models) and -55°C to +125°C (S and T models) temperature ranges. Assorted linearity grades ( $\pm$ ½ LSB,  $\pm$ 1LSB) at room temperature and over temperature are available as outlined in the specification table. All devices guarantee "no missing codes" over temperature (to either the 12-bit or 11-bit level).

MICRO NETWORKS

324 Clark St., Worcester, MA 01606 (508) 852-5400

February 1988

# MN7145 SERIES 8-CHANNEL, 12-Bit, DATA ACQUISITION SYSTEMS

#### **ABSOLUTE MAXIMUM RATINGS**

Operating Temperature Range Specified Temperature Range: J and K Models S. S/B, T, T/B Models Storage Temperature Range Positive Supply (+ Vcc, Pin 19) Negative Supply (+ Vcc, Pin 7) Logic Supply (+ Vdd, Pin 6) Digital Inputs (Pins 3, 4, 8-10) Analog Inputs: (Pins 11-18) (Pins 20, 21) - 55°C to + 125°C

0°C to + 70°C

- 55°C to + 125°C

- 65°C to + 150°C

0 to + 16.5 Volts

0 to - 16.5 Volts

0 to + 7 Volts

- 0.5 to (+ Vdd + 0.5) Volts

± Voc ± 20V

± Vcc

PART NUMBER — MN714XX/B CH

Select MN7145 (0 to +10V), MN7146(±5V)

or MN7147(±10V) —

Select suffix J,K,S or T for

desired performance and specified

temperature range.

Add "/B" to "S" or "T" models for

Environmental Stress Screening

Add "CH" to "S/B" or "T/B" models for

100% screening according to

MIL-H-38534.

ORDERING INFORMATION

# DESIGN SPECIFICATIONS ALL UNITS ( $T_A = +25$ °C, $\pm Vcc = \pm 15V$ , + Vdd = +5V unless otherwise indicated) (Note 1)

| ANALOG INPUTS                                                                                                                    | MIN.                         | TYP.                             | MAX.                             | UNITS                                              |

|----------------------------------------------------------------------------------------------------------------------------------|------------------------------|----------------------------------|----------------------------------|----------------------------------------------------|

| Number of Input Channels                                                                                                         |                              | 8 Single-Ended                   |                                  |                                                    |

| Input Voltage Ranges: MN7145<br>MN7146<br>MN7147                                                                                 |                              | 0 to + 10<br>±5<br>±10           |                                  | Volts<br>Volts<br>Volts                            |

| Input Impedance (Note 2): On Channel Off Channels                                                                                |                              | 10¹º / 100<br>10¹º / 10          |                                  | Ω/pF<br>Ω/pF                                       |

| Input Bias Current (On Channel): +25°C (Note 2) T <sub>min</sub> to T <sub>max</sub> (Note 3)                                    |                              | ± 1<br>± 50                      | ± 250                            | nA<br>nA                                           |

| Input Leakage Current (Off Channels, Note 2): +25°C<br>T <sub>min</sub> to T <sub>max</sub> (Note 3)                             |                              | ± 1<br>± 50                      |                                  | nA<br>nA                                           |

| DIGITAL INPUTS                                                                                                                   |                              |                                  |                                  |                                                    |

| Logic Levels: A <sub>0</sub> , R/C̄: Logic "1"<br>Logic "0"<br>MA <sub>0</sub> -MA <sub>2</sub> (Note 4): Logic "1"<br>Logic "0" | + 2.4<br>- 0.5<br>+ 4.0<br>0 |                                  | + 5.5<br>+ 0.8<br>+ 5.5<br>+ 0.8 | Volts<br>Volts<br>Volts<br>Volts                   |

| Logic Currents (All Inputs): Logic "1"<br>Logic "0"                                                                              |                              |                                  | ± 10<br>± 10                     | μ <b>Α</b><br>μ <b>Α</b>                           |

| DIGITAL OUTPUTS (Status, DBO-DB11)                                                                                               |                              |                                  |                                  |                                                    |

| Output Coding (Note 5): Unipolar Ranges<br>Bipolar Ranges                                                                        |                              | Straight Binary<br>Offset Binary |                                  |                                                    |

| Logic Levels: Logic "1" ( $I_{source} \le 500\mu A$ )<br>Logic "0" ( $I_{sink} \le 1.6mA$ )                                      | + 2.4                        |                                  | + 0.4                            | Volts<br>Volts                                     |

| Leakage (DBO-DB11) in High-Z State                                                                                               |                              | ±1                               | ± 10                             | μΑ                                                 |

| Output Capacitance (Note 2)                                                                                                      |                              | 5                                |                                  | pF                                                 |

| POWER SUPPLY REQUIREMENTS                                                                                                        |                              |                                  |                                  |                                                    |

| Power Supply Range: ± V <sub>CC</sub> Supplies<br>+ V <sub>dd</sub> Supply                                                       | ± 13.5<br>+ 4.5              | ± 15<br>+ 5                      | ± 16.5<br>+ 5.5                  | Volts<br>Volts                                     |

| Power Supply Rejection (Note 6): + V <sub>CC</sub> Supply - V <sub>CC</sub> Supply + V <sub>dd</sub> Supply                      |                              | ± 0.002<br>± 0.002<br>± 0.002    | ± 0.005<br>± 0.005<br>± 0.005    | % FSR/% Supply<br>% FSR/% Supply<br>% FSR/% Supply |

| Current Drains: +V <sub>CC</sub> Supply -V <sub>CC</sub> Supply +V <sub>dd</sub> Supply                                          |                              | + 18<br>- 26<br>+ 10             | + 25<br>- 35<br>+ 20             | mA<br>mA<br>mA                                     |

| Power Consumption                                                                                                                |                              | 710                              | 1000                             | mW                                                 |

| DYNAMIC CHARACTERISTICS                                                                                                          |                              |                                  |                                  |                                                    |

| Conversion Time (Note 7): 12-Bit Conversion<br>8-Bit Conversion                                                                  |                              | 20<br>13                         | 25<br>17                         | μsec<br>μsec                                       |

| Throughput Rate                                                                                                                  | 25                           | 35                               |                                  | kHz                                                |

PERFORMANCE SPECIFICATIONS (Typical at T<sub>A</sub> = +25°C, ± Vcc = ±15V, + Vdd = +5V unless otherwise indicated) (Note 8)

| MODEL                                                                                                                         | MN7145J<br>MN7146J<br>MN7147J | MN7145K<br>MN7146K<br>MN7147K | MN7145S<br>MN7146S<br>MN7147S | MN7145T<br>MN7146T<br>MN7147T | UNITS                  |

|-------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|------------------------|

| Integral Linearity Error:<br>Initial ( + 25°C) (Maximum)<br>T <sub>min</sub> to T <sub>max</sub> (Maximum, Note 3)            | ± 1<br>± 1                    | ± ½<br>± ½                    | ±1<br>±1                      | ± ½<br>± 1                    | LSB<br>LSB             |

| Resolution for Which No Missing<br>Codes is Guaranteed:<br>Initial ( + 25°C)<br>T <sub>min</sub> to T <sub>max</sub> (Note 3) | 11<br>11                      | 12<br>12                      | 11<br>11                      | 12<br>12                      | Bits<br>Bits           |

| Unipolar Offset Error (Notes 9,10):<br>Initial ( + 25°C) (Maximum)<br>Drift (Maximum)                                         | ± 0.05<br>± 15                | ± 0.05<br>± 10                | ± 0.05<br>± 25                | ± 0.05<br>± 20                | % FSR<br>ppm of FSR/°C |

| Bipolar Offset Error (Notes 9,11):<br>Initial ( + 25°C) (Maximum)<br>Drift (Maximum)                                          | ± 0.25<br>± 25                | ± 0.1<br>± 20                 | ± 0.25<br>± 25                | ± 0.1<br>± 20                 | % FSR<br>ppm of FSR/°C |

| Gain Error (Notes 9,12):<br>Initial ( + 25°C) (Maximum)<br>Drift (Maximum)                                                    | ± 0.3<br>± 50                 | ± 0.3<br>± 25                 | ± 0.3<br>± 50                 | ± 0.3<br>± 25                 | %<br>ppm/°C            |

#### SPECIFICATION NOTES:

- Detailed timing specifications appear in the Timing sections of this data sheet. FSR = Full Scale Range. MN7145 (0 to +10V input voltage range) and MN7146 (± 5V input voltage range) have a 10V FSR. MN7147 (± 10V input voltage range) has a 20V FSR.

- These parameters are listed for reference only and are not tested.

J and K models are fully specified for 0°C to +70°C operation. S, S/B, T and T/B models are fully specified for -55°C to +125°C operation. See ordering information

- 4. If the multiplexer inputs are driven from standard TTL logic,  $1k\Omega$  pullup resistors to +5V should be used.

- 5. See table of transition voltages in section labeled Digital Output Coding.

- 6. Power supply rejection is defined as the change in the analog input voltage at which the 1111 1111 1110 to 1111 1111 1111 or 0000 0000 0000 to 0000 0000 0001 output transitions occur versus a change in power-supply voltage

- 7. Whenever the Status Output (pin 22) is low (logic "0"), the internal T/H is in the track mode and the A/D converter is not converting. When Status is high (the definition of A/D conversion time), the T/H is in the hold mode,

- and the A/D is performing a conversion.

8. All performance specifications are specified and tested while sampling and converting at a 25kHz throughput rate

- 9. Adjustable to zero with external potentiometer.

- 10. Unipolar offset error is defined as the difference between the ideal and the actual input voltage at which the digital output just changes from 0000 0000 0000 to 0000 0000 0001 when operating the MN7145 on its unipolar range. The ideal value at which this transition should occur is + 1/2 LSB. See Digital Output Coding.

- 11. Bipolar offset error is defined as the difference between the ideal and the actual input voltage at which the digital output just changes from 0000 0000 0000 to 0000 0000 0001 when operating the MN7146 or MN7147 on a bipolar range. The ideal value at which this transition should occur is -F.S. + ½ LSB. See Digital Output Coding.

- 12. Gain error is defined as the error in the slope of the converter transfer function. It is expressed as a percentage and is equivalent to the deviation (divided by the ideal value) between the actual and the ideal value for the full input voltage span from the input voltage at which the output changes from 1111 1111 1111 to 1111 1111 1110 to the input voltage at which the output changes from 0000 0000 0001 to 0000 0000 0000.

Specifications subject to change without notice as Micro Networks reserves the right to make improvements and changes in its products.

CAUTION: These devices are sensitive to electronic discharge. Proper I.C, handling procedures should be followed.

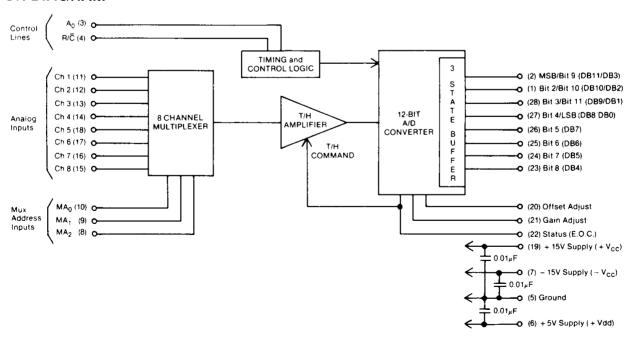

#### **BLOCK DIAGRAM**

# ORDERING INFORMATION

|               | Input         | Specified         | Integral Li | nearity (1) | No Missing<br>Codes | Guaranteed<br>Throughput Rate |            |

|---------------|---------------|-------------------|-------------|-------------|---------------------|-------------------------------|------------|

| Part Number   | Voltage Range | Temp. Range       | + 25°C      | Temp.       | Over Temp.          | (Channels/sec)                | Package    |

| MN7145J       | 0 to + 10V    | 0°C to +70°C      | ± 1         | ± 1         | 11 Bits             | 25,000                        | 28-Pin DIP |

| MN7145K       | 0 to + 10V    | 0°C to +70°C      | ± 1/2       | ± 1/2       | 12 Bits             | 25,000                        | 28-Pin DIP |

| MN7145S       | 0 to + 10V    | -55°C to +125°C   | ±1          | ±1          | 11 Bits             | 25,000                        | 28-Pin DIP |

| MN7145S/B (2) | 0 to + 10V    | -55°C to +125°C   | ± 1         | ± 1         | 11 Bits             | 25,000                        | 28-Pin DIP |

| MN7145T       | 0 to + 10V    | -55°C to +125°C   | ± ½         | ± 1         | 12 Bits             | 25,000                        | 28-Pin DIP |

| MN7145T/B (2) | 0 to +10V     | - 55°C to + 125°C | ± 1/2       | ± 1         | 12 Bits             | 25,000                        | 28-Pin DIP |

| MN7146J       | ± 5V          | 0°C to + 70°C     | ±1          | ±1          | 11 Bits             | 25,000                        | 28-Pin DIP |

| MN7146K       | ± 5V          | 0°C to +70°C      | ± 1/2       | ± 1/2       | 12 Bits             | 25,000                        | 28-Pin DIP |

| MN7146S       | ± 5V          | -55°C to +125°C   | ± 1         | ±1          | 11 Bits             | 25,000                        | 28-Pin DIP |

| MN7146S/B (2) | ± 5V          | -55°C to +125°C   | ± 1         | ±1          | 11 Bits             | 25,000                        | 28-Pin DIP |

| MN7146T       | ± 5V          | -55°C to +125°C   | ± ½         | ±1          | 12 Bits             | 25,000                        | 28-Pin DIP |

| MN7146T/B (2) | ± 5V          | -55°C to +125°C   | ± ½         | ± 1         | 12 Bits             | 25,000                        | 28-Pin DIP |

| MN7147J       | ± 10V         | 0°C to + 70°C     | ±1          | ±1          | 11 Bits             | 25,000                        | 28-Pin DIP |

| MN7147K       | ± 10V         | 0°C to +70°C      | ± 1/2       | ± 1/2       | 12 Bits             | 25,000                        | 28-Pin DIP |

| MN7147S       | ± 10V         | -55°C to +125°C   | ±1          | ±1          | 11 Bits             | 25,000                        | 28-Pin DIP |

| MN7147S/B (2) | ± 10V         | -55°C to +125°C   | ±1          | ± 1         | 11 Bits             | 25,000                        | 28-Pin DIP |

| MN7147T       | ± 10V         | -55°C to +125°C   | ± 1/2       | ± 1         | 12 Bits             | 25,000                        | 28-Pin DIP |

| MN7147T/B (2) | ± 10V         | -55°C to +125°C   | ± ½         | ±1          | 12 Bits             | 25,000                        | 28-Pin DIP |

<sup>1.</sup> Maximum error expressed in LSB's for 12 bits.

#### PIN DESIGNATIONS

| • 28<br>Pin 1 | 1 Bit 2/Bit 10 (DB10/DB2) 2 MSB/Bit 9 (DB11/DB3) 3 Address Line (A <sub>0</sub> ) 4 Read/Convert (R/C) 5 Ground 6 + 5V Supply (+ V <sub>dd</sub> ) 7 - 15V Supply (- V <sub>CC</sub> ) 8 Mux Address A <sub>2</sub> (MA <sub>2</sub> ) 9 Mux Address A <sub>1</sub> (MA <sub>1</sub> ) 10 Mux Address A <sub>0</sub> (MA <sub>0</sub> ) 11 Channel 1 Input 12 Channel 2 Input 13 Channel 3 input | 28 Bit 3/Bit 11 (DB9/DB1) 27 Bit 4/LSB (DB8/DB0) 26 Bit 5 (DB7) 25 Bit 6 (DB6) 24 Bit 7 (DB5) 23 Bit 8 (DB4) 22 Status (E.O.C.) 21 Gain Adjust 20 Offset Adjust 19 +15V Supply (+V <sub>CC</sub> ) 18 Channel 5 Input 17 Channel 6 Input 16 Channel 7 Input |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14 15         | 13 Channel 3 Input<br>14 Channel 4 Input                                                                                                                                                                                                                                                                                                                                                         | 16 Channel 7 Input<br>15 Channel 8 Input                                                                                                                                                                                                                    |

### **APPLICATIONS INFORMATION**

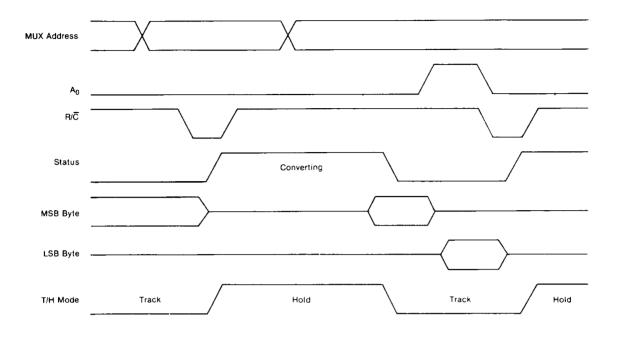

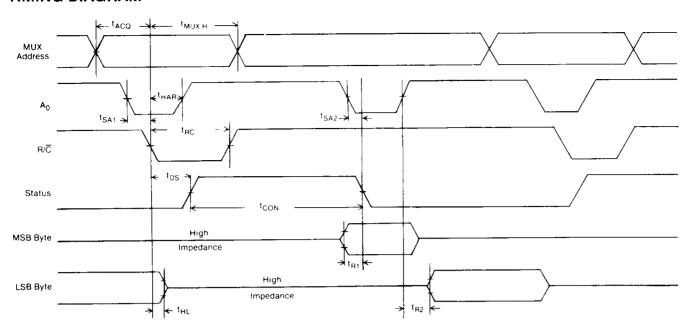

**DESCRIPTION OF OPERATION** — MN7145 Series devices are 8-channel, 12-bit, data acquisition systems with internal 8-channel multiplexer, track-hold (T/H) amplifier, 12-bit analog-to-digital (A/D) converter, and microprocessor interface logic (3-state buffer, address line, read/convert line). A minimal amount of signals need to be supplied externally to these devices in order to achieve true multichannel data acquisition. High input impedance and low input bias currents allow analog signal sources to be connected directly to the multiplexer inputs. Multiplexer channels are randomly selected via three mux address lines (MA<sub>0</sub>, MA<sub>1</sub>, MA<sub>2</sub>). The T/H is controlled directly by the A/D and requires no external commands. The address  $(A_0)$  and read/convert  $(R/\overline{C})$  lines are used in assorted combinations to: initiate (write) 12-bit conversions, initiate 8-bit conversions, read back MSB data and read back LSB data. In normal operation, a mux address is selected (000 = channel 1, 111 = channel 8), and time must be allowed for the mux to switch and settle and for the T/H to acquire and track the new analog input signal. Then the A/D conversion is initiated by dropping the R/Č line. Once a conversion has been initiated, the device's Status output (pin 22)

rises to a logic "1" signaling that a conversion is in progress. This action drives the T/H into the hold mode instantaneously "freezing" the appropriate analog input and holding it constant while the A/D conversion proceeds. When the conversion is complete, Status drops back to a logic "0"; the T/H is driven back into the track mode; and output data is held in a 3-state buffer ready to be read. At this point, output data is available in two 8-bit bytes (multiplexed on a single set of output lines) and can be enabled by bringing R/ $\overline{C}$  high and toggling  $A_0$  ( $A_0$  = "0" enables MSB data byte;  $A_0$  = "1" enables LSB data byte). If R/ $\overline{C}$  is brought high during a conversion, output data is automatically enabled when the conversion is complete. The output data lines return to the high-impedance state when R/ $\overline{C}$  is brought low initiating a new conversion.

The multiplexer address can be changed during or after a conversion. In order to achieve maximum device performance, the multiplexer address may be changed  $1\mu$ sec after initiating a conversion. If the multiplexer is updated in this fashion, and a new channel is selected while a conversion is in process, the T/H will immediately start to acquire and track

<sup>2.</sup> Includes 100% screening to MIL-STD-883.

the new analog input signal when the conversion is complete. This allows the microprocessor to read output data while the T/H is acquiring the next analog input signal. The diagram

below illustrates the relationships of the timing signals previously discussed. For more detailed timing information, see the timing section of this data sheet.

#### **TIMING DIAGRAM**

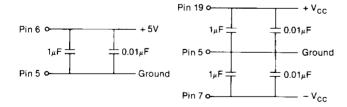

LAYOUT CONSIDERATIONS AND GROUNDING—Proper attention to layout and decoupling is necessary to obtain specified accuracy from MN7145 Series devices. It is critically important that the devices' power supplies be filtered, well-regulated and free from high-frequency noise. Use of noisy supplies may cause unstable output codes to be generated. Switching power supplies are not recommended for circuits attempting to achieve 12-bit accuracy unless great care is used in filtering any switching spikes present in the output.

Decoupling capacitors should be used on all power-supply pins; the supply decoupling capacitors should be connected directly from Vdd (pin 6), + Vcc (pin 19) and - Vcc (pin 7) to Ground (pin 5). Suitable decoupling capacitors are  $1\mu F$  tantalum types in parallel with  $0.01\mu F$  ceramic discs. See diagram below.

#### POWER SUPPLY DECOUPLING

Coupling between analog inputs and digital signals should be minimized to avoid noise pickup. Analog input runs should be well separated from digital clock lines and other noise sources. The use of wire-wrap circuit construction is not recommended. Careful printed-circuit construction is preferred. If external offset and gain adjust potentiometers are used, the pots and associated series resistors should be located as close to the device as possible. If external adjustment potentiometers are not used, Offset Adjust (pin 20) and Gain Adjust (pin 21) should be left open. Do not ground.

Ground (pin 5) should be connected to system analog ground as close to the unit as possible, preferably through a large analog ground plane beneath the package.

**CONTROL FUNCTIONS**—Operating MN7145 Series devices under microprocessor control is most easily understood by examining the control-line funtions in a truth table. Table 1 below is a summary of the control-line functions. Table 2 is the control-line truth table.

Table 1: MN7145 Series Control Line Functions

| Pin<br>Designations                             | Definition                                      | Function                                                                                                                                                                                                                                                           |

|-------------------------------------------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MA <sub>0</sub> -MA <sub>2</sub><br>(Pins 8-10) | MUX Address<br>In                               | Selects MUX channel to be held and converted.                                                                                                                                                                                                                      |

| R/C<br>(Pin 4)                                  | Read/Convert<br>("1" = Read)<br>("0" = Convert) | $R/\overline{C}$ 1 – 0 edge is used to initiate 8 or 12-bit conversions.<br>$R/\overline{C}$ = "1" enables output data during a read cycle.                                                                                                                        |

| A <sub>0</sub><br>(Pin 3)                       | Byte Address<br>Short Cycle                     | In the start-convert mode, $A_0$ selects 8-bit ( $A_0$ = "1") or 12-bit ( $A_0$ = "0") conversion mode. When reading output data, $A_0$ selects the output data format. $A_0$ = "0" enables high and middle bits. $A_0$ = "1" enables low bits and trailing "0's". |

Multiplexer input channels on MN7145 Series devices are randomly accessed via Address lines (MA0, MA1, MA2). The multiplexer address may be changed after a conversion cycle is complete. However, if desired, the multiplexer address may be changed during a conversion cycle. If doing so, caution must be used to ensure that the address is not updated within  $1\mu$ sec of having initiated the conversion.

The Read/Convert input (R/C, pin 4) is used in combination with the Byte Address/Short Cycle input (A<sub>0</sub>, pin 3) to initiate either 8 or 12-bit conversion cycles and to read back output data stored in the A/D's 3-state output buffer. Conversion cycles are initiated by bringing R/C low. Read cycles are initiated by bringing R/C high. R/C may remain low during a conversion or it may be brought back high. If it is returned high, it must be done so within  $1.5 \mu sec$  after the conversion begins. If R/C is left low during a conversion, it should not be brought high until after the status line has fallen indicating that the conversion is complete.

Output data is only enabled when Status = "0" and  $R/\bar{C}$  = "1". However, if  $R/\overline{C}$  has been brought high during the conversion, output data will automatically be enabled 300nsec (minimum) prior to the fall of Status. If R/C is left low during a conversion, the output lines will remain in the high-impedance state when Status returns low. R/C must then be brought high to read output data.

The Byte Address/Short Cycle input (A<sub>0</sub>, pin 3) is used in combination with R/C when initiating conversions and reading output data. When initiating a conversion, the signal applied to  $A_0$  determines whether a 12-bit ( $A_0 = "0"$ ) or an 8-bit conversion is initiated (A<sub>0</sub> = "1"). As discussed earlier, conversion cycles are initiated by the falling edge of R/C. When reading digital output data from MN7145 Series devices, the signal applied to A<sub>0</sub> determines which 8-bit data byte is multiplexed to the eight digital output lines. When  $A_0$  = "0", the MSB byte (MSB through bit 8) is enabled. When  $A_0$  = "1", the LSB byte (bit 9 through LSB) is enabled.

Table 2: MN7145 Series Truth Table

|     | Con | trol Li         | nes             |     |                                                |

|-----|-----|-----------------|-----------------|-----|------------------------------------------------|

| R/C | Ao  | MA <sub>2</sub> | MA <sub>1</sub> | MAo | Device Operation                               |

| X   | Х   | 0               | 0               | 0   | Select MUX Channel 1                           |

| X   | Х   | 0               | 0               | 1   | Select MUX Channel 2                           |

| X   | Х   | 0               | 1               | 0   | Select MUX Channel 3                           |

| ×   | Х   | 0               | 1               | 1   | Select MUX Channel 4                           |

| X   | X   | 1               | 0               | 0   | Select MUX Channel 5                           |

| X   | Х   | 1               | 0               | 1   | Select MUX Channel 6                           |

| X   | X   | 1               | 1               | 0   | Select MUX Channel 7                           |

| X   | Ιx  | 1               | 1               | 1   | Select MUX Channel 8                           |

| 1-0 | 0   | Х               | X               | Х   | Initiate 12-Bit Conversion on                  |

|     |     |                 |                 |     | Selected Channel                               |

| 1-0 | 1   | Х               | X               | X   | Initiate 8-Bit Conversion on                   |

| 1   |     |                 |                 | Ì   | Selected Channel                               |

| 1   | 0   | Х               | X               | X   | Enable 8 MSB's (high and middle                |

| i   |     |                 |                 | 1   | bits)                                          |

| 1   | 1   | Х               | X               | X   | Enable 4 LSB's (low bits) and 4 trailing "0's" |

|     | ×   | ×               | ×               | x   | Output Data Disabled (high-                    |

| 0   | *   |                 | \               | ^   | impedance state)                               |

#### TABLE 1, TABLE 2 NOTES:

- 1. "1" indicates TTL logic high (2.4V minimum).

- "0" indicates TTL logic low (0.8V maximum)

- 3. X indicates "don't care"

- 4. 1-0 indicates logic transition (falling edge).

5. Output data format is as follows:

| ata torrita | 10000                | • • •                  |                     |     |

|-------------|----------------------|------------------------|---------------------|-----|

| MSB         | XXXX<br>High<br>Bits | XXXX<br>Middle<br>Bits | XXXX<br>Low<br>Bits | LSB |

|             | e MCD's              |                        | 4 1 SR'e            |     |

TIMING - MUX ADDRESSING-MN7145 Series devices' input multiplexer is randomly addressed by applying the desired channel address (000 = channel 1, 111 = channel 8) to the address lines (MA<sub>0</sub>, MA<sub>1</sub>, MA<sub>2</sub>). Once the desired channel is selected, 10µsec must be allowed for T/H acquisition time (tACO) prior to initiating a conversion. The multiplexer address may be updated as early as 1µsec (t<sub>MUXH</sub>) after the conversion cycle has begun if this is necessary to meet system timing requirements. This address hold time (t<sub>MUXH</sub>) ensures that the T/H amplifier has fully switched into the hold mode prior to being presented with the signal on the next channel.

TIMING - INITIATING CONVERSIONS—As stated earlier, the falling edge of R/C in combination with A<sub>0</sub> initiates either 8-bit conversion cycles (A<sub>0</sub> = "1") or 12-bit conversion cycles ( $A_0 = "0"$ ). If the multiplexer address has been changed prior to initiating a conversion, a minimum of 10 µsec must be allowed for T/H acquisition time. As stated earlier, the multiplexer address may be changed during an ongoing conversion. In this case, the T/H will be commanded back into the track mode and will start acquiring the new channel's signal as soon as the ongoing conversion is complete

Timing for a typical 12-bit conversion cycle is shown below. In this example, the multiplexer is addressed; 10µsec T/H acquisition time is allowed; and  $A_0$  is set to a logic "0" all prior to initiating the 12-bit conversion cycle. Ao must remain valid for 50nsec while R/C is low to ensure that a 12-bit conversion cycle is properly initiated ( $t_{HAR}\!=\!50$ nsec min.). Status output rises to a logic "1" 200nsec after R/C is brought low (t<sub>DS</sub> = 200nsec max.) commanding the T/H amplifier into the hold mode and signaling that a conversion cycle is in progress. While Status is high, the output buffers return to the high-impedance state and output data cannot be read. The multiplexer address is updated after a minimum address hold time of  $1\mu$ sec ( $t_{MUXH} = 1\mu$ sec min.). In this example, R/C is returned high during the conversion cycle so that output data will be automatically enabled upon completion of the cycle. Once a conversion has started, additional R/C falling edges will be ignored. However,\_if A0 changes state after a conversion begins, additional R/C falling edges will latch the new state of Ao, possibly causing a wrong cycle length (8 vs. 12 bits) for that conversion. Not shown in the example below, R/C may remain low during the conversion in which case the output data will remain in the high-impedance state when Status returns low at the end of the conversion. Output data can then be enabled by bringing R/ $\overline{C}$  high and asserting A<sub>0</sub> as desired.

TIMING - RETRIEVING DATA—When the conversion cycle is complete and Status output is low, the combination of signals applied to R/C and  $A_0$  allows output data bytes to be read  $(A_0 = "0" \text{ MSB byte}, A_0 = "1" \text{ LSB byte})$ . In the example below, R/C is returned high during the conversion, and A₀ is set so that the MSB byte is automatically enabled 300nsec before the end of the conversion cycle. After the MSB byte has been accessed by the system, the LSB byte is multiplexed to the data output lines by bringing A₀ high. Break-before-make action ensures that MSB and LSB data bytes will not be enabled at the same time. Data access time is 150nsec from the change of  $A_0$  ( $t_{R2}$  = 150nsec max.). If one desires,  $R/\bar{C}$  may remain low during the conversion, in which case, output data will not be enabled until Status is low and R/C is brought high. In this case, data access from  $R/\overline{C}=$  "1" is similarly 150nsec.

### **TIMING DIAGRAM**

**MN7145 Series Timing Parameters**

| Symbol            | Parameter                            | Min. | Тур. | Max. | Units |

|-------------------|--------------------------------------|------|------|------|-------|

| t <sub>ACQ</sub>  | T/H Acquisition Time                 | 10   | 6    |      | μsec  |

| t <sub>MUXH</sub> | Multiplexer Address Hold Time        | 1    |      |      | μsec  |

| t <sub>SA1</sub>  | A <sub>0</sub> Setup to R/C Low      | 0    |      | ļ    | nsec  |

| t <sub>SA2</sub>  | A <sub>0</sub> Setup to Status Low   | 100  | 50   |      | пѕес  |

| t <sub>HAR</sub>  | A <sub>0</sub> Valid During R/C Low  | 50   |      | l    | nsec  |

| t <sub>RC</sub>   | R/C Pulse Width                      | 50   |      |      | nsec  |

| tos               | Status Delay from R/C Low            |      | 100  | 200  | nsec  |

| t <sub>R1</sub>   | Status Delay After Data Valid        | 300  | 500  | 1000 | nsec  |

| t <sub>R2</sub>   | Data Access Time from A <sub>0</sub> |      | 60   | 150  | nsec  |

| t <sub>HL</sub>   | Data Valid After R/C Low             | 25   |      |      | nsec  |

| tcon              | Conversion Time:                     |      |      |      |       |

| 0011              | 8-Bit Cycle                          | 10   | 13   | 17   | μsec  |

|                   | 12-Bit Cycle                         | 15   | 20   | 25   | μsec  |

**OPTIONAL OFFSET AND GAIN ADJUSTMENTS**—MN7145 Series devices will operate as specified without additional adjustments. If desired, however, system absolute accuracy error can be improved by following the trimming procedure below. Adjustments should be made following warmup, and to avoid interaction, the offset adjustment should be made before the gain adjustment. Multiturn potentiometers with TCR's of 100ppm/°C or less are recommended to minimize drift with temperature. Series resistors can be  $\pm 20\%$  carbon composition or better. If these adjustments are not used, pins 20 and 21 should be left open. Do not ground. If gain and offset adjusting is performed on MN7145 Series devices, reference voltages may be applied to any of the analog input channels. It is recommended that offset and gain adjustments be made while the system is performing continuous or at least repeated conversions.

**OFFSET ADJUSTMENT**—Connect the offset potentiometer as shown below and apply an analog input voltage equivalent to  $+\frac{1}{2}$  LSB (MN7145) or  $-FS + \frac{1}{2}$  LSB (MN7146/7147). See Digital Output Coding section for the appropriate analog input voltages. While the device is performing repeated con-

versions, monitor the output and adjust the offset potentiometer "down" until all output bits are "0". Then adjust "up" until the LSB "flickers" on and off.

GAIN ADJUSTMENT—Connect the gain potentiometer as shown below and apply the analog input voltage equivalent to +FS - 1½ LSB. See Digital Output Coding section for the appropriate analog input voltages. While the device is performing repeated conversions, monitor the output and adjust the gain potentiometer "up" until all output bits are "1". Then adjust "down" until the LSB "flickers" on and off.

Pin 20 0 1.5M

$$\Omega$$

Pin 21 0 6M $\Omega$  20k $\Omega$  Pin 21 0 - 15V

OFFSET ADJUST GAIN ADJUST

**DIGITAL OUTPUTS**—MN7145 Series devices have 8 digital output lines (pins 1, 2, 23-28) on which a 12-bit data word can be read in two 8-bit bytes. In the read mode, the state of Ao determines if the MSB byte  $(A_0 = "0")$  or the LSB byte  $(A_0 = "1")$  is multiplexed to the digital output lines. Break-before-make action guarantees that the MSB and LSB bytes will not be enabled at the same time. Digital output data can only be read between conversions because output data lines are returned to the high impedance state whenever a conversion is in progress. See Pin Designations for data bit (DB0-DB11) assignments.

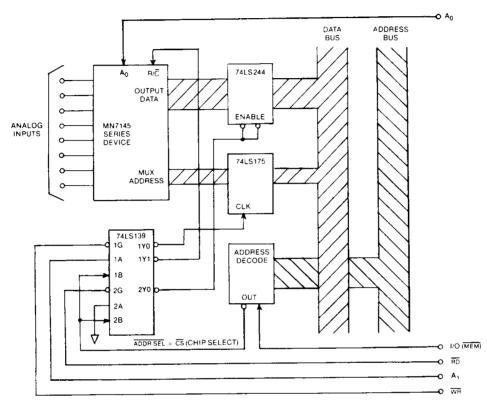

MICROPROCESSOR INTERFACE—The MN7145 Series DAS can be interfaced with most popular microprocessors. The DAS may be addressed either as a memory location (memory mapped) or as an I/O device. In the case of memory mapping, the DAS acts as a static RAM to which READ and WRITE instructions are given to the selected address. When the DAS is connected as an I/O device, the I/O ENABLE can be substituted for MEMORY ENABLE or I/OR and I/OW substituted for MEMR and MEMW. The accompanying diagram shows a typical scheme to implement this interface.

STS is not used in this example; the  $\mu$ P must read data 30 $\mu$ sec after conversion starts. This delay can be generated with NOP or other instructions inserted between the WRITE and READ functions. The STS line can also be used to cause the processor to WAIT or HALT or can be used as an interrupt line such as IREQ (in the case of 6800 or 6502).

## DIGITAL OUTPUT CODING

| Analog Input Voltage (Volts)     |                                  |                                  | Analog Input Voltage (Volts) Digital Outp |         |  | Output |

|----------------------------------|----------------------------------|----------------------------------|-------------------------------------------|---------|--|--------|

| MN7145                           | MN7146                           | MN7147                           |                                           |         |  |        |

| 0 to + 10V                       | ± 5V                             | ± 10V                            | MSB                                       | LSB     |  |        |

| + 10.0000<br>+ 9.9963            | + 5.0000<br>+ 4.9963             | + 10.0000<br>+ 9.9927            | 1111 111<br>1111 111                      |         |  |        |

| + 5.0012<br>+ 4.9988<br>+ 4.9963 | + 0.0012<br>- 0.0012<br>- 0.0037 | + 0.0024<br>- 0.0024<br>- 0.0073 | 1000 000<br>ØØØØ ØØØ<br>0111 111          | g øøøø* |  |        |

| + 0.0012<br>0.0000               | - 4.9988<br>- 5.0000             | - 9.9976<br>- 10.0000            | 0000 0000                                 |         |  |        |

#### **DIGITAL OUTPUT CODING NOTES:**

- 1. For unipolar input range, output coding is straight binary.

- For bipolar input ranges, output coding is offset binary. For 0 to  $\pm$  10V or  $\pm$  5V input ranges, 1LSB for 12 bits = 2.44mV. 1LSB for 11 bits = 4.88mV.

- 4. For  $\pm$  10V input range, 1LSB for 12 bits = 4.88mV. 1LSB for 11 bits = 9.77mV.

EXAMPLE: For an MN7147 operating on its ± 10V input range, the transition from digital output 0000 0000 0000 to 0000 0000 0001 (or vice versa) will ideally occur at an input voltage of -9.9976 volts. Subsequently, any input voltage more negative than -9.9976 volts will give a digital output of all "0's". The transition from digital output 1000 0000 0000 to 0111 1111 1111 will ideally occur at an input of -0.0024 volts, and the 1111 1111 1111 to 1111 1111 1110 transition will occur at + 9.9927 volts. An input more positive than + 9.9927 volts will give

<sup>\*</sup>Voltages given are the theoretical values for the transitions indicated. Ideally, with the converter continuously converting, the output bits indicated as Ø will change from "1" to "0" or vice versa as the input voltage passes through the level indicated.