# Preliminary Data Sheet

# D6005B

# **Digital Speech/ Signal Processor** for an All Digital **Answering Machine**

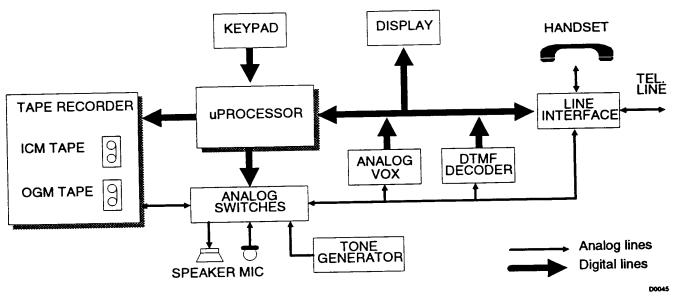

#### **GENERAL DESCRIPTION**

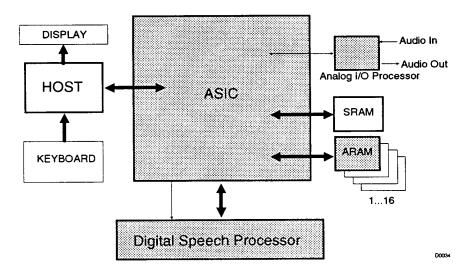

The D6005B chipset is a digital speech/signal processing subsystem that implements all the functions of speech compression, telephone line signal processing and memory management, for an all digital telephone answering machine. The D6005B is fully controlled by the system host through a simple interface protocol. The host processor provides activation and control of all chipset functions such as speech recording and playback, DTMF generation and line monitoring.

The fully digital solution uses no moving parts, yielding high reliability. The flexibility of a programmable system enables a range of answering device features for the end user. The D6005B includes a digital signal processor, analog I/O interface chip, ARAM memory, and an ASIC.

#### **FEATURES**

- High quality, low rate digital speech compres-

- Flexible storage of ICM/OGM

- Voice activated recording

- DTMF receive/transmit

- Near-end echo cancellation improves DTMF detection

- Highly reliable—no moving parts

- Minimal chip count

- Programmable, modular design

- 8-bit HOST interface

- Speed dial

- Telephone number storage

Figure 1. D6005B Block Diagram

All specifications are subject to change without prior notice

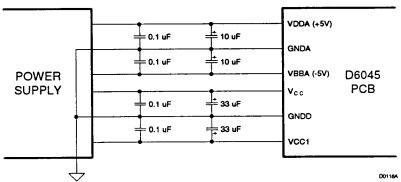

#### CHIPSET CONFIGURATION

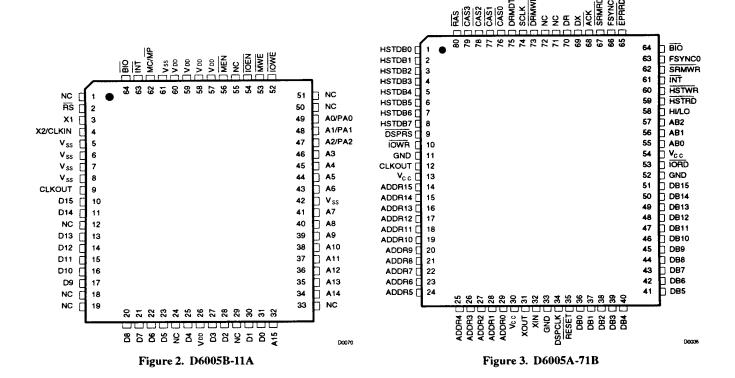

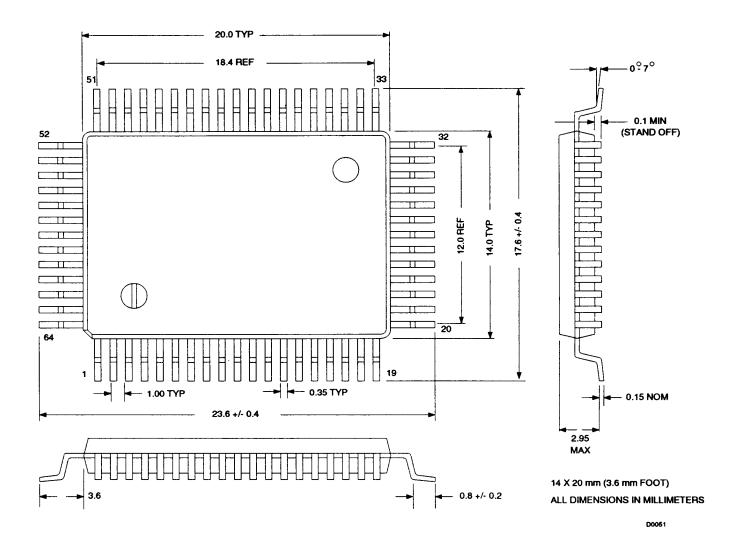

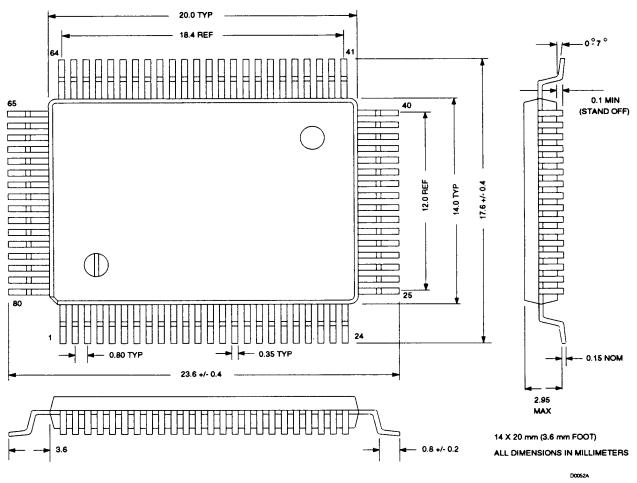

- D6005B-11A Digital Speech Processor (64-pin PQFP)—1 each

- D6005A-71B ASIC (80-pin PQFP)—1 each

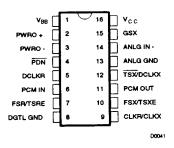

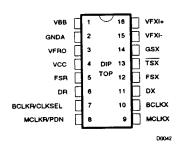

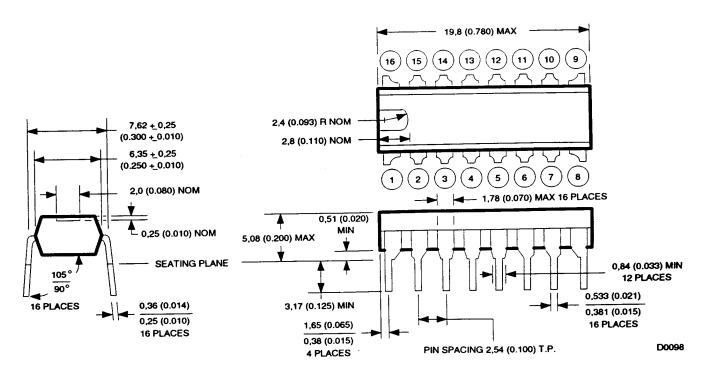

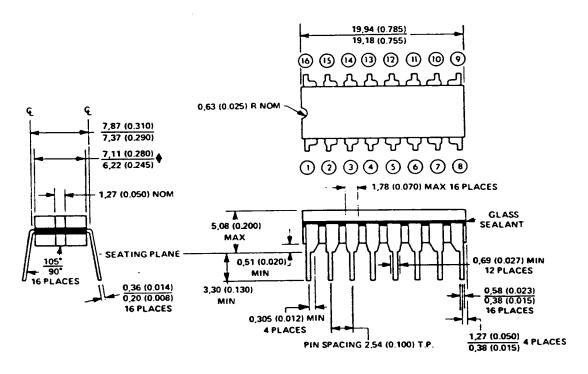

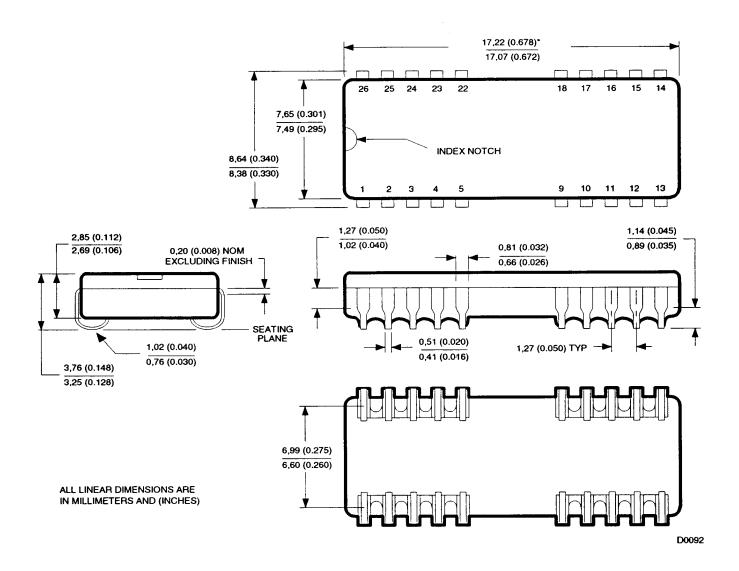

- D0000-26 or D0000-29 Analog I/O Interface (16-pin DIP)—1 each

- D0000-31A 1Mbit ARAM Message Memory (18-pin DIP or SOJ)—1 to 16 each or

D0000-34A 4Mbit ARAM Message Memory (SOJ)—1 to 4 each

Note: An 8K × 8 static RAM chip will be supplied by the customer.

Figure 4. D0000-26 DIP

Figure 5. D0000-29 DIP

Figure 6. D0000-31A DIP

Figure 7. D0000-31A SOJ

Figure 8. D0000-34A (SOJ)

#### **PIN DESCRIPTIONS**

| D6005B-11A | (DSP)      |        |                                                                                                                                                                                                                                                                |  |  |  |  |

|------------|------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| ADDRESS/   | DATA BUSES |        |                                                                                                                                                                                                                                                                |  |  |  |  |

| Pin        |            |        |                                                                                                                                                                                                                                                                |  |  |  |  |

| Name       | No.        | I/O/Z* | Description                                                                                                                                                                                                                                                    |  |  |  |  |

| A15 MSB    | 32         | 0      | Program memory address bus A15 (MSB) through A0 (LSB) and port addresses PA2 (MSB) through PA0                                                                                                                                                                 |  |  |  |  |

| A14        | 34         |        | (LSB). Addresses A15 through A0 are always active and never go to high impedance. During execution of the IN and OUT instructions, pins A2 through A0 carry the port addresses. (Address pins A15 through A3 are always driven low on IN and OUT instruction). |  |  |  |  |

| A13        | 35         |        |                                                                                                                                                                                                                                                                |  |  |  |  |

| A12        | 36         |        | , , , , , , , , , , , , , , , , , , ,                                                                                                                                                                                                                          |  |  |  |  |

| A11        | 37         |        |                                                                                                                                                                                                                                                                |  |  |  |  |

| A10        | 38         |        |                                                                                                                                                                                                                                                                |  |  |  |  |

| A9         | 39         |        |                                                                                                                                                                                                                                                                |  |  |  |  |

| A8         | 40         |        |                                                                                                                                                                                                                                                                |  |  |  |  |

| A7         | 41         |        |                                                                                                                                                                                                                                                                |  |  |  |  |

| A6         | 43         |        |                                                                                                                                                                                                                                                                |  |  |  |  |

| A5         | 44         |        |                                                                                                                                                                                                                                                                |  |  |  |  |

| A4         | 45         |        |                                                                                                                                                                                                                                                                |  |  |  |  |

| A3         | 46         |        |                                                                                                                                                                                                                                                                |  |  |  |  |

| A2/PA2     | 47         |        |                                                                                                                                                                                                                                                                |  |  |  |  |

| A1/PA1     | 48         |        |                                                                                                                                                                                                                                                                |  |  |  |  |

| A0/PA0     | 49         |        |                                                                                                                                                                                                                                                                |  |  |  |  |

| D15 MSB    | 10         | I/O/Z  | Parallel data bus D15 (MSB) through D0 (LSB). The data bus is always in the high-impedance state except                                                                                                                                                        |  |  |  |  |

| D14        | 11         |        | when IOWE or MWE are active (low).                                                                                                                                                                                                                             |  |  |  |  |

| D13        | 13         |        |                                                                                                                                                                                                                                                                |  |  |  |  |

| D12        | 14         |        |                                                                                                                                                                                                                                                                |  |  |  |  |

| D11        | 15         |        |                                                                                                                                                                                                                                                                |  |  |  |  |

| D10        | 16         |        |                                                                                                                                                                                                                                                                |  |  |  |  |

| D9         | 17         |        |                                                                                                                                                                                                                                                                |  |  |  |  |

| D8         | 20         |        |                                                                                                                                                                                                                                                                |  |  |  |  |

| D7         | 21         |        |                                                                                                                                                                                                                                                                |  |  |  |  |

| D6         | 22         |        |                                                                                                                                                                                                                                                                |  |  |  |  |

| D5         | 23         |        | 1                                                                                                                                                                                                                                                              |  |  |  |  |

| D4         | 25         |        |                                                                                                                                                                                                                                                                |  |  |  |  |

| D3         | 27         |        |                                                                                                                                                                                                                                                                |  |  |  |  |

| D2         | 28         |        | 1                                                                                                                                                                                                                                                              |  |  |  |  |

| DI         | 30         | 1      | 1                                                                                                                                                                                                                                                              |  |  |  |  |

| D0 LSB     | 31         |        | 1                                                                                                                                                                                                                                                              |  |  |  |  |

<sup>\*</sup>Input/Output/High-Impedance state.

| D6005B-11 | A (DSP)                                        |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|-----------|------------------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| INTERRU   | INTERRUPT AND MISCELLANEOUS SIGNALS            |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|           | Pin                                            |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| Name      | No.                                            | I/O/Z* | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| BIO       | 64                                             | I      | External polling input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| IOEN      | 54                                             | 0      | Data enable for device input data. When active (low), IOEN indicates that the device will accept data from the data bus. When IOEN is active, MEN, IOWE, and MWE will always be inactive (high).                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| ĪOWE      | 52                                             | 0      | Write enable for device output data. When active (low), $\overline{\text{IOWE}}$ indicates that data will be output from the device on the data bus. When $\overline{\text{IOWE}}$ is active, $\overline{\text{MEN}}$ , $\overline{\text{IOEN}}$ , and $\overline{\text{MWE}}$ will always be inactive (high).                                                                                                                                                                                                                                                                                                                                              |  |  |

| INT       | 63                                             | I      | External interrupt input. The interrupt signals generated by applying a negative-going edge to the INT pin. The edge is used to latch the interrupt flag register INTF) until an interrupt is granted by the device. An active low evel will also be sensed.                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| MC/MP     | 62                                             | I      | Memory mode select pin. High selects the microcomputer mode, in which internal on-chip program memory is available. This pin should be tied to VDD at all times.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| MEN       | 56                                             | 0      | Memory enable. MEN is an active low control signal generated by the device to enable instruction fetches from program memory. MEN will be active on instructions fetched from both internal and external memory. When MEN is active, MWE, TOWE, and IOEN will be inactive (high).                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| MWE       | 12                                             | 0      | Write enable for device output data. When active (low), MWE indicates that data will be output from the device on the data bus. When MWE is active, MEN, IOEN, and IOWE will always be inactive (high).                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| NC        | 1, 12, 18,<br>19, 24, 29,<br>33, 50, 51,<br>55 |        | No connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| RS        | 2                                              | I      | Schmitt-triggered input for initializing the device. When held active for a minimum of five clock cycles, $\overline{\text{IOEN}}$ , $\overline{\text{IOWE}}$ , $\overline{\text{MWE}}$ , and $\overline{\text{MEN}}$ are forced high; and, the data bus (D15 through D0) is not driven. The program counter (PC) and the address bus (A15 through A0) are then synchronously cleared after the next complete clock cycle from the falling edge of $\overline{\text{RS}}$ . Reset also disables the interrupt, clears the interrupt flag register, and leaves the overflow mode register unchanged. The device can be held in the reset state indefinitely. |  |  |

| SUPPLY/OS       | SUPPLY/OSCILLATOR SIGNALS |        |                                                                                                                                                                                             |  |  |

|-----------------|---------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin             |                           |        |                                                                                                                                                                                             |  |  |

| Name            | No.                       | I/O/Z* | Description                                                                                                                                                                                 |  |  |

| CLKOUT          | 9                         | 0      | System clock output (one-fourth crystal/CLKIN frequency).                                                                                                                                   |  |  |

| V <sub>DD</sub> | 26, 57, 58,<br>59, 60     | I      | 5V supply pins.                                                                                                                                                                             |  |  |

| V <sub>SS</sub> | 5, 6, 7, 8,<br>42, 61     | I      | Ground pins.                                                                                                                                                                                |  |  |

| X1              | 3                         | О      | Crystal output pin for internal oscillator. If the internal oscillator is not used, this pin should be left unconnected.                                                                    |  |  |

| X2/CLKIN        | 4                         | I      | Input pin to the internal oscillator (X2) from the crystal. Alternatively, an input pin for an external oscillator (CLKIN). The crystal or external oscillator frequency must be 22.25 MHz. |  |  |

| D0000-26 (Ar    |            | iteriace) |                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|-----------------|------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin             |            | 110.774   | The contest on                                                                                                                                                                                                                                                                                                                                                                                    |  |

| Name            | No. I/O/Z* |           | Description                                                                                                                                                                                                                                                                                                                                                                                       |  |

| V <sub>BB</sub> | 1          | PWR       | Negative supply voltage; -5V.                                                                                                                                                                                                                                                                                                                                                                     |  |

| PWRO+           | 2          | 0         | Noninverting output of power amplifier. Can drive transformer hybrids or high-impedance loads directly in either a differential or a single-ended configuration.                                                                                                                                                                                                                                  |  |

| PWRO-           | 3          | 0         | Inverting output of power amplifier; functionally identical with and complementary to PWRO+.                                                                                                                                                                                                                                                                                                      |  |

| PDN             | 4          | I         | Power-down select. The device is inactive with a TTL low-level input to this pin and active with a TTL high-level input to the pin.                                                                                                                                                                                                                                                               |  |

| DCLKR           | 5          | 1         | Selects fixed or variable data-rate operation. When this pin is connected to VBB, the device operates in the fixed data-rate mode. When DCLKR is not connected to VBB, the device operates in the variable-data-rate mode, and DCLKR becomes the receive data clock, which operates at frequencies from 64 KHz to 2.048 MHz.                                                                      |  |

| PCM IN          | 6          | I         | Receive PCM input. PCM data is clocked in on this pin on eight consecutive negative transitions of the receive data clock, which is CLKN in fixed-data-rate timing and DCLKR in variable-data-rate timing.                                                                                                                                                                                        |  |

| FSR/TSRE        | 7          | I         | Frame synchronization clock input/time slot enable for receive channel. In the fixed-data-rate mode, FSR distinguishes between signalling and non-signalling frames by a double- or single-length pulse, respectively. In the variable-data-rate mode, this signal must remain high for the duration of the timeslot. The receive channel enters the standby state when FSR is TTL low for 300ms. |  |

| DGTL GND        | 8          | PWR       | Digital ground for all internal logic circuits. Not internally connected to ANLG GND.                                                                                                                                                                                                                                                                                                             |  |

| CLKR/<br>CLKX   | 9          | I         | Transmit/Receive master clock and data clock for the fixed-data-rate mode. Transmit/Receive master clock only for variable-data-rate mode.                                                                                                                                                                                                                                                        |  |

| FSX/TSXE        | 10         | I         | Frame synchronization clock input/time-slot enable for transmit channel. Operates independently of, but in an analogous manner to, FSR/TSRE. The transmit channel enters the standby state when FSX is low for 300ms.                                                                                                                                                                             |  |

| PCM OUT         | 11         | 0         | Transmit PCM output. PCM data is clocked out on this output on eight consecutive positive transitions of the transmit data clock, which is CLKX in fixed-data-rate timing and DCLKX in variable-date-rate timing.                                                                                                                                                                                 |  |

| TSX/<br>DCLKX   | 12         | 1/0       | Transmit channel time slot strobe (output) or data clock (input) for the transmit channel. In the fixed-data-rate mode, this pin is an open-drain output to be used as an enable signal for a three-state buffer. In the variable-data-rate mode, DCLKX becomes the transmit data clock, which operates at TTL levels from 64 KHz to 2.048 MHz.                                                   |  |

| ANLG GND        | 13         | PWR       | Analog ground return for all internal voice circuits. Not internally connected to DGTL GND.                                                                                                                                                                                                                                                                                                       |  |

| ANLG IN-        | 14         | I         | Inverting analog input to uncommitted transmit operational amplifier.                                                                                                                                                                                                                                                                                                                             |  |

| GSX             | 15         | 0         | Output terminal of internal uncommitted operational amplifier. Internally, this is the voice signal input to the transmit filter.                                                                                                                                                                                                                                                                 |  |

| VCC             | 16         | PWR       | Positive supply voltage; 5V.                                                                                                                                                                                                                                                                                                                                                                      |  |

| D0000-29 (Analog I/O Interface) |     |        |                                                                                                                                                                                                         |  |

|---------------------------------|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin                             |     |        |                                                                                                                                                                                                         |  |

| Name                            | No. | I/O/Z* | Description                                                                                                                                                                                             |  |

| V <sub>BB</sub>                 | 1   | PWR    | Negative power supply pin. $V_{BB} = -5V$                                                                                                                                                               |  |

| GNDA                            | 2   | PWR    | Analog ground. All signals are referenced to this pin.                                                                                                                                                  |  |

| VFRO                            | 3   | 0      | Analog output of the receive power amplifier.                                                                                                                                                           |  |

| Vcc                             | 4   | PWR    | Positive power supply pin. VCC = +5V.                                                                                                                                                                   |  |

| FSR                             | 5   | I      | Receive frame sync pulse which enables BCLKR to shift PCM data into DR.                                                                                                                                 |  |

| DR                              | 6   | I      | Receive data input. PCM data is shifted into DR following the FSR leading edge.                                                                                                                         |  |

| BCLKR/<br>CLKSEL                | 7   | I      | Logic input which selects either 1.536 MHz/1.544 MHz or 2.048 MHz for master clock in synchronous mode and BCLKx is used for both transmit and receive directions. This input should be tied to ground. |  |

| MCLKR/<br>PDN                   | 8   | I      | Receive master clock. When MCLKR is connected continuously low, MCLKX is selected for all internal timing. When MCLKR is connected continuously high, the device is powered down.                       |  |

| MCLKX                           | 9   | I      | Transmit master clock. Must be 1.536 MHz, 1.544 MHz or 2.048 MHz. May be asynchronous with MCLKR. Best performance is realized from synchronous operation.                                              |  |

| BCLKX                           | 10  | I      | The bit clock which shifts out the PCM data on DX. May vary from 64 KHz to 2.048 MHz, but must be synchronous with MCLKX.                                                                               |  |

| Dx                              | 11  | O/Z    | PCM data output which is enabled by FSX.                                                                                                                                                                |  |

| FSX                             | 12  | I      | Transmit frame sync pulse input which enables BCLKX to shift out the PCM data on DX. FSX is an 8 KHz pulse train.                                                                                       |  |

| TSX                             | 13  | 0      | Open drain output which pulses low during the encoder time slot.                                                                                                                                        |  |

| GSX                             | 14  | 0      | Analog output of the transmit input amplifier. Used to externally set gain.                                                                                                                             |  |

| VF <sub>X</sub> I <sub>-</sub>  | 15  | I      | Inverting input of the transmit input amplifier.                                                                                                                                                        |  |

| VFxI+                           | 16  | I      | Non-inverting input of the transmit input amplifier.                                                                                                                                                    |  |

| D0000-31                | D0000-31 (SOJ) |        |                                                                                                              |  |  |

|-------------------------|----------------|--------|--------------------------------------------------------------------------------------------------------------|--|--|

| Pin                     |                |        |                                                                                                              |  |  |

| Name                    | No.            | I/O/Z* | Description                                                                                                  |  |  |

| <b>A</b> 0              | 9              | 1      | Row and column address bits. Row address bits are latched in the chip by the RAS signal. Column address bits |  |  |

| Al                      | 10             | I      | are latched in by the CAS signal.                                                                            |  |  |

| A2                      | 11             | 1      |                                                                                                              |  |  |

| A3                      | 12             | I      |                                                                                                              |  |  |

| A4                      | 14             | I      |                                                                                                              |  |  |

| A5                      | 15             | I      |                                                                                                              |  |  |

| A6                      | 16             | I      |                                                                                                              |  |  |

| A7                      | 17             | 1      |                                                                                                              |  |  |

| A8                      | 18             | I      |                                                                                                              |  |  |

| A9                      | 22             | 1      |                                                                                                              |  |  |

| RAS                     | 3              | I      | Row address strobe                                                                                           |  |  |

| CAS                     | 24             | I      | Column address strobe                                                                                        |  |  |

| D                       | 1              | I      | Data input                                                                                                   |  |  |

| Q                       | 25             | 0      | Data output                                                                                                  |  |  |

| $\overline{\mathbf{w}}$ | 2              | I      | Write enable input which selects read or write mode                                                          |  |  |

| VCC                     | 13             | -      | +5V supply                                                                                                   |  |  |

| VSS                     | 26             | _      | Ground                                                                                                       |  |  |

| TF                      | 4              | I      | No connection                                                                                                |  |  |

| D0000-34                | (SOJ) |        |                                                                                                              |  |

|-------------------------|-------|--------|--------------------------------------------------------------------------------------------------------------|--|

| Pin                     |       |        |                                                                                                              |  |

| Name                    | No.   | I/O/Z* | Description                                                                                                  |  |

| A0                      | 9     | I      | Row and column address bits. Row address bits are latched in the chip by the RAS signal. Column address bits |  |

| Al                      | 10    | I      | are latched in by the CAS signal.                                                                            |  |

| A2                      | 11    | I      |                                                                                                              |  |

| A3                      | 12    | 1      |                                                                                                              |  |

| A4                      | 14    | I      |                                                                                                              |  |

| A5                      | 15    | I      |                                                                                                              |  |

| A6                      | 16    | I      |                                                                                                              |  |

| A7                      | 17    | I      |                                                                                                              |  |

| A8                      | 18    | I      |                                                                                                              |  |

| A9                      | 22    | I      |                                                                                                              |  |

| A10                     | 5     | 1      |                                                                                                              |  |

| RAS                     | 3     | I      | Row address strobe                                                                                           |  |

| CAS                     | 24    | I      | Column address strobe                                                                                        |  |

| D                       | 1     | I      | Data input                                                                                                   |  |

| Q                       | 25    | 0      | Data output                                                                                                  |  |

| $\overline{\mathbf{w}}$ | 2     | I      | Write enable input which selects read or write mode                                                          |  |

| VCC                     | 13    | -      | +5V supply                                                                                                   |  |

| vss                     | 26    | -      | Ground                                                                                                       |  |

| TF                      | 4     | I      | No connection                                                                                                |  |

| D6005A-71I |     |                    |                          |  |

|------------|-----|--------------------|--------------------------|--|

| Pin        |     | ⊢ <sub>VO/Z*</sub> | Description              |  |

| Name       | No. |                    |                          |  |

| AB0        | 55  | 1                  | DSPADDRESS               |  |

| AB1        | 56  | I                  | DSPADDRESS               |  |

| AB2        | 57  | I                  | DSPADDRESS               |  |

| ACK        | 68  | 0                  | HOST INTERRUPT           |  |

| ADDR0      | 29  | 0                  | MEMORY ADDRESS BUS (LSB) |  |

| ADDRI      | 28  | 0                  | MEMORY ADDRESS           |  |

| ADDR2      | 27  | 0                  | MEMORY ADDRESS           |  |

| ADDR3      | 26  | 0                  | MEMORY ADDRESS           |  |

| ADDR4      | 25  | 0                  | MEMORY ADDRESS           |  |

| ADDR5      | 24  | 0                  | MEMORY ADDRESS           |  |

| ADDR6      | 23  | 0                  | MEMORY ADDRESS           |  |

| ADDR7      | 22  | 0                  | MEMORY ADDRESS           |  |

| ADDR8      | 21  | 0                  | MEMORY ADDRESS           |  |

| ADDR9      | 20  | 0                  | MEMORY ADDRESS           |  |

| ADDR10     | 19  | 0                  | MEMORY ADDRESS           |  |

| ADDR11     | 18  | 0                  | MEMORY ADDRESS           |  |

| ADDR12     | 17  | 0                  | MEMORY ADDRESS           |  |

| ADDR13     | 16  | 0                  | MEMORY ADDRESS           |  |

| ADDR14     | 15  | 0                  | MEMORY ADDRESS           |  |

| ADDR15     | 14  | 0                  | MEMORY ADDRESS BUS (MSB) |  |

| BIO        | 64  | 0                  | DSP BIO                  |  |

| CAS0       | 76  | 0                  | ARAM CAS                 |  |

| CAS1       | 77  | 0                  | ARAM CAS                 |  |

| CAS2       | 78  | 0                  | ARAM CAS                 |  |

| CAS3       | 79  | 0                  | ARAM CAS                 |  |

| RAS        | 80  | 0                  | ARAM RAS                 |  |

| DB0        | 36  | I/O/Z              | DSP DATA BUS (LSB)       |  |

| DB1        | 37  | 1/O/Z              | DSP DATA BUS             |  |

| DB2        | 38  | I/O/Z              | DSP DATA BUS             |  |

| DB3        | 39  | I/O/Z              | DSP DATA BUS             |  |

| DB3<br>DB4 | 40  | I/O/Z              | DSP DATA BUS             |  |

| DB5        | 41  | I/O/Z              | DSP DATA BUS             |  |

|            |     | I/O/Z              | DSP DATA BUS             |  |

| DB6        | 42  | VO/Z               | DSP DATA BUS             |  |

| DB7        |     |                    | DSP DATA BUS             |  |

| DB8        | 44  | 1/0/Z              |                          |  |

| DB9        | 45  | 1/O/Z              | DSP DATA BUS             |  |

| DB10       | 46  | I/O/Z              | DSP DATA BUS             |  |

| DB11       | 47  | I/O/Z              | DSP DATA BUS             |  |

| DB12       | 48  | I/O/Z              | DSP DATA BUS             |  |

| DB13       | 49  | I/O/Z              | DSP DATA BUS             |  |

| DB14       | 50  | I/O/Z              | DSP DATA BUS             |  |

| DB15       | 51  | I/O/Z              | DSP DATA BUS (MSB)       |  |

| DR         | 70  | I                  | PCM IN                   |  |

| NC         | 72  | I                  |                          |  |

| DRMDT      | 75  | 1/O/Z              | ARAM DATA                |  |

# PIN DESCRIPTIONS (CONTINUED)

| D6005A-71E |     |        |                             |  |

|------------|-----|--------|-----------------------------|--|

| Pin        |     |        |                             |  |

| Name       | No. | I/O/Z* | Description                 |  |

| DRMWR      | 73  | 0      | ARAM WRITE                  |  |

| DSPCLK     | 34  | 0      | DSP CLOCK                   |  |

| DSPRS      | 9   | 0      | DSP RESET                   |  |

| DX         | 69  | 0      | PCM OUT                     |  |

| NC         | 71  | 0      |                             |  |

| FSYNC0     | 63  | 0      | CODECO FS YNC               |  |

| FSYNC1     | 66  | 0      | CODECI FSYNC                |  |

| HI/LO      | 58  | I      | HIGH/LOW BYTE SELECT        |  |

| HSTDB0     | 1   | I/O/Z  | HOST DATA BUS               |  |

| HSTDB1     | 2   | I/O/Z  | HOST DATA BUS               |  |

| HSTDB2     | 3   | 1/O/Z  | HOST DATA BUS               |  |

| HSTDB3     | 4   | I/O/Z  | HOST DATA BUS               |  |

| HSTDB4     | 5   | I/O/Z  | HOST DATA BUS               |  |

| HSTDB5     | 6   | 1/O/Z  | HOST DATA BUS               |  |

| HSTDB6     | 7   | 1/O/Z  | HOST DATA BUS               |  |

| HSTDB7     | 8   | I/O/Z  | HOST DATA BUS               |  |

| HSTRD      | 59  | I      | HOST READ                   |  |

| HSTWR      | 60  | I      | HOST WRITE                  |  |

| ĪNT        | 61  | 0      | DSP INTERRUPT               |  |

| IORD       | 53  | I      | DSP IO READ                 |  |

| ĪOWR       | 10  | I      | DSP IO WRITE                |  |

| RESET      | 35  | I      | ACTIVE LOW ASIC RESET INPUT |  |

| SCLK       | 74  | 0      | CODEC SER. CLK              |  |

| SRMRD      | 67  | 0      | SRAM READ                   |  |

| SRMWR      | 62  | 0      | SRAM WRITE                  |  |

| EPRRD      | 65  | 0      | EPROM READ                  |  |

| XIN        | 32  | ı      | XTAL IN                     |  |

| XOUT       | 31  | 0      | XTAL OUT                    |  |

| CLKOUT     | 12  | I      | DSP CLKOUT                  |  |

| GND        | 52  | PWR    | GROUND PIN                  |  |

| GND        | 33  | PWR    | GROUND PIN                  |  |

| GND        | 11  | PWR    | GROUND PIN                  |  |

| Vcc        | 54  | PWR    | 5V PIN                      |  |

| Vcc        | 30  | PWR    | 5V PIN                      |  |

| Vcc        | 13  | PWR    | 5V PIN                      |  |

NOTE: CODEC 1 and EPROM interfaces are reserved for advanced features.

#### **FUNCTIONAL DESCRIPTION**

# Voice Message Storage—Incoming and Outgoing Messages

The D6005B chipset supports up to 26 minutes of voice storage. The voice messages are stored in audio grade RAMs (ARAMs) in configurations of 4-Mbit or 1-Mbit devices. The chipset enables the recording of a total of up to 64 variable length incoming and outgoing messages. Multiple outgoing messages are supported. The message storage memory may be enlarged by adding memory chips up to a total of 16 Megabits. Each 1 Megabit memory chip allows an additional message storage time of 103 seconds.

The D6005B message storage uses a proprietary high quality speech compression technique at a rate of 10.2 Kbps. The compression technique used is enhanced by an error correction algorithm that enables use of ARAM (Audio grade DRAMs) memory without degradation of speech quality.

The D6005B is capable to report to the host the status of the currently available memory storage area, as well as the overall status of the ARAMs (number of recorded messages).

#### Digital voice activated recording (VOX)

The digital speech detection is implemented in the DSP chip. The DSP chip performs speech detection at 22ms intervals, at the end of which it indicates to the HOST whether a speech frame has been detected. The HOST reads this status information and decides accordingly whether to stop the recording of this message. During recording, the D6005B performs telephone line monitoring. The host is capable of terminating the recording with a deletion of the last n\*0.7 seconds from the memory (Tail Cut function).

#### Playback of Messages

The D6005B supports random playback of any message previously recorded. Playback from the beginning or from a predefined offset time may be performed. During the playback, the D6005B performs monitoring of the telephone line.

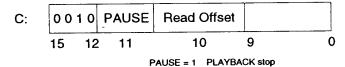

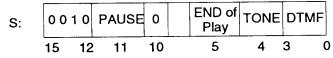

#### Pause and Offset Report

The playback of the prerecorded message can be stopped by a PAUSE command, initiated by the host. The DSP responds with a time offset (from the beginning of the current message) information if Read Offset bit (bit 10) was set. The offset may be received on a continuous basis during normal playback as well. After PAUSE, playback may be resumed from the same point.

#### Message Deletion

The D6005B enables random deletion of any prerecorded message from the memory. After each deletion message directory is updated accordingly. To improve memory utilization, the D6005B supports "Garbage Collection," which eliminates empty spaces in the message memory.

#### Time Stamp of Messages

The host may send a 16-bit time indication to the D6005B, which can be used for time stamping of the message recorded.

#### **DTMF Detection**

The DTMF detection is implemented by the DSP in software. This function may be used for remote control operation of the answering device. The identification code of one of 12 detected DTMF signals is transferred to the host for further processing.

#### **Tone Generation**

DTMF signals are generated in accordance with the requirements of EIA RS-470. Voice processing is disabled during DTMF generation. Each tone pair may be selected by a host controller command. Thus, the duration of the tone is controlled by the host. The host processor controls the tone signal level.

#### Call Progress Tone

The D6005B monitors the line for incoming telephone line signals and detects the presence of a call progress tone in a predefined frequency region. The D6005B supports Call Progress Tones detection by utilizing one out of two filter/detectors. Selection of the detector is done during initialization (Self Test). The wide filter is 335-650 Hz and the narrow one is 330-500 Hz. Indication of call progress tone presence is transferred to the host processor every 22ms.

#### Speed Dial Telephone Number Storage

The host may store in the static RAM controlled by the D6005B up to 32 different telephone numbers, each with up to 16 digits.

#### Self Test and Parameter Initialization

The D6005B supports a self test function which is responsible for testing of both the ARAMs and the SRAM. Status indication about the success of each device test is returned to the host.

#### **HOST Interface**

The host interface is an 8-bit parallel data port, used for control and status information transfer. The host controls the operation of the D6005B using a simple command protocol. The D6005B status information is updated after each command.

The command and status protocol enables the host to have full control over the functions of the D6005B. The protocol is described in the next section.

#### MODES OF OPERATION

There are 13 modes of operation. The entrance to each of these modes from the monitor program is made through an IDLE mode. Following is the list of the 13 modes:

- IDLE—In this mode the DSP performs command polling. It checks the command register in the HOST-DSP interface and transfers to the requested operation mode.

- Record mode—In this mode the DSP performs speech compression and message recording into the ARAM.

- 3. Playback mode—In this mode the DSP performs message playback using compressed speech data stored in the ARAM.

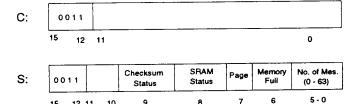

- 4. Read Memory status—In this mode the DSP returns to the HOST information on the Memory status (Number of messages stored, availability of memory for recording the next message, ROM checksum and SRAM status).

- Write Tel. #—In this mode the DSP receives a 16 digit telephone number from HOST and stores it in the SRAM in the telephone number directory.

- Read Tel. #—In this mode the DSP returns to the HOST a telephone number stored in the telephone directory under the index number given by the HOST.

- 7. Tone generation mode—In this mode the DSP generates a tone signal a dual tone out of 16 or one of 15 general purpose tones. The index number of the tone to be generated is sent by the HOST in the command word.

- 8. Line monitoring mode—In this mode the DSP monitors the telephone line for detection of either a DTMF signal or any other Call Progress tone. The DSP reports on any such detection to the HOST in the status word.

- 9. Delete message—In this mode the DSP erases the memory message entry whose ID is specified by the HOST from the messages directory. It then shifts all the other entries one entry down. If the message entry number sent by the HOST is 7FH, the DSP performs a "Garbage Collection" process, getting rid of unused memory space between messages.

- Write current time—In this mode the HOST sends to the DSP the current time & date stamp.

- 11. Get time stamp—In this mode the DSP returns to the HOST the time & date stamp pertaining to the message whose ID is specified by the HOST in the command word.

- 12 Get available record time—In this mode the DSP reports available record time.

- 13. Self test & Init ARAM —In this mode the DSP performs Static RAM and DRAM testing. The test results are returned to the HOST indicating the status of SRAM and ARAMs.

#### **DESCRIPTION OF MODES OF OPERATION**

#### **IDLE** mode

This is a polling mode in which the DSP monitors the DSP-HOST interface waiting for HOST commands. Transition to any other mode is always done through the IDLE MODE.

#### Record mode

In this mode the DSP performs speech compression and message recording into the ARAM. The DSP starts to store the message to ARAM after detecting VOX. While in this mode, the DSP continuously monitors (every 22ms) a communication port for HOST command. If no new command has been detected, the DSP continues message recording. If a new command detected is a record command, the DSP returns the VOX, line monitoring (tone detection information) and ARAM status to the HOST. Otherwise the DSP ends recording, updates the message directory and returns to IDLE mode. The DSP indicates this to the HOST by sending the IDLE mode status word.

When the DSP is in RECORD mode, the host can stop recording of message with a deletion of the last n\*0.7 seconds from the memory (Tail Cut function). After this command the DSP returns to IDLE mode.

The Memory Full (bit 5) in the status word is set if the ARAM is full. In the case that the ARAM is full, the DSP remains in record mode, stops recording, but continues to perform line monitoring and VOX functions.

#### Playback mode

In playback mode, the DSP performs message playback and line monitoring. This mode is entered upon receiving a playback command while in IDLE mode. The DSP returns the same word as a status command. The second word that the HOST sends to the DSP is an OFFSET indicating where to start playback from the beginning of the message, in units of 1.4 seconds. The DSP returns the OFFSET word to the HOST. Then, it begins playing the message from that point on.

The DSP checks the HOST port every 22ms for new commands. If no new command has been detected, the DSP continues to play the message. If the new command is not a Playback command, the DSP exits Playback mode and returns to IDLE mode. It indicates this to the HOST by sending the IDLE mode status word. During playback, the host can read the offset and pause the recording by issuing respective additional playback commands.

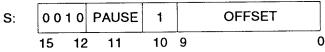

#### **Read Memory Status**

In this mode the DSP returns to the HOST the status of the ARAM indicating whether there is space in the ARAM for recording of a new message. It also returns the number of the last message recorded. When 64 messages were recorded or when there is no available memory space for recording further messages, Memory Full bit is set. When 64 messages were recorded, 8 LSB bits of status word are '1'.

The SRAM self test includes writing of fixed patterns to predefined locations. SRAM status bit indicates whether reading back these patterns back and comparing them to its known values was successful. The checksum status indicates result of DSP internal ROM checksum test.

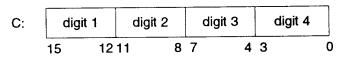

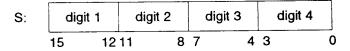

#### WriteTelephone Number

In this mode the DSP receives from the HOST a word containing 4 telephone digits and writes it in the telephone directory under the entry number specified in the command word (the first word). The DSP automatically returns to the IDLE mode after this command.

#### Read Telephone Number

In this mode the DSP returns to the HOST a word containing 4 telephone digits from the telephone directory using the entry specified in the first command word.

#### Tone Generation mode

In this mode the DSP generates a DTMF signal or one of 15 general purpose tones. The index for the signal/tone to be generated is sent by the HOST in the command word.

The indices are as follows:

| GEN CODE | DTMF CODE | FREQ 1 | FREQ 2 |

|----------|-----------|--------|--------|

| 0        | No Tone   |        |        |

| 1        | 1         | 697    | 1209   |

| 2        | 2         | 697    | 1336   |

| 3        | 3         | 697    | 1477   |

| 4        | 4         | 770    | 1209   |

| 5        | 5         | 770    | 1336   |

| 6        | 6         | 770    | 1477   |

| 7        | 7         | 852    | 1209   |

| 8        | 8         | 852    | 1336   |

| 9        | 9         | 852    | 1447   |

| Α        | *         | 941    | 1209   |

| В        | 0         | 941    | 1336   |

| С        | #         | 941    | 1477   |

| D        |           | 800    |        |

| E        |           | 1000   |        |

| F        |           | 1250   |        |

| 10       |           | 950    |        |

| 11       |           | 1100   |        |

| 12       |           | 1400   |        |

| 13       |           | 1500   |        |

| 14       |           | 1600   |        |

| 15       |           | 1800   |        |

| 16       |           | 2100   |        |

| 17       |           | 1300   |        |

| 18       |           | 2450   |        |

| 19       |           | 350    | 440    |

| 1A |   | 440 | 480  |

|----|---|-----|------|

| 1B |   | 480 | 620  |

| 1C | A | 697 | 1633 |

| 1D | В | 770 | 1633 |

| 1E | С | 852 | 1633 |

| 1F | D | 941 | 1633 |

The DSP checks the host port every 22ms for a new HOST command. Whenever a new tone generation command is sent, the DSP retrieves the tone index from command word and starts generating the new tone. In case that the command is not a TONE generation command, the DSP returns to the IDLE mode.

If no new command is sent, the DSP continues generating the previously generated tone.

#### Line Monitoring mode

In this mode the DSP monitors the telephone line for the detection of a DTMF signal or any of the Call Progress tones. Again, the DSP checks for a new HOST command each 22ms.

In case that HOST sends a Line monitoring command, the DSP returns a status word to the HOST containing the index of the signal that has been detected:

| INDEX | DESCRIPTION                  |  |

|-------|------------------------------|--|

| 0     | No signal has been detected. |  |

| 1-12  | A DTMF signal ID.            |  |

In addition the status word reports the presence of a Call Progress tone.

If the command is not a Line monitoring command, the DSP returns to the IDLE mode. In case that no command has been sent, it continues in the Line monitoring mode.

#### Delete Message

In this mode the DSP performs one of the following two functions:

- 1. If the message number is from 0 to 63, the DSP removes the message entry from the message directory and shifts all message entries above one place down in the directory. It then updates the last message number to be lower by one.

- 2. If the message number is 7FH, the DSP performs GARBAGE COLLECTION to get rid of empty spaces in the message memory. It then updates the message directory accordingly. When the DSP completes performing this process, it sends a status word to the HOST.

#### Write Current Time

In this mode the HOST sends to the DSP the current time & date mark that will be used for time stamping of the next message to be recorded. This time stamp is attached to the message and can be retrived by Get Time Stamp command.

#### **Get Time Stamp**

In this mode the DSP sends to the HOST the time & date stamp of the message specified in the command word.

#### Get Available Record Time

In this mode, the DSP sends to the HOST the available record time in 1.4s units.

#### Self Test & Init ARAM

In this mode the DSP performs testing of both the Static RAM and the ARAM. The DSP returns status bits indicating Pass or Fail for SRAM and ARAM memory space status. This command erases the contents of both SRAM and ARAMs. Therefore, it should be used only on first power-up.

In addition this command selects which call progress tone filter will be used - narrow or wide. The host processor can skip the initialization of the SRAM and ARAM memory and just select call progress filter.

If the memories were not initialized after first power-up, the D6005B assumes that the system has 16 Mbit ARAM memory.

#### **HOST INTERFACE PERFORMANCE**

The D6005B maximal response times to host commands are listed on the following table:

| COMMAND                                   | MAX STAT US<br>RESPONSE TIME |

|-------------------------------------------|------------------------------|

| Idle                                      | 22 msec                      |

| Record                                    | 22 msec                      |

| First Playback                            | 1 msec                       |

| Second Playback (offset)                  | 1 msec                       |

| Next Playback (continue)                  | 22 msec                      |

| Line Monitor                              | 22 msec                      |

| Delete Message without Garbage Collection | 1 msec                       |

| Delete Message with Garbage Collection    | 5 sec **                     |

| Set Current Time                          | 1 msec                       |

| Get Time                                  | 1 msec                       |

| Get Available Record Time                 | 1 msec                       |

| Read ARAM Status                          | 1 msec                       |

| Write Telephone Number                    | 1 msec                       |

| Read Telephone Number                     | 1 msec                       |

| DTMF Generation                           | 1 msec ***                   |

| Self Test                                 | 40 sec *                     |

- \* execution time for 6005B system with 8 Mbit ARAM

- \*\* execution time for D6005B system with 7 minutes of recorded messages

- \*\*\* status response is less than 1 ms. The tone is generated in less than 5 ms.

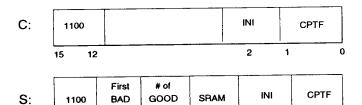

## 0. IDLE

- C: 0000 | 15 12 0

# 1. Record

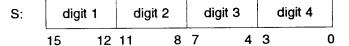

- C: 0 0 0 1 15 12 0

- S: 0 0 0 1 VOX MEMORY TONE DTMF 15 12 6 5 4 3 0

(The last command in RECORD mode)

- C: 0 0 0 1 1 0 00000 TAIL CUT FACTOR 15 12 11 10 5 0

- S: 0 0 0 1 1 0 00000 TAIL CUT FACTOR 15 12 11 10 5 0

Cutting Factor – Message tail cutting in units of 0.7 seconds. 00000 – Message tail is not cut.

NOTE: This command is optional and does not have to be sent.

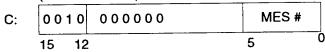

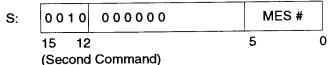

# 2. Playback

#### (First Command)

The next Playback command is a playback internal command for monitoring the playback mode:

PAUSE = 0 Continue PLAYBACK

If Read Offset = 1 then:

If Read Offset = 0 then:

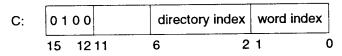

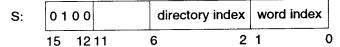

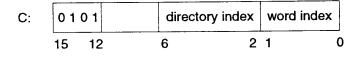

# 3. Read Memory Status

12 11

7

Page = 1 for messages #64 - 126 (reserved) SRAM status and Checksum status - '0' when OK. When set indicate error.

# Write Telephone Number

# **Read Telephone Number**

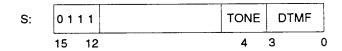

#### 6. Tone Generation

#### TONE LEVEL **TONE CODE** C: 0110 15

1-12, 28 - 31 DTMF 13 - 27 General purpose tones

TONE LEVEL = 0000 - Normal (0 dB = 0.267 V RMS) 0001 - 0111 - Gain level (+2dB steps)

1001 - 1111 - Attenuation level (-2dB steps) S:

NOTE: DTMF levels are -1 dB for DTMFLO and +1 dB for DTMFHI relative to the tone level.

Gain of 14 dB is not supported.

#### 7. Line Monitor

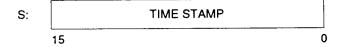

# 10. Get Time Stamp

9. Set Current Time

1001

1001

12

12

15

15

15

15

C:

S:

C:

TIME STAMP

TIME STAMP

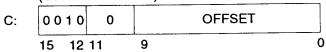

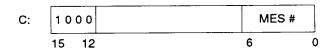

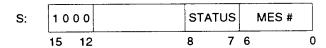

# **Delete Message**

MES #: 0 - 63

Del MES.

127 -Garbage Collection

STATUS: 00 - OK

> 01 - Empty Message 10 - Garbage Collection

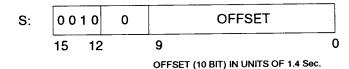

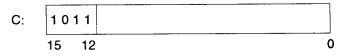

# 11. Get Available Record Time

AVAILABLE TIME: in units of 1.4 Sec.

0

0

0

0

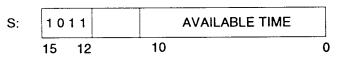

# 12. Self Test & Initialize Memory

ARAMS

8 7

3

2

0

No. of GOOD ARAMS – no. of good 1Mbit ARAMS (If 16 then = 0000 and index of 1st bad = 0001)

INDEX OF FIRST BAD ARAM -

ARAM

12 11

Position of 1st BAD ARAM from the beginning of ARAM ARRAY

SRAM STATUS - 0 SRAM OK

1 SRAM BAD

CPTF - Call Progress Tone Filter

00 = Narrow (330 - 530 Hz) 01 = Wide (330 - 660 Hz)

INI - Memory Initialize

0 = Initialize memory

I = Do not initialize memory

#### **FUNCTIONAL BLOCKS**

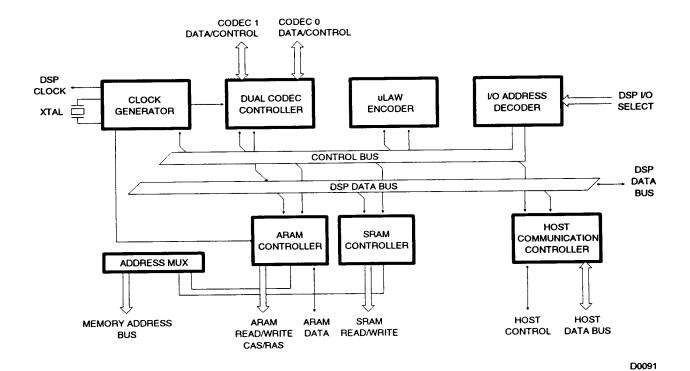

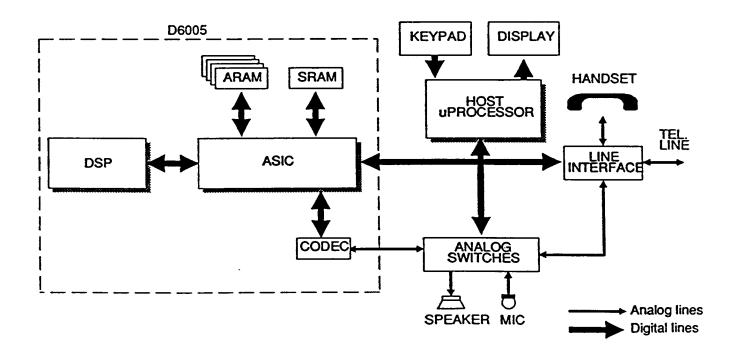

The block diagram in Figure 10 shows the D6005A-71B and its functional blocks and interfaces.

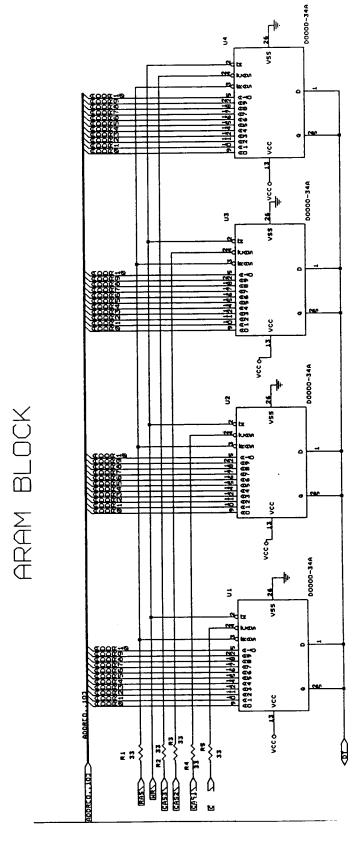

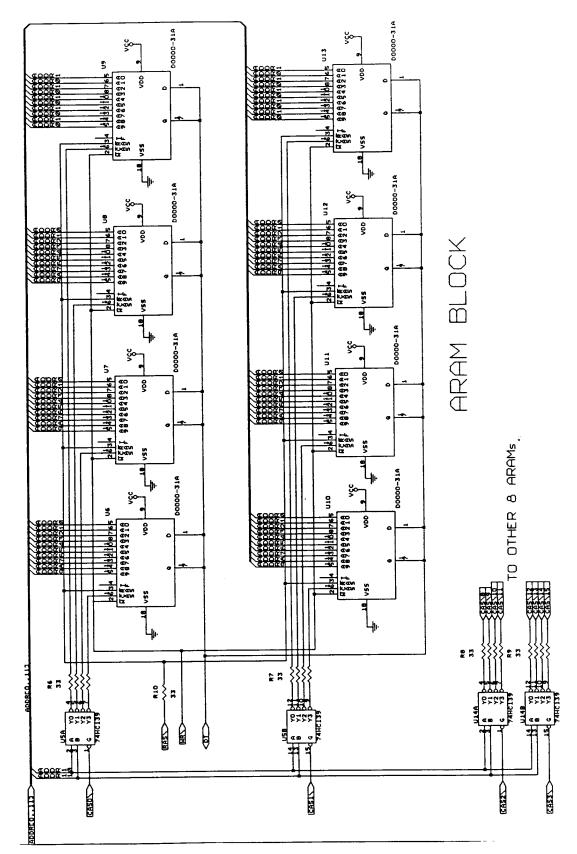

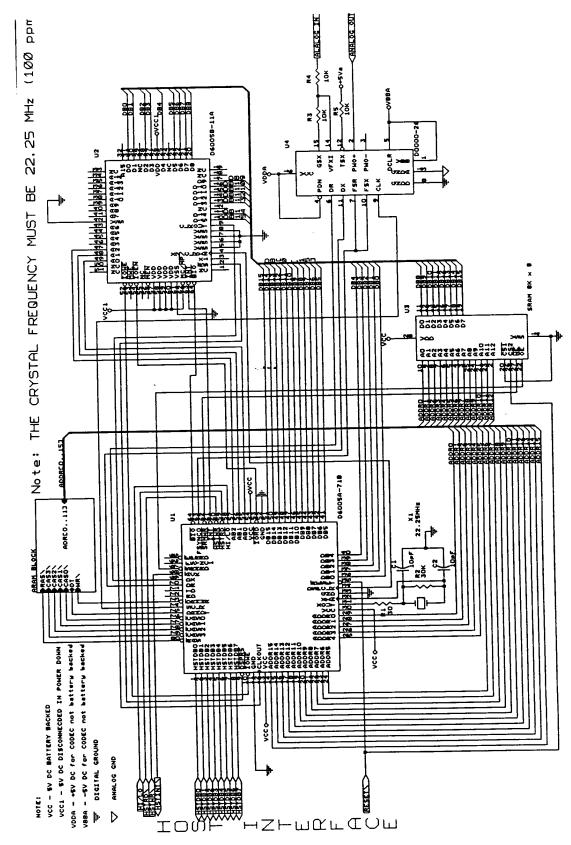

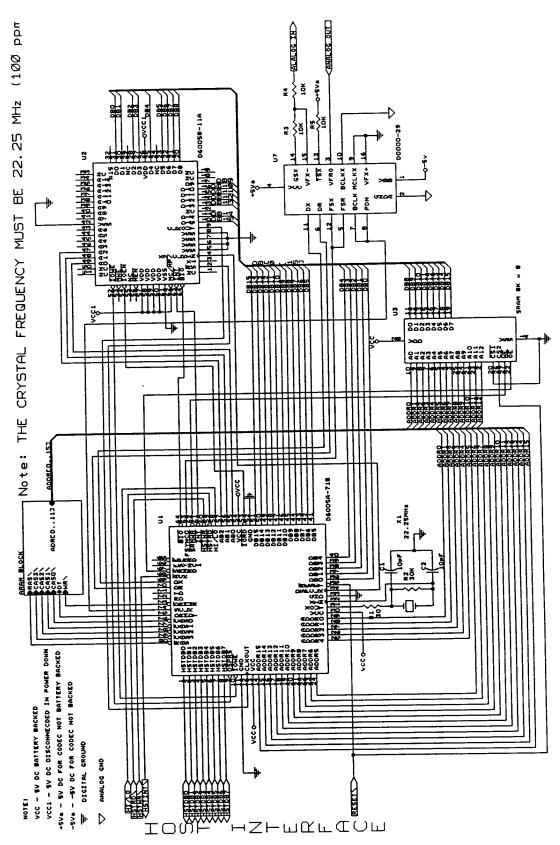

#### **ARAM INTERFACE**

The ARAM interface offers up to 16Mbits of ARAM storage for message storage. This interface can support up to 4 chips of 4Mbit x 1 ARAMS without external logic, or up to 16 chips of 1Mbit x 1 ARAM with additional logic (2 chips of 74HC139).

This block consits of two parts:

- a. ARAM read/write logic

- b. Refresh logic

The 12 address lines shared with address lines of SRAM. When accessing SRAM, refresh is disabled and the address bus is switched to SRAM address via the Address MUX.

Figure 9. D6005A-71B (ASIC) Block Diagram

Figure 10. ARAM Block—4 Meg Devices (D0000-34)

Figure 11. ARAM Block—1 Meg Devices (D0000-31)

#### **SRAM INTERFACE**

The SRAM interface supports access to single chip SRAM 8K x 8 with access time up to 100ns (at 22.25 MHz). The DSP will read/write from/to this static memory using the 16-bit bus. The D6005A-71B prepares the data before DSP reads by reading one byte from SRAM into an internal 18-bit register.

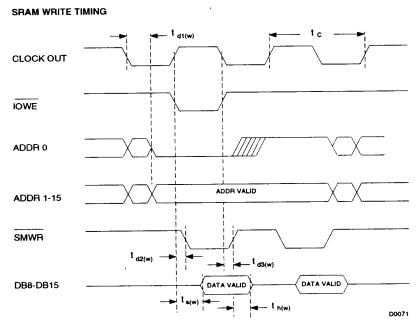

When the DSP reads this register it initiates the data read from SRAM in the next successful cycle. Loading address will also initiate data preparation in the D6005A-71B. When the DSP writes data to the internal register, in the next-following cycle, this data will be written by the D6005A-71B to the SRAM. The SRAM data bus will be connected to the same data bus as the DSP, using the high byte of this bus. The choice of accessing either SRAM or EPROM (reserved) is determined by the loading address: under 32K is SRAM, over 32K is EPROM (A15). Figures 13 and 14 show timing data for the SRAM interface.

Figure 12. Timing data for the SRAM Interface—WRITE

| $t_{d1(w)} = 65$ ns max       |  |

|-------------------------------|--|

| td2(w) = 20ns max             |  |

| td3(w) = 15ns max             |  |

| $t_{s(w)} = 27 \text{ns max}$ |  |

| $t_{h(w)} = 3ns min$          |  |

<sup>&</sup>quot;tc" in all the timing diagrams is 180ns nominal.

# CLOCK OUT IOEN SRMRD ADDR 1-15 ADDR VALID NEXT ADDR VALID D0072

Figure 13. Timing data for the SRAM Interface—READ

| td1(r) = 110ns max     |  |

|------------------------|--|

| td2(r) = 0ns max       |  |

| td3(r) = 90ns max      |  |

| $t_{s(r)} = 30$ ns min |  |

| th(r) = Ons min        |  |

#### Power Down Mode

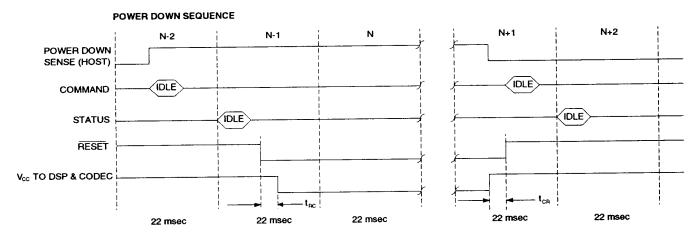

When the D6005B chipset is disconnected from its external power supply, it enters Power Down Mode. In this mode, power is supplied by internal TAD batteries. In Power Down mode, power is supplied to the D6005A-71B, SRAM and ARAMs in order to retain the essential data. The SRAM should be in non active mode (CE, WR, OE High), ARAM in minimum refresh mode and the DSP disconnected from its power supply, with the address decoder locked. Power Down Mode will be entered by applying a RESET signal to the D6005A-71B. When in power down mode the clock to the DSP will be held in low level to prevent contention. Figure 15 shows timing data for power down mode:

#### μ-LAW ENCODER

This is an interface implemented in the D6005A-71B to convert linear code (14-bit) to 8-bit  $\mu$ -law PCM code. It works by writing 14-bit linear data to this interface. By next reading from this port we will get 8-bit PCM data.

#### Analog I/O Controller

The Analog I/O Controller implements the data transfer and synchronization functions required to interface the DSP with Analog I/O Interface (codec) chips. The data transfer to/from the codecs is serial, while shift registers enable an 8-bit parallel link with the DSP. The INT interrupt signal informs the DSP that a data byte is received or has to be transmitted.

#### **Clock Generator**

The clock generator is connected to an external 22.25MHz crystal, and generates clock signals for the DSP, Analog I/O Controller and memory controllers.

#### I/O Address Decoder

The I/O Address Decoder receives three DSP address lines (AB0-2) with I/O access control signals, and generates the required I/O read and write pulses for the DSP peripheral devices.

Figure 14. Timing data for the Power Down Sequence

| tRC | = 5µs min |  |

|-----|-----------|--|

| tCR | = 5µs min |  |

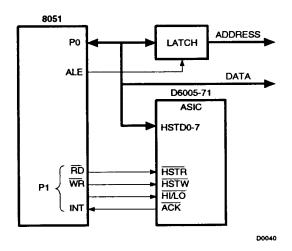

#### HOST-DSP COMMUNICATION CONTROLLER

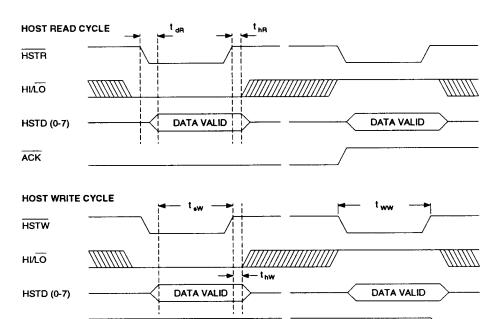

The host communication port is a 16-bit bidirectional register. The DSP will access this register by one 16-bit width access. HOST will access this register in two accesses, using the 8-bit bus: low byte and high byte. When HOST writes to High byte of this register it will set an internal flag, which is connected to the DSP BIO pin.

When the DSP reads the communication register this flag will be reset. When the DSP writes to the communication register it sets the ACK pin (External pin) which is connected to HOST for indication. When HOST reads the high byte of this register it will clear this ACK bit. The choice of high/low byte for host will be made by pin HI/LO. HOST will write to the communication register by strobing the HSTWR pin and by reading the HSTRD pin.

Table 1. Communication Interface Signals

| Pin Name | Type(*)      | Description                                |

|----------|--------------|--------------------------------------------|

| HSTD[07] | Input/Output | HOST 8-bit data bus                        |

| HSTR     | Input        | HOST READ line from register               |

| HSTW     | Input        | HOST WRITE line into register              |

| ACK      | Output       | Flag to HOST-status byte ready in register |