# **SoundPort Controller**

# AD1812

**FEATURES**

Compatibility with:

Sound Blaster Pro\*

AdLib\*

Windows\* Sound System

16-Bit  $\Sigma \Delta$  Stereo Codec

MPC Level-2+ Mixer

**Dual DMA/Full Duplex Operation**

**On-Chip FIFO Buffers**

Sample Rates from 5.5 kHz to 50 kHz

**ADPCM Compression/Decompression**

**Plug and Play Compliant**

Compatible MIDI MPU-401 Port

**Integrated Game Port**

Free Supporting Software:

Windows 3.1 Driver

Windows 95 Driver

**Control Applets**

**Diagnostics**

**Power Management Modes**

Operation from +5 V Supply

16-Bit Parallel Interface to ISA Bus

24 mA Bus Drive Capability

\*Sound Blaster Pro is a trademark of Creative Labs, Ltd. AdLib is a trademark of AdLib Multimedia. Windows is a trademark and Microsoft is a registered trademark of

Microsoft Corp.

SoundPort is a registered trademark of Analog Devices, Inc.

#### PRODUCT OVERVIEW

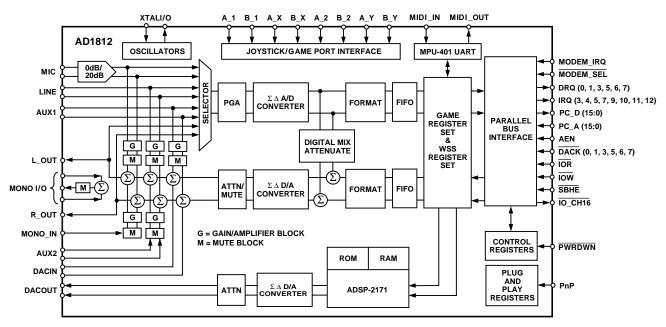

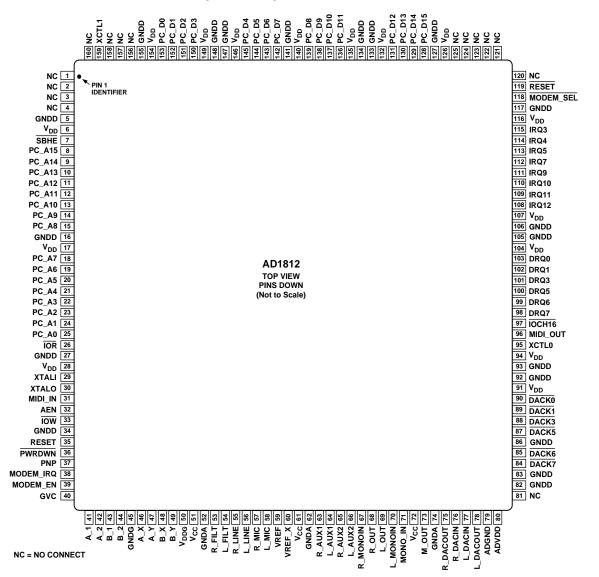

The AD1812 SoundPort® Controller is a single chip audio subsystem for adding 16-bit stereo audio to personal computers. The AD1812 is compatible with Sound Blaster Pro, AdLib, and the Microsoft\* Windows Sound System. The AD1812 provides an integrated audio solution for enhanced business audio, entertainment sound effects, and multimedia applications.

The AD1812 audio subsystem combines an integrated digital audio controller, a powerful signal processor, a mixer, and a 16-bit  $\Sigma\Delta$  stereo codec. The DOS games register set, the Windows Sound System register set, music synthesis hardware, an MPU-401 compatible UART interface, a game port (with timer), and a Plug and Play ISA interface are all contained on chip. The on-chip Plug and Play (PnP) routine provides configuration services for the internal logical devices and an external modem chipset.

The AD1812 can record compress and playback voice, sound and music. The system provides all PC 95 audio conversion and compatibility requirements for a multimedia enabled PC.

(continued on Page 12)

### FUNCTIONAL BLOCK DIAGRAM

REV. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

© Analog Devices, Inc., 1996

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 617/329-4700 Fax: 617/326-8703

# **AD1812—SPECIFICATIONS**

# STANDARD TEST CONDITIONS UNLESS OTHERWISE NOTED

| OTHER PROPERTY                    | TIONS CHILLSON O'TH | DICTION TO LED |                                      |

|-----------------------------------|---------------------|----------------|--------------------------------------|

|                                   |                     |                | DAC Test Conditions                  |

| Temperature                       | 0                   | °C             | Calibrated                           |

| Digital Supply (V <sub>DD</sub> ) | 5.0                 | V              | 0 dB Attenuation                     |

| Analog Supply (V <sub>CC</sub> )  | 5.0                 | V              | Input Full Scale                     |

|                                   |                     |                | 16-Bit Linear Mode                   |

| Sample Rate (F <sub>S</sub> )     | 48                  | kHz            | 10 kΩ Output Load                    |

| Input Signal                      | 1008                | Hz             | Mute Off                             |

| Analog Output Passband            | 20 Hz to 20 kHz     |                | ADC Test Conditions                  |

| $ m V_{IH}$                       | 2.0                 | V              | Calibrated                           |

|                                   |                     |                | 0 dB Gain                            |

| $ m V_{IL}$                       | 0.8                 | V              | Input –1.0 dB Relative to Full Scale |

| $V_{OH}$                          | 2.4                 | V              | Line Input Selected                  |

| $V_{OL}$                          | 0.4                 | V              | 16-Bit Linear Mode                   |

|                                   |                     |                |                                      |

# **ANALOG INPUT**

| Parameter                                                                          | Min   | Тур   | Max   | Units |

|------------------------------------------------------------------------------------|-------|-------|-------|-------|

| Input Voltage (RMS Values Assume Sine Wave Input) LINE, AUX1, MONO IN, AUX2, DACIN |       | 1     |       | V rms |

| , , , <u>-</u> , ,                                                                 | 2.55  | 2.83  | 3.11  | V p-p |

| MIC with +20 dB Gain (MGE = 1)                                                     |       | 0.1   |       | V rms |

|                                                                                    | 0.250 | 0.283 | 0.316 | V p-p |

| MIC with 0 dB Gain (MGE = $0$ )                                                    |       | 1     |       | V rms |

|                                                                                    | 2.55  | 2.83  | 3.11  | V p-p |

| Input Impedance*                                                                   | 10    | 17    |       | kΩ    |

| Input Capacitance*                                                                 |       |       | 15    | pF    |

## PROGRAMMABLE GAIN AMPLIFIER—ADC

| Parameter                                      | Min  | Тур  | Max  | Units |

|------------------------------------------------|------|------|------|-------|

| Step Size (0 dB to 22.5 dB) (All Steps Tested) | 1.3  | 1.5  | 1.7  | dB    |

| PGA Gain Range Span                            | 21.5 | 22.5 | 23.5 | dB    |

## AUXILIARY, LINE, MICROPHONE AND MONO INPUT ANALOG GAIN/AMPLIFIERS/ATTENUATORS

| Parameter                                                  | Min  | Typ  | Max  | Units |

|------------------------------------------------------------|------|------|------|-------|

| Step Size: AUX1, AUX2, DACIN, LINE, MIC (All Steps Tested) |      |      |      |       |

| (+12 dB to -30 dB)                                         | 1.25 | 1.5  | 1.75 | dB    |

| (-31.5  dB to  -34.5  dB)                                  | 1    | 1.5  | 2.0  | dB    |

| Input Gain/Attenuation Range: AUX1, AUX2, DACIN, LINE, MIC | 45.0 | 46.5 | 47.5 | dB    |

| Step Size: MONO_IN (All Steps Tested)                      |      |      |      |       |

| (0  dB to  -39  dB)                                        | 2.5  | 3.0  | 3.6  | dB    |

| (-42 dB to -45 dB)                                         | 2.2  | 3.0  | 3.85 | dB    |

| Input Gain/Attenuation Range: MONO_IN                      | 43   | 45   | 46   | dB    |

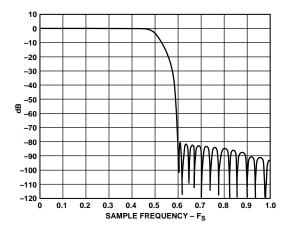

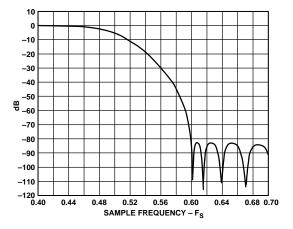

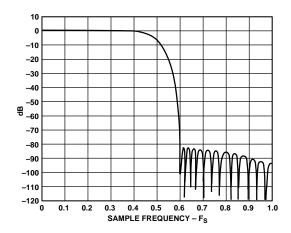

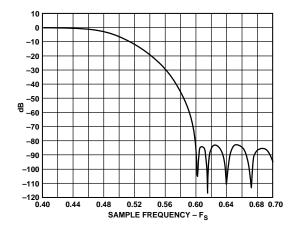

#### DIGITAL DECIMATION AND INTERPOLATION FILTERS\*

| Parameter                           | Min              | Typ | Max               | Units |

|-------------------------------------|------------------|-----|-------------------|-------|

| Passband                            | 0                |     | $0.4 \times F_S$  | Hz    |

| Passband Ripple                     |                  |     | $\pm 0.1$         | dB    |

| Transition Band                     | $0.4 \times F_S$ |     | $0.6 \times F_S$  | Hz    |

| Stopband                            | $0.6 \times F_S$ |     | ∞                 | Hz    |

| Stopband Rejection                  | 74               |     |                   | dB    |

| Group Delay                         |                  |     | 15/F <sub>S</sub> | sec   |

| Group Delay Variation Over Passband |                  |     | 0.0               | μs    |

<sup>\*</sup>Guaranteed not tested.

Specifications subject to change without notice.

-2- REV. 0

## ANALOG-TO-DIGITAL CONVERTERS

| Parameter                                                               | Min | Typ | Max       | Units |

|-------------------------------------------------------------------------|-----|-----|-----------|-------|

| Resolution                                                              |     | 16  |           | Bits  |

| Dynamic Range (-60 dB Input THD+N Referenced to Full Scale, A-Weighted) | 80  | 86  |           | dB    |

| THD+N (Referenced to Full Scale)                                        |     |     | 0.02      | %     |

|                                                                         |     | -78 | -74       | dB    |

| Signal-to-Intermodulation Distortion* (CCIF Method)                     |     | 80  |           | dB    |

| ADC Crosstalk*                                                          |     |     |           |       |

| Line Inputs (Input L, Ground R, Read R; Input R, Ground L, Read L)      |     | -90 | -80       | dB    |

| Line to MIC (Input LINE, Ground and Select MIC, Read ADC)               |     | -90 | -80       | dB    |

| Line to AUX1                                                            |     | -90 | -80       | dB    |

| Line to AUX2                                                            |     | -90 | -80       | dB    |

| Gain Error (Full-Scale Span Relative to Nominal Input Voltage)          |     |     | $\pm 10$  | %     |

| Interchannel Gain Mismatch (Difference of Gain Errors)                  |     |     | $\pm 0.5$ | dB    |

| ADC Offset Error                                                        |     |     | 10        | mV    |

# **DIGITAL-TO-ANALOG CONVERTERS**

| Parameter                                                                       | Min | Тур        | Max   | Units |

|---------------------------------------------------------------------------------|-----|------------|-------|-------|

| Resolution                                                                      |     | 16         |       | Bits  |

| Dynamic Range (-60 dB Input THD+N Referenced to Full Scale, A-Weighted)         | 74  | 81         |       | dB    |

| THD+N (Referenced to Full Scale)                                                |     |            | 0.022 | %     |

|                                                                                 |     | <b>-77</b> | -73   | dB    |

| Signal-to-Intermodulation Distortion* (CCIF Method)                             |     |            | 90    | dB    |

| Gain Error (Full-Scale Span Relative to Nominal Input Voltage)                  |     |            | ±15   | %     |

| Interchannel Gain Mismatch (Difference of Gain Errors)                          |     |            | ±0.5  | dB    |

| DAC Crosstalk* (Input L, Zero R, Measure R_OUT; Input R, Zero L, Measure L OUT) |     | -90        | -80   | dB    |

| Total Out-of-Band Energy (Measured from $0.6 \times F_S$ to 100 kHz)*           |     |            | -60   | dB    |

| Audible Out-of-Band Energy (Measured from $0.6 \times F_S$ to 20 kHz)*          |     |            | -70   | dB    |

# DAC ATTENUATOR

| Parameter                             | Min  | Typ  | Max  | Units |

|---------------------------------------|------|------|------|-------|

| Step Size (0 dB to -22.5 dB)          | 1.3  | 1.5  | 1.7  | dB    |

| Step Size (-22.5 dB to -94.5 dB)*     | 1.0  | 1.5  | 2.0  | dB    |

| Output Attenuation Range Span*        | 93.5 | 94.5 | 95.5 | dB    |

| Mute Attenuation of 0 dB Fundamental* |      |      | 80   | dB    |

# DIGITAL MIX ATTENUATOR

| Parameter                           | Min  | Тур  | Max  | Units |

|-------------------------------------|------|------|------|-------|

| Step Size (0 dB to -22.5 dB)        | 1.3  | 1.5  | 1.7  | dB    |

| Step Size (−22.5 dB to −94.5 dB)*   | 1.0  | 1.5  | 2.0  | dB    |

| Digital Mix Attenuation Range Span* | 93.5 | 94.5 | 95.5 | dB    |

<sup>\*</sup>Guaranteed not tested.

REV. 0 -3-

Specifications subject to change without notice.

# ANALOG OUTPUT

| Parameter                                                    | Min  | Тур  | Max  | Units |

|--------------------------------------------------------------|------|------|------|-------|

| Full-Scale Output Voltage                                    |      |      |      |       |

| $O_L = 0$                                                    | 1.8  | 2.0  | 2.2  | V p-p |

| $O_L = 1$                                                    | 2.5  | 2.8  | 3.11 | V p-p |

| Output Impedance*                                            |      |      | 600  | Ω     |

| External Load Impedance                                      | 10   |      |      | kΩ    |

| Output Capacitance*                                          |      |      | 15   | pF    |

| External Load Capacitance                                    |      |      | 100  | pF    |

| $V_{ m REF}$                                                 | 2.05 | 2.25 | 2.45 | V     |

| V <sub>REF</sub> Output Impedance                            |      | 4    |      | kΩ    |

| Mute Click (Muted Output Minus Unmuted Midscale DAC Output)* |      |      | ±5   | mV    |

# **SYSTEM SPECIFICATIONS**

| Parameter                                                                                                     | Min | Typ | Max            | Units                |

|---------------------------------------------------------------------------------------------------------------|-----|-----|----------------|----------------------|

| System Frequency Response Ripple* (Line In to Line Out) Differential Nonlinearity* Phase Linearity Deviation* |     |     | 1.0<br>±1<br>5 | dB<br>LSB<br>Degrees |

## STATIC DIGITAL SPECIFICATIONS

| Parameter                                                        | Min | Typ | Max | Units |

|------------------------------------------------------------------|-----|-----|-----|-------|

| High-Level Input Voltage (V <sub>IH</sub> ): Digital Inputs      | 2   |     |     | V     |

| Low-Level Input Voltage (V <sub>IL</sub> )                       |     |     | 0.8 | V     |

| High-Level Output Voltage ( $V_{OH}$ ), $I_{OH} = 24 \text{ mA}$ | 2.4 |     |     | V     |

| Low-Level Output Voltage ( $V_{OL}$ ), $I_{OL} = 24 \text{ mA}$  |     |     | 0.4 | V     |

| Input Leakage Current                                            | -10 |     | 10  | μΑ    |

| Output Leakage Current                                           | -10 |     | 10  | μA    |

# **POWER SUPPLY**

| Parameter                                                    | Min  | Typ | Max  | Units |

|--------------------------------------------------------------|------|-----|------|-------|

| Power Supply Range—Analog                                    | 4.75 |     | 5.25 | V     |

| Power Supply Range—Digital                                   | 4.75 |     | 5.25 | V     |

| Power Supply Current                                         |      |     | 250  | mA    |

| Power Dissipation                                            |      |     | 1.25 | W     |

| Analog Supply Current                                        |      |     | 55   | mA    |

| Digital Supply Current                                       |      |     | 195  | mA    |

| Digital Power Supply Current—Power Down                      |      |     | 15   | mA    |

| Analog Power Supply Current—Power Down                       |      |     | 1    | mA    |

| Power Supply Rejection (100 mV p-p Signal @ 1 kHz)*          |      |     |      |       |

| (At Both Analog and Digital Supply Pins, Both ADCs and DACs) | 40   |     |      | dB    |

# **CLOCK SPECIFICATIONS\***

| Parameter                    | Min | Тур      | Max | Units |

|------------------------------|-----|----------|-----|-------|

| Input Clock Frequency        | 6   | 14.31818 | 18  | MHz   |

| Recommended Clock Duty Cycle | 10  | 50       | 90  | %     |

| Power Up Initialization Time |     |          | 500 | ms    |

<sup>\*</sup>Guaranteed not tested.

-4- REV. 0

Specifications subject to change without notice.

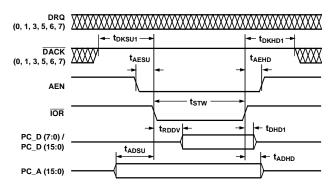

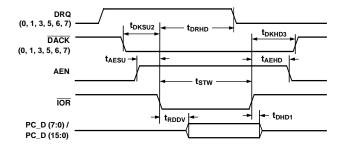

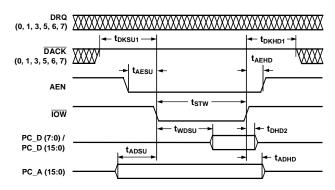

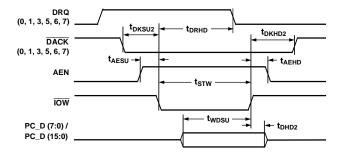

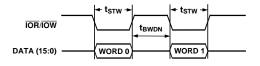

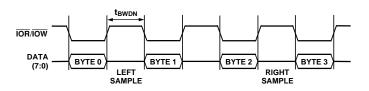

### TIMING PARAMETERS (GUARANTEED OVER OPERATING TEMPERATURE RANGE)

| Parameter                                                          | Symbol             | Min | Тур | Max | Units |

|--------------------------------------------------------------------|--------------------|-----|-----|-----|-------|

| IOW/IOR Strobe Width                                               | t <sub>STW</sub>   | 100 |     |     | ns    |

| IOW/IOR Rising to IOW/IOR Falling                                  | $t_{BWDN}$         | 80  |     |     | ns    |

| Write Data Setup to IOW Rising                                     | $t_{ m WDSU}$      | 10  |     |     | ns    |

| IOR Falling to Valid Read Data                                     | $t_{RDDV}$         |     |     | 40  | ns    |

| AEN Setup to $\overline{\text{IOW}}/\overline{\text{IOR}}$ Falling | $t_{ m AESU}$      | 10  |     |     | ns    |

| AEN Hold from IOW/IOR Rising                                       | t <sub>AEHD</sub>  | 0   |     |     | ns    |

| Adr Setup to IOW/IOR Falling                                       | $t_{ m ADSU}$      | 10  |     |     | ns    |

| Adr Hold from IOW/IOR Rising                                       | t <sub>ADHD</sub>  | 10  |     |     | ns    |

| DACK Rising to IOW/IOR Falling                                     | t <sub>DKSU1</sub> | 20  |     |     | ns    |

| IOW/IOR Rising to DACK Falling                                     | t <sub>DKHD1</sub> | 0   |     |     | ns    |

| DACK Setup to IOW/IOR Falling                                      | t <sub>DKSU2</sub> | 10  |     |     | ns    |

| Data Hold from IOR Rising                                          | t <sub>DHD1</sub>  |     |     | 20  | ns    |

| Data Hold from IOW Rising                                          | $t_{ m DHD2}$      | 15  |     |     | ns    |

| DRQ Hold from IOW/IOR Falling                                      | $t_{ m DRHD}$      |     |     | 25  | ns    |

| DACK Hold from IOW Rising                                          | t <sub>DKHD2</sub> | 10  |     |     | ns    |

| DACK Hold from IOR Rising                                          | t <sub>DKHD3</sub> | 10  |     |     | ns    |

<sup>\*</sup>Guaranteed, not tested.

Specifications subject to change without notice.

#### **General Notes**

Use the exact timing information given. Do not attempt to derive parameters from the addition or subtraction of others. While addition or subtraction would yield meaningful results for an additional device, the values given in this data sheet reflect statistical variations and worst cases. Consequently, you cannot meaningfully add up parameters to derive longer times. Note that all 8-bit DMA transfers occur on channels 0, 1, and 3, while all 16-bit DMA transfers occur on channels 5, 6, and 7.

Figure 1. PIO Read Cycle

Figure 3. DMA Read Cycle

Figure 2. PIO Write Cycle

Figure 4. DMA Write Cycle

REV. 0 –5–

Table I. Codec Transfer 16-Bit Interface, No Byte Swap (P/CINF8 = 0, P/CBSW = 0)\*

| Format                    |                 |                     | (16-Bit)            | SB                  |                  | Word 0 (            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | en              |  |

|---------------------------|-----------------|---------------------|---------------------|---------------------|------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|

|                           | IVI             | SB                  | L                   | <b>SB</b>           | MSB              |                     | LSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                 |  |

| Mono, 16-Bit              |                 | 8 Bits of           |                     | 8 Bits of           |                  | 8 Bits of           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Lower 8 Bits of |  |

| Little Endian             | San             | ple 1               | Sar                 | nple 1              | San              | ple 0               | Sam                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ple 0           |  |

|                           | Left (          | Channel             | Left (              | Channel             | Left (           | Channel             | Left C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Channel         |  |

| Stereo, 16-Bit            | Upper           | 8 Bits of           | Lower               | 8 Bits of           | Upper            | 8 Bits of           | Lower                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 8 Bits of       |  |

|                           | San             | ple 0               | Sar                 | nple 0              | San              | nple 0              | San                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | nple 0          |  |

| Little Endian             | Right           | Channel             | Right               | Channel             | Left (           | Channel             | Left C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Channel         |  |

| Mana 9 Dit                |                 | 3, 8 Bits           |                     |                     |                  | 1, 8 Bits           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0, 8 Bits       |  |

| Mono, 8-Bit<br>Linear PCM | Sample          | 5, 6 DIIS           | Sample              | 2, 8 Bits           | Sample           | 1, 6 Bits           | Sample                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | U, o bits       |  |

| μ-Law PCM<br>A-Law PCM    | Left (          | Channel             | Left (              | Channel             | Left (           | Channel             | Left C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Channel         |  |

| Stereo, 8-Bit             | Sample          | 1, 8 Bits           | Sample 1, 8 Bits    |                     | Sample 0, 8 Bits |                     | Sample 0, 8 Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 |  |

| Linear PCM                |                 | ,                   |                     |                     | F : 1, 2 = 222   |                     | The Part of the Pa |                 |  |

| μ-Law PCM<br>A-Law PCM    | Right           | Channel             | Left Channel        |                     | Right Channel    |                     | Left Channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                 |  |

| Mono, 4-Bit               | Sample 7,       | Sample 6,           | Sample 5,           | Sample 4,           | Sample 3,        | Sample 2,           | Sample 1,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Sample 0,       |  |

| IMA-ADPCM                 | 4 Bits          | 4 Bits              | 4 Bits              | 4 Bits              | 4 Bits           | 4 Bits              | 4 Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4 Bits          |  |

| IMA-ADI CM                | Left            | Left                | Left                | Left                | Left             | Left                | Left                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Left            |  |

|                           | Channel         | Channel             | Channel             | Channel             | Channel          | Channel             | Channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Channel         |  |

| Stereo, 4-Bit             | Sample 3,       | Sample 3,<br>4 Bits | Sample 2,<br>4 Bits | Sample 2,<br>4 Bits | Sample 1,        | Sample 1,<br>4 Bits | Sample 0,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Sample 0,       |  |

| IMA-ADPCM                 | 4 Dits          | 4 Dits              | 4 Dits              | 4 Dits              | 4 Dits           | 4 Dits              | 4 Dits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4 Dits          |  |

|                           | Right           | Left                | Right               | Left                | Right            | Left                | Right                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Left            |  |

|                           | Channel         | Channel             | Channel             | Channel             | Channel          | Channel             | Channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Channel         |  |

| Mono, 16-Bit              |                 | 8 Bits of           |                     | 8 Bits of           | Lower 8 Bits of  |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8 Bits of       |  |

| Big Endian                | Sample 1        |                     | Sam                 | iple 1              | San              | iple 0              | Sar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | nple 0          |  |

| big Endian                | Left Channel    |                     | Left (              | Channel             | Left Channel     |                     | Left Channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                 |  |

| Stereo, 16-Bit            | Lower 8 Bits of |                     | Upper               | 8 Bits of           | Lower 8 Bits of  |                     | Upper 8 Bits of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |  |