# Semicustom

**Bi-CMOS**

# **ASTRO MASTER IV Specification**

(for PLL frequency synthesizers)

# **MB1570 Series**

### **■ DESCRIPTION**

The ASTRO MASTER IV is a master-slice type semi-custom LSI ideal for use in high-frequency front-end circuits in VCO, amplifier, mixer and I/Q modulator devices.

The MB1570 series features an analog circuit unit that is a more highly integrated version of the ASTRO MASTER I series.

The PLL, prescaler and high-frequency analog circuits can be designed to users' specifications using FUJITSU's standard macro cells as well as customized macro cells.

This LSI series uses FUJITSU's latest process technology for power-saving operation and master-slice semicustom design to reduce lead times and lower costs. In addition, the ultra-compact flat package helps maintain circuit confidentiality, and contributes to lighter, more compact design by reducing the number of components.

The ASTRO MASTER IV is ideal for high-frequency applications, particularly mobile communication devices operating on digital specifications such as PCN, DECT, PHS and so on.

ASTRO: Advanced Semi-Custom Technology of Super PLL with RF System on LSI.

#### **■ FEATURES**

- PLL circuits can be customized for operating frequency, logical circuits, etc.

- High frequency analog circuits with adjustable resistance levels

(Continued)

# **■ PACKAGES**

# (Continued)

- High speed operating capacity to 3.0 GHz

- On-chip low-current consumption and power-saving circuits

- On-chip high-speed lockup function

- Supply voltage: 2.7 V to 3.3 V (minimum operating voltage to 2.0 V min.)

- Development time (standard): approx. 10 weeks

# **■** LINEUP

| Series | Prescaler  | PLL        | Analog circuits | Operating frequency | Package<br>LQFP | Remarks                         |

|--------|------------|------------|-----------------|---------------------|-----------------|---------------------------------|

| MB1570 | 2 circuits | 2 circuits | 6 circuits      | 3.0 GHz             | 48<br>64        | For dual frequency synthesizers |

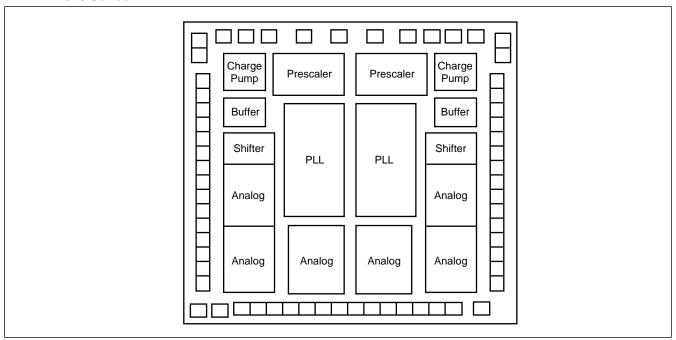

# **■ CHIP LAYOUT**

### • MB1570 Series

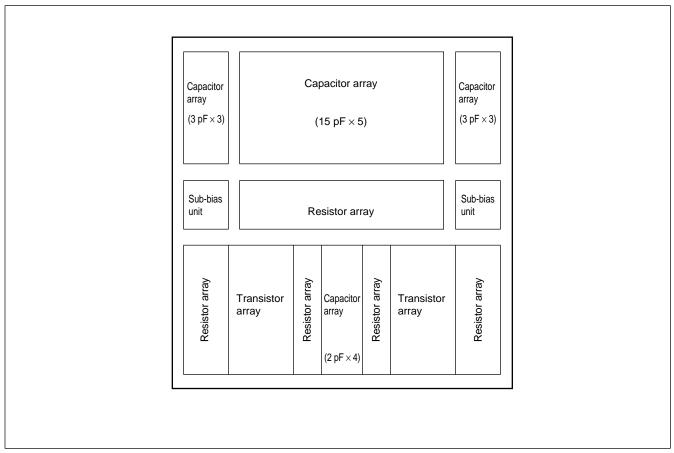

# Analog Cell

### **■ MACRO CELL DESCRIPTIONS**

#### 1. Prescaler

Divides the reference frequency by any given value and outputs the resulting frequency. Choice of two-modulus or fixed output mode.

### 2. PLL

### Phase comparator

The phase comparator has a phase detection range of  $-2 \pi$  to  $+2 \pi$ , and is designed to eliminate blind spots in phase comparison by output of a margin-of-error signal to the charge pump even when the phase difference is zero. Phase comparator characteristics can also be tuned to the polarity of VCO.

#### Counters

The divide ratios of the comparator-side counter and reference-side counter can be either programmable or fixed.

### Charge pump

The "H" level output voltage from the charge pump is determined by power supply voltage. Charge pump characteristics for the sending and receiving systems can be optimized for each specific application. For example, when FM modulation is applied directly to the VCO signal, charge pump characteristics can be adjusted for lower speeds in order to reduce the sensitivity of the synthesizer loop so that output does not track the modulation.

### · Analog switch

When switching frequencies, the analog switch can be used to switch the capacitance of the low pass filter, to reduce the time constant in the filter and the load on the charge pump. This enables higher lock-up speed. Switch control is synchronous with the LE signal, to that the analog switch is on when the LE signal is "high".

### High speed lock-up circuit

This circuit is specially designed for faster lock-up speeds.

### Intermittent operation control circuit

This on-chip power-saving function reduces circuit current flow in standby status, enabling devices to operate with less power demand. A special circuit is built in to prevent excessive error signal from increasing lock-up delay during the transition from power-saving mode to operating mode.

#### · List of standard macro cells

| Ту | /pe | Vcc | lcc  | Operating frequency | Prescaler<br>divide ratio | Comparator<br>counter<br>divide ratio<br>(M) | Swallow<br>counter<br>divide ratio<br>(A) | Reference<br>counter<br>divide ratio<br>(R) |

|----|-----|-----|------|---------------------|---------------------------|----------------------------------------------|-------------------------------------------|---------------------------------------------|

| PL | _L1 | 3V  | 4 mA | 1.1 GHz             | 64/65                     | 16 to 2047                                   | 0 to 127                                  | 8 to 16383                                  |

| PL | L2  | 3 V | 6 mA | 2.0 GHz             | 04/03                     | 10 10 2047                                   | 0 10 127                                  | 0 10 10303                                  |

Crystal oscillator input frequency: Up to 32 MHz

Standby mode current demand: 100 µA

### 3. High Frequency Analog Cells

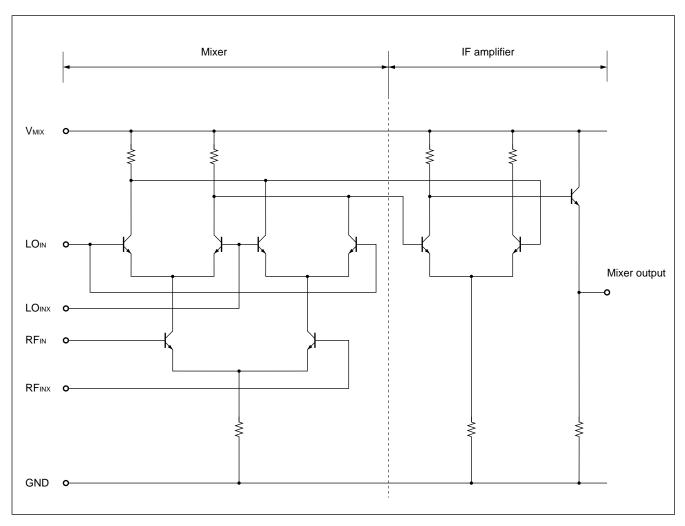

#### Mixer

Active type double-balanced mixer

#### • IF amplifier

The IF amplifier is configured from a differential amplifier plus an NPN transistor using emitter-follower output from the differential amplifier.

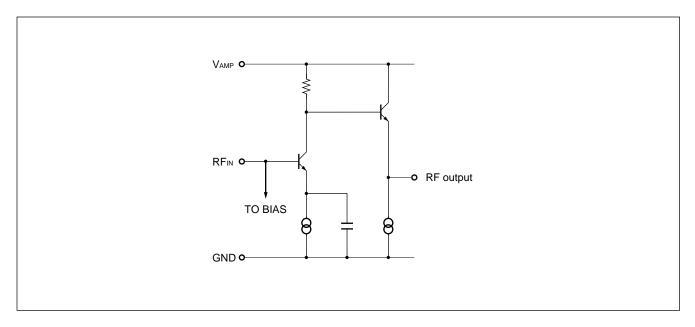

### RF amplifier

Provides emitter-follower output of the output signal from the emitter-ground circuit. The RF input side can be connected to an internal bias circuit.

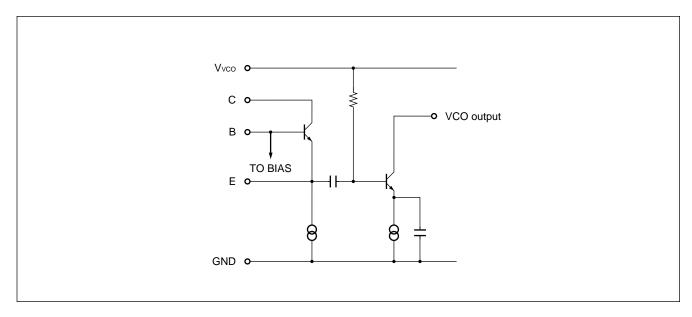

#### VCO

Configured from an oscillator transistor in a base-ground Colpitts type oscillator circuit, plus a transistor acting as output buffer. Can be connected to external devices such as varicap or resonator.

### Orthogonal modulator

An orthogonal modulator is used for IF frequency modulation. In addition, a flip-flop type  $90^{\circ}$  phase shift circuit can be included in the configuration.

Note: Circuit format and other details can be adjusted to meet customer requirements.

### **■ CIRCUIT OPERATING DESCRIPTIONS**

# 1. Intermittent Operation Control Circuit

The intermittent operation control circuit operates the LSI circuits during communication operations and at all other times places the chip in standby status to reduce power demand.

### (1) Circuit operation in operating mode

All circuits are in operating status, and the chip performs normal PLL operations.

### (2) Circuit operation in standby mode

All circuits that can be stopped without interfering with operation are shut down, and the chip goes into low-power operating mode.

Latch data: Saves immediately preceding data

Shift register: Data input enabled Charge pump output: High impedance

VCO input voltage: Saves voltage level stored in low-pass filter during the last operating mode

<Caution> The digital system power supply must still be applied in standby mode.

### 2. Phase Lock Detection Circuit

To detect phase lock condition from the LD signal pin output, the T-bit should be selected. When the phase difference is greater than tw, the LD pin will output an L level signal, and when the difference is less than tw for 3 or more cycles, the output will change to H level. The length of the tw time interval can be set in the range of 625 ns to 1250 ns by connection to the crystal oscillator.

# • LD Signal operating status

| Operating status | PLL circuit | LD output |  |

|------------------|-------------|-----------|--|

| Standby mode     | Standby     | Н         |  |

| Operating mode   | Un-lock     | L         |  |

| Operating mode   | Lock        | Н         |  |

# 3. High Speed Tuning Circuit

The following high speed tuning circuits are available for use according to specific applications.

### High speed tuning circuits for ASTRO MASTER IV

| Function             | Operation                                                               | Optimum applications                             |

|----------------------|-------------------------------------------------------------------------|--------------------------------------------------|

| Analog switch        | Circuit temporarily reduces LPF time constant at lock-up.               | Analog portable phone devices (receiving system) |

| Turbo circuits       | For broad-band steps, circuit forcibly switches charge pump on/off      | PHS devices                                      |

| Supercharger circuit | Circuit increases charge pump drive capacity                            | PHS devices                                      |

| Hypercharger circuit | Circuit further enhances the drive capacity of the supercharger circuit | PDC, GSM etc.                                    |

### **■ SERIAL DATA**

# 1. Data Bit Configuration

PLL operating settings are made through serial data input. The standard serial format is shown in the table below. Serial data is entered MSB-first, and the data length is in the range of 22 to 37 bits.

#### · Standard format for serial data

| Bit name (ab                  | breviation)      | Functional description                                     | Standard bit count |  |

|-------------------------------|------------------|------------------------------------------------------------|--------------------|--|

| Control bit (CNT bit)         |                  | Selects transfer destination (sending or receiving system) | 1 to 2             |  |

| LD select bit (T-bit)         |                  | Selects LD output                                          | 1 to 2             |  |

| FC bit (F-bit)                |                  | Switches the phase of phase comparator                     | 1                  |  |

| Programmable cour             | nter bit (N-bit) | Sets the programmable counter's divide ratio               | 11                 |  |

| Swallow counter bit (A-bit)   |                  | Sets the swallow counter's divide ratio                    | 7                  |  |

| Reference counter bit (R-bit) | Fixed            | Sets the reference counter's divide ratio                  | 1 to 2             |  |

|                               | Programmable     | Sets the releience counter's divide fatto                  | 14                 |  |

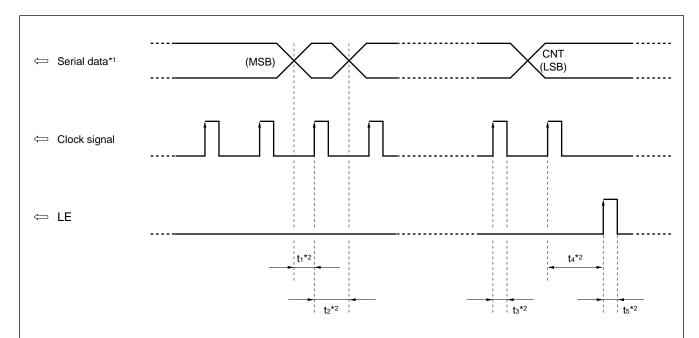

### 2. Serial Data Input Timing

After the serail data is stored in the shift register, it can be transferred to the latch circuit by means of the LE signal.

- \*1: Serial data is input, MSB-first.

- \*2: 100 ns  $\leq$  t<sub>1</sub>, t<sub>4</sub> 300 ns  $\leq$  t<sub>3</sub> 800 ns  $\leq$  t<sub>5</sub> 1000 ns  $\leq$  t<sub>2</sub>

Notes: • Data input utilizes the serial data, clock and LE signals at supply voltage or lower levels

- Shift register data is updated sequentially each time the clock signal is input. Data is synchronized with the rising edge of the clock signal, and is read sequentially into the shift register, MSB-first.

- After LSB input, the LE signal is changed from L level to H level.

- Shift register data is transferred to the latch circuit while the LE signal is at H level.

- Each input signal pin has a Schmitt trigger circuit to protect against abnormal operation due to noise.

# ■ ABSOLUTE MAXIMUM RATINGS

| Parameter           | Symbol | Rat         | Unit     |       |

|---------------------|--------|-------------|----------|-------|

| Parameter           |        | Min.        | Max.     | Ullit |

| Supply voltage*     | Vcc    | -0.5        | +4.0     | V     |

| Input voltage*      | Vin    | -0.5        | Vcc +0.5 | V     |

| Output current      | Іоит   | -10         | 10       | mA    |

| Storage temperature | Tstg   | <b>–</b> 55 | +125     | °C    |

<sup>\*:</sup> Voltage values are based on GND = 0 V.

Note: Permanent device damage may occur if the above Absolute Maximum Ratings are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### ■ RECOMMENDED OPERATING CONDITIONS

| Parameter             | Symbol | Value |      |      | Unit |

|-----------------------|--------|-------|------|------|------|

| Farameter             |        | Min.  | Тур. | Max. | Oill |

| Supply voltage*1      | Vcc    | 2.7*  | _    | 3.3  | V    |

| Supply voltage*1      | GND    | _     | 0    | _    | V    |

| Operating temperature | Та     | -40   | _    | +85  | °C   |

<sup>\*1:</sup> Voltage values are based on GND = 0 V

<sup>\*2:</sup> Operation is assured to the minimum operating voltage level of 2.0 V min.

# ■ ANALOG CIRCUIT CHARACTERISTICS

| Circuit        | Parameter              |         | Conditions                                        | Value<br>(typ.) | Unit  |

|----------------|------------------------|---------|---------------------------------------------------|-----------------|-------|

|                | Supply voltage         |         | _                                                 | 3.0             | V     |

|                | Current demand         |         | _                                                 | 11              | mA    |

|                | Operating fr           | equency | _                                                 | 900             | MHz   |

| vco            | C/N ratio              |         | Offset frequency = 25 kHz,<br>Band width = 16 kHz | 77              | dB    |

|                | S/N ratio              |         | BW = 0.3 to 3 kHz, 3 kHz/Dev                      | 44              | dB    |

|                | Output power           | er      | _                                                 | -2              | dBm   |

|                | Conversion             | gain    | _                                                 | 6               | MHz/V |

|                | Supply volta           | age     | _                                                 | 3.0             | V     |

|                | Current demand         |         | _                                                 | 12              | mA    |

|                | Operating frequency    | IF      | _                                                 | 800             | MHz   |

|                |                        | LO      | PLO = -10 dBm                                     | 110             | MHz   |

| Mixer          |                        | RF      | fr= fLO + fIF                                     | 910             | MHz   |

| IVIIXEI        | Conversion gain        |         | _                                                 | 6               | dB    |

|                | Maximum output power   |         | _                                                 | -11             | dBm   |

|                | 1 dB compression point |         | Output level                                      | -15             | dBm   |

|                | Intercept point        |         | Input level                                       | -8              | dBm   |

|                | NF                     |         | DSB measurement                                   | 12              | dB    |

|                | Supply voltage         |         | _                                                 | 3.0             | V     |

|                | Current demand         |         | _                                                 | 6               | mA    |

|                | Operating frequency    |         | _                                                 | 900             | MHz   |

| A man lift a r | Gain                   |         | f = 900 MHz (-30 dBm in)                          | 14              | dB    |

| Amplifier      | Maximum output power   |         | f = 900 MHz                                       | -3              | dBm   |

|                | 1 dB compression point |         | f = 900 MHz, output level                         | -8              | dBm   |

|                | Intercept po           | int     | f = 900 MHz, 900.1 MHz, input level               | -12             | dBm   |

|                | NF                     |         | f = 900 MHz                                       | 2.2             | dB    |

| Circuit              | Parameter           |                     | Conditions                 | Value<br>(typ.) | Unit |

|----------------------|---------------------|---------------------|----------------------------|-----------------|------|

|                      | Supply volta        | ige                 | _                          | 3.0             | V    |

|                      | Current demand      |                     | _                          | 25              | mA   |

|                      |                     | LO1                 | PLO1 = -5 dBm              | 500             | MHz  |

|                      | Operating frequency | LO2                 | $P_{LO2} = -5 \text{ dBm}$ | 1650            | MHz  |

|                      |                     | RF                  | fRF = fLO2 + fLO1/2        | 1900            | MHz  |

| Orthogonal modulator | Output level        |                     | _                          | -14             | dBm  |

| modulator            | Modulator precision | Amplitude deviation | RMS Magnitude Error        | 1.9             | %    |

|                      |                     | Phase deviation     | RMS Phase Error            | 0.9             | deg. |

|                      |                     | Vector error        | RMS Vector Error           | 2.4             | %    |

|                      | Carrier leak        |                     | _                          | -31             | dBc  |

# ■ ANALOG SYSTEM: BASIC EQUIVALENT CIRCUITS

# 1. Mixer, IF Amplifier

The MB1570 series features an active-type double-balanced mixer. The LO and RF output can be connected to an internal bias circuit. The mixer output is connected through on-chip load resistor to the chip's power supply, and then to the next-stage IF amplifier. The IF amplifier is configured from a differential amplifier and NPN transistor, and provides emitter-follower differential amplifier output.

# 2. RF Amplifier

The emitter-ground circuit output signal is output as an emitter-follower signal. The RF input can be grounded to an internal bias circuit.

# 3. VCO Amplifier

The VCO amplifier is configured from an oscillator transistor in a base-ground Colpitts type oscillator circuit, plus a transistor acting as output buffer. The VCO amplifier can be connected to external devices such as varicap or resonator.

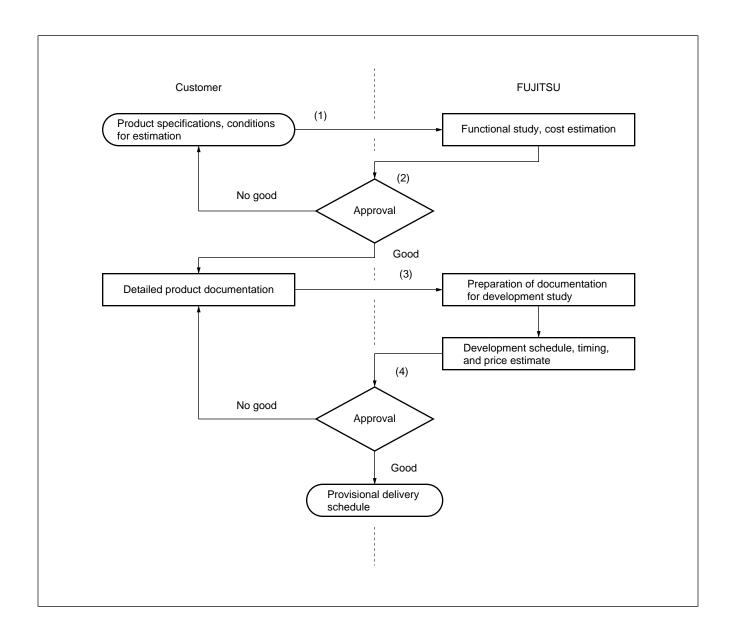

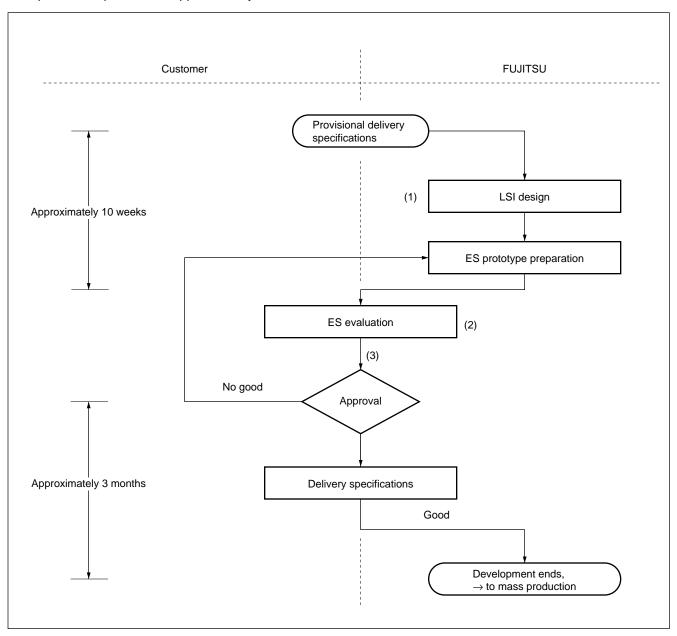

### **■ DEVELOPMENT PROCESSES**

Each product in the ASTRO MASTER IV series is developed through the following processes, based on requirements and specifications supplied by the customer.

### 1. Feasibility Study

### (1) Product specifications and development process study

FUJITSU conducts simulations based on documentation provided by the customer, in order to evaluate the technical and economic feasibility of each proposed design.

### **Product Documentation**

Technical documentation: Functional descriptions, I/O signal descriptions, block diagrams.

Characteristics documentation: For prescalers, PLL, VCO, mixers, amplifiers, etc.

### **Development Documentation**

Delivery schedule documentation: Development schedule, division of responsibilities, etc.

Cost estimates: Volume requirements, development costs, target prices

# (2) Product feasibility evaluation

Based on the foregoing studies, FUJITSU and the customer meet to evaluate feasibility.

### (3) Development of planned specifications

Circuit functions and characteristics are studied in detail, and circuit specifications and testing specifications are developed. After specifications have been determined, final estimates of the development schedule, timing and cost, and the product price can be produced.

### (4) Approval of provisional delivery specifications

After FUJITSU and the customer have determined the feasibility of product development, a provisional delivery schedule is agreed upon.

# 2. LSI Development

# (1) LSI design, prototype development

Based on the provisional delivery specifications agreed by the customer and FUJITSU, chip design and prototype work begins. The standard time required for an ES prototype is approximately 10 weeks from the approval of provisional delivery specifications.

### (2) ES (engineering sample) evaluation

Both the customer and FUJITSU evaluate the ES prototype based on the provisional delivery specifications.

### (3) Final approval

If there are no problems with the evaluation, FUJITSU and the customer agree on final delivery specifications and end development, moving to the mass production stage. The standard lead time for delivery of mass production products is approximately three months.

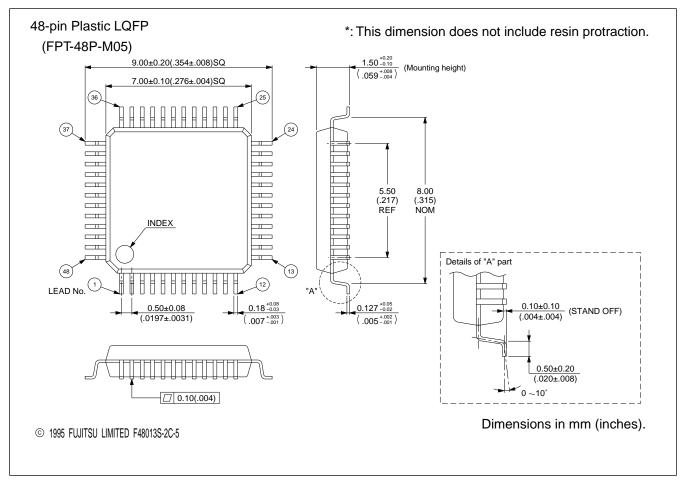

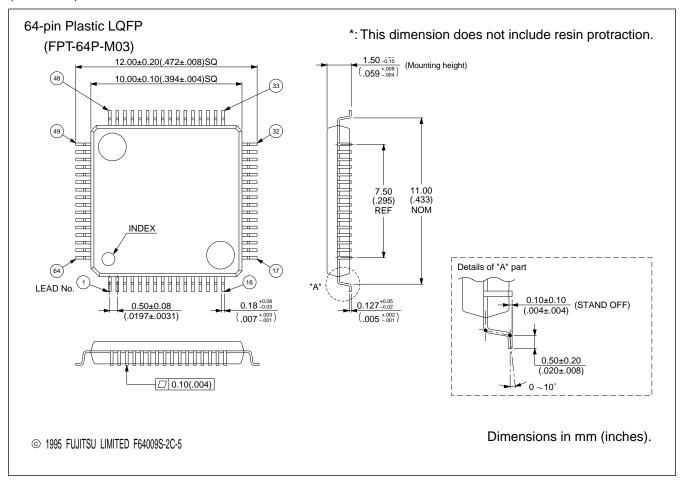

# **■ PACKAGE DIMENSIONS**

# **FUJITSU LIMITED**

For further information please contact:

#### **Japan**

FUJITSU LIMITED Corporate Global Business Support Division Electronic Devices KAWASAKI PLANT, 4-1-1, Kamikodanaka Nakahara-ku, Kawasaki-shi Kanagawa 211-88, Japan

Tel: (044) 754-3763 Fax: (044) 754-3329

#### **North and South America**

FUJITSU MICROELECTRONICS, INC. Semiconductor Division 3545 North First Street San Jose, CA 95134-1804, U.S.A.

Tel: (408) 922-9000 Fax: (408) 432-9044/9045

#### **Europe**

FUJITSU MIKROELEKTRONIK GmbH Am Siebenstein 6-10 63303 Dreieich-Buchschlag Germany Tel: (06103) 690-0

Fax: (06103) 690-0

#### **Asia Pacific**

FUJITSU MICROELECTRONICS ASIA PTE. LIMITED #05-08, 151 Lorong Chuan New Tech Park Singapore 556741

Tel: (65) 281-0770 Fax: (65) 281-0220

#### All Rights Reserved.

The contents of this document are subject to change without notice. Customers are advised to consult with FUJITSU sales representatives before ordering.

The information and circuit diagrams in this document presented as examples of semiconductor device applications, and are not intended to be incorporated in devices for actual use. Also, FUJITSU is unable to assume responsibility for infringement of any patent rights or other rights of third parties arising from the use of this information or circuit diagrams.

FUJITSU semiconductor devices are intended for use in standard applications (computers, office automation and other office equipment, industrial, communications, and measurement equipment, personal or household devices, etc.).

CAUTION:

Customers considering the use of our products in special applications where failure or abnormal operation may directly affect human lives or cause physical injury or property damage, or where extremely high levels of reliability are demanded (such as aerospace systems, atomic energy controls, sea floor repeaters, vehicle operating controls, medical devices for life support, etc.) are requested to consult with FUJITSU sales representatives before such use. The company will not be responsible for damages arising from such use without prior approval.

Any semiconductor devices have inherently a certain rate of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

If any products described in this document represent goods or technologies subject to certain restrictions on export under the Foreign Exchange and Foreign Trade Control Law of Japan, the prior authorization by Japanese government should be required for export of those products from Japan.

#### F9703

© FUJITSU LIMITED Printed in Japan