770 09194 D T-75-11-13

4302271 HARRIS SEMICOND SECTOR

# HC-5512C

## **PCM or CVSD Monolithic Filter**

## **FEATURES**

- +5V, -5V POWER SUPPLIES

- LOW POWER CONSUMPTION:

45mW (600Ω 0dBm LOAD) 30mW (POWER AMPS DISABLED)

- POWER DOWN MODE: 0.5mW

- 20dB GAIN ADJUST RANGE

- NO EXTERNAL ANTI-ALIASING COMPONENTS

- SIN x/x CORRECTION IN RECEIVE FILTER

- 50/60Hz REJECTION IN TRANSMIT FILTER

- TTL AND CMOS COMPATIBLE LOGIC

- ALL INPUTS PROTECTED AGAINST STATIC DISCHARGE DUE TO HANDLING

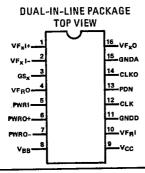

#### **PINOUT**

## **DESCRIPTION**

The HC-5512C filter is a monolithic circuit containing both transmit and receive filters originally designed for PCM CODEC filtering applications in 8kHz sampled systems.

The filter lends itself well as a cost effective replacement of a discrete audio input/output filter for the continuously variable slope delta modulator (CVSD).

The filter is manufactured using double-poly silicon gate CMOS technology. Switched capacitor integrators are used to simulate classical LC ladder filters which exhibit low component sensitivity.

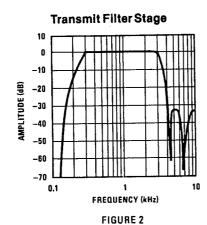

## TRANSMIT FILTER STAGE

The transmit filter is a fifth order elliptic low pass filter in series with a fourth order Chebyshev high-pass filter. It provides a flat response in the passband and rejection of signals below 200Hz and above 3.4kHz.

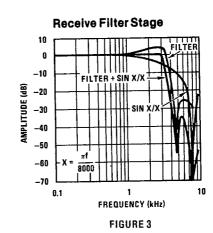

## RECEIVE FILTER STAGE

The receive filter is a fifth order elliptic low pass filter designed to reconstruct the voice signal from the decoded/demultiplexed signal which, as a result of the sampling process, is a stairstep signal having the inherent sin x/x frequency response. The receive filter approximates the function required to compensate for the degraded frequency response and restore the flat passband

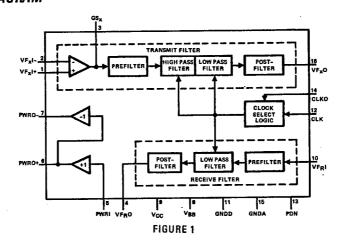

## FUNCTIONAL DIAGRAM

## 4302271 HARRIS SEMICOND SECTOR

**SPECIFICATIONS**

770 09195

T-75-11-13

## **ABSOLUTE MAXIMUM RATINGS**

Supply Voltages

Power Dissipation

Input Voltage

Output Short-Circuit Duration

Operating Temperature Range

Storage Temperature

Lead Temperature (Soldering, 10 seconds)

±7V 1W/Package ±7V Continuous -55°C to +125°C

-65°C to +150°C 300°C

## DC ELECTRICAL CHARACTERISTICS

Unless otherwise noted,  $T_A = 0^{\circ}C$  to  $75^{\circ}C$ ,  $V_{CC} = 5.0V \pm 5\%$ ,  $V_{BB} = -5.0V \pm 5\%$ , clock frequency is 1.544MHz. Typical parameters are specified at  $T_A = 25^{\circ}C$ ,  $V_{CC} = 5.0V$ ,  $V_{BB} = -5.0V$ . Digital interface voltages measured with respect to digital ground, GNDD. Analog voltages measured with respect to analog ground, GNDA.

| Symbol             | Parameter                                          | Conditions                                               | Min                  | Тур | Max                   | Units |

|--------------------|----------------------------------------------------|----------------------------------------------------------|----------------------|-----|-----------------------|-------|

| POWER              | DISSIPATION                                        |                                                          |                      |     |                       |       |

| I <sub>CC0</sub>   | V <sub>CC</sub> Standby Current                    | PDN = V <sub>DD</sub> , Power Down Mode                  |                      | 50  | 100                   | μА    |

| 1 <sub>880</sub>   | V <sub>BB</sub> Standby Current                    | PDN = V <sub>DD</sub> , Power Down Mode                  |                      | 50  | 100                   | μΑ    |

| CC1                | V <sub>CC</sub> Operating Current                  | PWRI = V <sub>BB</sub> , Power Amp Inactive              |                      | 3.0 | 4.5                   | mA    |

| BB1                | V <sub>BB</sub> Operating Current                  | PWRI = V <sub>BB</sub> , Power Amp Inactive              |                      | 3.0 | 4,5                   | mΑ    |

| l <sub>CC2</sub>   | V <sub>CC</sub> Operating Current                  | Note 1                                                   |                      | 4.6 | 6.4                   | mA    |

| BB2                | V <sub>BB</sub> Operating Current                  | Note 1                                                   |                      | 4.6 | 6.4                   | mA    |

| DIGITAL            | INTERFACE                                          |                                                          |                      |     |                       |       |

| I <sub>INC</sub>   | Input Current, CLK                                 | GNDD ≤ V <sub>IN</sub> ≤ V <sub>CC</sub>                 | -10                  |     | 10                    | μΑ    |

| I <sub>INP</sub>   | Input Current, PDN                                 | GNDD ≤ V <sub>IN</sub> ≤ V <sub>CC</sub>                 | - 100                |     |                       | μΑ    |

| I <sub>INO</sub>   | Input Current, CLK0                                | V <sub>BB</sub> ≤V <sub>IN</sub> ≤V <sub>CC</sub> - 0.5V | - 10                 |     | 0                     | μΑ    |

| V <sub>IL</sub>    | input Low Voltage, CLK, PDN                        |                                                          | 0                    |     | 0.8                   | ٧     |

| V <sub>IH</sub>    | Input High Voltage, CLK, PDN                       |                                                          | 2.2                  |     | V <sub>CC</sub>       | ٧     |

| V <sub>ILO</sub>   | input Low Voltage, CLK0                            |                                                          | V <sub>BB</sub>      |     | V <sub>BB</sub> + 0.5 | ٧     |

| V <sub>IIO</sub>   | Input Intermediate Voltage, CLK0                   |                                                          | - 0.8                |     | 0.8                   | ٧     |

| V <sub>IHO</sub>   | Input High Voltage, CLK0                           |                                                          | V <sub>CC</sub> -0.5 |     | V <sub>CC</sub>       | ٧     |

| TRANS              | MIT INPUT OP AMP                                   |                                                          |                      |     |                       |       |

| IB <sub>x</sub> I  | Input Leakage Current, VF <sub>x</sub> I           | V <sub>BB</sub> ≤VF <sub>x</sub> I≤V <sub>CC</sub>       | -100                 |     | 100                   | nΑ    |

| Rl <sub>x</sub> l  | Input Resistance, VF <sub>x</sub> I                | V <sub>BB</sub> ≤VF <sub>x</sub> I≤V <sub>CC</sub>       | 10                   |     |                       | МΩ    |

| vos <sub>x</sub> ı | Input Offset Voltage, VF <sub>x</sub> I            |                                                          | -20                  |     | 20                    | m۷    |

| V <sub>CM</sub>    | Common-Mode Range, VF <sub>x</sub> I               |                                                          | -2.5                 |     | 2.5                   | ٧     |

| CMRR               | Common-Mode Rejection Ratio                        | -2,5V ≤ V <sub>IN</sub> ≤ +2,5V                          | 60                   |     |                       | dB    |

| PSRR               | Power Supply Rejection of $V_{CC}$ or $V_{BB}$     |                                                          | 60                   |     |                       | dB    |

| R <sub>OL</sub>    | Open Loop Output Resistance,<br>GS <sub>x</sub>    |                                                          |                      | 1   |                       | kΩ    |

| $R_L$              | Minimum Load Resistance, GS <sub>x</sub>           |                                                          | 10                   |     |                       | kΩ    |

| CL                 | Maximum Load Capacitance, GS <sub>x</sub>          |                                                          |                      |     | 100                   | pF    |

| VO <sub>x</sub> I  | Output Voltage Swing, GS <sub>x</sub>              | R <sub>L</sub> ≥ 10k                                     | ± 2.5                |     |                       | ٧     |

| A <sub>VOL</sub>   | Open Loop Voltage Gain, GS <sub>x</sub>            | R <sub>L</sub> ≥ 10k                                     | 3400                 |     |                       | V/V   |

| F <sub>c</sub>     | Open Loop Unity Gain Bandwidth,<br>GS <sub>x</sub> |                                                          |                      | 2   |                       | MH:   |

TELECOM- WUNICATIONS

# **SPECIFICATIONS**

## AC ELECTRICAL CHARACTERISTICS

Unless otherwise specified,  $T_A = 25^{\circ}C$ . All parameters are specified for a signal level of 0 dBm0 at 1kHz. The 0 dBm0 level is assumed to be 1.54 Vrms measured at the output of the transmit or receive filter.

| Symbol            | Parameter                                                                 | Conditions                                                                                                       | Min                                 | Тур          | Max                                                                  | Units                                  |

|-------------------|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-------------------------------------|--------------|----------------------------------------------------------------------|----------------------------------------|

| RANSI<br>nless ot | AIT FILTER (Transmit filter inpu<br>herwise noted.)                       | t op amp set to the non-inverting unit                                                                           | y gain mod                          | de, with V   | F <sub>X</sub> I = 1.                                                | .09 Vr                                 |

| RL <sub>x</sub>   | Minimum Load Resistance                                                   | -3.2V < V <sub>OUT</sub> < 3.2V                                                                                  | 10                                  |              |                                                                      | kΩ                                     |

| CLx               | Load Capacitance, VF <sub>x</sub> O                                       |                                                                                                                  |                                     | ĺ            | 100                                                                  | pF                                     |

| RO <sub>x</sub>   | Output Resistance, VF <sub>x</sub> O                                      |                                                                                                                  | ĺ                                   | 1            | 3                                                                    | Ω                                      |

| PSRR1             | V <sub>CC</sub> Power Supply Rejection, VF <sub>x</sub> O                 | f=1 kHz, VF <sub>x</sub> l+=0 Vrms                                                                               | 30                                  |              |                                                                      | dΒ                                     |

| PSRR2             | V <sub>BB</sub> Power Supply Rejection, VF <sub>x</sub> O                 | Same as Above                                                                                                    | 30                                  |              |                                                                      | ₫B                                     |

| GA <sub>x</sub>   | Absolute Gain                                                             | f = 1 kHz                                                                                                        | 2.8                                 | 3,0          | 3.2                                                                  | dB                                     |

| GR <sub>x</sub>   | Gain Relative to GA <sub>x</sub>                                          | Below 50 Hz<br>50 Hz<br>60 Hz<br>200 Hz<br>300 Hz to 3 kHz<br>3.3 kHz<br>3.4 kHz<br>4.0 kHz<br>4.6 kHz and Above | - 1.5<br>- 0.15<br>- 0.45<br>- 0.70 | - 41<br>- 35 | - 35<br>- 35<br>- 30<br>0.2<br>0.15<br>0.25<br>- 0.1<br>- 14<br>- 32 | dB<br>dB<br>dB<br>dB<br>dB<br>dB<br>dB |

| DA <sub>x</sub>   | Absolute Delay at 1 kHz                                                   |                                                                                                                  |                                     |              | 230                                                                  | μS                                     |

| DD <sub>x</sub>   | Differential Envelope Delay from<br>1 kHz to 2.6 kHz                      |                                                                                                                  |                                     |              | 60                                                                   | μS                                     |

| DP <sub>x</sub> 1 | Single Frequency Distortion Products                                      |                                                                                                                  |                                     |              | <i>–</i> 40                                                          | d₿                                     |

| DP <sub>x</sub> 2 | Distortion at Maximum Signal Level                                        | 0,16Vrms,1 kHz Signal Applied to VF <sub>x</sub> l + , Gain = 20 dB, R <sub>L</sub> = 10k                        |                                     |              | - 40                                                                 | dB                                     |

| NC <sub>x</sub> 1 | Total C Message Noise at VF <sub>x</sub> O with V <sub>IN</sub> = 0       |                                                                                                                  |                                     |              | 10                                                                   | dBrnc                                  |

| NC <sub>x</sub> 2 | Total C Message Noise at VF <sub>x</sub> O with V <sub>IN</sub> = 0       | Gain Setting Op Amp at 20 dB,<br>Non-Inverting, Note 3                                                           |                                     |              | 10                                                                   | dBrnc                                  |

| GA <sub>x</sub> T | Temperature Coefficient of 1 kHz Gain                                     |                                                                                                                  |                                     | 0.0004       |                                                                      | dB/°C                                  |

| GA <sub>x</sub> S | Supply Voltage Coefficient of 1 kHz Gain                                  |                                                                                                                  | !                                   | 0.01         |                                                                      | dB/V                                   |

| CT <sub>RX</sub>  | Crosstalk, Receive to Transmit 20 log VF <sub>x</sub> O VF <sub>B</sub> O | Receive Filter Output = 2.2 Vrms<br>$VF_xI + = 0 Vrms$ , $f = 0.2 kHz$ to 3.4 kHz<br>Measure $VF_xO$             |                                     |              | - 60                                                                 | dB                                     |

| GR <sub>x</sub> L | Gaintracking Relative to GA <sub>x</sub>                                  | Output Level = +3 dBm0<br>+2 dBm0 to - 40 dBm0<br>-40 dBm0 to -55 dBm0                                           | -0.1<br>-0.05<br>-0.1               |              | 0.1<br>0.05<br>0.1                                                   | dB<br>dB                               |

T-75-11-13

4302271 HARRIS SEMICOND SECTOR

770 09197

## **SPECIFICATIONS**

## AC ELECTRICAL CHARACTERISTICS (Continued)

Unless otherwise specified,  $T_A = 25^{\circ}C$ . All parameters are specified for a signal level of 0 dBm0 at 1KHz. The 0 dBm0 level is assumed to be 1.54 Vrms measured at the output of the transmit or receive filter.

| Symbol            | Parameter                                                                 | Conditions                                                                                                           | Min                       | Тур        | Max                                      | Units                      |

|-------------------|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|---------------------------|------------|------------------------------------------|----------------------------|

|                   | VE FILTER (Unless otherwise no<br>1.54 Vrms.)                             | ted, the receive filter is preceded by a                                                                             | sin x/x filt              | er with ar | input si                                 | gnal                       |

| IB <sub>R</sub>   | Input Leakage Current, VF <sub>R</sub> I                                  | -2.5V≤V <sub>IN</sub> ≤2.5V                                                                                          | -100                      |            | 100                                      | nA                         |

| RIR               | input Resistance, VF <sub>R</sub> I                                       |                                                                                                                      | 10                        | :          |                                          | МΩ                         |

| ROR               | Output Resistance, VF <sub>R</sub> O                                      |                                                                                                                      |                           | 1          | 3                                        | Ω                          |

| CLR               | Load Capacitance, VF <sub>R</sub> O                                       |                                                                                                                      |                           |            | 100                                      | pF                         |

| RLR               | Load Resistance, VF <sub>R</sub> O                                        |                                                                                                                      | 10                        |            |                                          | kΩ                         |

| PSRR3             | Power Supply Rejection of $V_{CC}$ or $V_{BB}$ , $VF_{RO}$                | VF <sub>R</sub> I Connected to GNDA<br>f = 1 kHz                                                                     | 30                        |            |                                          | ₫B                         |

| VOSRO             | Output DC Offset, VF <sub>R</sub> O                                       | VF <sub>R</sub> I Connected to GNDA                                                                                  | -200                      |            | 200                                      | m۷                         |

| GAR               | Absolute Gain                                                             | f = 1 kHz                                                                                                            | - 0.2                     | 0          | 0.2                                      | dB                         |

| GR <sub>R</sub>   | Gain Relative to Gain at 1 kHz                                            | Below 300 Hz<br>300 Hz to 3.0 kHz<br>3.3 kHz<br>3.4 kHz<br>4.0 kHz<br>4.6 kHz and Above                              | - 0.15<br>- 0.45<br>- 0.7 |            | 0.125<br>0.15<br>0.25<br>0.1<br>14<br>32 | dB<br>dB<br>dB<br>dB<br>dB |

| DAR               | Absolute Delay at 1 kHz                                                   |                                                                                                                      |                           |            | 100                                      | μS                         |

| DDR               | Differential Envelope Delay 1 kHz to 2.6 kHz                              |                                                                                                                      |                           |            | 100                                      | μS                         |

| DP <sub>R</sub> 1 | Single Frequency Distortion<br>Products                                   | f = 1 kHz                                                                                                            |                           |            | - 40                                     | dB                         |

| DP <sub>R</sub> 2 | Distortion at Maximum Signal<br>Level                                     | 2.2 Vrms Input to Sin x/x Filter,<br>f = 1 kHz, R <sub>L</sub> = 10k                                                 |                           |            | - 40                                     | dB                         |

| NCR               | Total C-Message Noise at VF <sub>R</sub> O                                |                                                                                                                      |                           |            | 10                                       | dBrnc                      |

| GA <sub>R</sub> T | Temperature Coefficient of 1 kHz<br>Gain                                  |                                                                                                                      |                           | 0.0004     |                                          | dB/°C                      |

| GA <sub>R</sub> S | Supply Voltage Coefficient of 1 kHz Gain                                  |                                                                                                                      |                           | 0.01       |                                          | dB/V                       |

| CT <sub>XR</sub>  | Crosstalk, Transmit to Receive 20 log VF <sub>R</sub> O VF <sub>x</sub> O | Transmit Filter Output = 2.2 Vrms<br>VF <sub>R</sub> I = 0 Vrms, f = 0.3 kHz to 3.4 kHz<br>Measure VF <sub>R</sub> O |                           | -          | -60                                      | dB                         |

| GR <sub>R</sub> L | Gaintracking Relative to GA <sub>R</sub>                                  | Output Level = + 3 dBm0<br>+2 dBm0 to - 40 dBm0<br>- 40 dBm0 to - 55 dBm0<br>Note 5                                  | - 0.1<br>- 0.05<br>- 0.1  |            | 0.1<br>0.05<br>0.1                       | dB<br>dB<br>dB             |

8 TELECOM-MUNICATIONS

# **SPECIFICATIONS**

## AC ELECTRICAL CHARACTERISTICS (Continued) -

Unless otherwise specified, TA = 25°C. All parameters are specified for a signal level of 0 dBm0 at 1KHz. The 0 dBm0 level is assumed to be 1.54 Vrms measured at the output of the transmit or receive filter.

| Symbol            | Parameter                                                    | Conditions                                                                                          | Min            | Тур     | Max          | Units            |

|-------------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|----------------|---------|--------------|------------------|

|                   | E OUTPUT POWER AMPLIFIER                                     |                                                                                                     |                |         |              |                  |

| IBP               | Input Leakage Current, PWRI                                  | $-2.5V \le V_{1N} \le 2.5V$                                                                         | 0.1<br>10      |         | 3            | μ <b>Α</b><br>ΜΩ |

| RIP<br>ROP1       | Input Resistance, PWRI Output Resistance, PWRO +. PWRO -     | Amplifiers Active                                                                                   |                | 1 .     |              | Ω                |

| CLP               | Load Capacitance, PWRO + . PWRO -                            |                                                                                                     |                |         | 500          | pF               |

| GA <sub>P</sub> + | Gain, PWRI to PWRO +<br>Gain, PWRI to PWRO -                 | $R_L = 600\Omega$ Connected Between PWRO + and PWRO Input Level = 0 dBm0 (Note 4)                   |                | 1<br>-1 |              | V/\<br>V/\       |

| GR <sub>P</sub> L | Gaintracking Relative to 0 dBm0 Output Level                 | $V = 2.05 \text{ Vrms}, R_L = 600\Omega$<br>$V = 1.75 \text{ Vrms}, R_L = 300\Omega$ (Notes 4, 5)   | - 0.1<br>- 0.1 |         | 0.1<br>0.1   | dE<br>dE         |

| S/D <sub>P</sub>  | Signal/Distortion                                            | $V = 2.05 \text{ Vrms. } R_L = 600\Omega$<br>$V = 1.75 \text{ Vrms. } R_L = 300\Omega$ (Notes 4. 5) |                |         | - 45<br>- 45 | dE<br>dE         |

| VOSP              | Output DC Offset, PWRO + .                                   | PWRI Connected to GNDA                                                                              | - 50           |         | 50           | m'               |

| PSRR5             | Power Supply Rejection of V <sub>CC</sub> or V <sub>BB</sub> | PWRI Connected to GNDA                                                                              | 45             |         |              | dl               |

Note 1: Maximum power consumption will depend on the load impedance connected to the power amplifier. The specification listed assumes 0 dBm is delivered to  $600\Omega$  connected from PWRO+ to PWRO-. Note 2: Voltage input to receive filter at 0V, VFRO connected to PWRI,  $600\Omega$  from PWRO+ to PWRO-. Output measured from PWRO+ to PWRO-.

Note 3: The 0dBm0 level for the filter is assumed to be 1,54 Vrms measured at the output of the XMT or RCV filter. Note 4: The 0dBm0 level for the power amplifiers is load dependent. For  $R_L = 600\Omega$  to GNDA the 0dBm0 level is 1.43 Vrms measured at the amplifier output for  $R_L = 300\Omega$  the 0dBm0 level is 1.22Vrms. Note 5: VFRO connected to PWRI, input signal applied to VFRI.

# TYPICAL PERFORMANCE CHARACTERISTICS

770 09199

# 4302271 HARRIS SEMICOND SECTOR

# PIN ASSIGNMENTS

| Pin<br>No. | Name               | Function                                                                                                                                           |

|------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | VF <sub>x</sub> i+ | The non-inverting input to the transmit filter stage.                                                                                              |

| 2          | VF <sub>x</sub> I  | The inverting input to the transmit filter stage.                                                                                                  |

| 3          | GS <sub>x</sub>    | The output used for gain<br>adjustments of the transmit<br>filter.                                                                                 |

| 4          | VF <sub>R</sub> O  | The low power receive filter output. This pin can directly drive the receive port of an electronic hybrid.                                         |

| 5          | PWRI               | The input to the receive filter differential power amplifier.                                                                                      |

| 6          | PWRO +             | The non-inverting output of<br>the receive filter power<br>amplifier. This output can<br>directly interface conven-<br>tional transformer hybrids. |

| 7          | PWRO –             | The inverting output of the receive filter power amplifier. This output can be used with PWRO + to differentially drive a transformer hybrid.      |

| 8          | V <sub>BB</sub>    | The negative power supply pin. Recommended input is – 5V.                                                                                          |

| 9          | V <sub>CC</sub>    | The positive power supply<br>pin. The recommended input<br>is 5V.                                                                                  |

| 10         | VF <sub>R</sub> I  | The input pin for the receive filter stage.                                                                                                        |

| Pin<br>No. | Name              | Function                                                                                                                                                                    |

|------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11         | GNDD              | Digital ground input pin. All digital signals are referenced to this pin.                                                                                                   |

| 12         | CLK               | Master input clock. Input fre-<br>quency can be selected as<br>2.048 MHz, 1.544 MHz or<br>1.536 MHz.                                                                        |

| 13         | PDN               | The input pin used to power down the HC-5512C during idle periods. Logic 1 (V <sub>CC</sub> ) input voltage causes a power down condition. An internal pull-up is provided. |

| 14         | CLK0              | This input pin selects in-<br>ternal counters in accord-<br>ance with the CLK input<br>clock frequency:                                                                     |

|            |                   | CLK Connect CLK0 to:                                                                                                                                                        |

|            |                   | 2048 kHz V <sub>CC</sub><br>1544 kHz GNDD<br>1536 kHz V <sub>BB</sub><br>An internal pull-up is<br>provided.                                                                |

| 15         | GNDA              | Analog ground input pin. All<br>analog signals are refer-<br>enced to this pin. Not inter-<br>nally connected to GNDD.                                                      |

| 16         | VF <sub>x</sub> O | The output of the transmit filter stage.                                                                                                                                    |

TELECOM-MUNICATIONS

the property of the second

## **FUNCTIONAL DESCRIPTION**

The HC-5512C monolithic filter contains four main sections; Transmit Filter, Receive Filter, Receive Filter Power Amplifier, and Frequency Divider/Select Logic (Figure 1). A brief description of the operation for each section is provided below.

## Transmit filter

The input stage of the transmit filter is a CMOS operational amplifier which provides an input resistance of greater than  $10M\Omega$ , a voltage gain of greater than 3,400, low power consumption (less than 3mW), high power supply rejection, and is capable of driving a  $10k\Omega$  load in parallel with up to 100pF. The inputs and output of the amplifier are accessible for added flexibility. Noninverting mode, inverting mode, or differential amplifier mode operation can be implemented with external resistors. It can also be connected to provide a gain of up to 20dB without degrading the overall filter performance.

The input stage is followed by a prefilter which is a two-pole RC active low pass filter designed to attenuate high frequency noise before the input signal enters the switched-capacitor high pass and low pass filters.

A high pass filter is provided to reject 200Hz or lower noise which may exist in the signal path. The low pass portion of the switched-capacitor filter provides stopband attenuation.

The output stage of the transmit filter, the postfilter, is also a two-pole RC active low pass filter which attenuates clock frequency noise by a least 40dB. The output of the transmit filter is capable of driving a  $\pm 2.5 V$  peak to peak signal into a  $10 k\Omega$  load in parallel with up to 100 pF.

#### Receive Filter

The input stage of the receive filter is a prefilter which is similar to the transmit prefilter. The prefilter attenuates high frequency noise that may be present on the receive input signal. A switched capacitor low pass

filter follows the prefilter to provide the necessary passband flatness, stopband rejection and sin x/x gain correction. A postfilter which is similar to the transmit postfilter follows the low pass stage. It attenuates clock frequency noise and provides a low output impedance capable of directly driving an electronic subscriber-line-interface circuit.

#### Receive Filter Power Amplifiers

Two power amplifiers are also provided to interface to transformer coupled line circuits in PCM applications. These two amplifiers are driven by the output of the receive postfilter through gain setting resistors, R3, R4 (Figure 4). The power amplifiers can be deactivated, when not required, by connecting the power amplifier input (pin 5) to the negative power supply VBB. This reduces the total filter power consumption by approximately 10mW-20mW depending on output signal amplitude.

#### **Power Down Control**

A power down mode is also provided. A logic 1 power down command applied on the PDN pin (pin 13) will reduce the total filter power consumption to less than 1mW. If the PWRI pin (pin 5) is connected to VBB, the power amplifier output will enter a high impedance (tri-state) mode. Otherwise, the power amplifier output will be clamped to VBB.

#### Frequency Divider and Select Logic Circuit

This circuit divides the external clock frequency down to the switching frequency of the low pass and high pass switched capacitor filters. The divider also contains a TTL-CMOS interface circuit which converts the external TTL clock level to the CMOS logic level required for the divider logic. This interface circuit can also be directly driven by CMOS logic. A frequency select circuit is provided to allow the filter to operate with 2.048MHz, 1.544MHz or 1.536MHz clock frequencies. By connecting the frequency select pin CLKO (pin 14) to VCC, a 2.048MHz clock input frequency is selected. Digital ground selects 1.544MHz and VBB selects 1.536MHz.

HARRIS SEMICOND SECTOR

.8

TELECOM-MUNICATIONS

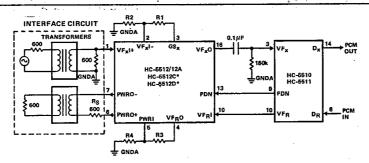

# INTERFACE CIRCUIT FOR HC-5510 CODEC

: Transmit voltage gain =  $\frac{R1 + R2}{R2} \times \sqrt{2}$  (The filter itself introduces a 3dB gain) (R1 +R2  $\geq$  10k).

Note 2: Receive gain = R4 (R3 + R4 ≥ 10k)

#### FIGURE 4

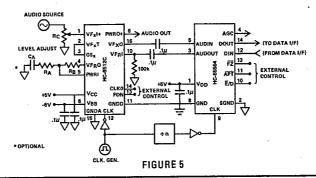

## INTERFACE CIRCUIT FOR HC-55564 CVSD

## APPLICATIONS INFORMATION

## Gain Adjust

Figure 4 shows the signal path interconnections between the HC-5512C and HC-5510 single channel CODEC. The transmit RC coupling components have been chosen both for minimum passband droop and to present the correct impedance to the CODEC during sampling.

Figure 5 shows the signal path interconnections between the HC-5512C and the HC-55564 CVSD. For the circuit shown, the audio signal into the CVSD should be 1Vp-p over the 3.2kHz band to obtain a flat response. RA, RB and CA form a simple lead lag filter at the output of the HC-5512C receive filter which introduces a pole and a zero at 3.3kHz to help compensate against the filters' inherent sin x/x characteristic. (See Figure 3). Note that the transmit side of the filter provides an inherent +3dB voltage gain, and the resistor RD, at VFRI causes a voltage loss from audio out to VFRI, owing to the 100K  $\!\Omega$  output impedance of the CVSD at audio out. Generally, the higher the RD value used, the more thermal noise introduced to the circuit.

Optimum noise and distortion performance will be obtained for the HC-5512C filter when operated with system peak

overload voltages of ±2.5V to ±3.2 at VFxO and VFRO. When interfacing to a PCM CODEC or CVSD with a peak overload voltage outside this range, further gain or attenuation may be required.

For example, the HC-5512/5512A/5512C/5512D filter can be used with the HC-5510/5511 series CODEC which has a 5.5V peak overload voltage, or with the HC-55564 CVSD which has a 4.0V peak overload voltage. A gain stage following the transmit filter output and an attenuation stage following the CODEC or CVSD output are required in this case.

#### **Board Layout**

Care must be taken in PCB layout to minimize power supply and ground noise. Analog ground of each filter and each CVSD should be connected to digital ground at a single point, which should be bypassed to both power supplies. Further power supply decoupling adjacent to each filter and CODEC, and each filter and CVSD is recommended. Ground loops should be avoided between GNDA and GNDD, between the GNDA traces of adjacent filters and CODECs, and between the analog ground traces of adjacent filters and CVSDs.