# 53/63RS881/A

Advanced Micro Devices

# High Performance 1024x8 Registered PROM

#### FEATURES/BENEFITS

- · Edge triggered "D" registers

- · Synchronous and asynchronous enables

- · Versatile 1:16 initialization words

- 8-Bit-wide in 24-pin SKINNYDIP® package for high board density

- · Simplifies system timing

- · Faster cycle times

- · 16 mA IOL output drive capability

- Reliable titanium-tungsten fuses (TIW), with programming yields typically greater than 98%

#### **APPLICATIONS**

- · Microprogram control store

- State sequencers

- Next address generation

- Mapping PROM

- Programmable Logic Element (PLE™) 10 inputs, 8 Registered Outputs, 1024 product terms

#### DESCRIPTION

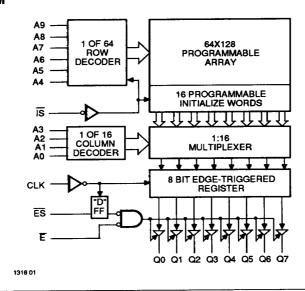

The 53/63RS881 and 53/63RS881A are 1Kx8 PROMs with on-chip "D" type registers, versatile output enable control through synchronous and asynchronous enable inputs, and flexible start-up sequencing through programmable initialization.

Data is transferred into the output registers on the rising edge of the clock. Provided that the asynchronous (Ē) and synchronous (ĒS) enables are LOW, the data will appear at the outputs. Prior to the positive clock edge, register data are not affected by changes in addressing or synchronous enable inputs.

Memory expansion and data control is made flexible with synchronous and asynchronous enable inputs. Outputs may be set to the high-impedance state at any time by setting  $\overline{E}$  to a HIGH or if  $\overline{ES}$  is HIGH when the rising clock edge occurs. When  $V_{cc}$  power is first ap-

plied, the synchronous enable flip-flop will be in the set condition, causing the outputs to be in the high-impedance state.

The flexible initialization feature allows start-up and time-out sequencing with 1:16 programmable words to be loaded into the output registers. With the synchronus INITIALIZE (IS) pin LOW, one of the sixteen column words (A3–A0) will be set in the output registers independent of the row addresses (A9–A4). The unprogrammed state of IS words are LOW, presenting a CLEAR with IS pin LOW. With all IS column words (A3–A0) programmed to the same pattern, the IS function will be independent of both row and column addressing and may be used as a single pin control. With all IS words programmed HIGH, a PRESET function is performed.

# **SELECTION GUIDE**

| Memory |              | Package |                               |             | Part Number  |                 |  |  |

|--------|--------------|---------|-------------------------------|-------------|--------------|-----------------|--|--|

| Size   | Organization | Pins    | Туре                          | Performance | 0°C to +75°C | -55°C to +125°C |  |  |

| 8K     | 1024x8       |         | CD 3024<br>PD 3024            | Enhanced    | 63RS881A     | 53RS881A        |  |  |

|        |              | (28)    | PL 028<br>. CL 024<br>CFM 024 | Standard    | 63RS881      | 53RS881         |  |  |

SKINNYDIP® is a registered trademark of Advanced Micro Devices. PLE™ is a trademark of Advanced Micro Devices. Publication # Rev. Amendment

11205 A /O

Issue Date: October 1988

### **BLOCK DIAGRAM**

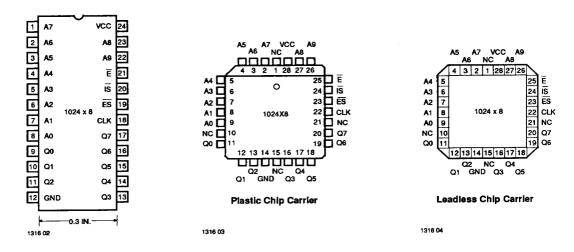

### PIN CONFIGURATIONS

5-202

53/63RS881/A

# **ABSOLUTE MAXIMUM RATINGS**

#### Operating Programming

| Supply voltage V <sub>cc</sub> | 0.5 V to 7 V   | 12 V |

|--------------------------------|----------------|------|

| Input voltage                  |                |      |

| Input current                  | 30 mA to +5 mA |      |

| Off-state output voltage       | 0.5 V to 5.5 V | 12 V |

| Storage temperature            | 65°C to +150°C |      |

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to Absolute Maximum Rating conditions for extended periods of time may affect relaibility. Absolute Maximum Ratings are for system design reference; parameters given are not tested.

## **Operating Conditions**

| Symbol                                    |                                  | Typt | Military†† |     |         |     | Commercial |      |         |      |      |

|-------------------------------------------|----------------------------------|------|------------|-----|---------|-----|------------|------|---------|------|------|

|                                           | Parameter                        |      | 53RS881A   |     | 53RS881 |     | 63RS881A   |      | 63RS881 |      | Unit |

|                                           |                                  |      | Min        | Max | Min     | Max | Min        | Max  | Min     | Max  |      |

| t,                                        | Width of clock (High or Low)     | 10   | 20         |     | 20      |     | 20         |      | 20      |      | ns   |

| t <sub>e(A)</sub>                         | Setup time from address to clock | 25   | 40         |     | 45      |     | 30         |      | 35      |      | ns   |

| t <sub>s(ES)</sub>                        | Setup time from ES to clock      | 8    | 15         |     | 15      |     | 15         |      | 15      |      | ns   |

| t <sub>e( \overline{1}\overline{5})</sub> | Setup time from IS to clock      | 20   | 30         |     | 35      |     | 25         |      | 30      |      | ns   |

| t <sub>h(A)</sub>                         | Hold time address to clock       | -5   | 0          |     | 0       |     | 0          |      | 0       |      | ns   |

| t <sub>h(ES)</sub>                        | Hold time (ES)                   | -3   | 5          |     | 5       |     | 5          |      | 5       |      | ns   |

| t <sub>h([S)</sub>                        | Hold time (IS)                   | 5    | 0          |     | 0       |     | 0          |      | 0       |      | ns   |

| V <sub>cc</sub>                           | Supply voltage                   | 5    | 4.5        | 5.5 | 4.5     | 5.5 | 4.75       | 5.25 | 4.75    | 5.25 | ٧    |

| T <sub>A</sub>                            | Operating temperature*           | 25   | -55        | 125 | -55     | 125 | 0          | 75   | 0       | 75   | ∘c   |

<sup>\*</sup> This is defined as the instant-on case temperature.\*

<sup>†</sup> Typicals at 5.0 V V<sub>cc</sub> and 25°C T<sub>A</sub>.

<sup>††</sup> Military burn-in is in accordance with the current revision of MIL-STD-883, Test Method 1015, Conditions A through E. Test conditions are selected at AMD's option.

**Electrical Characteristics** Over Operating Conditions. For APL Products, Group A, Subgroups 1, 2, 3 are tested unless otherwise noted.

| Symbol           | Parameter                     | Т                        | est Condit                 | ions                                                 | Min | Typt | Max   | Unit |

|------------------|-------------------------------|--------------------------|----------------------------|------------------------------------------------------|-----|------|-------|------|

| V <sub>IL</sub>  | Low-level input voltage**     |                          |                            |                                                      |     |      | 0.8   | v    |

| V <sub>IH</sub>  | High-level input voltage**    |                          |                            |                                                      | 2.0 |      |       | V    |

| V <sub>ic</sub>  | Input clamp voltage           | V <sub>cc</sub> = MIN    | I, = -18                   | mA                                                   |     |      | -1.2  | V    |

| i,L              | Low-level input current       | V <sub>cc</sub> = MAX    | V <sub>1</sub> = 0.4       | V                                                    |     |      | -0.25 | mA   |

| l <sub>H</sub>   | High-level input current      | V <sub>cc</sub> = MAX    | VI = V <sub>c</sub>        | c MAX                                                |     |      | 40    | μА   |

| V <sub>ol</sub>  | Low-level output voltage      | V <sub>cc</sub> = MIN    | I <sub>oL</sub> = 16 mA    |                                                      |     |      | 0.5   | v    |

| V <sub>OH</sub>  | High-level output voltage     | V <sub>cc</sub> = MIN    | Com<br>Mil                 | i <sub>oH</sub> = -3.2 mA<br>i <sub>oH</sub> = -2 mA | 2.4 |      |       | v    |

| l <sub>ozL</sub> |                               |                          | V <sub>o</sub> = 0.        | 4 V                                                  |     |      | -40   |      |

| l <sub>ozh</sub> | Off-state output current      | V <sub>cc</sub> = MAX    | MAX V <sub>o</sub> = 2.4 V |                                                      |     |      | 40    | μА   |

| los              | Output short-circuit current* | V <sub>cc</sub> = 5 V    | V <sub>0</sub> = 0 \       | /                                                    | -20 |      | -90   | mA   |

| l <sub>cc</sub>  | Supply current                | V <sub>cc</sub> = MAX. A | 130                        | 180                                                  | mA  |      |       |      |

Not more than one output should be shorted at a time, and duration of the short-circuit should not exceed one second.

† Typicals at 5.0 V V<sub>cc</sub> and 25°C T<sub>A</sub>.

Switching Characteristics Over Operating Conditions and using Standard Test Load. For APL Products, Group A, subgroups 9, 10, 11 are tested unless otherwise noted.††

| Symbol           | Parameter                           | Typt | Military |     |         |     | Commercial |     |         |     |      |

|------------------|-------------------------------------|------|----------|-----|---------|-----|------------|-----|---------|-----|------|

|                  |                                     |      | 53RS881A |     | 53RS881 |     | 63RS881A   |     | 63RS881 |     | Unit |

|                  |                                     |      | Min      | Max | Min     | Max | Min        | Max | Min     | Max |      |

| t <sub>GLK</sub> | Clock to output Delay               | 10   |          | 20  |         | 25  |            | 15  |         | 20  | ns   |

| t <sub>ESA</sub> | Clock to output access time (ES)    | 18   |          | 30  |         | 35  |            | 25  |         | 30  | ns   |

| t <sub>ESR</sub> | Clock to output recovery time (ES)  | 17   |          | 30  |         | 35  |            | 25  |         | 30  | ns   |

| t <sub>EA</sub>  | Enable to output access time (E)    | 18   |          | 30  |         | 35  |            | 25  |         | 30  | ns   |

| t <sub>ER</sub>  | Disable to output recovery time (E) | 17   |          | 30  |         | 35  |            | 25  |         | 30  | ns   |

†† Subgroups 7 and 8 apply to Functional tests.

<sup>\*\*</sup> V<sub>IL</sub> and V<sub>IH</sub> are input conditions of output tests and are not themselves directly tested. V<sub>IL</sub> and V<sub>IH</sub> are absolute voltages with respect to device ground and include all overshoots due to system and/or tester noise. Do not attempt to test these values without suitable equipment.

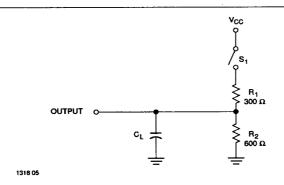

Figure 1. Switching Test Load

1316 06

1316 07

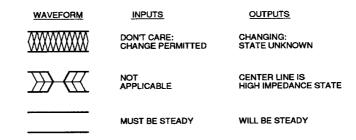

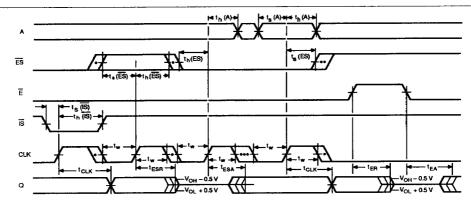

Figure 2. Definition of Timing Diagrams

NOTES: 1. INPUT PULSE AMPLITUDE OV TO 3.0 V.

- 2. INPUT RISE AND FALL TIMES 2-5 ns FROM 0.8 V TO 2.0 V.

- 3. INPUT ACCESS MEASURED AT THE 1.5 V LEVEL.

- 4.  $t_{AA}$  is tested with switch  $s_1$  closed,  $c_L = 30$  pF and MEASURED AT 1.5 V OUTPUT LEVEL.

- 5.  $t_{EA}$  AND  $t_{ESA}$  ARE MEASURED AT THE 1.5 V OUTPUT LEVEL WITH  $C_L = 30 \, \mathrm{pF}$ .  $S_1$  IS OPEN FOR HIGH IMPEDANCE TO "1" TEST, AND CLOSED FOR HIGH IMPEDANCE TO "0" TEST.

1 ER AND 1 ESR ARE TESTED WITH C L + 5 pF. S1 IS OPEN FOR "1" TO HIGH IMPEDANCE TEST, MEASURED AT VOH - 0.5 V OUTPUT LEVEL; S1 IS CLOSED FOR "O" TO HIGH IMPEDANCE TEST, MEASURED AT VOL + 0.5 V OUTPUT LEVEL.

Figure 3. Defintion of Waveforms

5-205