# Core8051s v2.4 Handbook

### **Actel Corporation, Mountain View, CA 94043**

© 2010 Actel Corporation. All rights reserved.

Printed in the United States of America

Part Number: 50200084-2 Release: September 2010

No part of this document may be copied or reproduced in any form or by any means without prior written consent of Actel.

Actel makes no warranties with respect to this documentation and disclaims any implied warranties of merchantability or fitness for a particular purpose. Information in this document is subject to change without notice. Actel assumes no responsibility for any errors that may appear in this document.

This document contains confidential proprietary information that is not to be disclosed to any unauthorized person without prior written consent of Actel Corporation.

#### **Trademarks**

Actel, Actel Fusion, IGLOO, Libero, Pigeon Point, ProASIC, SmartFusion and the associated logos are trademarks or registered trademarks of Actel Corporation. All other trademarks and service marks are the property of their respective owners.

# **Table of Contents**

| 1 Core8051s Overview 2 Supported Interfaces Ports Interface Descriptions 3 Tool Flows SmartDesign Example System Simulation Synthesis in Libero IDE Place-and-Route in Libero IDE 4 Core8051s Features Software Memory Map Interrupts OCI Block 5 Instruction Set Functional Ordered Instructions Hexadecimal Ordered Instructions Instruction Definitions C Compiler Support C Header Files 6 Instruction Timing Program Memory Bus Cycle External Data Memory Bus Cycle APB Bus Cycles | 17 20 21 21          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Ports Interface Descriptions  3 Tool Flows SmartDesign Example System Simulation Synthesis in Libero IDE Place-and-Route in Libero IDE  4 Core8051s Features Software Memory Map Interrupts OCI Block  5 Instruction Set Functional Ordered Instructions Hexadecimal Ordered Instructions Instruction Definitions C Compiler Support C Header Files  6 Instruction Timing Program Memory Bus Cycle External Data Memory Bus Cycle APB Bus Cycles                                         | 17 20 21 21          |

| SmartDesign Example System Simulation Synthesis in Libero IDE Place-and-Route in Libero IDE  4 Core8051s Features Software Memory Map Interrupts OCI Block  5 Instruction Set Functional Ordered Instructions Hexadecimal Ordered Instructions Instruction Definitions C Compiler Support C Header Files  6 Instruction Timing Program Memory Bus Cycle External Data Memory Bus Cycle APB Bus Cycles                                                                                    | 21<br>24             |

| Software Memory Map Interrupts OCI Block  5 Instruction Set Functional Ordered Instructions Hexadecimal Ordered Instructions Instruction Definitions C Compiler Support C Header Files  6 Instruction Timing Program Memory Bus Cycle External Data Memory Bus Cycle APB Bus Cycles                                                                                                                                                                                                      | 27                   |

| Functional Ordered Instructions Hexadecimal Ordered Instructions Instruction Definitions C Compiler Support C Header Files  Instruction Timing Program Memory Bus Cycle External Data Memory Bus Cycle APB Bus Cycles                                                                                                                                                                                                                                                                    | 29<br>34             |

| Program Memory Bus Cycle  External Data Memory Bus Cycle  APB Bus Cycles                                                                                                                                                                                                                                                                                                                                                                                                                 | 36<br>41<br>45<br>46 |

| 7 List of Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 51<br>53             |

| 7 List of Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                      |

| A Product Support Customer Service Actel Customer Technical Support Center Actel Technical Support Website Contacting the Customer Technical Support Center                                                                                                                                                                                                                                                                                                                              | 61<br>61<br>61<br>61 |

## Introduction

This document describes the architecture of a small, general-purpose processor, called the Core8051s. This processor is compatible with the instruction set of the 8051 microcontroller, and preserves the three distinct software memory spaces so that it may be targeted by existing 8051 C compilers. To make it smaller and more flexible than the 8051, the following microcontroller-specific features of the original 8051 are not present:

- SFR-mapped peripherals

- · Power management circuitry

- Serial channel

- I/O ports

- Timers

The following set of 8051 microcontroller features are available in Core8051s, but are either optional or reduced in scope:

- Multiply and divide instructions (MUL, DIV, and DA) present by default, but may optionally be implemented as NOPs

- Second data pointer (data pointer 1) not enabled by default

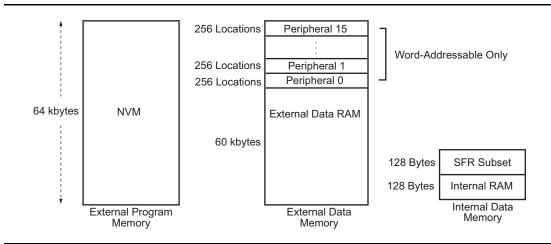

- Of the 64 kbytes allocated to external data memory, 4 kbytes are allocated to an APB-based peripheral bus and 60 kbytes is allocated to an external data memory interface

- Interrupt control logic for 2 interrupts

Supported Actel FPGA Families for the Core8051s are as follows:

- IGLOO<sup>®</sup>/e/PLUS

- ProASIC3®/E/L

- Fusion

- ProASICPLUS®

- Axcelerator<sup>®</sup>

- RTAX-S

## **Utilization and Performance**

Table 1 through Table 7 on page 13 give resource usage and performance data for various configurations of Core8051s for each type of FPGA technology. These tables do not cover every possible configuration, but instead list a range of configurations which should give a good indication of the expected resource usage and performance of the core. Abbreviated versions of configuration options are used in the tables to aid readability. The meanings of the entries in the debug, program memory access control, data memory access control, and internal RAM columns are described in the following paragraphs.

## **Debug Column**

- · None: Debug logic is not included.

- I/Os: Debug logic is included and general purpose I/Os are used for the debug connection.

- UJTAG: Debug logic is included and the dedicated JTAG pins of the device and the UJTAG macro are used for the debug connection.

## **Program Memory Access Control**

- ACK: Acknowledge signal (MEMPSACKI) is used to control access to program memory.

- X: X (where X can range from 0 to 7) wait states are inserted in each access to program memory, instead of using acknowledge control.

## **Data Memory Access Control**

- ACK: Acknowledge signal (MEMACKI) is used to control accesses to data memory.

- X: X (where X can range from 0 to 7) wait states are inserted in each access to data memory, instead of using acknowledge control.

#### **Internal RAM**

- Instantiated: Internal 256x8 RAM is implemented using an instantiated RAM block.

- Inferred: Internal 256x8 RAM is implemented by inferring RAM during synthesis.

## **Registers**

Registers (FPGA tiles) are inferred for the 256x8 RAM during synthesis.

Table 1 • Core8051s Utilization and Performance for IGLOO 1.2 V Devices (STD speed grade)

|       |                   |                   |                                | Configur                                 | ation                            |                               |                |              |        | zation<br>forma |      |

|-------|-------------------|-------------------|--------------------------------|------------------------------------------|----------------------------------|-------------------------------|----------------|--------------|--------|-----------------|------|

| Debug | Include Trace RAM | Hardware Triggers | Include Second<br>Data Pointer | Include MUL, DIV,<br>and DA Instructions | Program Memory<br>Access Control | Data Memory<br>Access Control | APB Data Width | Internal RAM | Tiles  | RAM Blocks      | MHz  |

| None  | _                 | _                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 3,435  | 1               | 14.8 |

| I/Os  | No                | 0                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 3,833  | 1               | 14.9 |

| ujtag | No                | 0                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 3,792  | 1               | 14.4 |

| ujtag | No                | 1                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 4,080  | 1               | 14.7 |

| ujtag | No                | 4                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 5,029  | 1               | 14.4 |

| ujtag | Yes               | 0                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 3,974  | 3               | 15.4 |

| ujtag | Yes               | 1                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 4,455  | 3               | 14.5 |

| ujtag | Yes               | 4                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 5,538  | 3               | 14.6 |

| None  | _                 | _                 | Yes                            | Yes                                      | ack                              | ack                           | 32             | Instantiated | 3,686  | 1               | 14.9 |

| None  | _                 | _                 | No                             | Yes                                      | 2                                | 2                             | 32             | Instantiated | 3,376  | 1               | 14.8 |

| None  | _                 | _                 | No                             | Yes                                      | 5                                | 5                             | 32             | Instantiated | 3,308  | 1               | 15.3 |

| None  | _                 | _                 | No                             | Yes                                      | ack                              | ack                           | 16             | Instantiated | 3,311  | 1               | 15.1 |

| None  | _                 | _                 | No                             | Yes                                      | ack                              | ack                           | 8              | Instantiated | 3,318  | 1               | 15.2 |

| None  | _                 | _                 | No                             | Yes                                      | ack                              | ack                           | 32             | Inferred     | 3,457  | 1               | 14.7 |

| None  | _                 | -                 | No                             | Yes                                      | ack                              | ack                           | 32             | Registers    | 7,853  | 0               | 13.9 |

| ujtag | Yes               | 4                 | Yes                            | Yes                                      | ack                              | ack                           | 32             | Registers    | 10,098 | 2               | 12.1 |

| None  | -                 | ı                 | No                             | No                                       | ack                              | ack                           | 8              | Instantiated | 2,849  | 1               | 14.7 |

Table 2 • Core8051s Utilization and Performance for IGLOO 1.5 V Devices (STD speed grade)

|       |                   |                   |                                | Configur                                 | ation                            |                               |                |              |       | zation<br>forma |      |

|-------|-------------------|-------------------|--------------------------------|------------------------------------------|----------------------------------|-------------------------------|----------------|--------------|-------|-----------------|------|

| Debug | Include Trace RAM | Hardware Triggers | Include Second<br>Data Pointer | Include MUL, DIV,<br>and DA Instructions | Program Memory<br>Access Control | Data Memory<br>Access Control | APB Data Width | Internal RAM | Tiles | RAM Blocks      | MHz  |

| None  | _                 | -                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 3,110 | 1               | 23.9 |

| I/Os  | No                | 0                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 3,548 | 1               | 22.7 |

| ujtag | No                | 0                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 3,483 | 1               | 24.3 |

| ujtag | No                | 1                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 3,772 | 1               | 23.6 |

| ujtag | No                | 4                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 4,847 | 1               | 23.3 |

| ujtag | Yes               | 0                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 3,742 | 3               | 22.9 |

| ujtag | Yes               | 1                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 4,083 | 3               | 23.9 |

| ujtag | Yes               | 4                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 5,125 | 3               | 23.8 |

| None  | -                 | _                 | Yes                            | Yes                                      | ack                              | ack                           | 32             | Instantiated | 3,318 | 1               | 24.2 |

| None  | -                 | _                 | No                             | Yes                                      | 2                                | 2                             | 32             | Instantiated | 3,386 | 1               | 24.2 |

| None  | _                 | _                 | No                             | Yes                                      | 5                                | 5                             | 32             | Instantiated | 3,357 | 1               | 22.9 |

| None  | _                 | _                 | No                             | Yes                                      | ack                              | ack                           | 16             | Instantiated | 2,995 | 1               | 24.5 |

| None  | -                 | _                 | No                             | Yes                                      | ack                              | ack                           | 8              | Instantiated | 2,915 | 1               | 23.9 |

| None  | 1                 | _                 | No                             | Yes                                      | ack                              | ack                           | 32             | Inferred     | 3,136 | 1               | 24.8 |

| None  | 1                 | _                 | No                             | Yes                                      | ack                              | ack                           | 32             | Registers    | 7,633 | 0               | 23.3 |

| UJTAG | Yes               | 4                 | Yes                            | Yes                                      | ack                              | ack                           | 32             | Registers    | 9,917 | 2               | 19.9 |

| None  | ı                 | -                 | No                             | No                                       | ack                              | ack                           | 8              | Instantiated | 2,568 | 1               | 23.8 |

Table 3 • Core8051s Utilization and Performance for Fusion, ProASIC3, and ProASIC3E Devices (-2 speed grade)

|       |                   |                   |                                | Configur                                 | ation                            |                               |                |              |       | zation<br>forma |      |

|-------|-------------------|-------------------|--------------------------------|------------------------------------------|----------------------------------|-------------------------------|----------------|--------------|-------|-----------------|------|

| Debug | Include Trace RAM | Hardware Triggers | Include Second<br>Data Pointer | Include MUL, DIV,<br>and DA Instructions | Program Memory<br>Access Control | Data Memory<br>Access Control | APB Data Width | Internal RAM | Tiles | RAM Blocks      | MHz  |

| None  | _                 | ı                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 3,324 | 1               | 37.1 |

| I/Os  | No                | 0                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 3,776 | 1               | 36.5 |

| ujtag | No                | 0                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 3,758 | 1               | 35.9 |

| ujtag | No                | 1                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 4,024 | 1               | 37.5 |

| ujtag | No                | 4                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 4,941 | 1               | 35.4 |

| ujtag | Yes               | 0                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 4,053 | 3               | 37.1 |

| ujtag | Yes               | 1                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 4,262 | 3               | 36.7 |

| ujtag | Yes               | 4                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 5,330 | 3               | 36.4 |

| None  | _                 | _                 | Yes                            | Yes                                      | ack                              | ack                           | 32             | Instantiated | 3,546 | 1               | 39.9 |

| None  | _                 | _                 | No                             | Yes                                      | 2                                | 2                             | 32             | Instantiated | 3,356 | 1               | 35.9 |

| None  | _                 | _                 | No                             | Yes                                      | 5                                | 5                             | 32             | Instantiated | 3,335 | 1               | 37.9 |

| None  | _                 | _                 | No                             | Yes                                      | ack                              | ack                           | 16             | Instantiated | 3,190 | 1               | 38.7 |

| None  | _                 | _                 | No                             | Yes                                      | ack                              | ack                           | 8              | Instantiated | 3,081 | 1               | 36.9 |

| None  | _                 | -                 | No                             | Yes                                      | ack                              | ack                           | 32             | Inferred     | 3,384 | 1               | 37.5 |

| None  | -                 | -                 | No                             | Yes                                      | ack                              | ack                           | 32             | Registers    | 7,739 | 0               | 35.9 |

| ujtag | Yes               | 4                 | Yes                            | Yes                                      | ack                              | ack                           | 32             | Registers    | 9,937 | 2               | 28.9 |

| None  | _                 | _                 | No                             | No                                       | ack                              | ack                           | 8              | Instantiated | 2,748 | 1               | 37.3 |

Table 4 • Core8051s Utilization and Performance for ProASIC3L (-1 speed grade)

|       |                   |                   |                                | Configur                                 | ation                            |                               |                |              | Utilization and<br>Performance |            |      |

|-------|-------------------|-------------------|--------------------------------|------------------------------------------|----------------------------------|-------------------------------|----------------|--------------|--------------------------------|------------|------|

| Debug | Include Trace RAM | Hardware Triggers | Include Second<br>Data Pointer | Include MUL, DIV,<br>and DA Instructions | Program Memory<br>Access Control | Data Memory<br>Access Control | APB Data Width | Internal RAM | Tiles                          | RAM Blocks | MHz  |

| None  | -                 | 1                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 2,936                          | 1          | 25.7 |

| I/Os  | No                | 0                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 3,360                          | 1          | 25.4 |

| ujtag | No                | 0                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 3,261                          | 1          | 25.1 |

| ujtag | No                | 1                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 3,624                          | 1          | 23.9 |

| ujtag | No                | 4                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 4,637                          | 1          | 24.5 |

| ujtag | Yes               | 0                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 3,541                          | 3          | 25.5 |

| ujtag | Yes               | 1                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 3,844                          | 3          | 24.4 |

| ujtag | Yes               | 4                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 4,926                          | 3          | 24.7 |

| None  | -                 | _                 | Yes                            | Yes                                      | ack                              | ack                           | 32             | Instantiated | 3,116                          | 1          | 24.2 |

| None  | -                 | _                 | No                             | Yes                                      | 2                                | 2                             | 32             | Instantiated | 2,931                          | 1          | 24.5 |

| None  | -                 | _                 | No                             | Yes                                      | 5                                | 5                             | 32             | Instantiated | 2,928                          | 1          | 26.5 |

| None  | -                 | _                 | No                             | Yes                                      | ack                              | ack                           | 16             | Instantiated | 2,778                          | 1          | 26.4 |

| None  | _                 | _                 | No                             | Yes                                      | ack                              | ack                           | 8              | Instantiated | 2,718                          | 1          | 25.5 |

| None  | _                 | _                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 2,943                          | 1          | 23.6 |

| None  | _                 | _                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 7,391                          | 0          | 25.4 |

| ujtag | Yes               | 4                 | Yes                            | Yes                                      | ack                              | ack                           | 32             | Instantiated | 9,755                          | 2          | 23.1 |

| None  | -                 | -                 | No                             | Yes                                      | ack                              | ack                           | 8              | Instantiated | 2,444                          | 1          | 24.9 |

Table 5 • Core8051s Utilization and Performance for ProASICPLUS Devices (STD speed grade)

|       |                   |                   | (                              | Configura                                | ation                            |                               |                |              |        | ization a  |      |

|-------|-------------------|-------------------|--------------------------------|------------------------------------------|----------------------------------|-------------------------------|----------------|--------------|--------|------------|------|

| Debug | Include Trace RAM | Hardware Triggers | Include Second<br>Data Pointer | Include MUL, DIV,<br>and DA Instructions | Program Memory<br>Access Control | Data Memory<br>Access Control | APB Data Width | Internal RAM | Tiles  | RAM Blocks | MHz  |

| None  | _                 | _                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 4,000  | 1          | 26.2 |

| I/Os  | No                | 0                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 4,318  | 1          | 26.4 |

| UJTAG | No                | 0                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 4,271  | 1          | 25.8 |

| UJTAG | No                | 1                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 4,709  | 1          | 25.7 |

| UJTAG | No                | 4                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 6,004  | 1          | 24.4 |

| UJTAG | Yes               | 0                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 4,580  | 4          | 26.8 |

| UJTAG | Yes               | 1                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 5,065  | 4          | 23.5 |

| UJTAG | Yes               | 4                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 6,368  | 4          | 23.5 |

| None  | -                 | _                 | Yes                            | Yes                                      | ack                              | ack                           | 32             | Instantiated | 4,344  | 1          | 26.8 |

| None  | -                 | _                 | No                             | Yes                                      | 2                                | 2                             | 32             | Instantiated | 4,185  | 1          | 27.8 |

| None  | -                 | _                 | No                             | Yes                                      | 5                                | 5                             | 32             | Instantiated | 4,135  | 1          | 29.8 |

| None  | -                 | _                 | No                             | Yes                                      | ack                              | ack                           | 16             | Instantiated | 3,821  | 1          | 28.1 |

| None  | -                 | -                 | No                             | Yes                                      | ack                              | ack                           | 8              | Instantiated | 3,773  | 1          | 28.9 |

| None  | -                 | -                 | No                             | Yes                                      | ack                              | ack                           | 32             | Inferred     | 4,056  | 1          | 26.2 |

| None  | -                 | -                 | No                             | Yes                                      | ack                              | ack                           | 32             | Registers    | 10,888 | 0          | 25.2 |

| UJTAG | Yes               | 4                 | Yes                            | Yes                                      | ack                              | ack                           | 32             | Registers    | 13,652 | 3          | 19.9 |

| None  | -                 | -                 | No                             | No                                       | ack                              | ack                           | 8              | Instantiated | 3,146  | 1          | 28.8 |

Table 6 • Core8051s Utilization and Performance for Axcelerator Devices (-2 speed grade)

|       |                   |                   |                                | Configur                                 | ation                            |                               |                |              | Utilization and Performance |            |      |

|-------|-------------------|-------------------|--------------------------------|------------------------------------------|----------------------------------|-------------------------------|----------------|--------------|-----------------------------|------------|------|

| Debug | Include Trace RAM | Hardware Triggers | Include Second<br>Data Pointer | Include MUL, DIV,<br>and DA Instructions | Program Memory<br>Access Control | Data Memory<br>Access Control | APB Data Width | Internal RAM | Tiles                       | RAM Blocks | ZHW  |

| None  | _                 | 1                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 2,111                       | 1          | 50.9 |

| I/Os  | No                | 0                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 2,343                       | 1          | 44.9 |

| I/Os  | No                | 1                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 2,608                       | 1          | 42.4 |

| I/Os  | No                | 4                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 3,197                       | 1          | 44.1 |

| I/Os  | Yes               | 0                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 2,554                       | 3          | 47.4 |

| I/Os  | Yes               | 1                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 2,797                       | 3          | 44.1 |

| I/Os  | Yes               | 4                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 3,413                       | 3          | 42.5 |

| None  | _                 | -                 | Yes                            | Yes                                      | ack                              | ack                           | 32             | Instantiated | 2,196                       | 1          | 53.4 |

| None  | _                 | -                 | No                             | Yes                                      | 2                                | 2                             | 32             | Instantiated | 2,091                       | 1          | 55.8 |

| None  | _                 | ı                 | No                             | Yes                                      | 5                                | 5                             | 32             | Instantiated | 2,104                       | 1          | 54.2 |

| None  | _                 | -                 | No                             | Yes                                      | ack                              | ack                           | 16             | Instantiated | 2,066                       | 1          | 53.3 |

| None  | _                 | -                 | No                             | Yes                                      | ack                              | ack                           | 8              | Instantiated | 1,977                       | 1          | 56.3 |

| None  | _                 | 1                 | No                             | Yes                                      | ack                              | ack                           | 32             | Inferred     | 2,104                       | 1          | 50.1 |

| None  | _                 | -                 | No                             | Yes                                      | ack                              | ack                           | 32             | Registers    | 5,245                       | 0          | 42.9 |

| I/Os  | Yes               | 4                 | Yes                            | Yes                                      | ack                              | ack                           | 32             | Registers    | 6,714                       | 2          | 33.1 |

| None  | -                 | -                 | No                             | No                                       | ack                              | ack                           | 8              | Instantiated | 1,757                       | 1          | 53.4 |

Table 7 • Core8051s Utilization and Performance for RTAX-S Devices (-1 speed grade)

|       |                   |                   |                                | Configu                                  | ration                           |                               |                |              |       | zation<br>forma |      |

|-------|-------------------|-------------------|--------------------------------|------------------------------------------|----------------------------------|-------------------------------|----------------|--------------|-------|-----------------|------|

| Debug | Include Trace RAM | Hardware Triggers | Include Second<br>Data Pointer | Include MUL, DIV,<br>and DA Instructions | Program Memory<br>Access Control | Data Memory<br>Access Control | APB Data Width | Internal RAM | Tiles | RAM Blocks      | MHz  |

| None  | _                 | ı                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 2,123 | 1               | 39.9 |

| I/Os  | No                | 0                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 2,357 | 1               | 33.1 |

| I/Os  | No                | 1                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 2,607 | 1               | 30.1 |

| I/Os  | No                | 4                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 3,137 | 1               | 28.6 |

| I/Os  | Yes               | 0                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 2,547 | 3               | 29.9 |

| I/Os  | Yes               | 1                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 2,836 | 3               | 33.6 |

| I/Os  | Yes               | 4                 | No                             | Yes                                      | ack                              | ack                           | 32             | Instantiated | 3,351 | 3               | 26.5 |

| None  | _                 | _                 | Yes                            | Yes                                      | ack                              | ack                           | 32             | Instantiated | 2,192 | 1               | 39.7 |

| None  | _                 | _                 | No                             | Yes                                      | 2                                | 2                             | 32             | Instantiated | 2,057 | 1               | 37.8 |

| None  | _                 | -                 | No                             | Yes                                      | 5                                | 5                             | 32             | Instantiated | 2,118 | 1               | 38.4 |

| None  | _                 | _                 | No                             | Yes                                      | ack                              | ack                           | 16             | Instantiated | 2,042 | 1               | 39.6 |

| None  | _                 | _                 | No                             | Yes                                      | ack                              | ack                           | 8              | Instantiated | 1,987 | 1               | 39.4 |

| None  | _                 | _                 | No                             | Yes                                      | ack                              | ack                           | 32             | Inferred     | 2,146 | 1               | 38.7 |

| None  | _                 | _                 | No                             | Yes                                      | ack                              | ack                           | 32             | Registers    | 5,224 | 0               | 29.2 |

| I/Os  | Yes               | 4                 | Yes                            | Yes                                      | ack                              | ack                           | 32             | Registers    | 6,694 | 2               | 22.8 |

| None  | _                 | _                 | No                             | No                                       | ack                              | ack                           | 8              | Instantiated | 1,778 | 1               | 39.8 |

## 1 - Core8051s Overview

The Core8051s is a high-performance, eight-bit microcontroller IP Core. It is a fully functional eight-bit embedded controller that executes all ASM51 instructions and has the same instruction set as the 80C31. Core8051s provides software and hardware interrupts.

The Core8051s architecture eliminates redundant bus states and implements parallel execution of fetch and execution phases. Since a cycle is aligned with memory fetch when possible, most of the one-byte instructions are performed in a single cycle. Core8051s uses one clock per cycle. This leads to an average performance improvement rate of 8.0 (in terms of MIPS) with respect to the Intel device working with the same clock frequency.

The original Intel 8051 had a 12-clock architecture. A machine cycle needed 12 clocks, and most instructions were either one or two machine cycles. Therefore, the 8051 used either 12 or 24 clocks for each instruction, except for the MUL and DIV instructions. Furthermore, each cycle in the 8051 used two memory fetches. In many cases, the second fetch was a "dummy" fetch and extra clocks were wasted.

Table 1-1 shows the speed advantage of Core8051s over the standard Intel 8051. A speed advantage of 12 in the first column means that Core8051s performs the same instruction 12 times faster than the standard Intel 8051. The second column in Table 1-1 lists the number of types of instructions that have the given speed advantage. The third column lists the total number of instructions that have the given speed advantage. The third column can be thought of as a subcategory of the second column. For example, there are two types of instructions that have a three-time speed advantage over the classic 8051, for which there are nine explicit instructions.

Table 1-1 • Core8051s Speed Advantage Summary

| Speed Advantage | Number of Instruction Types | Number of Instructions (Opcodes) |

|-----------------|-----------------------------|----------------------------------|

| 24              | 1                           | 1                                |

| 12              | 27                          | 83                               |

| 9.6             | 2                           | 2                                |

| 8               | 16                          | 38                               |

| 6               | 44                          | 89                               |

| 4.8             | 1                           | 2                                |

| 4               | 18                          | 31                               |

| 3               | 2                           | 9                                |

Average: 8.0 Sum: 111 Sum: 255

# 2 - Supported Interfaces

## **Ports**

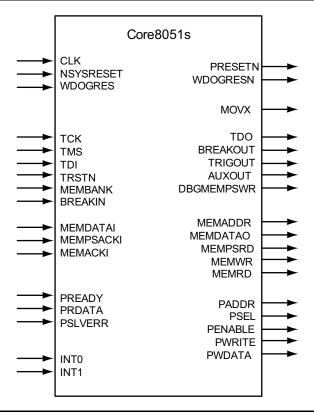

The port signals of Core8051s are illustrated in Figure 2-1.

Figure 2-1 • Core8051s I/O Signals

The signals listed in Table 2-1 are present at the Core8051s boundary.

Table 2-1 • Core8051s Ports

| Signal Name | Туре   | Polarity/Bus<br>Size | Description                                                                                                                                                                                                                                           |

|-------------|--------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             |        |                      | System Signals                                                                                                                                                                                                                                        |

| CLK         | Input  | Rise                 | Clock input for internal logic. This signal must also be used to clock any APB peripherals, if present.                                                                                                                                               |

| NSYSRESET   | Input  | Low                  | Hardware reset input. A logic zero on this signal for two clock cycles while the oscillator is running resets the device.                                                                                                                             |

| PRESETN     | Output | Low                  | Synchronized reset output. This signal should be used to reset any APB peripherals, if present.                                                                                                                                                       |

| WDOGRES     | Input  | High                 | Watchdog timeout indication                                                                                                                                                                                                                           |

| WDOGRESN    | Output | Low                  | Reset signal for watchdog                                                                                                                                                                                                                             |

| MOVX        | Output | High                 | MOVX instruction executing                                                                                                                                                                                                                            |

|             |        | On-C                 | hip Debug Interface (Optional)                                                                                                                                                                                                                        |

| TCK         | Input  | Rise                 | JTAG test clock. If OCI is not used, connect to logic 1.                                                                                                                                                                                              |

| TMS         | Input  | High                 | JTAG test mode select. If OCI is not used, connect to logic 0.                                                                                                                                                                                        |

| TDI         | Input  | High                 | JTAG test data in. If OCI is not used, connect to logic 0.                                                                                                                                                                                            |

| TDO         | Output | High                 | JTAG test data out                                                                                                                                                                                                                                    |

| TRSTN       | Input  | Low                  | JTAG test reset. If OCI is not used, connect to logic 1.                                                                                                                                                                                              |

| MEMBANK     | Input  | 4                    | Optional code memory bank selection. If not used, connect to logic 0.                                                                                                                                                                                 |

| BREAKIN     | Input  | High                 | Break bus input. When sampled high, a breakpoint is generated. If not used, connect to logic 0.                                                                                                                                                       |

| BREAKOUT    | Output | High                 | Break bus output. This is driven high when Core8051s stops emulation. This can be connected to an open-drain break bus that connects to multiple processors, so that when any CPU stops, all others on the bus are stopped within a few clock cycles. |

| TRIGOUT     | Output | High                 | Trigger output. This signal can be optionally connected to external test equipment to cross-trigger with internal Core8051s activity.                                                                                                                 |

| AUXOUT      | Output | High                 | Auxiliary output. This signal is an optional general purpose output that can be controlled via the OCI debugger software.                                                                                                                             |

| DBGMEMPSWR  | Output | High                 | Debug program store write.                                                                                                                                                                                                                            |

|             |        |                      | External Interrupts                                                                                                                                                                                                                                   |

| INT0        | Input  | High                 | External Interrupt 0 (low priority)                                                                                                                                                                                                                   |

| INT1        | Input  | High                 | External Interrupt 1 (high priority)                                                                                                                                                                                                                  |

|             |        | Ex                   | ternal Memory Bus Interface                                                                                                                                                                                                                           |

| MEMPSACKI   | Input  | High                 | Program memory read acknowledge                                                                                                                                                                                                                       |

| MEMACKI     | Input  | High                 | Data memory acknowledge                                                                                                                                                                                                                               |

| MEMDATAI    | Input  | 8                    | Memory data input                                                                                                                                                                                                                                     |

| MEMDATAO    | Output | 8                    | Memory data output                                                                                                                                                                                                                                    |

| MEMADDR     | Output | 16                   | Memory address                                                                                                                                                                                                                                        |

## Table 2-1 • Core8051s Ports (continued)

| Signal Name | Туре   | Polarity/Bus<br>Size | Description                                                                                                                                                                                                            |

|-------------|--------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MEMPSRD     | Output | High                 | Program store read enable                                                                                                                                                                                              |

| MEMWR       | Output | High                 | Data memory write enable                                                                                                                                                                                               |

| MEMRD       | Output | High                 | Data memory read enable                                                                                                                                                                                                |

|             | -      |                      | APB3 Interface                                                                                                                                                                                                         |

| PADDR       | Output | 12                   | This is the APB address bus.                                                                                                                                                                                           |

| PSEL        | Output | 1                    | This signal indicates that the slave device is selected and a data transfer is required.                                                                                                                               |

| PENABLE     | Output | High                 | This strobe signal is used to time all accesses on the peripheral bus. The enable signal is used to indicate the second cycle of an APB transfer. The rising edge of PENABLE occurs in the middle of the APB transfer. |

| PWRITE      | Output | High                 | When high, this signal indicates an APB write access. When low, it indicates an APB read access.                                                                                                                       |

| PRDATA      | Input  | 8, 16, or 32         | The read data bus is driven by the selected slave during read cycles (when PWRITE is low). The width of this bus matches the width of the widest peripheral in the system.                                             |

| PWDATA      | Output | 8, 16, or 32         | The write data bus is driven by the Core8051s during write cycles (when PWRITE is high). The width of this bus matches the width of the widest peripheral in the system.                                               |

| PREADY      | Input  | 1                    | This signal is the ready signal for the APB interface. This signal conforms to APB version 3.0. Using this signal, APB slave peripherals can stall reads or writes, if not ready to complete the transaction.          |

| PSLVERR     | Input  | 1                    | This signal is specified in v3.0 of the APB specification. It is currently unused in Core8051s.                                                                                                                        |

## **Interface Descriptions**

## **Parameters/Generics**

The Verilog parameters or VHDL generics shown in Table 2-2 are present in the Core8051s RTL code. These may be modified by the user to configure Core8051s as required. When working with SmartDesign, these parameters/generics are set to appropriate values using the Core8051s configuration window.

Table 2-2 • Table x. Core8051s Parameters/Generics

| Parameter/Generic     | Default<br>Value | Description                                                                                                                                                                                                                  |

|-----------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DEBUG                 | 0                | 0 = On-chip instrumentation (OCI) debug logic not included.                                                                                                                                                                  |

|                       |                  | 1 = OCI debug logic included; general purpose FPGA I/Os used for debug connection                                                                                                                                            |

|                       |                  | 2 = OCI debug logic included, dedicated JTAG pins of device (along with UJTAG macro) used for debug connection                                                                                                               |

| INCL_TRACE            | 0                | 0 = Trace RAM not included                                                                                                                                                                                                   |

|                       |                  | 1 = Trace RAM included                                                                                                                                                                                                       |

| TRIG_NUM              | 0                | Number of hardware triggers. Possible settings are 0, 1, 2, or 4.                                                                                                                                                            |

| INCL_DPTR1            | 0                | 0 = Second data pointer not included.                                                                                                                                                                                        |

|                       |                  | 1 = Second data pointer included.                                                                                                                                                                                            |

| INCL_MUL_DIV          | 1                | 0 = MUL, DIV, and DA instructions not included.                                                                                                                                                                              |

|                       |                  | 1 = MUL, DIV, and DA instructions included.                                                                                                                                                                                  |

| VARIABLE_WAIT         | 1                | 0 = Program store memory related acknowledge input (MEMPSACKI) not used for controlling accesses to program memory. A fixed number of wait states (defined by WAIT_VAL parameter) is used for each access to program memory. |

| WAIT_VAL              | 0                | This setting is only used when VARIABLE_WAIT = 0 and defines the (fixed) number of wait states inserted in each access to program memory. Possible values are 0 to 7.                                                        |

| VARIABLE_STRETCH      | 1                | 0 = Data memory related acknowledge input (MEMACKI) not used for controlling accesses to program memory. A fixed number of wait states (defined by WAIT_VAL parameter) is used for each access to program memory.            |

|                       |                  | 1 = Data memory related acknowledge input (MEMACKI) is used for controlling accesses to program memory.                                                                                                                      |

| STRETCH_VAL           | 1                | This setting is only used when VARIABLE_STRETCH = 0 and defines the (fixed) number of wait states inserted in each access to data memory. Possible values are 0 to 7.                                                        |

| APB_DWIDTH            | 32               | Data width in number of bits for APB bus. Possible settings are 8, 16, or 32.                                                                                                                                                |

| INTRAM_IMPLEMENTATION | 0                | This parameter is used to control how the internal (256x8) RAM is implemented. Possible settings are:                                                                                                                        |

|                       |                  | 0 = Instantiate RAM block                                                                                                                                                                                                    |

|                       |                  | 1 = Infer RAM block during synthesis                                                                                                                                                                                         |

|                       |                  | 2 = Infer registers for RAM during synthesis                                                                                                                                                                                 |

## 3 - Tool Flows

## **SmartDesign**

Core8051s is available for download to the SmartDesign IP Catalog via the Libero® Integrated Design Environment (IDE) web repository. For information on using SmartDesign to instantiate, configure, connect, and generate cores, refer to the Libero IDE online help.

The advanced peripheral bus (APB) version 3 interface of Core8051s will typically be connected to the mirrored master interface of CoreAPB3, with various APB or APB3 slaves connected to the slave interfaces of CoreAPB3. The external memory interface (ExternalMemIf) of Core8051s must be connected to program and data memories, which can be implemented either on-chip or off-chip. If debug functionality is enabled, the JTAG signals (TCK, TMS, TDI, TDO, and TRSTN) of the debug interface (DebugIf) must be routed to the top level of your design. Either the dedicated JTAG pins of the device or general purpose I/O pins can be used for the JTAG debug connection. The UJTAG macro is employed when the dedicated JTAG pins are used for the debug connection.

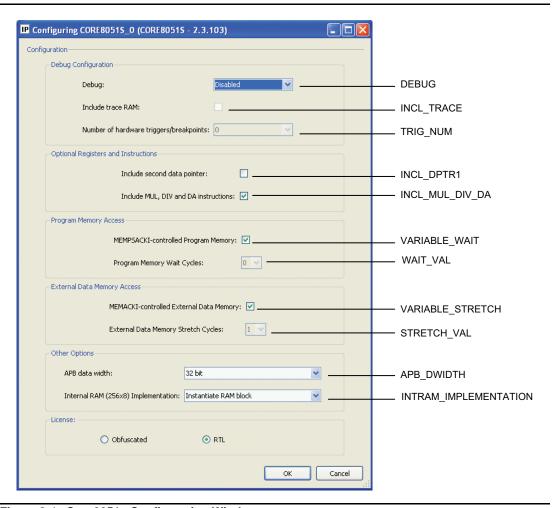

Figure 3-1 shows the Core8051s configuration window, along with cross-references to the corresponding top-level parameters. The parameters/generics of the core are fully described in the "Parameters/Generics" section on page 20.

Figure 3-1 • Core8051s Configuration Window

The configuration options for Core8051s are described in the following paragraphs. The Core8051s configuration window is used to adjust the values of the underlying parameters/generics in the RTL code for the core. Each configuration option presented in the configuration window corresponds directly to an actual parameter/generic in the RTL code for Core8051s.

## **Debug Configuration**

- There are three debug-related configuration options. Set the Debug option to choose to enable or disable on-chip instrumentation (OCI) debug functionality and to control how any debug connection is implemented. When this functionality is enabled, you can connect a debugger to the processor via a JTAG connection. You can disable the debug functionality if you do not intend to use a debugger and want to minimize the number of tiles consumed by the processor. There are two possibilities for implementing the JTAG connection. From the Debug drop-down menu, choose one of these options:

- Disabled to exclude debug functionality

- Enabled using UJTAG to include debug functionality and to use the dedicated JTAG pins of the

device (via the UJTAG macro) for the debug connection. This setting is mostly used when only

one debug connection is required. With this setting you can make use of the FlashPro3 or lowcost programming stick (LCPS) connection for the debug connection.

- Enabled using I/Os to include debug functionality and to use general purpose I/O pins for the

debug connection. Select this option if the UJTAG macro is either not present on your device or is

already in use and not available for the Core8051s debug connection.

- When Debug is set to Enabled using UJTAG or Enabled using I/Os, two additional debug options are available for added control over the debug functionality to be included:

- Select Include trace RAM to include a 256-byte deep trace RAM within Core8051s. No trace RAM is present if this option is not selected. Including the trace RAM increases the tile count for the processor and consumes RAM blocks on the device.

- Set Number of hardware triggers/breakpoints to 0, 1, 2, or 4 to set the maximum number of hardware triggers/breakpoints available when debugging a Core8051s system. Increasing the number of hardware triggers/breakpoints increases the tile count of the processor.

## **Optional Registers and Instructions**

Select **Include second data pointer** to include a second data pointer. When this option is selected, two additional special function registers (SFRs) are included to implement the second (16-bit) data pointer.

Select **Include MUL, DIV, and DA instructions** to include the multiply, divide, and decimal adjust instructions. If the software to be run on the processor does not make use of the MUL, DIV, and DA instructions, this option check box can be cleared to reduce the tile count of the core. The behavior of the processor is undefined when attempting to execute a MUL, DIV or DA instruction while the processor is not configured to include support for these instructions.

## **Program Memory Access**

There are two possible methods for controlling accesses by the processor to program memory:

- Select MEMPSACKI-controlled Program Memory when the MEMPSACKI (program store

memory acknowledge input) signal is used to control accesses to program memory. When this

option is selected, the program memory or memory subsystem must assert MEMPSACKI when a

write to program memory has completed and when valid read data is available.

- Clear the check box for MEMPSACKI-controlled Program Memory and set a fixed number of wait cycles for each access to program memory by adjusting the Program Memory Wait Cycles option.

Note: Program Memory Wait Cycles is only enabled when **MEMPSACKI-controlled Program Memory** is not selected.

**External Data Memory Access**

There are two possible methods for controlling accesses by the processor to external data memory.

- Select MEMACKI-controlled External Data Memory when the MEMACKI (data memory acknowledge input) signal is used to control accesses to data memory. When this option is selected, the data memory or memory subsystem must assert MEMACKI when a write to data memory has completed and when valid read data is available.

- Clear the check box for MEMACKI-controlled External Data Memory and set a fixed number of

wait cycles for each access to data memory by adjusting the External Data Memory Stretch

Cycles option.

Note: Note that the External Data Memory Stretch Cycles is only enabled when MEMACKI-controlled External Data Memory is not selected.

The external data memory is external to the processor but can be implemented using either on-chip or off-chip memory resources.

## **Other Options**

Set APB data width to **8 bit**, **16 bit**, or **32 bit** to select the appropriate data width for the APB interface of the processor. When the APB data width is 16 bits or 32 bits, extra SFRs are used to store the upper bytes of APB data when the (8-bit) processor core carries out an access to APB space. See the "External Data Memory Space" section on page 30 for more information on the APB interface.

The Internal RAM (256x8) Implementation option is used to control how the internal 256x8 RAM is implemented. Three choices are available:

- Instantiate RAM block: A RAM macro block is directly instantiated in the RTL code.

- Infer RAM block during synthesis: A synthesis directive (in the form of a structured comment) is used in the RTL code to cause the synthesis tool to infer RAM during synthesis. A RAM macro block will be used in this case, which means that this choice gives a very similar outcome to Instantiate RAM block.

- Infer registers for RAM during synthesis: A synthesis directive (in the form of a structured comment) is used in the RTL code to cause the synthesis tool to use registers (FPGA tiles) to implement the 256x8 internal RAM. This considerably increases the tile count for the core but has the benefit of enhancing the fault-tolerant capabilities of Core8051s.

## **Example System**

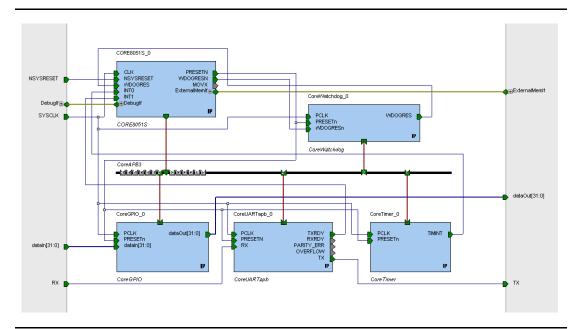

A typical system that includes Core8051s is shown in Figure 3-2. Connections can be made automatically in SmartDesign using the Auto Connect menu option.

Figure 3-2 • Example System Including Core8051s

## **Simulation**

Core8051s comes with a verification testbench and also supports bus functional model (BFM)-based simulation of a system in which it is instantiated. The BFM only simulates transactions on the APB interface of Core8051s and does implement a complete model of the processor. It is not possible to simulate code running on the processor with a BFM-based simulation.

Core8051s simulation can be invoked from the Libero IDE Project Manager. After the design has been generated, click the **Simulation** button in the Libero IDE to run a simulation.

The Core8051s component must be set as the design root (right-click Core8051s and select **Set As Root**), before running a Core8051s simulation. However, if intending to run a BFM-based simulation, you must first compile the component which instantiates Core8051s. To do this, set the design root one level of hierarchy above the Core8051s component and click the **Simulation** button to invoke ModelSim® and compilation of the relevant components. When the (automatically generated) ModelSim script finishes, exit ModelSim. Now set the design root to the Core8051s component and click the **Simulation** button again. This enables you to run a BFM-based simulation of your Core8051s system. The Core8051s verification testbench can be run directly, without the need to first compile the component that instantiates Core8051s.

The following message will appear in the ModelSim transcript window when running (pre-synthesis) Core8051s simulation:

```

The following (pre-synthesis) simulation options are available for your Core8051s-based system:

bfm - APB Bus Functional Model (BFM-driven) simulation of your system oci - Run Core8051s On Chip Instrumentation (OCI) tests

opcode - Run Core8051s opcode test suite, consisting of 256 opcode tests

<num> - Enter a number in the range 1 to 256 to run a specific opcode test

Enter "bfm", "oci", "opcode" or a number between 1 and 256 and hit return key to select simulation type

```

Follow the instructions in the ModelSim transcript window to choose the type of simulation to run. BFM-based simulation is not supported after synthesis has been run and *bfm* does not appear as a simulation option in the post-synthesis ModelSim message, which is shown below:

```

The following (post-synthesis) simulation options are available for your Core8051s-based system:

oci - Run Core8051s On Chip Instrumentation (OCI) tests

opcode - Run Core8051s opcode test suite, consisting of 256 opcode tests

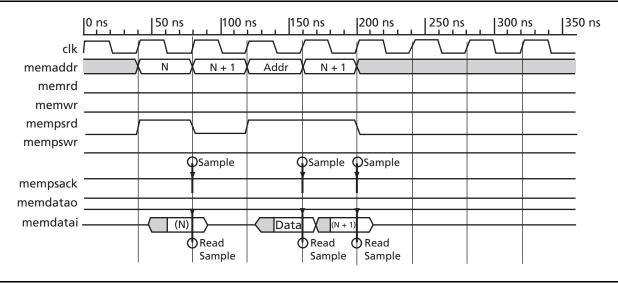

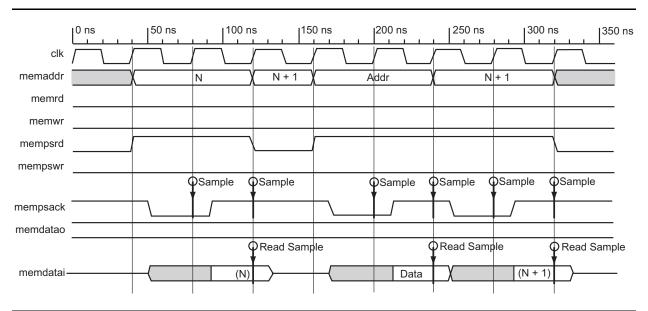

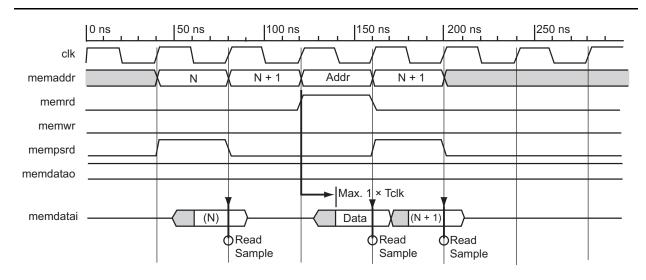

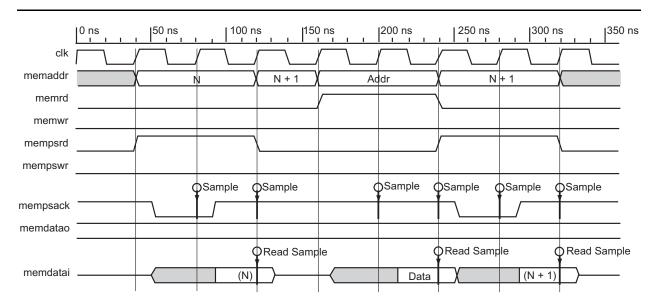

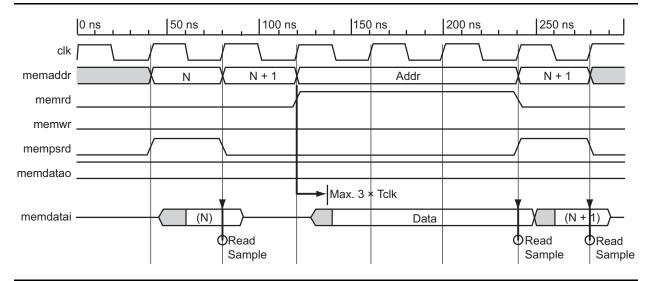

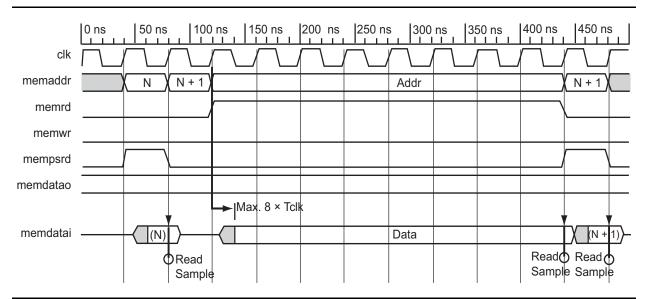

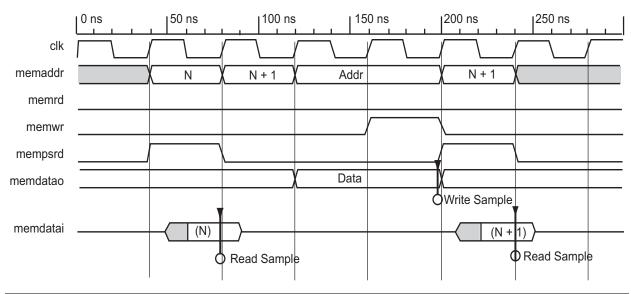

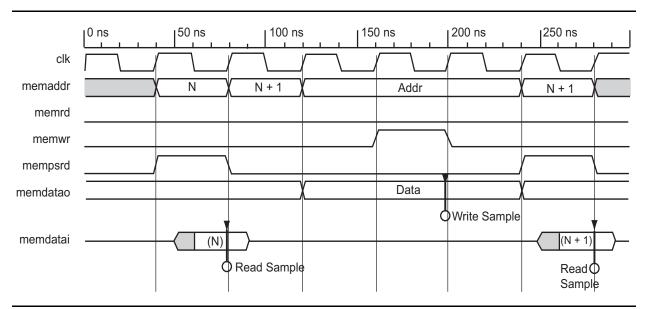

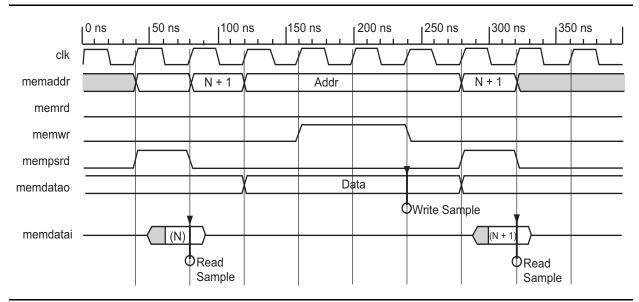

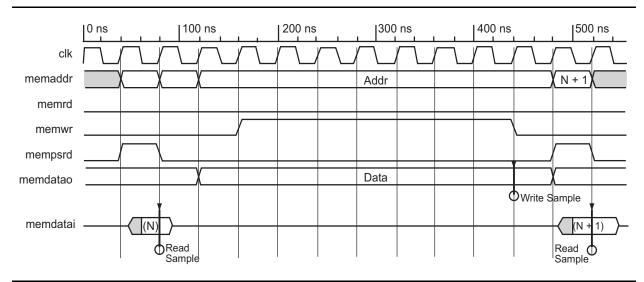

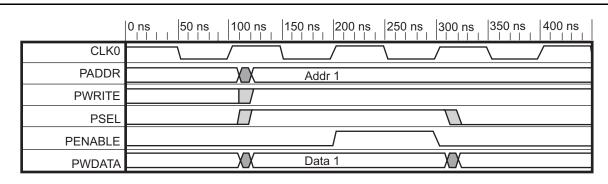

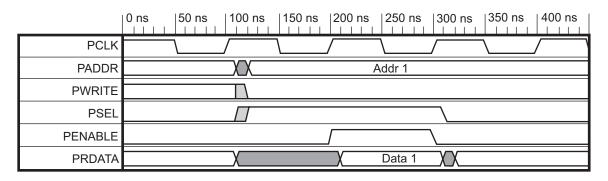

<num> - Enter a number in the range 1 to 256 to run a specific opcode test