# 128K x 8 SRAM WITH LATCHED/ BUFFERED ADDRESS LINES, REGISTERED DATA<sub>IN</sub> LINES AND LATCHED/BUFFERED DATA<sub>OUT</sub> LINES

**IDT7M822**

### **FEATURES:**

- Latched and buffered address lines

- Registered input data lines

- Latched and buffered output data lines

- Separate I/O

- · High-speed access time:

- Military temperature range: 55ns (max.)

- Commercial temperature range: 45ns (max.)

- 20MHz read/write cycle time

#### DESCRIPTION:

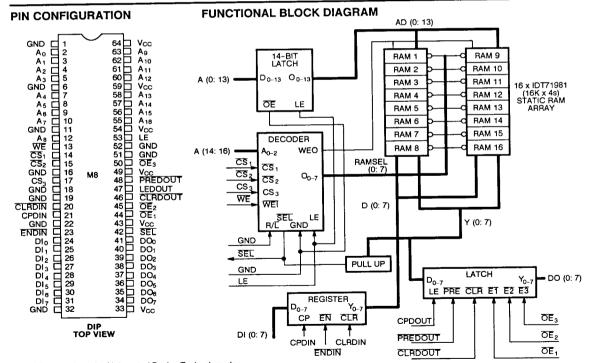

The IDT7M822 is a 128K x 8 RAM with latched address, registered DATA<sub>IN</sub> and latched DATA<sub>OUT</sub> lines. The address and DATA<sub>IN</sub> latches have independent latch enables (LE) allowing the latch to be used as a buffer by connecting its Latch Enable LE to

Address, Write Enable ( $\overline{\text{WE}}$ ) and the three Chip Select ( $\overline{\text{CS}}$ ) lines are controlled by LE. When LE is high, the address latches and decoder are transparent or in the buffer mode. All address,

$\overline{\text{CS}}$  and  $\overline{\text{WE}}$  data that meets the specified set-up time will be latched when LE goes low.

DATA<sub>IN</sub> is controlled by its own clock, CPDIN. When ENDIN (clock enable) is asserted, all DATA<sub>IN</sub> data that meets the specified set-up time requirements will be registered on the rising edge of CPDIN. CLRDIN is an asynchronous control that can be used to clear the DATA<sub>IN</sub> register.

DATAour is controlled by its own enable, LEDOUT. With this line in the high state, the latch is in the transparent or buffer mode. Data out of the RAM array that meets the set-up time requirements will be latched when LEDOUT goes low. PREDOUT and CLRDOUT are asynchronous controls that can be used to preset or clear the DATAour latch. The preset function overrides the clear so that, with both asserted, the latch will be preset. There are three active low output enables for DATAour. Unless all three of these lines are asserted, the output will be in the high impedance state.

The SEL signal is an output that can be used to monitor the state of the internal RAM array output bus.

13-178

CEMOS is a trademark of Integrated Device Technology, Inc.

MILITARY AND COMMERCIAL TEMPERATURE RANGES

**DECEMBER 1987**

© 1987 Integrated Device Technology, Inc.

DSC-7000/-

### **AC TEST CONDITIONS**

| Input Pulse Levels            | GND to 3.0V         |  |  |  |  |  |

|-------------------------------|---------------------|--|--|--|--|--|

| Input Rise/Fall Times         | 10ns                |  |  |  |  |  |

| Input Timing Reference Levels | 1.5V                |  |  |  |  |  |

| Output Reference Levels       | 1.5V                |  |  |  |  |  |

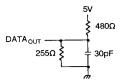

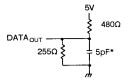

| Output Load                   | See Figures 1 and 2 |  |  |  |  |  |

| Output Load                   | +++                 |  |  |  |  |  |

Figure 1. Output Load

Figure 2. Output Load (for t<sub>OHZ</sub>)

## AC ELECTRICAL CHARACTERISTICS (V<sub>CC</sub> = 5V±10%, T<sub>A</sub> = 0°C to +70°C and -55°C to +125°C)

| SYMBOL                | PARAMETER                                                  | IDT7M822S45     |      | IDT7M822S55 |      | IDT7M822S70 |      | דומט |

|-----------------------|------------------------------------------------------------|-----------------|------|-------------|------|-------------|------|------|

|                       |                                                            | (COM'L.<br>M!N. | MAX. | MIN.        | MAX. | MIN.        | MAX. | JAIT |

| READ C                | YCLE <sup>(1)</sup>                                        |                 |      |             |      |             |      |      |

| tAA                   | Address, CS Access Time                                    | _               | 45   |             | 55   |             | 70   | ns   |

| t <sub>ADS</sub>      | Address, CS to LE Set-up Time                              | 2               | _    | 2           |      | 2           |      | ns   |

| t <sub>ADH</sub>      | Address, CS from LE Hold Time                              | 2               | _    | 2           | _    | 3           | _    | ns   |

| t <sub>LEDO</sub> (2) | DATA <sub>OUT</sub> Latch from Address, CS                 | _               | 36   | _           | 40   | _           | 55   | ns   |

| toE                   | OE to Data Valid                                           | _               | 8    | _           | 9    | 1           | 15   | ns   |

| t <sub>OHZ</sub> (3)  | OE to High Z                                               | _               | 7    | 1           | 9    |             | 15   | ns   |

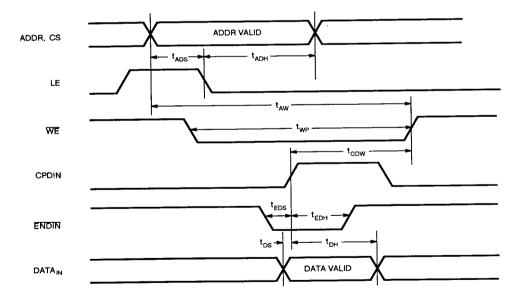

| WRITE                 | CYCLE                                                      |                 |      |             |      |             |      |      |

| t <sub>AW</sub>       | Address, CS to End of Write                                | 31              |      | 45          | _    | 55          |      | ns   |

| t <sub>WP</sub>       | Write Pulse Width                                          | 27              | _    | 35          | -    | 45          | -    | ns   |

| t <sub>ADS</sub>      | Address, CS to LE Set-up Time                              | 2               |      | 2           | _    | 2           | -    | ns   |

| t <sub>ADH</sub>      | Address, CS from LE Hold Time                              | 2               | _    | 2           | _    | 3           |      | ns   |

| t <sub>EDS</sub>      | DATA <sub>IN</sub> Clock Enable to Clock Set-up Time       | 3               |      | 3           |      | 3           |      | ns   |

| t <sub>EDH</sub>      | DATA <sub>IN</sub> Clock Enable from Clock Hold Time       | 0               |      | 0           |      | 2           |      | ns   |

| t <sub>DS</sub>       | DATA <sub>IN</sub> to DATA <sub>IN</sub> Clock Set-up Time | 3               |      | 3           |      | 5           |      | ns   |

| t <sub>DH</sub>       | DATA <sub>IN</sub> from DATA <sub>IN</sub> Clock Hold Time | 2               |      | 2           | -    | 3           |      | ns   |

| t <sub>CDW</sub>      | DATA <sub>IN</sub> Clock to End of Write Cycle             | 27              | -    | 31          | _    | 40          |      | ns   |

#### NOTES:

- 1. WE Must be high for read cycles.

- 2. Latch Enable signal arriving after this maximum will delay overall access time ( $t_{AA}$ ).

- 3. Transition is measured -200mV from steady state voltage with specified loading in Figure 2.

13

<sup>\*</sup> Including scope and jig.

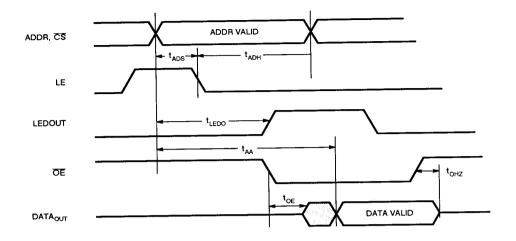

## TIMING WAVEFORM OF READ CYCLE

# TIMING WAVEFORM OF WRITE CYCLE