# 16-bit Proprietary Microcontroller

**CMOS**

# F2MC-16LX MB90480/485 Series

## MB90F481/F482/487B/488B/483C MB90F488B/F489B/V480/V485B

#### ■ DESCRIPTION

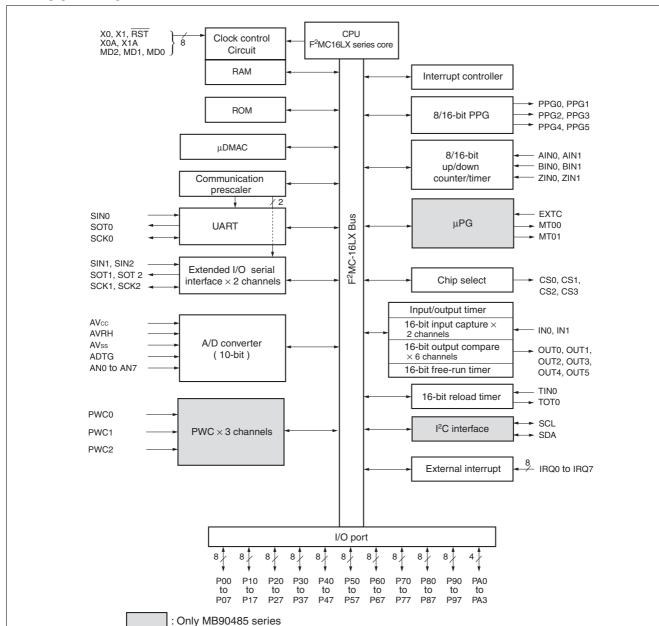

The MB90480/485 series is a 16-bit general-purpose FUJITSU microcontroller designed for process control in consumer devices and other applications requiring high-speed real-time processing.

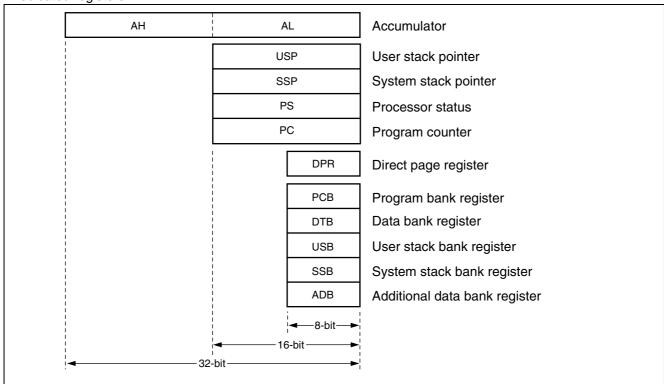

The F<sup>2</sup>MC-16LX CPU core instruction set retains the AT architecture of the F<sup>2</sup>MC\*<sup>1</sup> family, with additional instructions for high-level languages, expanded addressing mode, enhanced multiply-drive instructions, and complete bit processing. In addition, a 32-bit accumulator is provided to enable long-word processing.

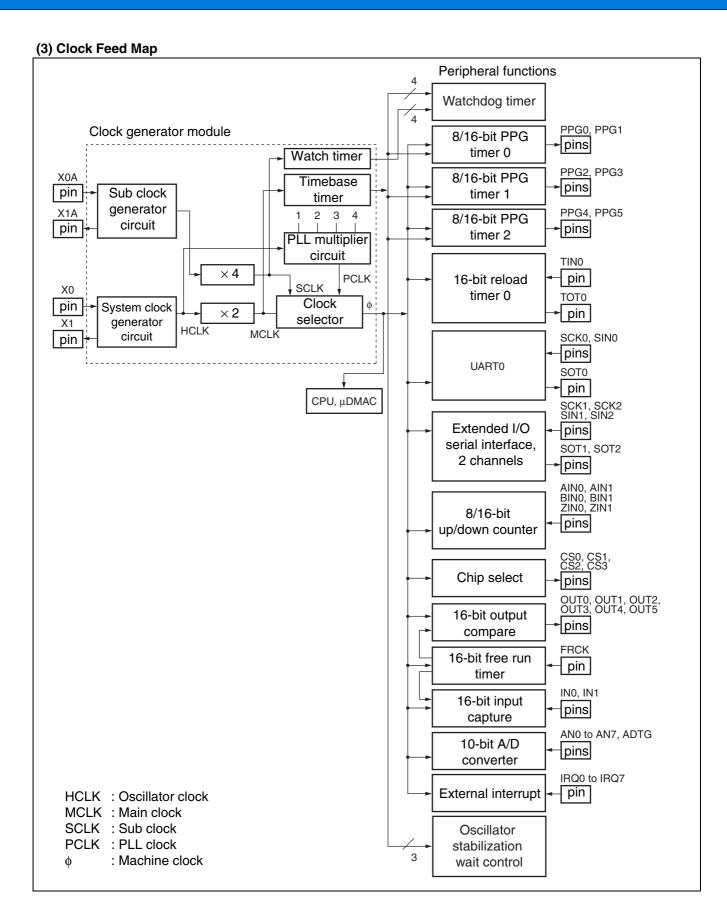

The MB90480/485 series features embedded peripheral resources including 8/16-bit PPG, expanded I/O serial interface, UART, 10-bit A/D converter, 16-bit I/O timer, 8/16-bit up/down-counter, PWC timer, I<sup>2</sup>C\*<sup>2</sup> interface, DTP/ external interrupt, chip select, and 16-bit reload timer.

- \*1: F2MC is the abbreviation for FUJITSU Flexible Microcontroller.

- \*2 : Purchase of Fujitsu I<sup>2</sup>C components conveys a license under the Philips I<sup>2</sup>C Patent Rights to use, these components in an I<sup>2</sup>C system provided that the system conforms to the I<sup>2</sup>C standard a Specification as defined by Philips.

### **■ FEATURES**

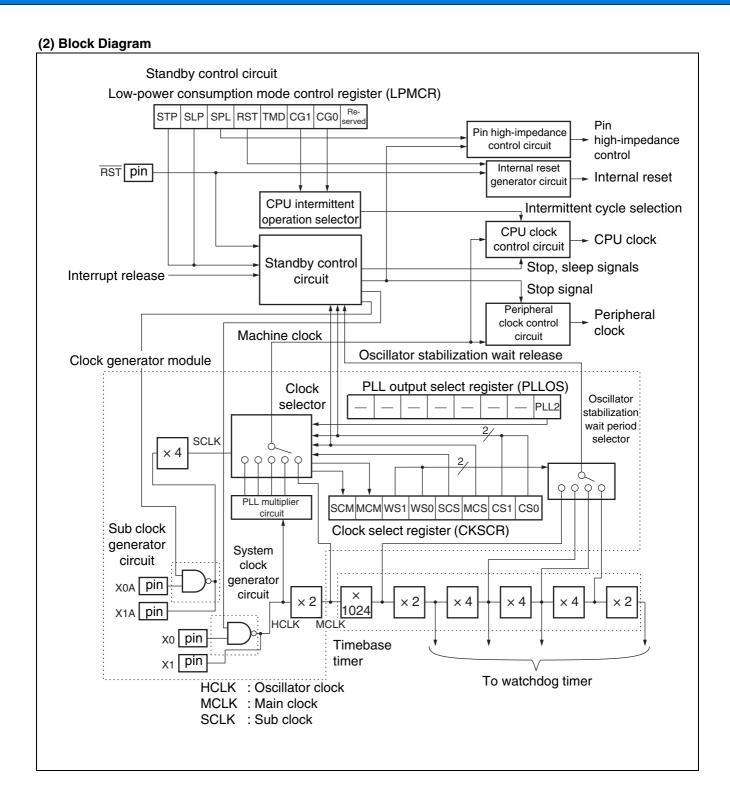

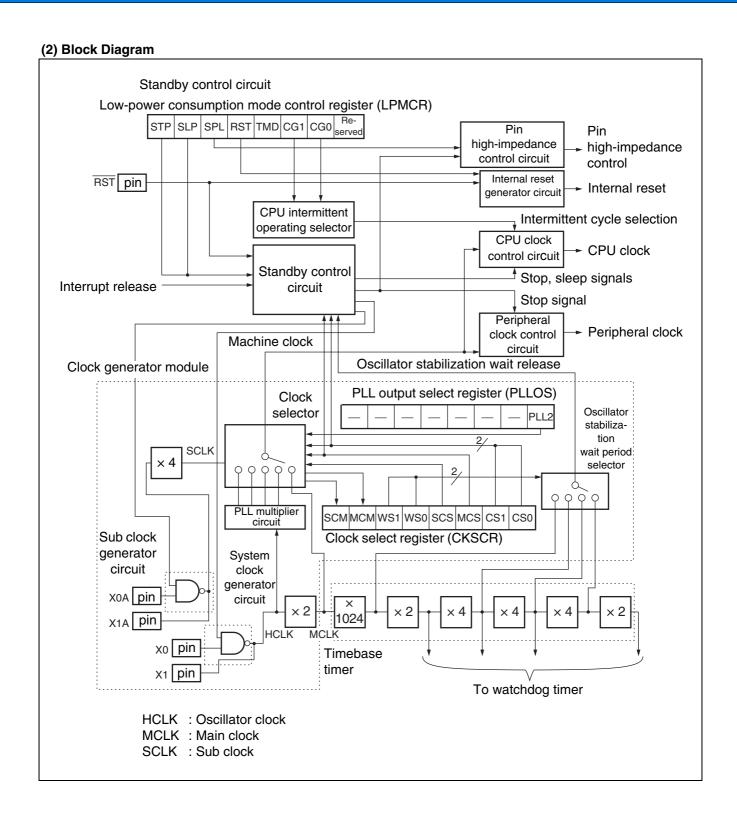

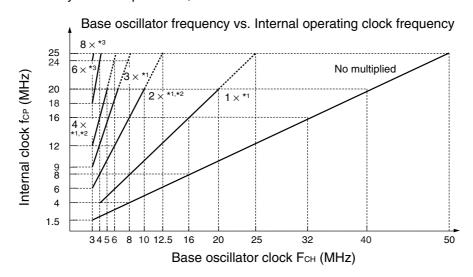

Clock

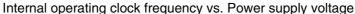

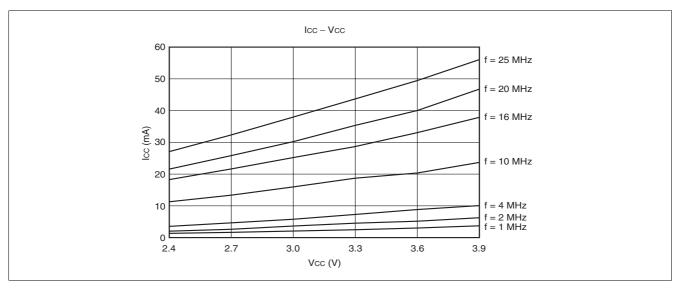

Minimum instruction execution time: 40.0 ns/6.25 MHz base frequency multiplied  $\times 4$  (25 MHz internal operating frequency/3.3 V  $\pm$  0.3 V)

62.5 ns/4 MHz base frequency multiplied  $\times$  4 (16 MHz internal operating frequency/3.0 V  $\pm$  0.3 V) PLL clock multiplier

Maximum memory space: 16 Mbytes

(Continued)

Be sure to refer to the "Check Sheet" for the latest cautions on development.

"Check Sheet" is seen at the following support page

URL: http://www.fujitsu.com/global/services/microelectronics/product/micom/support/index.html

"Check Sheet" lists the minimal requirement items to be checked to prevent problems beforehand in system development.

#### (Continued)

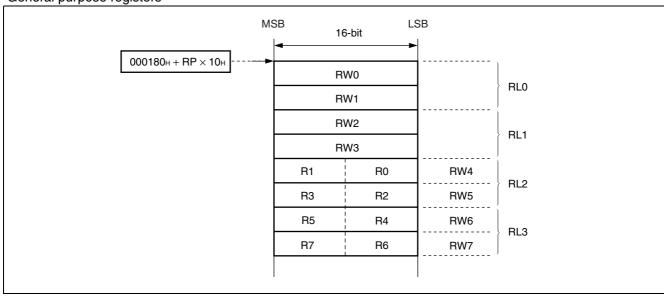

· Instruction set optimized for controller applications

Supported data types (bit, byte, word, or long word)

Typical addressing modes (23 types)

32-bit accumulator for enhanced high-precision calculation

Enhanced signed multiplication/division instruction and RETI instruction functions

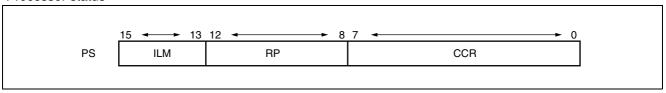

• Instruction set designed for high-level programming language (C) and multi-task operations System stack pointer adopted

Instruction set symmetry and barrel shift instructions

- Non-multiplex bus/multiplex bus compatible

- · Enhanced execution speed

- 4-byte instruction queue

- Enhanced interrupt functions

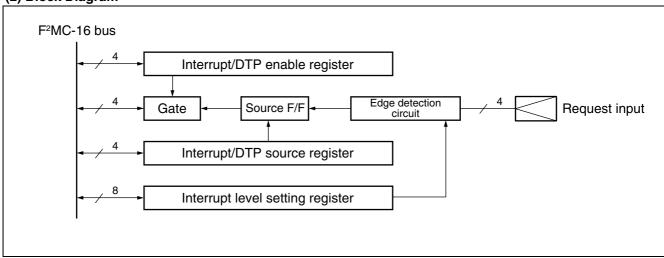

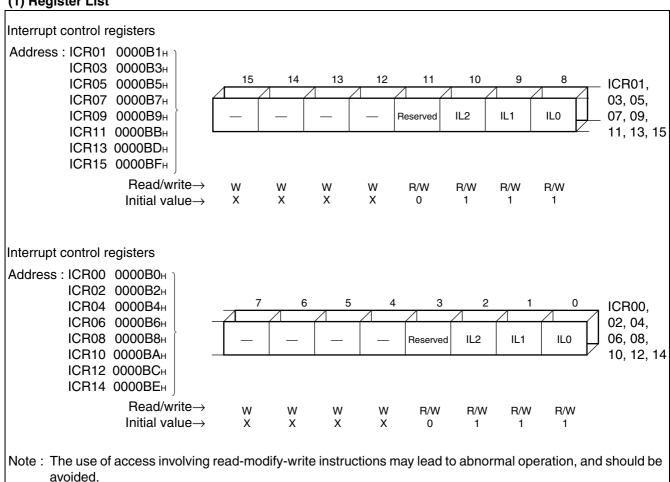

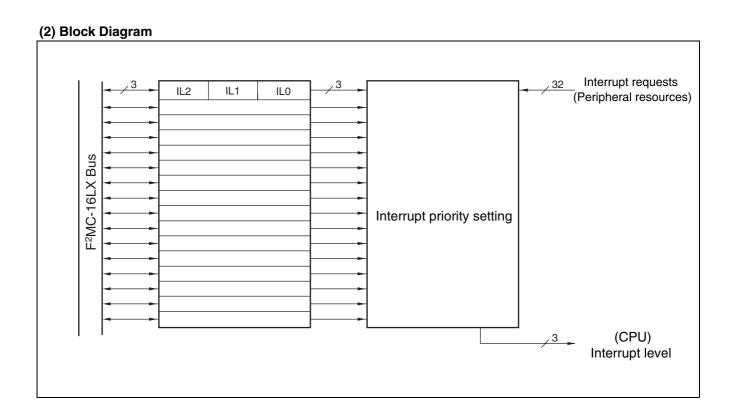

8 levels setting with programmable priority, 8 external interrupts

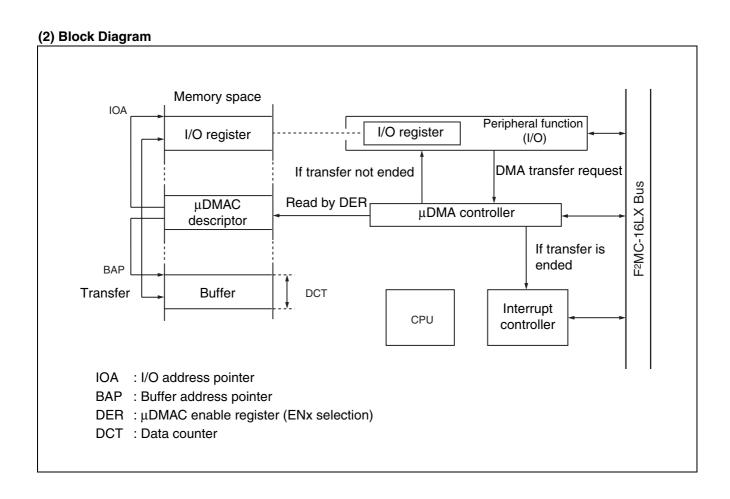

Data transfer function (μDMAC)

Up to 16 channels

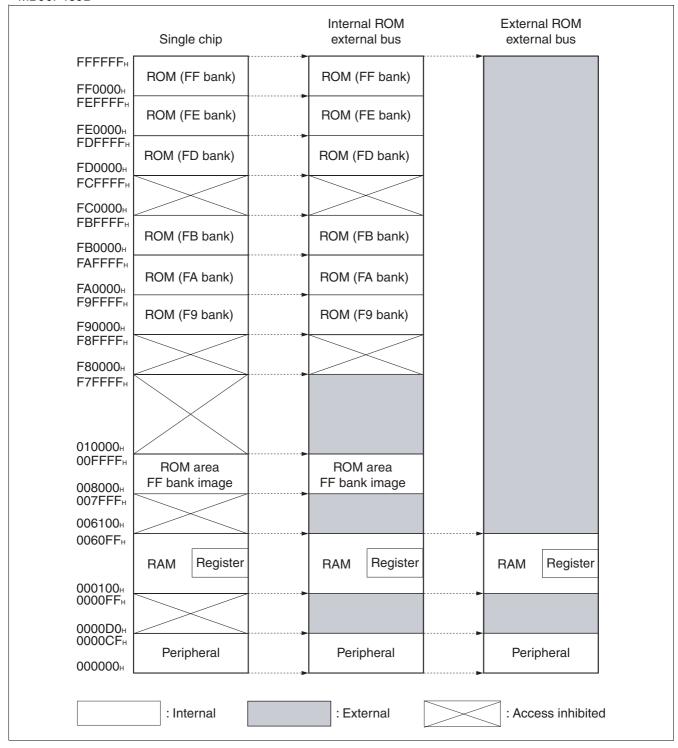

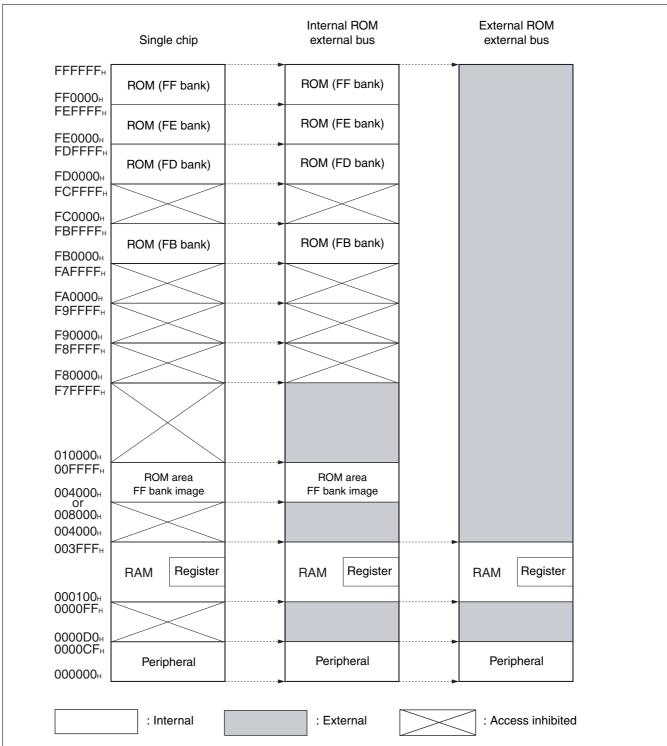

Embedded ROM

Flash versions: 192 Kbytes, 256 Kbytes, 384 Kbytes, MASK versions: 192 Kbytes, 256 Kbytes

Embedded RAM

Flash versions: 4 Kbytes, 6 Kbytes, 10 Kbytes, 24 Kbytes, MASK versions: 10 Kbytes, 16 Kbytes

· General purpose ports

Up to 84 ports

(Includes 16 ports with input pull-up resistance settings, 16 ports with output open-drain settings)

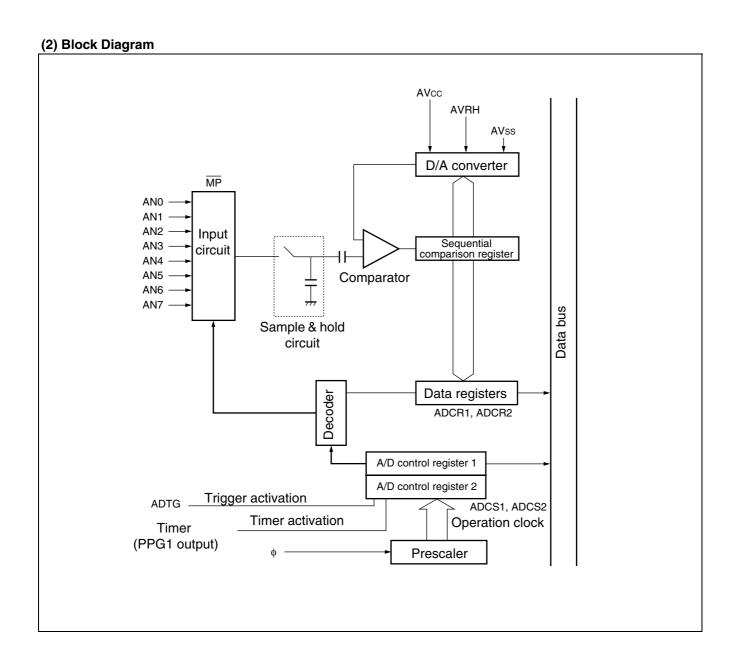

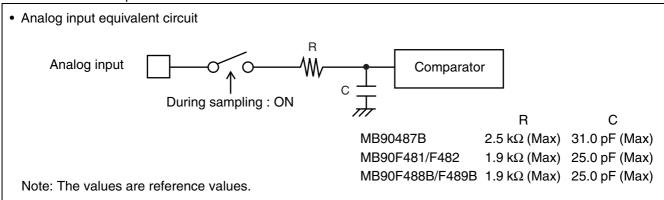

A/D converter

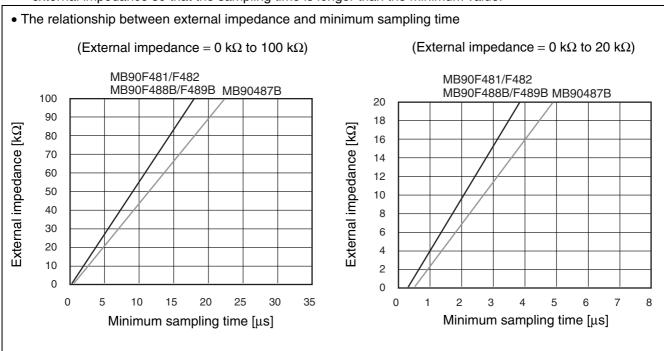

8-channel RC sequential comparison type (10-bit resolution, 3.68 μs conversion time (at 25 MHz))

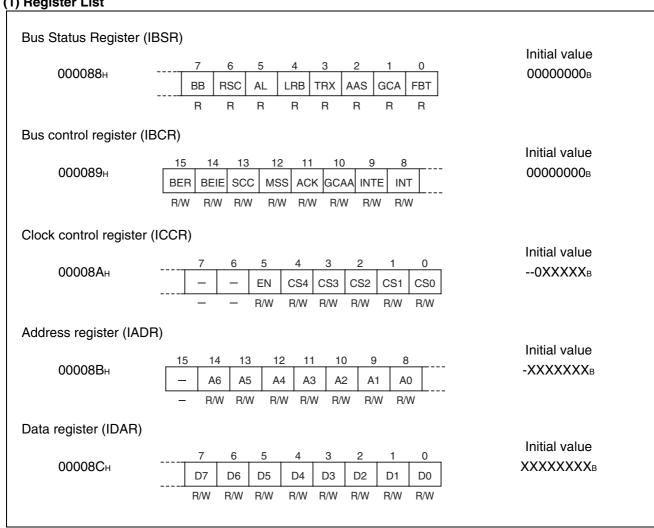

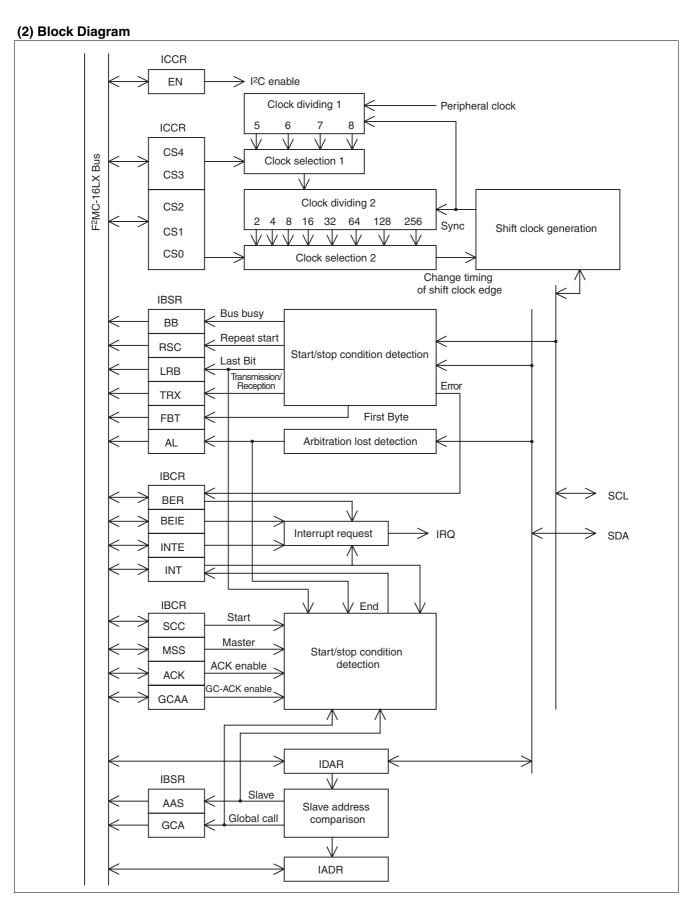

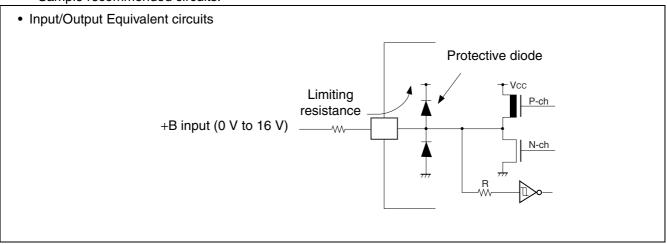

• I<sup>2</sup>C interface (MB90485 series only) : 1channel, P76/P77 N-ch open drain pin (without P-ch)

Do not apply high voltage in excess of recommended operating ranges to the N-ch open drain pin (with P-ch) in MB90V485B.

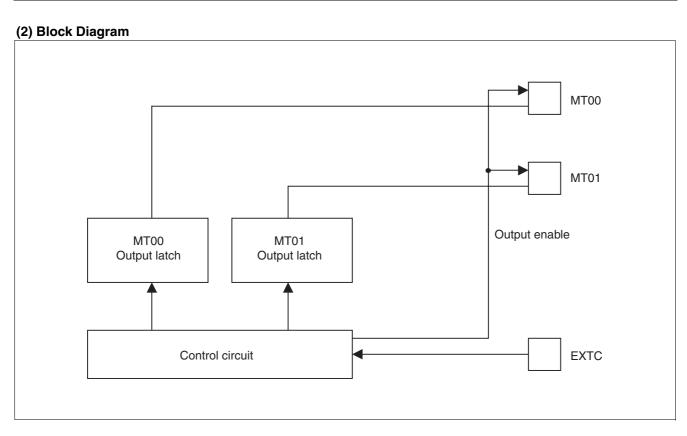

- μPG (MB90485 series only) : 1 channel

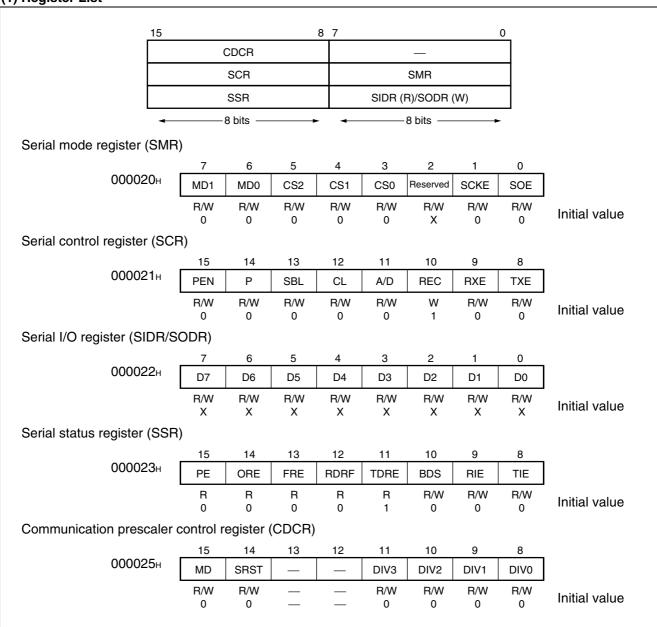

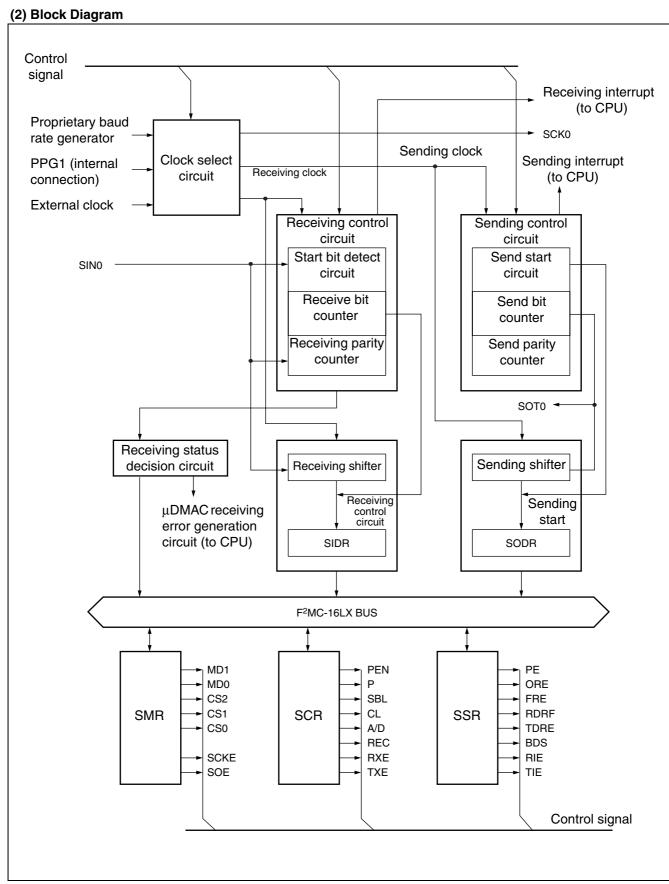

- UART: 1 channel

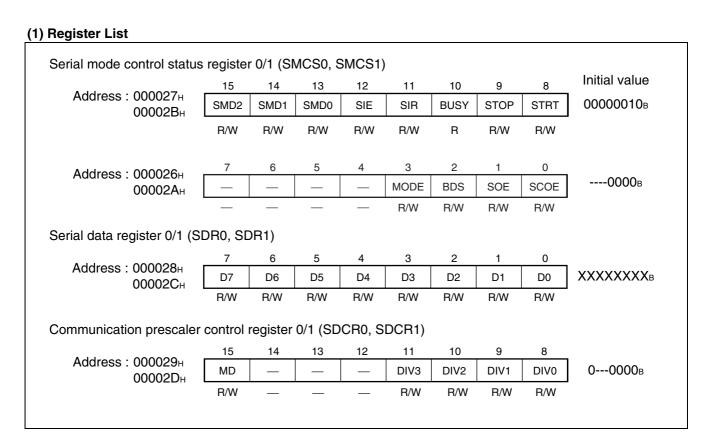

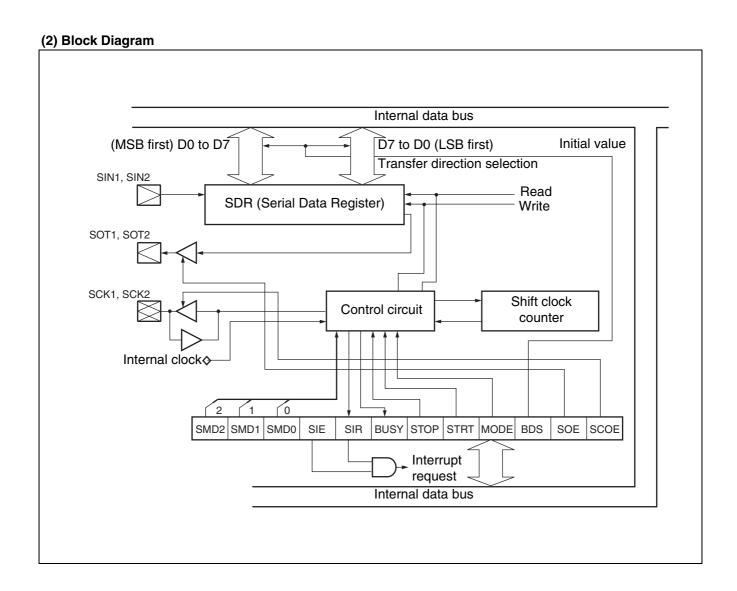

- Extended I/O serial interface (SIO): 2 channels

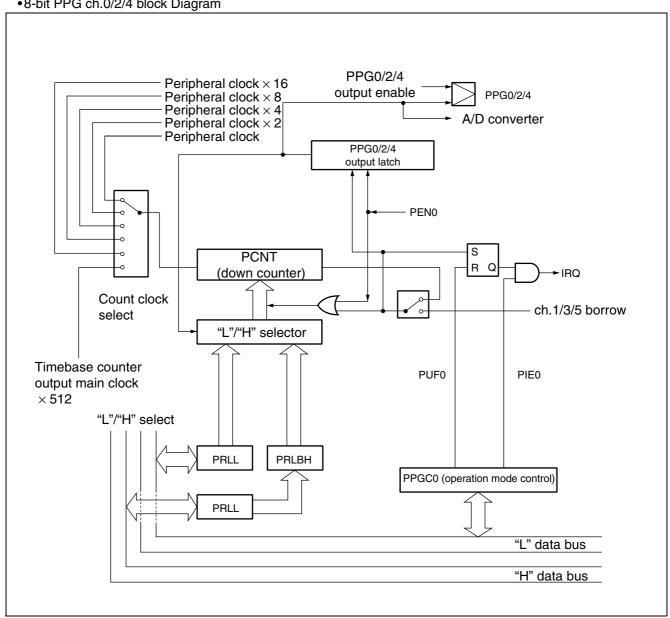

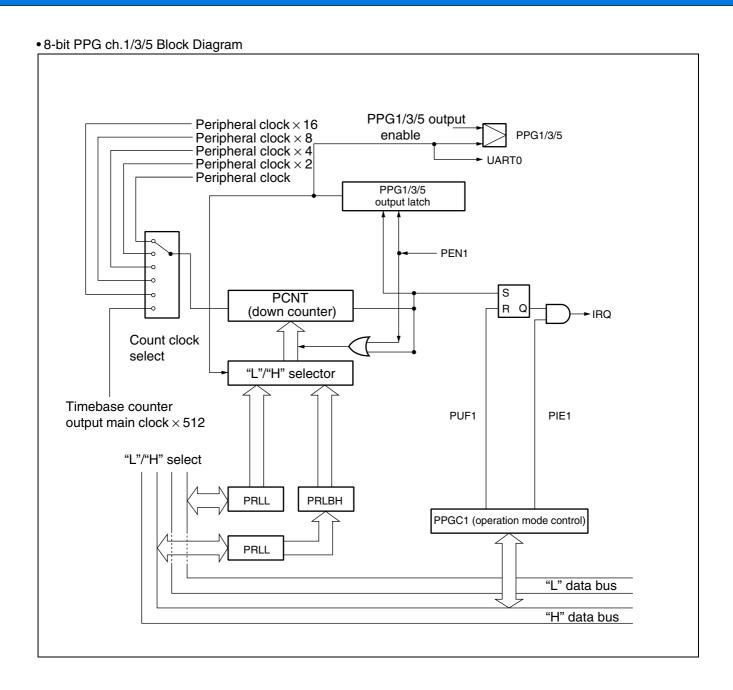

- 8/16-bit PPG: 3 channels (with 8-bit × 6 channel/16-bit × 3 channel mode switching function)

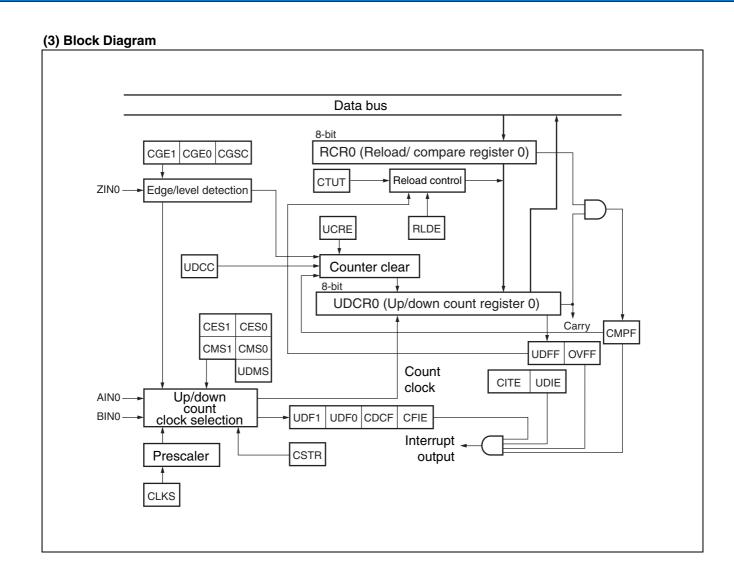

- 8/16-bit up/down counter/timer: 1 channel (with 8-bit × 2 channels/16-bit × 1-channel mode switching function)

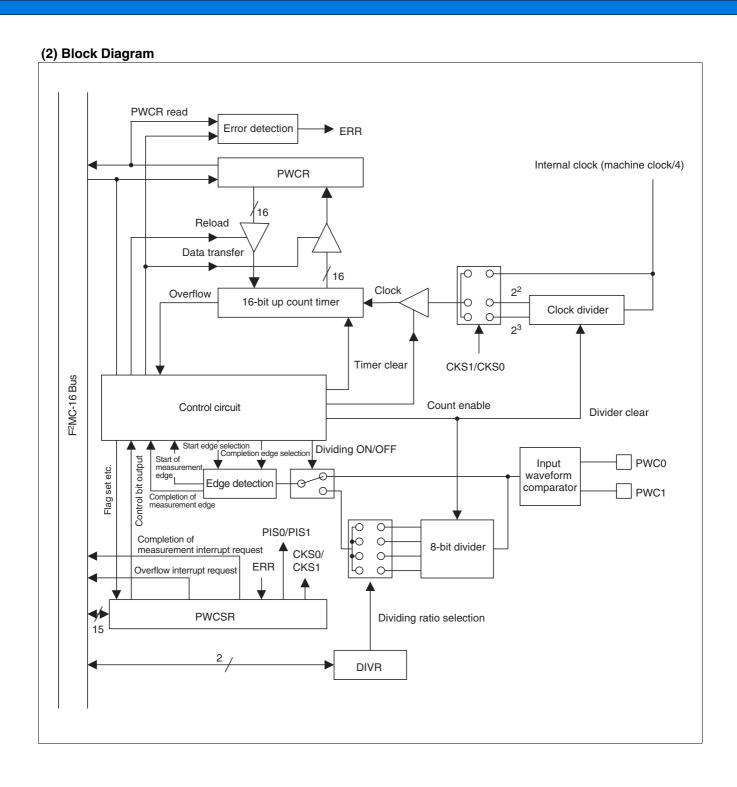

- PWC (MB90485 series only) : 3 channels (Capable of compare the inputs to two of the three)

- 3 V/5 V I/F pin (MB90485 series only)

P20 to P27, P30 to P37, P40 to P47, P70 to P77

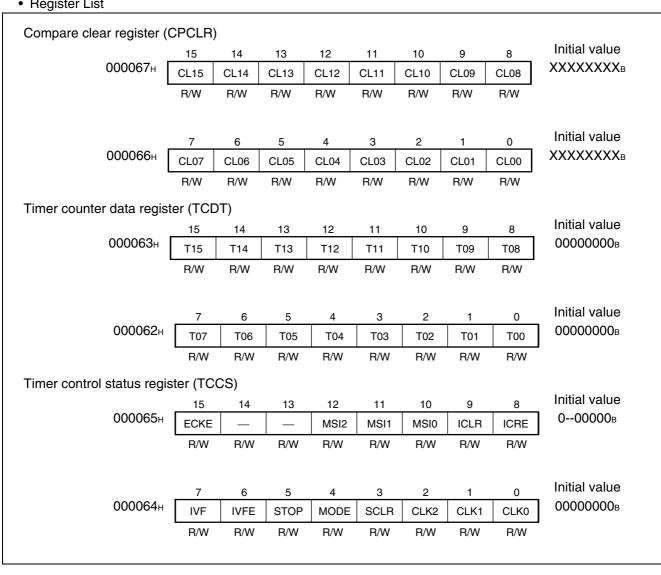

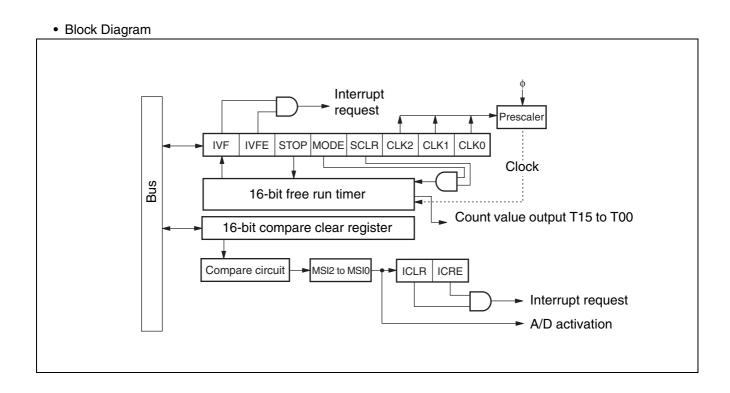

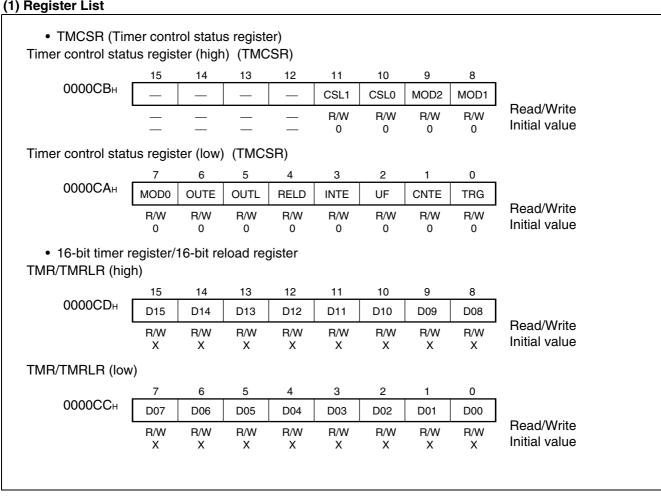

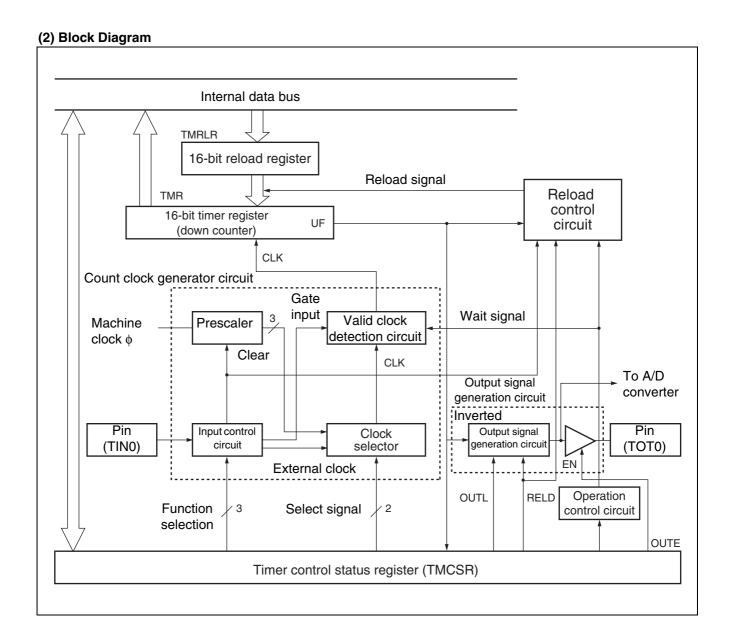

- 16-bit reload timer: 1 channel

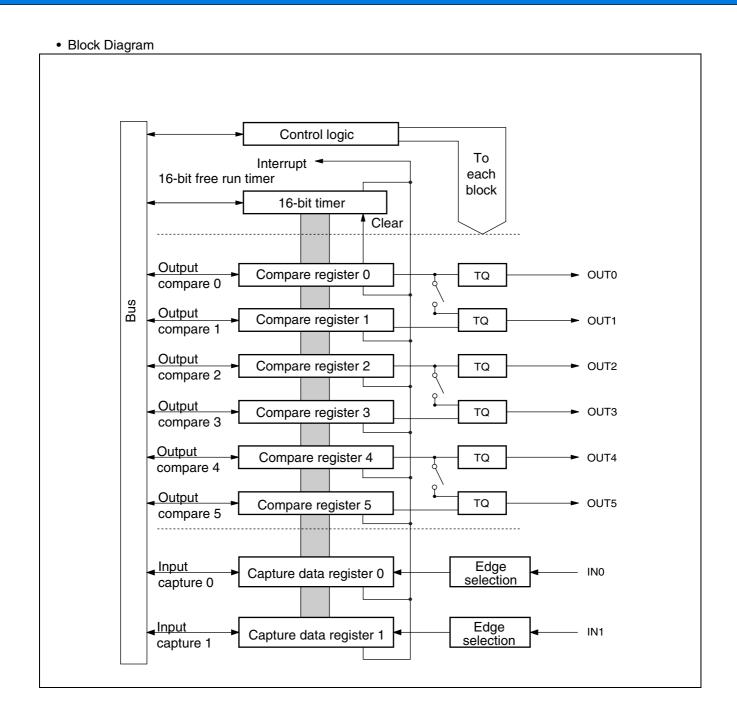

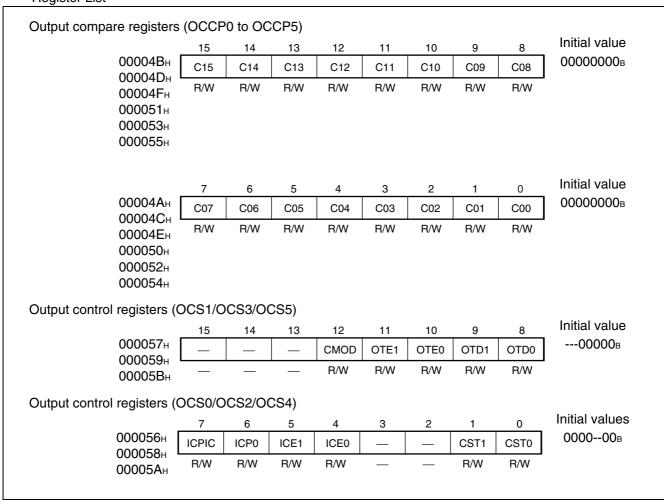

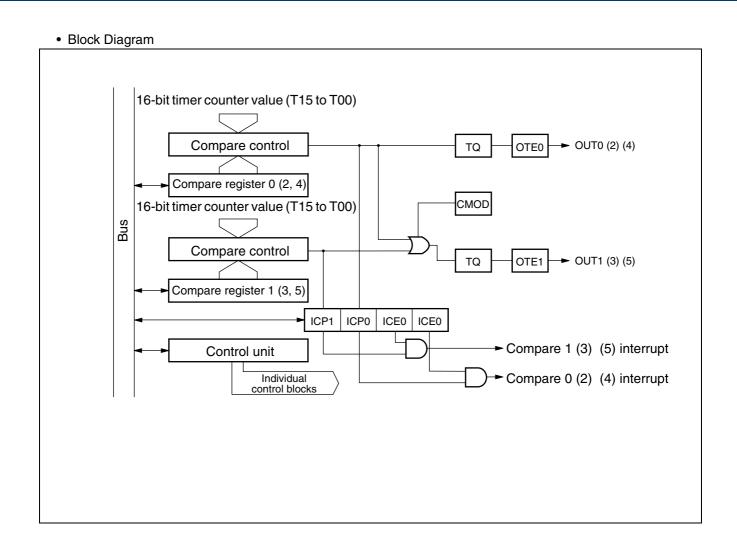

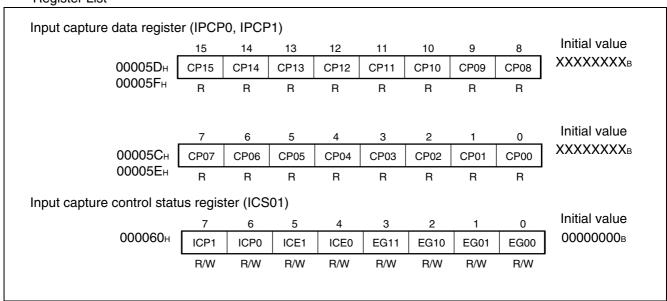

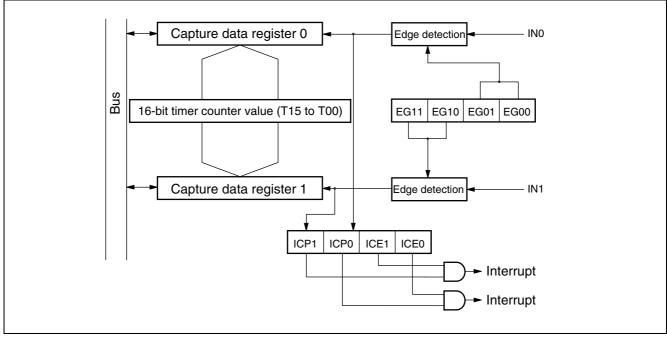

- 16-bit I/O timer: 2 channels input capture, 6 channels output compare, 1 channel free run timer

- On chip dual clock generator system

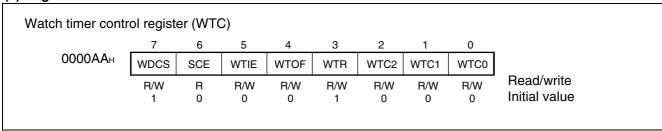

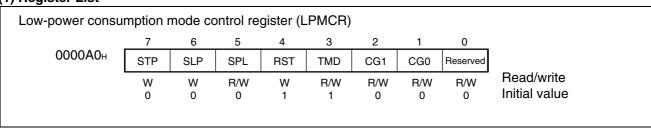

- Low-power consumption mode

With stop mode, sleep mode, CPU intermittent operation mode, watch mode, timebase timer mode

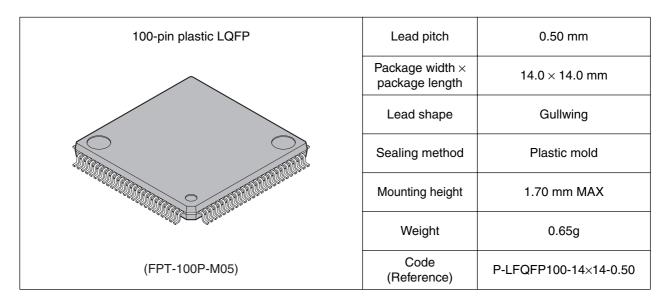

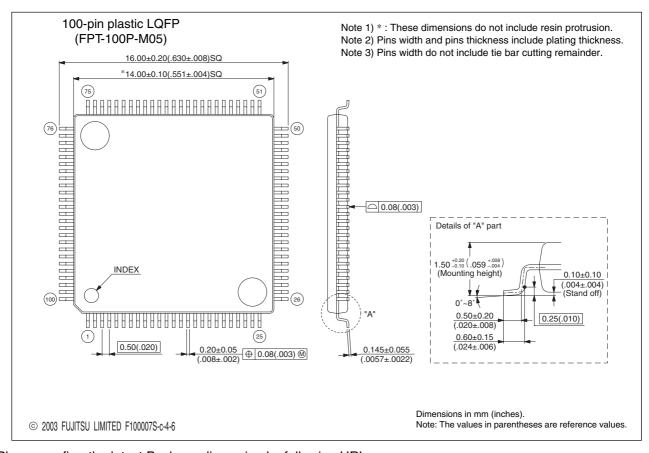

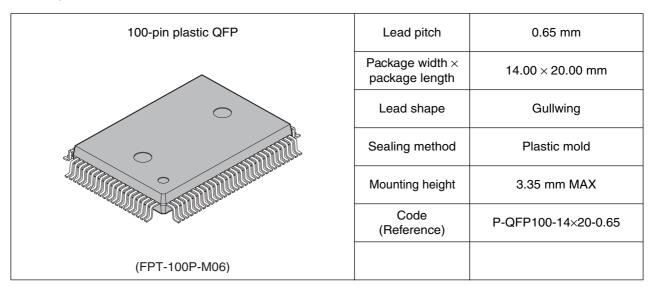

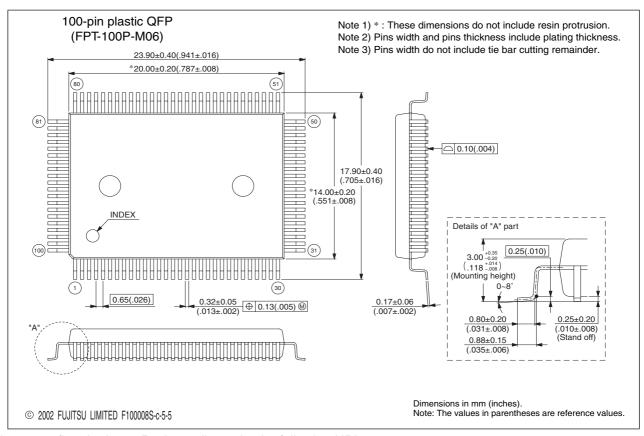

- Packages : QFP 100/LQFP 100

- Process : CMOS technology

- Power supply voltage: 3 V, single power supply (some ports can be operated by 5 V power supply at MB90485 series)

### **■ PRODUCT LINEUP**

#### • MB90480 series

| Classification Flash memory product Evaluation product ROM size 192 Kbytes 256 Kbytes — RAM size 4 Kbytes 6 Kbytes 16 Kbytes 17 Kbytes 17 Kbytes 17 Kbytes 17 Kbytes 18 Kbytes 17 Kbytes 18 Kbytes 1 | Item        | Part number           | MB90F481                                                                                            | MB90F482                                                                                                               | MB90V480                                                                                    |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--|--|--|

| ROM size 192 Kbytes 256 Kbytes — RAM size 4 Kbytes 6 Kbytes 16 Kby |             | on                    | Flash memo                                                                                          | ory product                                                                                                            | Evaluation product                                                                          |  |  |  |

| RAM size                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             | <u> </u>              | 1                                                                                                   |                                                                                                                        |                                                                                             |  |  |  |

| Number of instructions : 351 Instruction bit length : 8-bit, 16-bit Instruction length : 1 byte to 7 bytes Data bit length : 1-bit, 8-bit, 16-bit Instruction length : 1-bit, 8-bit, 16-bit Minimum instruction execution time : 40 ns (25 MHz machine cloc General-purpose I/O ports: up to 84 General-purpose I/O ports (CMOS output) General-purpose I/O ports (With pull-up resistance) General-purpose I/O ports (N-ch open drain output)  UART                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |                       | ·                                                                                                   | <u> </u>                                                                                                               | 16 Khytes                                                                                   |  |  |  |

| Instruction bit length : 8-bit, 16-bit Instruction length : 1 byte to 7 bytes Data bit length : 1-bit, 8-bit, 16-bit Minimum instruction execution time : 40 ns (25 MHz machine clock Minimum instruction execution time : 40 ns (25 MHz machine clock General-purpose I/O ports: up to 84 General-purpose I/O ports (with pull-up resistance) General-purpose I/O ports (With pull-up resista | 10 10 0120  |                       | •                                                                                                   |                                                                                                                        | To Naytoo                                                                                   |  |  |  |

| Ports  General-purpose I/O ports (CMOS output) General-purpose I/O ports (with pull-up resistance) General-purpose I/O ports (N-ch open drain output)  UART  1 channel, start-stop synchronized  8/16-bit PPG  8-bit × 6 channels/16-bit × 3 channels  8/16-bit up/down counter/timer  16-bit free run timer  Output compare (ICU)  DITUING capture (ICU)  Principut qapture (ICU)  Rewriting a register value upon a pin input (rising, falling, or both edges)  DTP/external interrupt circuit  Extended I/O serial interface  Timebase timer  18-bit counter Interrupt cycles: 1.0 ms, 4.1 ms, 16.4 ms, 131.1 ms (at 4 MHz base oscillator) Conversion resolution: 8/10-bit, switchable One-shot conversion mode (converts selected channels) Continuous conversion mode (repeated conversion of selected channels) Stop conversion mode (conversion of selected channels) Reset generation interval: 3.58 ms, 14.33 ms, 57.23 ms, 458.75 ms (minimum value, at 4 MHz base oscillator)  Low-power consumption (standby) modes  Type  Not included security function  General-purpose I/O ports (with pull-up resistance) General-purpose I/O ports (N-ch open drain output)  1 channels, variation output) Seneral number of channels: 2 Rewriting a register value upon a pin input (rising, falling, or both edges) Process  Conversion interrupt pin channels: 8 (edge or level detection)  Embedded 2 channels  18-bit counter Interrupt cycles: 1.0 ms, 4.1 ms, 16.4 ms, 131.1 ms (at 4 MHz base oscillator)  Conversion resolution: 8/10-bit, switchable One-shot conversion for multiple consecutive channels, programmable up to 8 channels)  Continuous conversion mode (conversion of selected channels with repeated paus  Reset generation interval: 3.58 ms, 14.33 ms, 57.23 ms, 458.75 ms (minimum value, at 4 MHz base oscillator)  Low-power consumption (standby) modes  Not included security function  User pin*1, 3 V/5 V versions                                                                                                                                                                      | CPU functi  | on                    | Instruction bit I<br>Instruction leng<br>Data bit length<br>Minimum instru                          | ength: 8-bit, 16-bit<br>gth: 1 byte to 7 t<br>: 1-bit, 8-bit, 3<br>uction execution time: 40                           | 16-bit                                                                                      |  |  |  |

| 8-bit × 6 channels/16-bit × 3 channels     8/16-bit up/down     16-bit up/down     16-bit free run timer     18-bit cannels : 6     19-bit free run timer     18-bit cannels : 2     19-bit free run timer     19-bit free run timer     19-bit free run timer     18-bit frea run t   | Ports       |                       | General-purpose I/O port<br>General-purpose I/O port                                                | ts (CMOS output)<br>ts (with pull-up resistance                                                                        |                                                                                             |  |  |  |

| Stop mode, Stop stores of CMOS    Stop mode, Stop mode, Stop mode, Stop mode, Stop stores of CMOS   Stop conversion mode (CMOS)   Stop conversion stop mode (CMOS)   Stop conversion mode (CMOS)   Stop conversion mode, CMOS   Stop conversion mode, Stop stores of CMOS   Stop conversion mode (CMOS)   Stop conversion mode, Stop stop mode, Stop stop mode, Stop stop mode, Stop stop stop mode, Stop    | UART        |                       | 1 channel, start-stop syn                                                                           | chronized                                                                                                              |                                                                                             |  |  |  |

| 16-bit free run timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 8/16-bit PF | PG .                  | 8-bit × 6 channels/16-bit                                                                           | × 3 channels                                                                                                           |                                                                                             |  |  |  |

| 16-bit tele run timer    18-bit counter    18-writing a register value upon a pin input (rising, falling, or both edges)  18-bit counter    18-b |             |                       |                                                                                                     |                                                                                                                        |                                                                                             |  |  |  |

| Input capture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |             | 16-bit free run timer |                                                                                                     |                                                                                                                        |                                                                                             |  |  |  |

| Input capture (ICU) Rewriting a register value upon a pin input (rising, falling, or both edges)  DTP/external interrupt circuit Extended I/O serial interface  Timebase timer  Interrupt cycles: 1.0 ms, 4.1 ms, 16.4 ms, 131.1 ms (at 4 MHz base oscillator)  Conversion resolution: 8/10-bit, switchable One-shot conversion mode (converts selected channel 1 time only) Scan conversion mode (conversion of multiple consecutive channels, programmable up to 8 channels) Continuous conversion mode (repeated conversion of selected channels with repeated paus  Watchdog timer  Reset generation interval: 3.58 ms, 14.33 ms, 57.23 ms, 458.75 ms (minimum value, at 4 MHz base oscillator)  Low-power consumption (standby) modes  Process  Not included security function  User pin*1, 3 V/5 V versions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 16-bit      | Output compare        |                                                                                                     |                                                                                                                        |                                                                                             |  |  |  |

| CICU  Rewriting a register value upon a pin input (rising, falling, or both edges)   DTP/external interrupt circuit   Number of external interrupt pin channels : 8 (edge or level detection)   Extended I/O serial interface   Embedded 2 channels   Timebase timer   18-bit counter   Interrupt cycles: 1.0 ms, 4.1 ms, 16.4 ms, 131.1 ms (at 4 MHz base oscillator)   Conversion resolution : 8/10-bit, switchable   One-shot conversion mode (converts selected channel 1 time only)   Scan conversion mode (conversion of multiple consecutive channels, programmable up to 8 channels)   Continuous conversion mode (repeated conversion of selected channels with repeated paus   Reset generation interval : 3.58 ms, 14.33 ms, 57.23 ms, 458.75 ms (minimum value, at 4 MHz base oscillator)   Stop mode, sleep mode, CPU intermittent operation mode, watch timer mod timebase timer mode   CMOS   User pin*1, 3 V/5 V versions   | I/O timers  | ' '                   |                                                                                                     |                                                                                                                        |                                                                                             |  |  |  |

| DTP/external interrupt circuit Extended I/O serial interface  Embedded 2 channels  18-bit counter Interrupt cycles: 1.0 ms, 4.1 ms, 16.4 ms, 131.1 ms (at 4 MHz base oscillator Conversion resolution: 8/10-bit, switchable One-shot conversion mode (conversion of multiple consecutive channels, programmable up to 8 channels) Continuous conversion mode (repeated conversion of selected channels with repeated paus  Watchdog timer  Watchdog timer  Reset generation interval: 3.58 ms, 14.33 ms, 57.23 ms, 458.75 ms (minimum value, at 4 MHz base oscillator)  Stop mode, sleep mode, CPU intermittent operation mode, watch timer mod timebase timer mode  Process  Not included security function  User pin*1, 3 V/5 V versions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |             |                       |                                                                                                     |                                                                                                                        |                                                                                             |  |  |  |

| Extended I/O serial interface  Timebase timer  18-bit counter Interrupt cycles: 1.0 ms, 4.1 ms, 16.4 ms, 131.1 ms (at 4 MHz base oscillated Conversion resolution: 8/10-bit, switchable One-shot conversion mode (converts selected channel 1 time only) Scan conversion mode (conversion of multiple consecutive channels, programmable up to 8 channels) Continuous conversion mode (repeated conversion of selected channels) Stop conversion mode (conversion of selected channels with repeated paus Watchdog timer  Reset generation interval: 3.58 ms, 14.33 ms, 57.23 ms, 458.75 ms (minimum value, at 4 MHz base oscillator)  Low-power consumption (standby) modes  Process  CMOS  Type  Not included security function  User pin*1, 3 V/5 V versions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             | ` '                   |                                                                                                     |                                                                                                                        |                                                                                             |  |  |  |

| Timebase timer    18-bit counter   Interrupt cycles: 1.0 ms, 4.1 ms, 16.4 ms, 131.1 ms (at 4 MHz base oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |                       |                                                                                                     | upt pin channels : 8 (edg                                                                                              | ge or level detection)                                                                      |  |  |  |

| Interrupt cycles: 1.0 ms, 4.1 ms, 16.4 ms, 131.1 ms (at 4 MHz base oscillator Conversion resolution: 8/10-bit, switchable One-shot conversion mode (converts selected channel 1 time only) Scan conversion mode (conversion of multiple consecutive channels, programmable up to 8 channels) Continuous conversion mode (repeated conversion of selected channels with repeated paus Stop conversion mode (conversion of selected channels with repeated paus Reset generation interval: 3.58 ms, 14.33 ms, 57.23 ms, 458.75 ms (minimum value, at 4 MHz base oscillator)  Low-power consumption (standby) modes  Process  Not included security function  User pin*1, 3 V/5 V versions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Extended I  | O serial interface    | Embedded 2 channels                                                                                 |                                                                                                                        |                                                                                             |  |  |  |

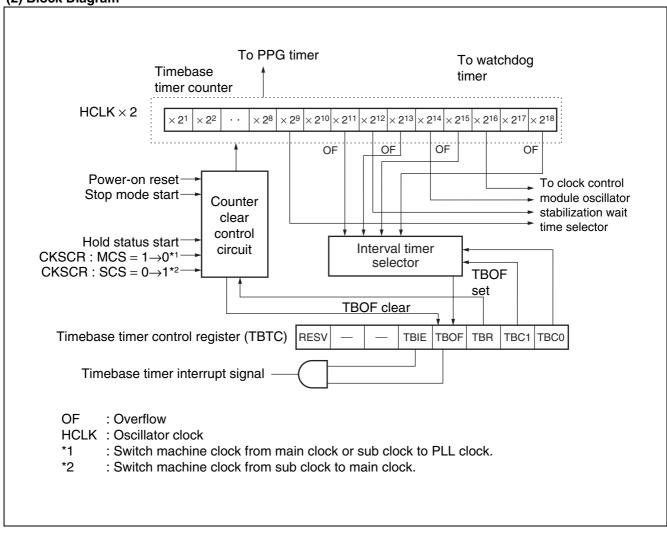

| A/D converter  One-shot conversion mode (converts selected channel 1 time only) Scan conversion mode (conversion of multiple consecutive channels, programmable up to 8 channels) Continuous conversion mode (repeated conversion of selected channels) Stop conversion mode (conversion of selected channels with repeated paus description of selected channels with repeated paus mode)  Reset generation interval: 3.58 ms, 14.33 ms, 57.23 ms, 458.75 ms (minimum value, at 4 MHz base oscillator)  Low-power consumption (standby) modes  Process  CMOS  Not included security function  User pin*1, 3 V/5 V versions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Timebase    | timer                 |                                                                                                     | 4.1 ms, 16.4 ms, 131.1 n                                                                                               | ns (at 4 MHz base oscillator)                                                               |  |  |  |

| (minimum value, at 4 MHz base oscillator)  Low-power consumption (standby) modes  Process  Type  (minimum value, at 4 MHz base oscillator)  Stop mode, sleep mode, CPU intermittent operation mode, watch timer mode  CMOS  User pin*1, 3 V/5 V versions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | A/D conve   | rter                  | One-shot conversion mode (continuous conversion mode)  Continuous conversion mode (conversion mode) | de (converts selected che conversion of multiple co programmable up to 8 che node (repeated conversion of selected che | nsecutive channels,<br>nannels)<br>on of selected channels)<br>nannels with repeated pause) |  |  |  |

| (standby) modes     timebase timer mode       Process     CMOS       Type     Not included security function     User pin*1, 3 V/5 V versions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Watchdog    | timer                 | Reset generation interval                                                                           |                                                                                                                        |                                                                                             |  |  |  |

| Type Not included security function User pin*1, 3 V/5 V versions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | •           | -                     |                                                                                                     | CPU intermittent operati                                                                                               | on mode, watch timer mode,                                                                  |  |  |  |

| 3 V/5 V versions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Process     |                       |                                                                                                     | CMOS                                                                                                                   |                                                                                             |  |  |  |

| Emulator power supply*2 — Included                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Туре        |                       | Not included se                                                                                     | ecurity function                                                                                                       |                                                                                             |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Emulator p  | ower supply*2         | _                                                                                                   | _                                                                                                                      | Included                                                                                    |  |  |  |

<sup>\*1:</sup> User pin: P20 to P27, P30 to P37, P40 to P47, P70 to P77

Note : Ensure that you must write to Flash at Vcc = 3.13 V to 3.60 V (3.3 V + 10%, -5%) .

<sup>\*2:</sup> It is setting of Jumper switch (TOOL VCC) when emulator (MB2147-01) is used. Please refer to the MB2147-01 or MB2147-20 hardware manual (3.3 Emulator-dedicated Power Supply switching) about details.

### • MB90485 series

|                         | Part number                |                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                              |                                                               |                                                               |                            |                  |  |  |  |

|-------------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|---------------------------------------------------------------|---------------------------------------------------------------|----------------------------|------------------|--|--|--|

| Item                    | Tarthambon                 | MB90487B                                                                                                                                                                                                                                                                                                                                                                                                                                        | MB90488B                                                                     | MB90F488B                                                     | MB90V485B                                                     | MB90F489B                  | MB90483C         |  |  |  |

| Classific               | ation                      | MASK RO                                                                                                                                                                                                                                                                                                                                                                                                                                         | M product                                                                    | Flash<br>memory<br>product                                    | Evaluation product                                            | Flash<br>memory<br>product | MASK ROM product |  |  |  |

| ROM siz                 | e                          | 192 Kbytes                                                                                                                                                                                                                                                                                                                                                                                                                                      | 256 Kbytes                                                                   | 256 Kbytes                                                    | _                                                             | 384 Kbytes                 | 256 Kbytes       |  |  |  |

| RAM siz                 | е                          | 10 Kbytes                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10 Kbytes                                                                    | 10 Kbytes                                                     | 16 Kbytes                                                     | 24 Kbytes                  | 16 Kbytes        |  |  |  |

| CPU fun                 | ction                      | Inst<br>Inst<br>Dat                                                                                                                                                                                                                                                                                                                                                                                                                             | nber of instruction bit lengruction bit length a bit length imum instruction | gth : 8-bit,<br>: 1 byt                                       | . 16-bit<br>e to 7 bytes<br>. 8-bit, 16-bit<br>me : 40 ns (25 | MHz machine                | clock)           |  |  |  |

| Ports                   |                            | General-purp<br>General-purp                                                                                                                                                                                                                                                                                                                                                                                                                    | ose I/O ports (                                                              | up to 84<br>CMOS output)<br>with pull-up res<br>N-ch open dra | sistance)                                                     |                            |                  |  |  |  |

| UART                    |                            | 1 channel, sta                                                                                                                                                                                                                                                                                                                                                                                                                                  | ırt-stop synchı                                                              | onized                                                        |                                                               |                            |                  |  |  |  |

| 8/16-bit                | PPG                        | 8-bit $\times$ 6 channels/16-bit $\times$ 3 channels                                                                                                                                                                                                                                                                                                                                                                                            |                                                                              |                                                               |                                                               |                            |                  |  |  |  |

| 8/16-bit<br>counter/    |                            | Event input pins : 6, 8-bit up/down counters : 2<br>8-bit reload/compare registers : 2                                                                                                                                                                                                                                                                                                                                                          |                                                                              |                                                               |                                                               |                            |                  |  |  |  |

|                         | 16-bit free run<br>timer   | Number of channels : 1 Overflow interrupt                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                              |                                                               |                                                               |                            |                  |  |  |  |

| 16-bit<br>I/O<br>timers | Output<br>compare<br>(OCU) | Number of ch<br>Pin input factor                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                              | gnal of compare                                               | e register                                                    |                            |                  |  |  |  |

|                         | Input capture (ICU)        | Number of channels : 2 Rewriting a register value upon a pin input (rising, falling, or both edges)                                                                                                                                                                                                                                                                                                                                             |                                                                              |                                                               |                                                               |                            |                  |  |  |  |

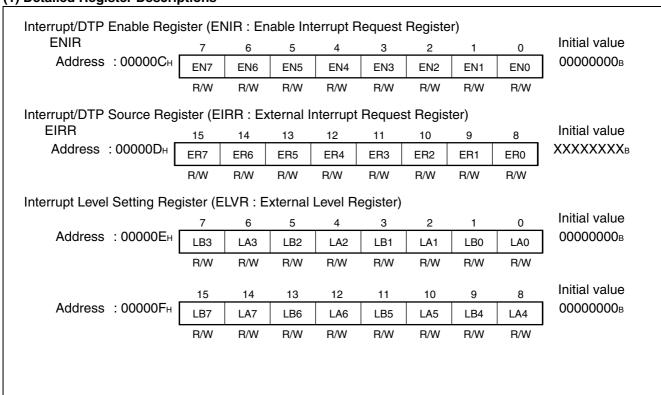

| DTP/exto                | ernal interrupt            | Number of external interrupt pin channels: 8 (edge or level detection)                                                                                                                                                                                                                                                                                                                                                                          |                                                                              |                                                               |                                                               |                            |                  |  |  |  |

| Extende interface       | d I/O serial               | Embedded 2 channels                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                              |                                                               |                                                               |                            |                  |  |  |  |

| I <sup>2</sup> C interf | ace*2                      | 1 channel                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                              |                                                               |                                                               |                            |                  |  |  |  |

| μPG                     |                            | 1 channel                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                              |                                                               |                                                               |                            |                  |  |  |  |

| PWC                     |                            | 3 channels                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                              |                                                               |                                                               |                            |                  |  |  |  |

| Timebas                 | e timer                    | 18-bit counter<br>Interrupt cycle                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                              | 1 ms, 16.4 ms,                                                | 131.1 ms (at 4                                                | MHz base ose               | cillator)        |  |  |  |

| A/D con                 | verter                     | Interrupt cycles: 1.0 ms, 4.1 ms, 16.4 ms, 131.1 ms (at 4 MHz base oscillator)  Conversion resolution: 8/10-bit, switchable One-shot conversion mode (converts selected channel 1 time only) Scan conversion mode (conversion of multiple consecutive channels, programmable up to 8 channels) Continuous conversion mode (repeated conversion of selected channels) Stop conversion mode (conversion of selected channels with repeated pause) |                                                                              |                                                               |                                                               |                            |                  |  |  |  |

### (Continued)

| (Continued)                           |                              |                              | T                                                             |                              | T                                                             |                              |

|---------------------------------------|------------------------------|------------------------------|---------------------------------------------------------------|------------------------------|---------------------------------------------------------------|------------------------------|

| Part number Item                      | MB90487B                     | MB90488B                     | MB90F488B                                                     | MB90V485B                    | MB90F489B                                                     | MB90483C                     |

| Watchdog timer                        | Reset genera                 |                              | .58 ms, 14.33 r<br>(minimum value                             |                              |                                                               |                              |

| Low-power consumption (standby) modes | Stop mode, sl<br>timer mode  | eep mode, CP                 | U intermittent o                                              | peration mode,               | watch timer mo                                                | ode, timebase                |

| Process                               | CMOS                         |                              |                                                               |                              |                                                               |                              |

| Туре                                  | 3 V/5 V<br>power<br>supply*1 | 3 V/5 V<br>power<br>supply*1 | 3 V/5 V power<br>supply*1<br>Included<br>security<br>function | 3 V/5 V<br>power<br>supply*1 | 3 V/5 V power<br>supply*1<br>Included<br>security<br>function | 3 V/5 V<br>power<br>supply*1 |

| Emulator power supply*3               | _                            | _                            | _                                                             | Included                     | _                                                             | _                            |

<sup>\*1: 3</sup> V/5 V I/F pin: All pins should be for 3 V power supply without P20 to P27, P30 to P37, P40 to P47, and P70 to P77.

Notes: • As for MB90V485B, input pins (PWC0, PWC1, PWC2/EXTC/SCL and SDA pins) for PWC/μPG/I²C become CMOS input.

$\bullet$  Ensure that you must write to Flash at Vcc = 3.13 V to 3.60 V (3.3 V + 10%, - 5%) .

$<sup>^*2</sup>$ : P76/P77 pins are N-ch open drain pins (without P-ch) at built-in I<sup>2</sup>C. However, MB90V485B uses the N-ch open drain pin (with P-ch) .

<sup>\*3:</sup> It is setting of Jumper switch (TOOL VCC) when emulator (MB2147-01) is used. Please refer to the MB2147-01 or MB2147-20 hardware manual (3.3 Emulator-dedicated Power Supply Switching) about details.

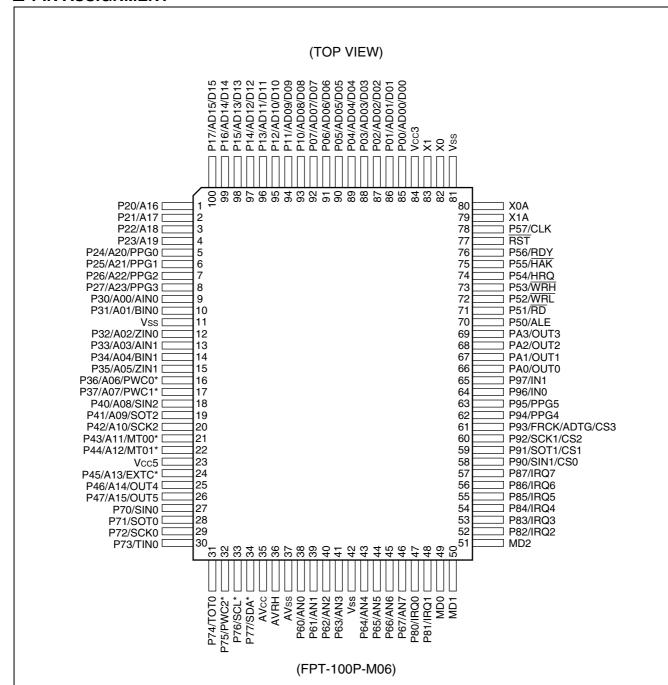

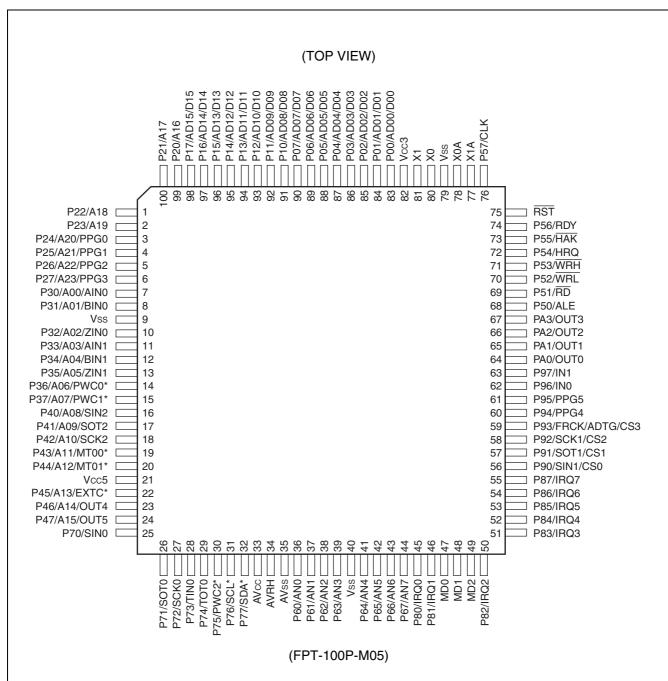

### **■ PIN ASSIGNMENT**

\*: These are the pins for MB90485 series. The pins for MB90480 series are P36/A06, P37/A07, P43/A11, P44/A12, P45/A13, P75 to P77.

Note: MB90485 series only

- I<sup>2</sup>C pin P77 and P76 are N-ch open drain pin (without P-ch) . However, MB90V485B uses the N-ch open drain pin (with P-ch) .

- P20 to P27, P30 to P37, P40 to P47 and P70 to P77 are also used as 3 V/5 V I/F pin.

- As for MB90V485B, input pins (PWC0, PWC1, PWC2/EXTC/SCL and SDA pins) for PWC/μPG/I<sup>2</sup>C become CMOS input.

\*: These are the pins for MB90485 series. The pins for MB90480 series are P36/A06, P37/A07, P43/A11, P44/A12, P45/A13, P75 to P77.

Note: MB90485 series only

- I<sup>2</sup>C pin P77 and P76 are N-ch open drain pin (without P-ch) . However, MB90V485B uses the N-ch open drain pin (with P-ch) .

- P20 to P27, P30 to P37, P40 to P47 and P70 to P77 are also used as 3 V/5 V I/F pin.

- As for MB90V485B, input pins (PWC0, PWC1, PWC2/EXTC/SCL and SDA pins) for PWC/ μPG/I<sup>2</sup>C become CMOS input.

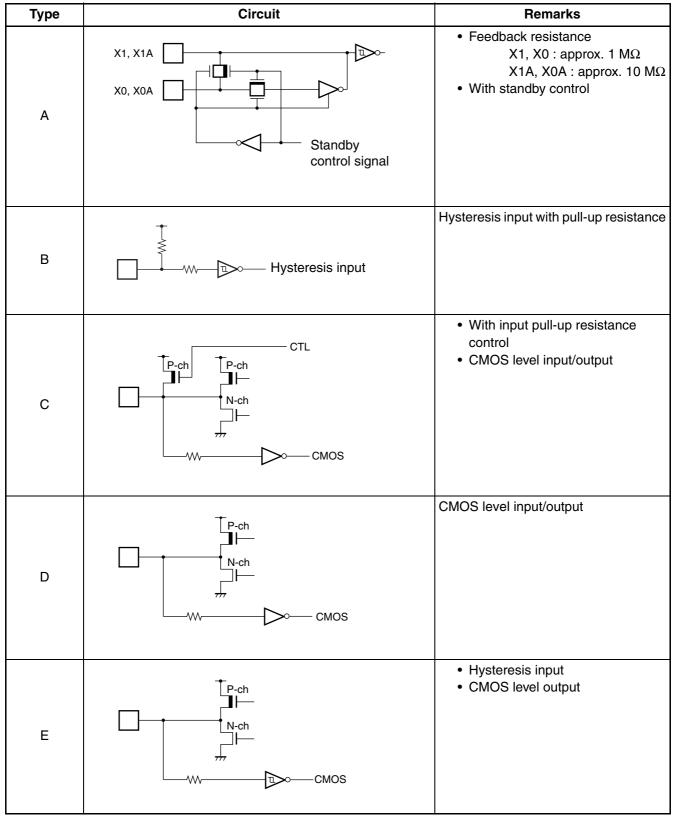

## ■ PIN DESCRIPTIONS

| Pin          | No.            |                 | I/O               |                                                                                                                                                                                                                                                                                                                                  |

|--------------|----------------|-----------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| QFP*1        | LQFP*2         | Pin name        | circuit<br>type*3 | Function                                                                                                                                                                                                                                                                                                                         |

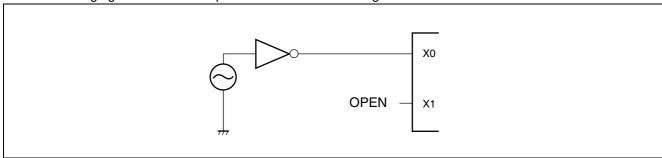

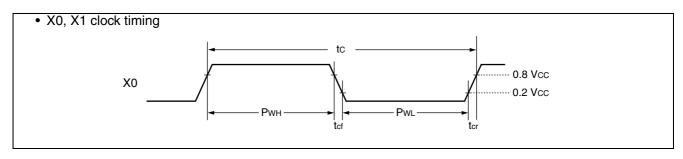

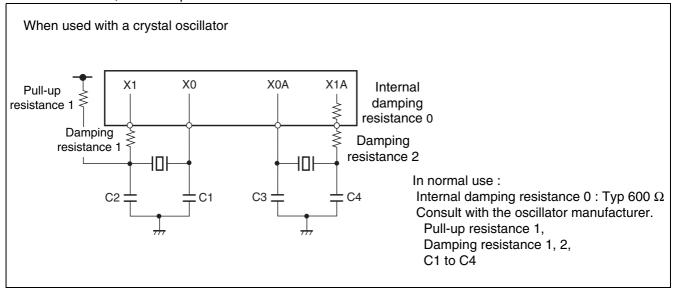

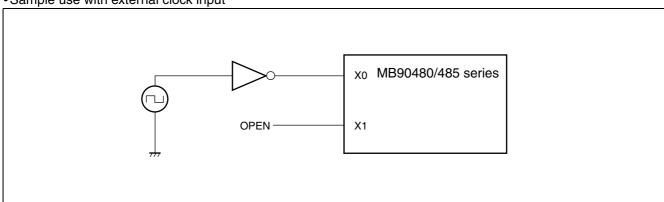

| 82           | 80             | X0              | Α                 | Clock (oscillator) input pin                                                                                                                                                                                                                                                                                                     |

| 83           | 81             | X1              | Α                 | Clock (oscillator) output pin                                                                                                                                                                                                                                                                                                    |

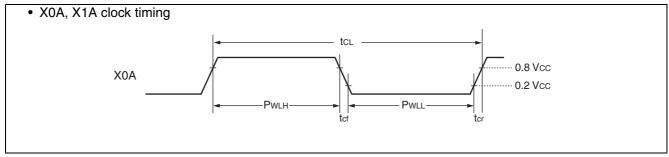

| 80           | 78             | X0A             | Α                 | Clock (32 kHz oscillator) input pin                                                                                                                                                                                                                                                                                              |

| 79           | 77             | X1A             | Α                 | Clock (32 kHz oscillator) output pin                                                                                                                                                                                                                                                                                             |

| 77           | 75             | RST             | В                 | Reset input pin                                                                                                                                                                                                                                                                                                                  |

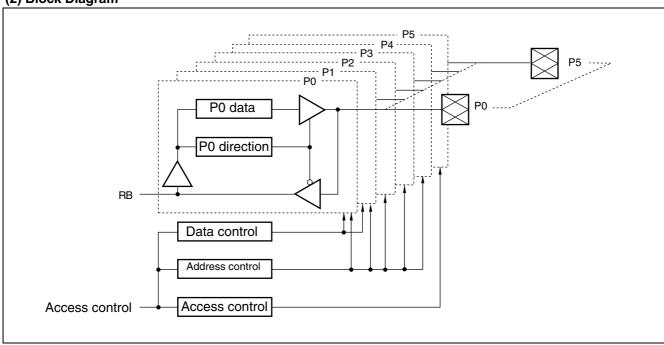

|              |                | P00 to P07      |                   | This is a general purpose I/O port. A setting in the port 0 input resistance register (RDR0) can be used to apply pull-up resistance (RD00-RD07 = "1") . (Disabled when pin is set for output.)                                                                                                                                  |

| 85 to 92     | 83 to 90       | AD00 to<br>AD07 | C<br>(CMOS)       | In multiplex mode, these pins function as the external address/data bus low I/O pins.                                                                                                                                                                                                                                            |

|              |                | D00 to D07      |                   | In non-multiplex mode, these pins function as the external data bus low output pins.                                                                                                                                                                                                                                             |

|              |                | P10 to P17      |                   | This is a general purpose I/O port. A setting in the port 1 input resistance register (RDR1) can be used to apply pull-up resistance (RD10-RD17 = "1") . (Disabled when pin is set for output.)                                                                                                                                  |

| 93 to<br>100 | 91 to 98       | AD08 to<br>AD15 | C<br>(CMOS)       | In multiplex mode, these pins function as the external address/data bus high I/O pins.                                                                                                                                                                                                                                           |

|              |                | D08 to D15      |                   | In non-multiplex mode, these pins function as the external data bus high output pins.                                                                                                                                                                                                                                            |

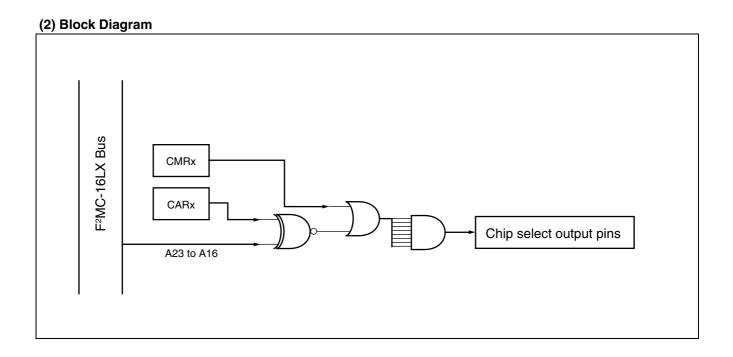

|              |                | P20 to P23      |                   | This is a general purpose I/O port. When the bits of external address output control register (HACR) are set to "1" in external bus mode, these pins function as general purpose I/O ports.                                                                                                                                      |