# SSI 32M594 Three-Phase Delta Motor Speed Controller Preliminary Data

July 1990

### DESCRIPTION

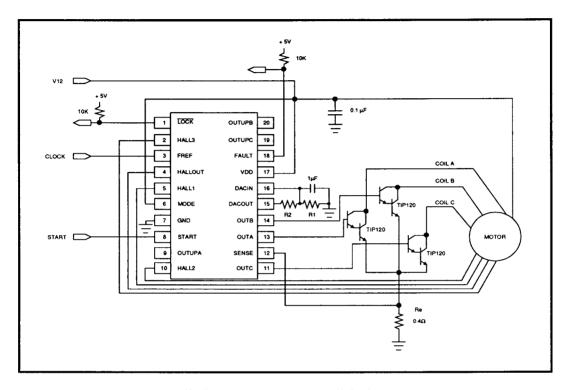

The SSI 32M594 is a motor speed control IC designed to provide all timing and control functions necessary to start, drive, and brake a 3-phase, 4 or 8 pole brushless DC spindle motor. External Darlington power transistors or external power FETs may be used by the SSI 32M594 to drive the spindle motor.

The motor Hall sensors are directly driven and decoded by the device. The controller is optimized for a 3600 rpm motor using a 2 MHz clock. Motor protection features include jammed platter shutdown, supply and clock fault detection, all of which are indicated by a FAULT signal, and coil over-current detection and control. A LOCK signal is provided to indicate that the motor is at speed. The device's linear control loop controls the power drivers using Pulse Amplitude Modulation.

The SSI 32M594 requires a +12V power supply, and is available in 20-pin DIP or SO packages.

## **FEATURES**

- Supports wide range of DC brushless 3-phase motors, including 3 1/2" motors

- 4 or 8-pole operation

- 3600 rpm speed control using a 2 MHz clock

- Highly accurate speed regulation of ±0.037%

- Provides for gain scaling of the motor current voltage

- On-chip digital filter

- · At speed indication provided

- Active braking function

- Output pre-driver for center tap or non-center tap windings

- Drives complementary Darlington power transistors or complementary power FETs

- Power supply fault protection

- Motor over-current protection

- Multiple retry on jammed spindle

- Single +12 volt power supply

# **BLOCK DIAGRAM** FRE OUTPUT VLVDT START START HALLOUT LOCK HALLOUT REVERSE HALL1 MODE SLEW DIA ACCUM. D/A OUTX SLEW CK VDAC DACOU 7-13

0790 - rev.

## **FUNCTIONAL DESCRIPTION**

The SSI 32M594 uses a mix of analog and digital techniques to accomplish speed control. The control signal is generated by analog conversion of a digital speed error term developed by examining the contents of a count-down counter once per motor revolution. The sign and magnitude of the remainder controls the amplitude of a correction signal applied to the motor. Commutation timing, developed from motor generated HALL signals, applies the correction in the proper phase sequence.

The device uses a Pulse Amplitude Modulation (PAM) scheme rather than Pulse Width Modulation (PWM) to avoid the switching transients and torque ripple inherent in PWM.

The SSI 32M594 generates a motor current voltage which is related to the motor speed error. This is implemented on the IC by digital/analog techniques, converting a motor frequency error derived from a reference clock and digital counter into a voltage using switched capacitor D/A's. The voltage Vc translates into a motor current across Re regulating motor speed.

In operation, the SSI 32M594 is installed in a closed loop control system that maintains the speed of a 3– Phase Brushless DC motor. By monitoring the HALL signal outputs of the motor, a control voltage is developed using both digital and analog techniques. The analog portion of the control loop uses switched capacitor techniques to eliminate the need for any external passive components required for loop compensation. An operation description of the circuit follows.

#### **CONTROL LOOP**

Referring to the block diagram, the major sections of the control loop are a 19-stage Counter, Integral and Proportional channels, D/A's and a Summer.

The speed error is determined by examining the contents of the counter once per revolution. The counter is preset once per revolution by an INDEX signal developed from the HALL1 input, at the same time any remainder resulting from a 500 KHz count-down rate is loaded into a latch.

The lower LSB's of the latch, except for the LSB, are used to drive the Proportional D/A while the entire contents of the latch are accumulated to control the Integral Channel. The MSB's of the accumulator drive the Integral D/A.

If the contents of the counter indicate that the speed is outside the linear regulation range ( $\pm 0.037\%$ ), this is decoded as a "FAST" or "SLOW" condition. Under these conditions the Proportional D/A output is driven to either end of its range, as appropriate. Under a slow condition, a fixed reference voltage is supplied to the output drives resulting in a start current of Vret/Re.

When  $\overline{\text{LOCK}}$  is low, the control voltage, VDAC, from the summer is used to generate the motor running current. VDAC is a summation of integral channel voltage which cancels out offsets in the loop and motor losses, and a proportional channel voltage which tracks speed variations from the counter. The two channel voltages are then summed and weighted. The control voltage applied is externally scaleable by resistors R1 and R2 at DACOUT and DACIN (see Typical Application diagram) to fit a wide range of motors including those used in 3 1/2" drives. Note that Re affects start current while R1 and R2 affect running current as Irunning = VDACIN/Re.

The Integral and Proportional channels perform several functions related to the operation of the control loop. One function is to control loop stability by maintaining the loop zero at 1 Hz. In operation this translates to the Integral channel responding to major bias point changes while the Proportional channel takes care of minor perturbations to the loop.

#### COMMUTATION

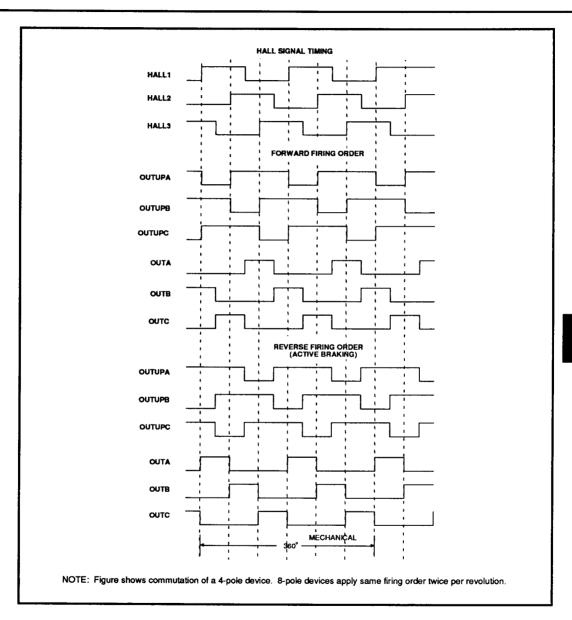

The summer output is channeled to the appropriate OUTA, B, C output according to the timing shown in Figure 1. To reduce switching transients, the outputs are slew rate controlled during each transition.

OUTUPA, B, C outputs cycle between approximately VDD in the OFF state and GND in the ON state also according to Figure 1. Again, rise and fall times are controlled during transitions.

FIGURE 1: Commutation Timing Diagram

## FUNCTIONAL DESCRIPTION (Continued)

#### MOTOR COIL OVER-CURRENT

Refer to SENSE input description. Sense voltage is generated by current through Re shown in the typical application. The SENSE input threshold limits the maximum coil current.

#### **FAULT CONDITIONS**

Four conditions cause an active high on the FAULT output pin, also disabling all drivers except as noted:

- (1) Low power supply VDD < Vlvdt

- (2) No FREF clock FREF < Fmin

- (3) Stalled motor. If the delay from power onset to a positive HALL index transition or the time

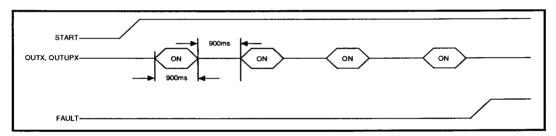

interval between successive HALL index transitions is greater than the specified time, the device interprets this delay as a stalled motor, reduces the motor current to zero and performs three retry cycles. If the motor continues to be stalled after three retries, then motor current is reduced to zero until such time as one positive HALL index transition is detected, the START pin is toggled, or power or FREF is removed and re-applied. After the fourth try, FAULT goes high. (See Figure 2)

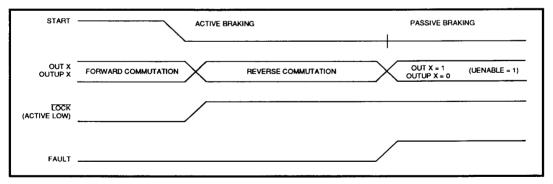

(4) Reverse shutdown speed. During active braking (START = 0) the HALL sensor's phasing is changed to apply a reverse torque to the motor until the motor speed drops below the reverse shutdown speed at which time the drivers turn off to deny power to the motor and FAULT goes high. (See Figure 3)

FIGURE 2: Jammed Platter Sequence

FIGURE 3: Active Braking Sequence

## **PIN DESCRIPTION**

| NAME         | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                               |  |

|--------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| VDD          | l    | +12V Power Supply                                                                                                                                                                                                                                                                                                         |  |

| GND          | 1    | Ground                                                                                                                                                                                                                                                                                                                    |  |

| FREF         | I    | The reference clock input used to set motor speed and operate circuit blocks.                                                                                                                                                                                                                                             |  |

| START        | ĺ    | A high level on this pin enables the motor. The START input must be low during power-up and should conform to Ts set-up time. Active braking is enabled by applying a logic "zero". During active braking the commutation is changed to apply a reverse torque to the motor until the motor velocity drops below 281 rpm. |  |

| MODE         | l    | Mode Control. When tied high (to VDD) selects 8-pole operation where HALL1 signal is divided by four to generate an index signal. When left open, 4-pole operation is selected and HALL1 is divided by two.                                                                                                               |  |

| FAULT        | 0    | FAULT goes active high indicating low VDD, no FREF, a stalled motor, or motor velocity below the reverse shutdown speed.                                                                                                                                                                                                  |  |

| LOCK         | 0    | LOCK, open drain active low, goes active low when the motor frequency is within a specified lock range.                                                                                                                                                                                                                   |  |

| SENSE        | I    | Coil Current Sense Input. Senses the coil current and limits the sense voltage to the specified threshold by limiting the voltage from the lower drivers. (OUTX)                                                                                                                                                          |  |

| HALLOUT      | 0    | Hall Sensor Bias Output. Provides a regulated bias voltage for the hall effect sensors.                                                                                                                                                                                                                                   |  |

| HALL1, 2, 3  | l    | Hall Sensor inputs that determine commutation. The TTL open-collector type motor outputs drive these inputs, which have internal resistor pullups referenced to the HALLOUT bias voltage.                                                                                                                                 |  |

| OUTUPA, B, C | 0    | Upper motor CMOS level outputs that drive either Darlingtons or PFETs.                                                                                                                                                                                                                                                    |  |

| OUTA, B, C   | 0    | Lower Driver Outputs. These three driver outputs drive external Bipolar or NFET power transistors to control the motor current through the current setting resistor Re. During normal operation, the drive voltages are adjusted as necessary to maintain the proper motor speed and drive current.                       |  |

| DACIN        | l    | Reference voltage for motor current.                                                                                                                                                                                                                                                                                      |  |

| DACOUT       | 0    | Summer Output (VDAC). The summation of integral and proportional channel voltages.                                                                                                                                                                                                                                        |  |

## **ELECTRICAL SPECIFICATIONS**

## **ABSOLUTE MAXIMUM RATINGS**

Maximum limits indicate where permanent device damage occurs. Continuous operation at these limits is not intended and should be limited to those conditions specified in the DC Operating Characteristics.

| RATING           | UNIT                                      |

|------------------|-------------------------------------------|

| -0.5 to +14V     | V                                         |

| -65 to +150      | °C                                        |

| 260              | °C                                        |

| 215              | °C                                        |

| -0.3 to VDD +0.3 | V                                         |

|                  | -0.5 to +14V<br>-65 to +150<br>260<br>215 |

## ELECTRICAL CHARACTERISTICS (Unless otherwise specified VIvdt <VDD<13.2V.)

| PARAMETER                        | CONDITIONS                            | MIN   | МОМ | MAX   | UNIT |

|----------------------------------|---------------------------------------|-------|-----|-------|------|

| VDD supply voltage               |                                       | 10.8  | 12  | 13.2  | ٧    |

| IDD supply current               | includes output driver current        | -     | 20  | 38    | mA   |

| PDD power dissipation            | loutA or B, or C = -10 mA             | -     | 240 | 375   | mW   |

|                                  | loutupA, or B, or $C = 10 \text{ mA}$ |       |     |       |      |

|                                  | IHALLOUT = -10 mA                     |       |     |       |      |

| FREF clock frequency             |                                       | 1.998 | 2   | 2.002 | MHz  |

| TA ambient temperature           |                                       | 0     | -   | 70    | °C   |

| TTL Inputs START, FREF           |                                       |       |     |       |      |

| VIL Input Low Voltage            | IIL ≤500 μA                           | -     | -   | 0.8   | ٧    |

| VIH Input High Voltage           | IIH ≤100 μA                           | 2.0   | •   | -     | ٧    |

| START Set-up time (Ts)           | FREF active to START 1                | 100   |     |       | μs   |

| MODE Input                       |                                       |       |     |       |      |

| VIL Input Low Voltage            |                                       | -     | -   | 0.5   | ٧    |

| VIH Input High Voltage           | IIH ≤500 μA                           | VDD5  | -   | -     | ٧    |

| HALLX Input                      |                                       |       |     |       |      |

| VIL Input Low Voltage            |                                       | -     | -   | 1.0   | ٧    |

| VIH Input High Voltage           | External pullup current ≤1.7 mA       | 3.0   | -   | -     | ٧    |

| Input Pullup-Pulldown Resistance |                                       |       |     |       |      |

| Internal pullup resistance       | START, FREF                           | 40    | -   | -     | kΩ   |

| Internal pullup resistance       | HALLX inputs                          | 5     | -   | 20    | kΩ   |

| Internal pulldown resistance     | MODE input                            | 40    | -   | -     | kΩ   |

| Input capacitance                | All inputs                            | -     | -   | 25    | pF   |

## **ELECTRICAL CHARACTERISTICS (Continued)**

| PARAMET                | TER                    | CONDITIONS                                 | MIN       | NOM       | MAX        | UNIT   |

|------------------------|------------------------|--------------------------------------------|-----------|-----------|------------|--------|

| SENSE In               | put                    |                                            |           |           |            |        |

| SENSE vo               | ltage threshold        | if exceeded, driver voltage is limited     | 0.9       | 1.0       | 1.1        | V      |

| Input curre            | ent                    |                                            | -100      | -         | +100       | μА     |

| Open Dra               | in Outputs LOCK, FA    | ULT                                        |           |           |            |        |

| VOL Outpo              | ut Low Voltage         | IOL = 2 mA                                 | -         | -         | 0.5        | V      |

| Typical ex             | ternal pullup resistor |                                            | -         | 10        |            | kΩ     |

| FAULT Inc              | dication               |                                            |           |           |            |        |

| VIvdt, low             | voltage                |                                            | 7.0       | -         | 9.5        | ٧      |

| Fmin, loss             | of FREF                |                                            | -         | -         | 100        | Hz     |

| Stuck moto             | or, start pulses       | drivers on, drivers off                    | -         | 0.90      | -          | sec    |

| Number of start pulses |                        |                                            | -         | 4         | -          | -      |

| Reverse shutdown speed |                        | START = 0                                  | -         | 281       | -          | rpm    |

| LOCK Indi              | ication                |                                            |           |           |            |        |

| Lock range             |                        | FREF = 2 MHz                               | 3594      | 3600      | 3607       | rpm    |

| Speed error            |                        | 10.8 < VDD < 13.2                          | -0.037    |           | +0.037     | %      |

| HALL Sen               | sor Interface          |                                            |           |           |            |        |

| HALLOUT                | bias voltage           | 10.8 < VDD < 13.2,<br>lload = -5 mA        | 5.0       |           | 6.8        | ٧      |

|                        |                        | 10.8 < VDD < 13.2,<br>lload = -10 mA       | 5.0       |           |            | V      |

| Driver Out             | tputs (FHALLX ≥ 100    | Hz, Vivdt < VDD $\leq$ 13.2, CL $\leq$ 500 | pF unless | otherwise | specified. | .)     |

| Slew rate              |                        | All driver outputs                         | 150       | -         | 500        | V/msec |

| OUTX                   | VOH                    | Iload = -7.5 mA                            | 3.75      | -         | -          | V      |

|                        | VOH                    | lload = -100 μA,<br>10.8 ≤ VDD ≤ 13.2      | 8.0       | -         | -          | ٧      |

|                        | VOL off state          | lload = 3.4mA,<br>5.0 ≤ VDD ≤ 13.2         | -         | -         | 0.5        | ٧      |

| OUTUPX                 | VOL                    | Iload = 10 mA                              | - 1       | -         | 3.0        | ٧      |

|                        | VOH off state          | Iload = -5 mA                              | VDD-0.5   | -         | -          | ٧      |

|                        | VOH off state          | lload = -2 mA,<br>5.0 ≤ VDD ≤ Vlvdt        | VDD-0.5   | -         | -          | V      |

## **APPLICATION INFORMATION**

| PARAMETER            | RECOMMENDED                         | MIN | NOM | MAX | UNIT |

|----------------------|-------------------------------------|-----|-----|-----|------|

| Power Transistors    |                                     |     | •   |     | -    |

| Power Darlington Vbe | Typical device: TIP 125,<br>TIP 120 | 0.8 | -   | 1.8 | V    |

| Power FET Vth        | Typical device: IRFT 001            | 2   | -   | 6   | ٧    |

| Power FET Rds (on)   |                                     | -   | -   | 0.4 | Ω    |

| Power FET BVds       |                                     | 30  | -   | -   | V    |

## R1, R2

| R1/(R1 + R2) | 0.02 | 0.2 | 1.0 |    |

|--------------|------|-----|-----|----|

| R1 + R2      | 20   | 50  | 200 | kΩ |

I running =

$$\frac{R1}{R1+R2} \cdot \frac{VDAC}{Re}$$

Where VDAC =  $Kp \cdot \Delta f + Ki \cdot \int \Delta f \cdot \Delta t$

Kp = Proportional constant = .213 V/rad/sec

Ki = Integral constant = 1.33 V/rad

$\Delta f = Frequency error$

#### **Motor Parameters**

The SSI 32M594 MSC is optimized for use with a wide range of Winchester motors including 3 1/2" motors. Torque Constant Range (KT) of 0.01 to 0.02 Nt - m/A and an Inertia Range (J) from 0.5 to 6.5 x 10<sup>-4</sup> Nt - m - sec  $^2$ . The choice of R1, R2 and Re will be affected by motor parameters, so some care in their selection is recommended.

#### **Control Loop Parameters**

The motor control loop consists of counter, logic, and digital-to-analog converters that provide loop time constants. The continuous time transfer function of the on-chip control can be modeled as follows:

$$H(s) = \frac{Vc(s)}{Fm(s)} = \frac{Ki}{s} + Kp$$

Vc(s) is the voltage applied to the external sense resistor (Re) by the modulator. By adjusting the value of Re, the gain the motor sees can be adjusted as can the starting current.

## Control Loop Parameters (Continued)

| PARAMETER                     | RECOMMENDED                     | MIN   | МОМ   | MAX   | UNIT    |

|-------------------------------|---------------------------------|-------|-------|-------|---------|

| Loop Bandwidth                | Nominal motor, Re = $0.4\Omega$ |       | 2     |       | Hz      |

| Loop Zero                     | Ki/Kp                           |       | 1.0   |       | Hz      |

| Kp, Proportional Channel Gain |                                 | 0.198 | 0.213 | 0.227 | V/rad/s |

| Ki, Integral Channel Gain     |                                 | 1.23  | 1.33  | 1.42  | V/rad   |

| Start current                 |                                 | 1.0   | 2.0   | 3.0   | Amps    |

| Running current               |                                 | 0.1   | 0.2   | 0.3   | Amps    |

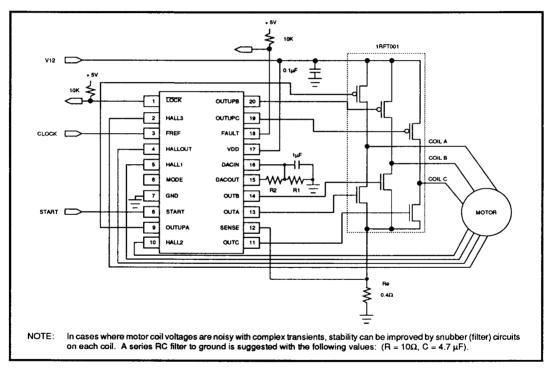

Typical Three-Phase, 4-Pole, Bipolar, Non-Center Tapped Motor using a Power FET Module

Typical Three-Phase, 8-Pole, Unipolar,

Center Tapped Motor using a Power Darlington. UENABLE must be tied to GND.

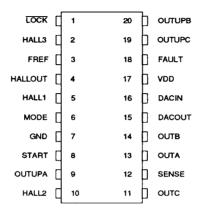

# PACKAGE PIN DESIGNATIONS

(TOP VIEW)

CAUTION: Use handling procedures necessary for a static sensitive component.

20-Pin PDIP or SOL

#### ORDERING INFORMATION

| PART DESCRIPTION                                    | ORDERING NUMBER | PACKAGE MARK |  |  |  |  |

|-----------------------------------------------------|-----------------|--------------|--|--|--|--|

| SSI 32M594 Three-Phase Delta Motor Speed Controller |                 |              |  |  |  |  |

| 20-Pin SOL 32M594-CL 32M594-CL                      |                 |              |  |  |  |  |

| 20-PIN PDIP                                         | 32M594-CP       | 32M594-CP    |  |  |  |  |

**Preliminary Data:** Indicates a product not completely released to production. The specifications are based on preliminary evaluations and are not guaranteed. Small quantities are available, and Silicon Systems should be consulted for current information.

No responsibility is assumed by Silicon Systems for use of this product nor for any infringements of patents and trademarks or other rights of third parties resulting from its use. No license is granted under any patents, patent rights or trademarks of Silicon Systems. Silicon Systems reserves the right to make changes in specifications at any time without notice. Accordingly, the reader is cautioned to verify that the data sheet is current before placing orders.

Silicon Systems, Inc. 14351 Myford Road, Tustin, CA 92680, (714) 731-7110, FAX (714) 573-6914

0790 - rev.

7-23

©1989 Silicon Systems, Inc.