# TECHNICAL MANUAL

Ethernet-110 Core

February 2001

Document Number DB14-000014-02, Second Edition (February 2001) This document describes LSI Logic Corporation's Ethernet-110 Core and will remain the official reference source for all revisions/releases of this product until rescinded by an update.

#### To receive product literature, visit us at http://www.lsilogic.com.

LSI Logic Corporation reserves the right to make changes to any products herein at any time without notice. LSI Logic does not assume any responsibility or liability arising out of the application or use of any product described herein, except as expressly agreed to in writing by LSI Logic; nor does the purchase or use of a product from LSI Logic convey a license under any patent rights, copyrights, trademark rights, or any other of the intellectual property rights of LSI Logic or third parties.

Copyright © 1996–2001 by LSI Logic Corporation. All rights reserved.

#### TRADEMARK ACKNOWLEDGMENT

LSI Logic logo design, CoreWare, and Right-First-Time are registered trademarks or trademarks of LSI Logic Corporation. All other brand and product names may be trademarks of their respective companies.

MΤ

# **Preface**

This manual is the primary reference for the Ethernet-110 (E-110) core, which includes the media access controller (MAC) core, the optional MAC control module core, the optional media independent interface management (MIIM) core, and the optional serial media independent interface (SMII) core. It contains a complete functional description for the E-110 core and includes complete physical and electrical specifications. The E-110 core is capable of operating at 10 or 100 Mbit/s for Ethernet and Fast Ethernet applications.

#### **Audience**

This manual assumes that you have some familiarity with Ethernet protocols and related support devices. It also assumes some familiarity with IEEE standards 802.3/802.3u and all applicable clauses describing 10 and 100 Mbit/s Ethernet operation. The people who benefit from this technical manual are:

- Engineers and managers who are evaluating the E-110 core for use in an ASIC application

- Engineers who are designing the E-110 core into an ASIC

# Organization

This document has the following chapters:

- Chapter 1, Introduction, provides an introduction to LSI Logic Corporation's E-110 core.

- Chapter 2, Signal Descriptions, provides a detailed description of each of the signals associated with the core.

Preface iii

- Chapter 3, Core Descriptions, describes the operation of the E-110 core.

- Chapter 4, Functional Timing, provides timing diagrams for the core.

- Chapter 5, Specifications, describes the AC timing and core inputs and outputs.

- Appendix A, Glossary, provides a list of terms used in this manual.

#### **Related Publications**

IEEE Standard 802.3, 10 Mbit/s Ethernet Specification

IEEE Standard 802.3u, 100BASE-T Fast Ethernet Specification

IEEE Standard 802.3x, 802.3 Full Duplex Operation Specification

Ethernet-10 (E-10) Core Technical Manual, LSI Logic Corporation, Order Number R14006

#### **Conventions Used in This Manual**

The first time a word or phrase is defined in this manual, it is *italicized*. See the glossary at the end of this manual for definitions of italicized words.

The word *assert* means to drive a signal true or active. The word *deassert* means to drive a signal false or inactive.

The following signal naming conventions are used throughout this manual:

- A level-significant signal that is true or valid when the signal is LOW always has a suffix of \_L attached to its name.

- An edge-significant signal that initiates actions on a HIGH-to-LOW transition always has a suffix of \_L attached to its name.

Hexadecimal numbers are indicated by the prefix "0x" before the number—for example, 0x32CF. Binary numbers are indicated by the prefix "0b," for example, 0b0011.0010.1100.1111.

# **Contents**

| Chapter 1 | Introduction                      |                            |                                       |      |  |

|-----------|-----------------------------------|----------------------------|---------------------------------------|------|--|

| ·         | 1.1 CoreWare <sup>®</sup> Program |                            |                                       | 1-1  |  |

|           | 1.2                               | Fast Ethernet (100 Mbit/s) |                                       | 1-3  |  |

|           |                                   | 1.2.1                      | Fast Ethernet Overview                | 1-3  |  |

|           |                                   | 1.2.2                      | Fast Ethernet Features                | 1-4  |  |

|           |                                   | 1.2.3                      | E-110 MAC Core and the OSI Model      | 1-6  |  |

|           |                                   | 1.2.4                      | Fast Ethernet Hubs                    | 1-7  |  |

|           |                                   | 1.2.5                      | Fast Ethernet Network Interface Cards | 1-10 |  |

|           | 1.3                               | VLAN                       | Support                               | 1-11 |  |

|           | 1.4                               | E-110 Core                 |                                       | 1-12 |  |

|           | 1.5                               | E-110                      | E-110 MAC Core                        |      |  |

|           |                                   | 1.5.1                      | MAC Core Host System Connection       | 1-13 |  |

|           |                                   | 1.5.2                      | MAC Multiple Channel Operation        | 1-18 |  |

|           |                                   | 1.5.3                      | MAC External Interfaces               | 1-19 |  |

|           |                                   | 1.5.4                      | MAC SMII/MII                          | 1-21 |  |

|           |                                   | 1.5.5                      | MAC Backoff Operation                 | 1-23 |  |

|           |                                   | 1.5.6                      | •                                     |      |  |

|           | 1.6                               | MAC Control Module Core    |                                       | 1-24 |  |

|           | 1.7                               | MIIM (                     | Core                                  | 1-25 |  |

|           | 1.8                               | SMII C                     | Core                                  | 1-26 |  |

| Chapter 2 | Signal Descriptions               |                            |                                       |      |  |

| -         | 2.1                               | MAC Core Signals           |                                       | 2-1  |  |

|           |                                   | 2.1.1                      | Transmit Function to Host Signals     | 2-3  |  |

|           |                                   | 2.1.2                      | Receive Function to Host Signals      | 2-5  |  |

|           |                                   | 2.1.3                      | MAC Control Module Signals (Optional) | 2-9  |  |

|           |                                   | 2.1.4                      | SMII/MII to PHY Signals               | 2-12 |  |

|           |                                   | 2.1.5                      | Host Control Signals                  | 2-15 |  |

|           |                                   | 2.1.6                      | Statistics Vector to Host Signals     | 2-24 |  |

Contents

|           |                   | 2.1.7   | Random Number Generator to Host Signals       | 2-30 |  |

|-----------|-------------------|---------|-----------------------------------------------|------|--|

|           |                   | 2.1.8   | Scan Test Signals                             | 2-31 |  |

|           | 2.2               | MAC C   | Control Module Signals                        | 2-31 |  |

|           |                   | 2.2.1   | MAC Control Module to E-110 Core Signals      | 2-32 |  |

|           |                   | 2.2.2   | MAC Control Module to PHY Signals             | 2-35 |  |

|           |                   | 2.2.3   | MAC Control Module to Host Signals            | 2-35 |  |

|           | 2.3               | MIIM C  | Core Signals                                  | 2-39 |  |

|           |                   | 2.3.1   | MIIM Core to Host Signals                     | 2-39 |  |

|           |                   | 2.3.2   | MIIM Core to PHY Signals                      | 2-43 |  |

|           | 2.4               | SMII C  | ore Signals                                   | 2-45 |  |

|           |                   | 2.4.1   | SMII Core to Host Signals                     | 2-45 |  |

|           |                   | 2.4.2   | SMII Core to MAC Signals                      | 2-47 |  |

|           |                   | 2.4.3   | SMII Core to PHY Signals for MII Operation    | 2-49 |  |

|           |                   | 2.4.4   | SMII Core to PHY Signals for SMII Operation   | 2-50 |  |

|           |                   | 2.4.5   | SMII Core to Clock Sources for SMII Operation | 2-51 |  |

| Chapter 3 | Core Descriptions |         |                                               |      |  |

|           | 3.1               | Clock ( | Operation                                     | 3-1  |  |

|           |                   | 3.1.1   | MTXC and MRXC                                 | 3-1  |  |

|           |                   | 3.1.2   | HCLK                                          | 3-3  |  |

|           |                   | 3.1.3   | MDC                                           | 3-3  |  |

|           | 3.2               | E-110   | Core Operation                                | 3-3  |  |

|           |                   | 3.2.1   | MAC Core Operation                            | 3-5  |  |

|           |                   | 3.2.2   | MAC Control Module Core Operation             | 3-17 |  |

|           |                   | 3.2.3   | MIIM Core Operation                           | 3-18 |  |

|           |                   | 3.2.4   | SMII Core Operation                           | 3-25 |  |

| Chapter 4 | Functional Timing |         |                                               |      |  |

|           | 4.1               | MAC F   | unctional Timing                              | 4-1  |  |

|           |                   | 4.1.1   | MAC Receive Packet Timing                     | 4-1  |  |

|           |                   | 4.1.2   | MAC Transmit Packet Timing                    | 4-4  |  |

|           | 4.2               | MIIM C  | Core Functional Timing                        | 4-7  |  |

|           |                   | 4.2.1   | MIIM Write Operation                          | 4-7  |  |

|           |                   | 4.2.2   | MAC MIIM Read Operation                       | 4-9  |  |

|           | 4.3               | Transm  | nit Collision Functional Timing               | 4-10 |  |

vi Contents

| Chapter 5  | Spec              | ifications                                |      |  |

|------------|-------------------|-------------------------------------------|------|--|

| •          | 5.1               | Derivation of AC Timing and Loading       | 5-1  |  |

|            | 5.2               | MAC Core AC Timing                        | 5-2  |  |

|            | 5.3               | MAC Core Pin Summary                      | 5-4  |  |

|            | 5.4               | MAC Control Module Core AC Timing         | 5-6  |  |

|            | 5.5               | MAC Control Module Core Pin Summary       | 5-8  |  |

|            | 5.6               | MIIM Core AC Timing                       | 5-10 |  |

|            | 5.7               | MIIM Core Pin Summary                     | 5-11 |  |

| Appendix A | Glossary          |                                           |      |  |

|            | Customer Feedback |                                           |      |  |

| Figures    |                   |                                           |      |  |

|            | 1.1               | 100BASE-T Media Specifications            | 1-6  |  |

|            | 1.2               | E-110 MAC Relationship to the OSI Model   | 1-7  |  |

|            | 1.3               | Hub Examples                              | 1-8  |  |

|            | 1.4               | Switched Hub Example                      | 1-10 |  |

|            | 1.5               | Network Interface Card Block Diagram      | 1-11 |  |

|            | 1.6               | E-110 ASIC Environment                    | 1-12 |  |

|            | 1.7               | E-110 MAC Host System Connection          | 1-14 |  |

|            | 1.8               | Centralized Statistics Updater            | 1-16 |  |

|            | 1.9               | Multiple Channel Application              | 1-19 |  |

|            | 1.10              | External Connections to the E-110 MAC     | 1-20 |  |

|            | 1.11              | MII Function                              | 1-22 |  |

|            | 1.12              | SMII Core (Optional)                      | 1-23 |  |

|            | 1.13              | MIIM Core                                 | 1-25 |  |

|            | 1.14              | SMII Core                                 | 1-26 |  |

|            | 2.1               | E-110 MAC Core Interface Diagram          | 2-2  |  |

|            | 2.2               | MAC Control Module Core Interface Diagram | 2-32 |  |

|            | 2.3               | MIIM Core Interface Diagram               | 2-39 |  |

|            | 2.4               | SMII Core Interface Diagram               | 2-45 |  |

|            | 3.1               | Overall Block Diagram                     | 3-4  |  |

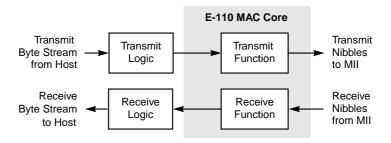

|            | 3.2               | Transmit and Receive Functions            | 3-5  |  |

|            | 3.3               | Transmit Function Interface               | 3-5  |  |

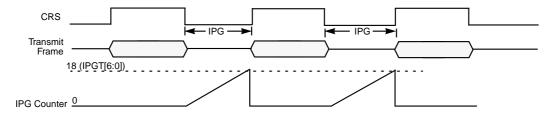

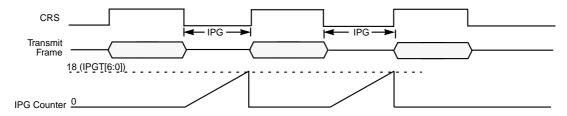

|            | 3.4               | Half-Duplex Back-to-Back IPG Operation    | 3-8  |  |

Contents vii

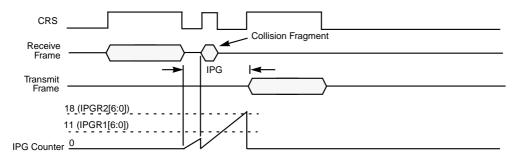

|        | 3.5  | Half-Duplex Non-Back-to-Back IPG Operation        | 3-8  |

|--------|------|---------------------------------------------------|------|

|        | 3.6  | Full-Duplex Back-to-Back IPG Operation            | 3-9  |

|        | 3.7  | Full-Duplex Non-Back-to-Back IPG Operation        | 3-9  |

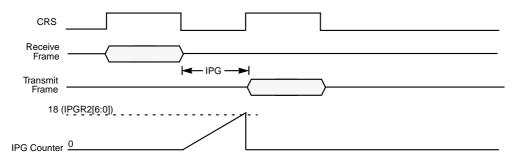

|        | 3.8  | Receive Function Interface                        | 3-14 |

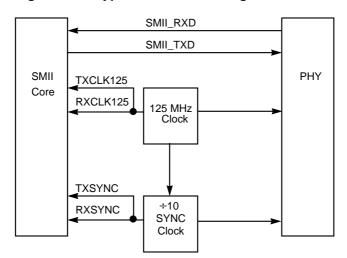

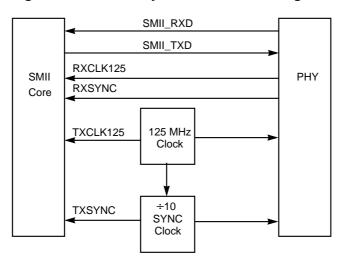

|        | 3.9  | Typical SMII Block Diagram                        | 3-26 |

|        | 3.10 | Source Synchronous Block Diagram                  | 3-27 |

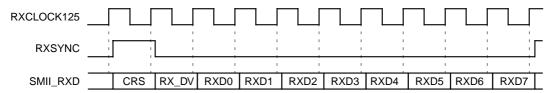

|        | 3.11 | Typical SMII Receive Data Timing                  | 3-28 |

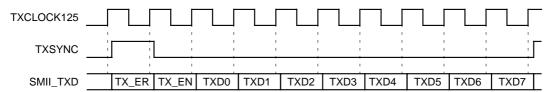

|        | 3.12 | Typical SMII Transmit Data Timing                 | 3-30 |

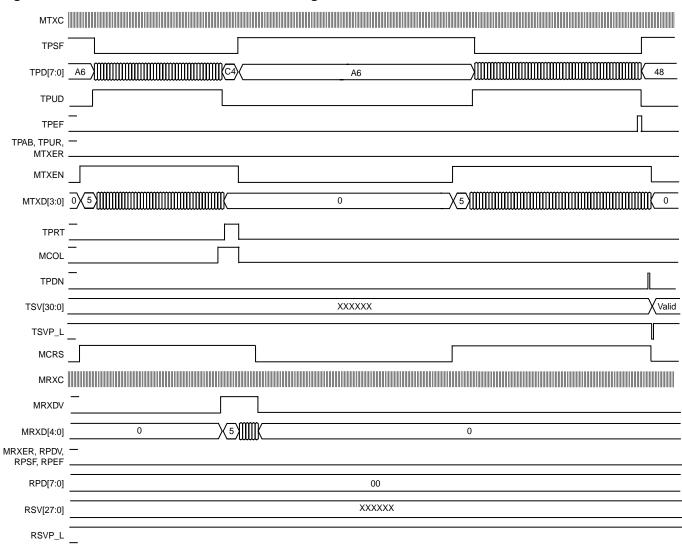

|        | 4.1  | E-110 MAC Receive Packet Timing                   | 4-2  |

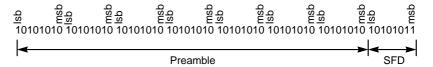

|        | 4.2  | Packet Preamble and SFD                           | 4-3  |

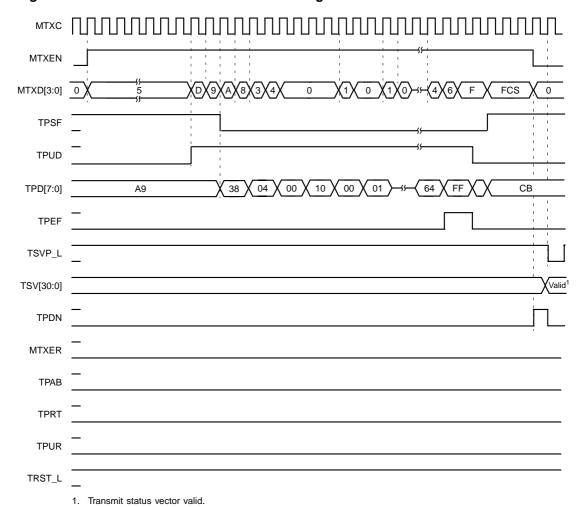

|        | 4.3  | E-110 MAC Transmit Packet Timing                  | 4-5  |

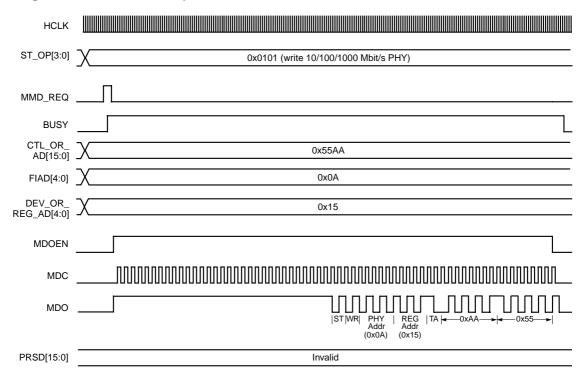

|        | 4.4  | MIIM Write Operation                              | 4-7  |

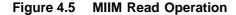

|        | 4.5  | MIIM Read Operation                               | 4-9  |

|        | 4.6  | Transmit Collision Functional Timing              | 4-11 |

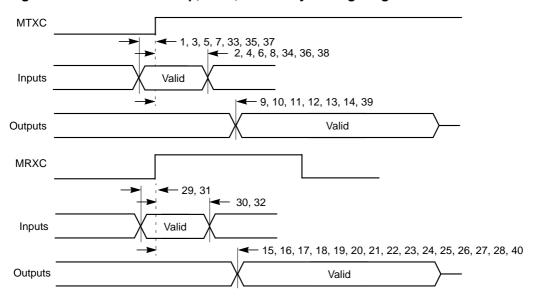

|        | 5.1  | MAC Core Setup, Hold, and Delay Timing Diagram    | 5-2  |

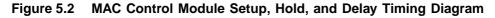

|        | 5.2  | MAC Control Module Setup, Hold, and Delay         |      |

|        |      | Timing Diagram                                    | 5-7  |

|        | 5.3  | MIIM Core Setup, Hold, and Delay Timing Diagram   | 5-10 |

| Tables |      |                                                   |      |

|        | 1.1  | 10BASE-T Ethernet vs. 100BASE-T Fast Ethernet     | 1-5  |

|        | 2.1  | Transmission Retry Algorithm for BKOFF_LIMIT[1:0] |      |

|        |      | (Maximum $k = 10, 8, 4, 1$ )                      | 2-18 |

|        | 3.1  | MIIM Register Set for 10/100/1000 Mbit/s PHYs     | 3-19 |

|        | 3.2  | PHY Control Register Bit Definitions              | 3-20 |

|        | 3.3  | PHY Status Register Bit Definitions               | 3-23 |

|        | 3.4  | Source Synchronous Clock and Synchronization      | 3-26 |

|        | 3.5  | SMII_RXD[7:0] Meaning                             | 3-28 |

|        | 3.6  | SMII_TXD[7:0] Meaning                             | 3-31 |

|        | 5.1  | MAC Core AC Timing Parameters                     | 5-3  |

|        | 5.2  | MAC Core Pin Summary                              | 5-4  |

|        | 5.3  | MAC Control Module AC Timing Parameters           | 5-7  |

|        | 5.4  | MAC Control Module Pin Summary                    | 5-8  |

|        | 5.5  | MIIM Core AC Timing Parameters                    | 5-10 |

|        | 5.6  | MIIM Core Pin Summary                             | 5-11 |

viii Contents

# Chapter 1 Introduction

This chapter describes the overall functions of the E-110 core. It contains the following sections:

- Section 1.1, "CoreWare® Program," page 1-1

- Section 1.2, "Fast Ethernet (100 Mbit/s)," page 1-3

- Section 1.3, "VLAN Support," page 1-11

- Section 1.4, "E-110 Core," page 1-12

- Section 1.5, "E-110 MAC Core," page 1-13

- Section 1.6, "MAC Control Module Core," page 1-24

- Section 1.7, "MIIM Core," page 1-25

- Section 1.8, "SMII Core," page 1-26

# 1.1 CoreWare® Program

An LSI Logic core is a fully defined and reusable block of logic. It supports industry-standard functions, and has predefined timing and layout. Every core possesses significant intellectual property value that comes from the construction, optimization, and productization of a particular function.

Through the CoreWare program, you can create systems on a chip uniquely suited to your applications. The CoreWare library contains a wide range of complex cores targeting the communications, consumer, and computer markets. The library consists of MIPS microprocessor cores, high-speed interconnect cores, MPEG-2 decoder cores, PCI cores, and many more.

The CoreWare library also includes megafunctions and building blocks, which provide useful functions for developing a system on a chip.

Each core has an associated set of deliverables, including:

- RTL simulation models for the Verilog HDL environment

- Structural simulation models for Verilog HDL and VHDL environments

- A system verification environment (SVE)<sup>1</sup> for RTL-based Verilog simulation

- A test vector suite

Because your design requirements are unique, LSI Logic is flexible in working with you to develop your system-on-a-chip CoreWare design. Three different working relationships are available:

- You provide LSI Logic with a detailed specification and LSI Logic does all of the design.

- You design some functions while LSI Logic provides you with the cores and megafunctions, and LSI Logic completes the integration.

- LSI Logic provides you with the cores, megafunctions, and development tools for you to do the entire design and integration.

Whatever the work relationship, the LSI Logic advanced CoreWare methodology and ASIC process technologies consistently produce Right-First-Time™ silicon.

<sup>1.</sup> The SVE provides a software environment for verifying core functionality.

# 1.2 Fast Ethernet (100 Mbit/s)

The E-110 core is a 100BASE-T *Fast Ethernet* solution. 100BASE-T is one of a number of technologies that provide greater bandwidth and improved client/server response times. The 100BASE-T standard is designed to provide a smooth evolution from 10BASE-T Ethernet—the dominant 10 Mbit/s network used today—to high-speed 100 Mbit/s performance.

#### 1.2.1 Fast Ethernet Overview

The Fast Ethernet standard for 100BASE-T has been established by the *IEEE 802.3* committee, the same committee that developed the original Ethernet standard. The 100BASE-T standard is found in the *IEEE 802.3u* specification, which serves as a supplement to the 802.3 standard and extends the operating speed to 100 Mbit/s.

100BASE-T Fast Ethernet is an extension of 10BASE-T technology. This technology uses the existing 802.3 media access control (MAC) layer (layer 2), connected through a media-independent interface (MII) or serial media-independent interface (SMII) to a physical layer device (PHY).

The SMII/MII specification is analogous to the 10 Mbit/s Ethernet attachment unit interface (AUI)—it provides a single interface that can support external transceivers for any of the 100BASE-T media specifications. In the Fast Ethernet MAC, the bit time (the time to transmit one bit of data) has been reduced by a factor of 10, thereby increasing packet speed to ten times that of 10BASE-T, while packet format and length, error control, and management information remain identical to 10BASE-T.

The 100BASE-T standard supports three PHY layers:

- 100BASE-TX (see IEEE 802.3u, clauses 24 and 25)

- 100BASE-T4 (see IEEE 802.3u, clause 23)

- 100BASE-FX (see IEEE 802.3u, clauses 24 and 26)

The 100BASE-X standard outlined in the IEEE 802.3u specification embodies the 100BASE-TX and 100BASE-FX standards. The term 100BASE-X is used when referring to the physical coding sublayer (PCS)

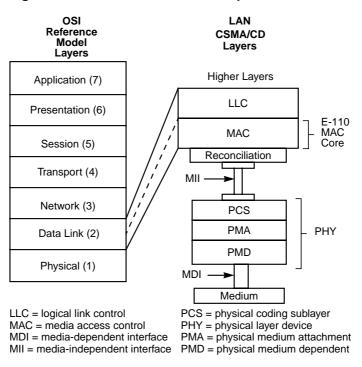

and physical medium attachment (PMA), which are common to both 100BASE-TX and 100BASE-FX. See Figure 1.2 on page 1-7.

The physical medium dependent (PMD) issues are different for 100BASE-TX and 100BASE-FX, and are described in separate sections of the IEEE 802.3u specification. The 100BASE-T4 standard is unique from 100BASE-TX and 100BASE-FX and is described in its own section of the IEEE 802.3u specification.

The 100BASE-T standard also defines a universal *hub* interface and a management interface.

The cable and fiber types currently used in 100BASE-T networks are:

- 100BASE-TX— a two-pair system for data grade (EIA 568

Category 5) unshielded twisted-pair (UTP) and 150 Ω shielded twisted-pair (STP) cabling

- 100BASE-T4—a four-pair system for both voice and data grade (Category 3, 4, or 5) UTP cabling

- 100BASE-FX— two multimode fibers

Additionally, the 100BASE-TX, 100BASE-T4, and 100BASE-FX systems can be mixed and interconnected through a hub.

### 1.2.2 Fast Ethernet Features

The key advantages of Fast Ethernet:

- Proven technology with speed increased by a factor of 10

- Simple migration from 10 Mbit/s to 100 Mbit/s networks

- Extensive multivendor support

#### 1.2.2.1 10BASE-T to 100BASE-T Comparison

Fast Ethernet, in the form of 100BASE-T technology, is really very similar to 10BASE-T, but is ten times faster. Unlike other high-speed technologies, Ethernet has been installed for over 20 years in business, government, and educational networks. Table 1.1 is a comparison between 10BASE-T and 100BASE-T.

Table 1.1 10BASE-T Ethernet vs. 100BASE-T Fast Ethernet

| Function                                          | Ethernet               | Fast Ethernet               |

|---------------------------------------------------|------------------------|-----------------------------|

| Speed                                             | 10 Mbit/s              | 100 Mbit/s                  |

| IEEE Standard                                     | 802.3                  | 802.3u                      |

| Media Access Protocol                             | CSMA/CD                | CSMA/CD                     |

| Topology                                          | Bus or Star            | Star                        |

| Cable Support                                     | Coax, UTP, Fiber       | UTP, Fiber                  |

| UTP <sup>1</sup> Cable Support                    | Category 3, 4, or 5    | Category 3, 4, or 5         |

| UTP Link Distance (max)                           | 100 Meters             | 100 Meters                  |

| Collision Domain Diameter (maximum with all UTP)  | 500 Meters             | 205 Meters                  |

| Maximum Network Diameter (using switches/routers) | Unlimited              | Unlimited                   |

| Media Independent Interface                       | Yes (AUI) <sup>2</sup> | Yes (SMII/MII) <sup>3</sup> |

| Full Duplex Capable                               | Yes                    | Yes                         |

- 1. UTP = unshielded twisted pair

- 2. AUI = auxiliary unit interface

- 3. SMII = serial media independent interface, MII = media independent interface

#### 1.2.2.2 CSMA/CD Transmission Protocol

Ethernet's fundamental transmission protocol is *Carrier Sense Multiple Access with Collision Detection (CSMA/CD)*. Fast Ethernet maintains this protocol, which allows it to move data between 10BASE-T and 100BASE-T stations on a *local area network (LAN)* without requiring protocol translation. A simple, low-cost *switching hub* or *bridge* is all that is required for connection. Because it is the same technology (but faster), 100BASE-T can be successfully integrated into 10BASE-T networks to form a reliable migration path to 100BASE-T networks.

#### 1.2.2.3 Media Specifications

A major advantage of Fast Ethernet over other high-performance technologies is that it can be deployed as a switching or shared technology. 100BASE-T networks are based on a combination of switching and shared hubs in order to maintain existing 10BASE-T infrastructures. 100BASE-T networks are capable of full-duplex operation.

100BASE-T combines the scaled MAC with a variety of media specifications to provide users with the maximum possible wiring flexibility, as shown in Figure 1.1. The media specifications (100BASE-TX, 100BASE-T4, and 100BASE-FX) are collectively referred to as 100BASE-T and enable users to retain their existing cabling infrastructure while migrating to Fast Ethernet.

10 Mbit/s Ethernet 100 Mbit/s Fast Ethernet CSMA/CD CSMA/CD Scaled by 10X MAC MAC Two-Pair Thick Coax Thin Coax Fiber UTP. STP (10BASE2) (10BASE5) (100BASE-FX) (100BASE-TX) Four-Pair UTP (100BASE-T4) Fiber Twisted-Pair (10BASE-F) (10BASE-T) 100BASE-T

Figure 1.1 100BASE-T Media Specifications

### 1.2.3 E-110 MAC Core and the OSI Model

Figure 1.2 shows how the E-110 MAC fits into the ISO Open Systems Interconnection (OSI) Reference model. The OSI model defines a data communications protocol consisting of seven distinct layers.

Figure 1.2 E-110 MAC Relationship to the OSI Model

Overviews of the operation of the MAC core, MAC control module core, and the MIIM core are found later in this chapter.

## 1.2.4 Fast Ethernet Hubs

A hub is a common wiring point for star-topology networks, and can perform various functions, such as switching, statistics gathering, and signal retiming.

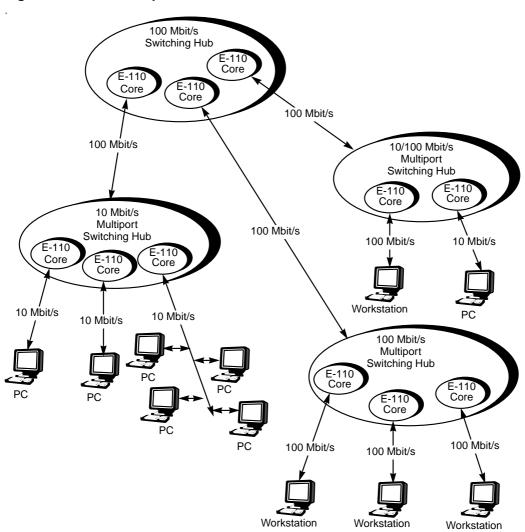

The E-110 core provides a high-integration solution to hub design because several cores may be placed on a single ASIC. Figure 1.3 illustrates how hubs might be configured using the E-110 core.

Figure 1.3 Hub Examples

A switching hub facilitates packet switching. Each port of a packet switching hub provides a connection to an Ethernet media system that operates as a separate *Ethernet LAN*. Unlike a repeater hub whose individual ports combine segments together to create a single large LAN, a switching hub makes it possible to divide a set of Ethernet media systems into multiple LANs that are linked together by way of the packet switching electronics in the hub. The round trip timing rules for each LAN stop at the switching hub port, allowing you to link a large number of

individual Ethernet LANs together. A given Ethernet LAN can consist of a single cable segment linking some number of computers, or it may consist of a repeater hub linking several such media segments together. Whole Ethernet LANs can themselves be linked together to form extended network systems using packet switching hubs. While an individual Ethernet LAN may typically support anywhere from a few up to several dozen computers, the total system of Ethernet LANs linked with packet switches at a given site may support many hundreds or thousands of machines.

A switching hub can be designed with an intelligent switching fabric and multiple E-110 cores. The switching may be done in any of the following manners:

- Cut-Through—the head of the frame leaves the switch before the tail

has arrived. You use an address compare buffer to decode the

destination address.

- Store and Forward–the entire frame is received and buffered before being forwarded to an output port.

- Adaptive Cut-Through—the hub looks at collision statistics. If too

many collisions occur, the hub changes from cut-through operation

to store and forward operation.

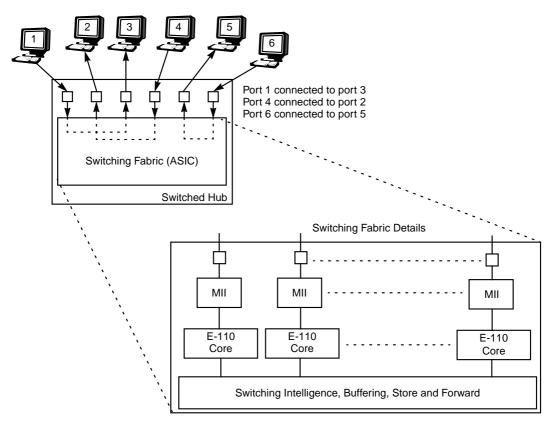

Figure 1.4 shows where the E-110 core fits in a switched hub.

Figure 1.4 Switched Hub Example

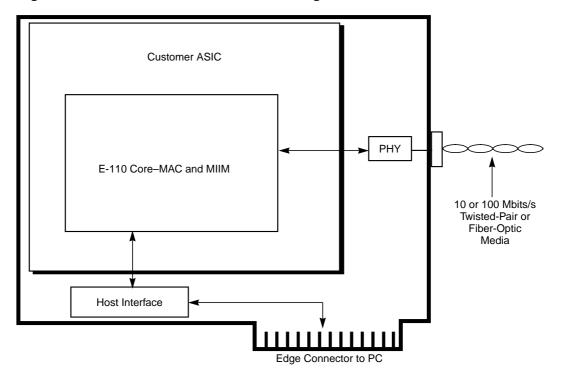

# 1.2.5 Fast Ethernet Network Interface Cards

Network cards can be designed with the E-110 core that will run at speeds of 10 or 100 Mbits/s. Figure 1.5 shows how the E-110 core fits into a network interface card (NIC). The E-110 core provides the MAC function and interfaces with 10 Mbit/s or 100 Mbit/s PHYs for single- or multipoint server solutions.

Figure 1.5 Network Interface Card Block Diagram

# 1.3 VLAN Support

The E-110 core supports Virtual Local Area Network (VLAN) operation. It is compatible with the provisions of the IEEE 802.3ac-1998 specification, which defines the MAC frame extensions for virtual bridged local area network (VLAN) tagging on 802.3 networks. The IEEE P802.1Q specification is the full VLAN document.

VLAN Support 1-11

# 1.4 E-110 Core

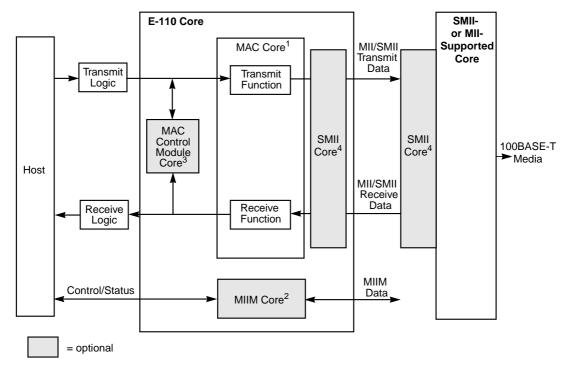

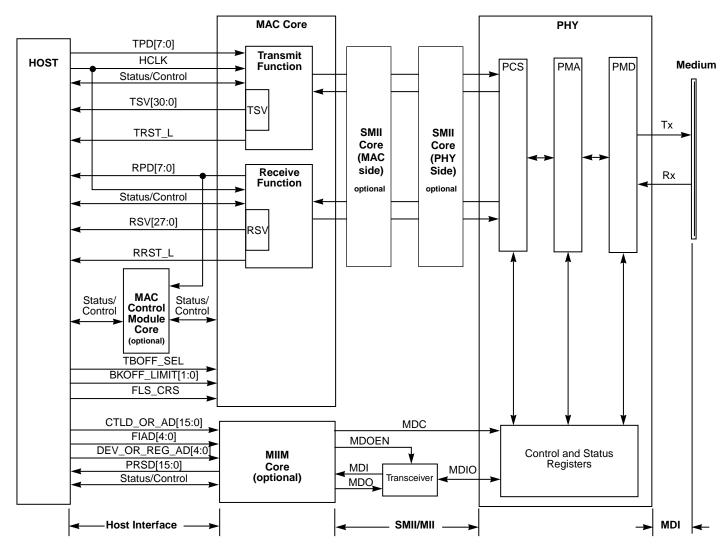

As shown in Figure 1.6, the E-110 core contains the following cores:

- MAC

- MAC Control Module (optional)

- MIIM (optional)

- SMII (optional)

Figure 1.6 E-110 ASIC Environment

- 1. The MAC is capable of 10 or 100 Mbit/s operation.

- 2. An optional MIIM core reads PHY status registers and writes PHY control registers.

- 3. An optional MAC control module core provides the flow control functions.

- 4. An optional SMII module provides a serial MII interface to a PHY with a compatible interface.

The MAC<sup>1</sup> core operates at 10 or 100 Mbits/s using an external PHY. An optional MAC control module core located external to the E-110 core allows the host to perform the flow control functions given in the IEEE 802.3/802.3u standard. An optional MIIM core allows a host to communicate with the control and status registers within an MII-supported PHY.

### 1.5 E-110 MAC Core

The E-110 MAC core consists of the transmit and receive functions.

The transmit and receive functions transport data between the MAC function's host interface and the SMII/MII. Data consists of bytes on the host side and nibbles on the MII side. The host provides some data buffering and logic to manage properly the receive and transmit data streams. The SMII/MII is a logical data interface only. The user must provide line drivers and receivers to meet cable interface or attachment unit interface requirements.

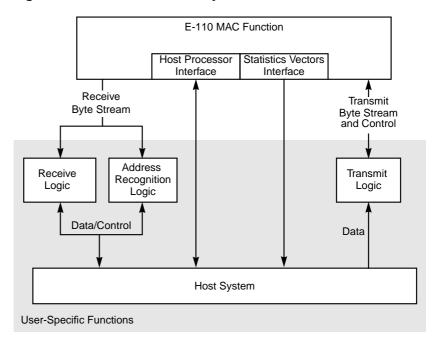

# 1.5.1 MAC Core Host System Connection

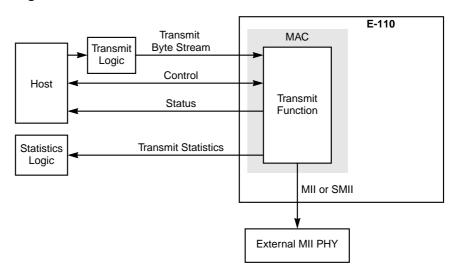

The E-110 MAC core is connected to a host system as shown in Figure 1.7. The following host connections are explained in this section:

- System Data Flow

- Statistics Vectors Interface

- Host Processor Interface

E-110 MAC Core 1-13

<sup>1.</sup> The MAC function meets the requirements of the IEEE 802.3u specification.

Figure 1.7 E-110 MAC Host System Connection

## 1.5.1.1 System Data Flow

The E-110 MAC operates at either 10 or 100 Mbits/s between an SMII/MII on one side and a host on the other. The receive and transmit data streams are independent from each other on both sides of the MAC.

The receive byte stream from the E-110 MAC operates on the SMII/MII receive clock. Another element of the overall system may assemble bytes from the receive byte stream into words for storage in a buffer memory or transmission to a system bus. Alternatively, the receive byte stream might enter directly into a FIFO. The output of the FIFO could then be interfaced into the overall system in a variety of ways, possibly using a common system clock.

The transmit byte stream for the E-110 MAC operates on the SMII/MII transmit clock. Another element of the overall system may disassemble words read from a buffer memory or received from a system bus into bytes for the transmit byte stream. Alternatively, the transmit byte stream might exit directly from a FIFO. The input of the FIFO could then be fed

from the overall system in a variety of ways, possibly using a common system clock.

Logic associated with the transmit and receive byte streams handles the packet and data flow control between the overall system and the E-110 MAC. Specifically, a device external to the E-110 MAC must monitor the receive byte stream to perform receive address recognition.

Details of the receive byte stream interface can be found in Section 3.2.1.2, "MAC Receive Function," on page 3-13. An explanation of the transmit byte stream interface can be found in Section 3.2.1.1, "MAC Transmit Function," on page 3-5. E-110 MAC behavior can be altered with external control signals. A description of the control signals is given in Chapter 2.

#### 1.5.1.2 Statistics Vectors Interface

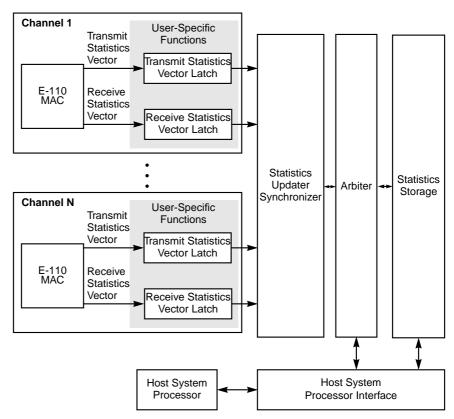

The E-110 MAC collects packet-by-packet statistics, but does not include statistics event counters or accumulating byte counters. Statistics for management purposes are collected outside the E-110 MAC for either end station or multiple channel applications.

Figure 1.8 shows how a centralized statistics collector for use with multiple E-110 MACs might be constructed.

E-110 MAC Core 1-15

Figure 1.8 Centralized Statistics Updater

Whenever the E-110 MAC receive and transmit functions complete the processing of a packet, the MAC creates a transmit or a receive statistics vector that may be latched external to the MAC function for use by the statistics updating process. Because the vector is latched, the receive and transmit functions do not hold the statistics vectors indefinitely. It then becomes the responsibility of the host to free up enough statistics storage space before the MAC overwrites the vectors with those for the next processed packet.

When the MAC latches the receive and transmit statistics vectors, the MAC provides synchronized latching signals for each of the transmit and receive vectors. The vectors include Packet Length bits that specify the length of the packet in bytes. In the example block diagram of Figure 1.8, the Statistics Updater Synchronizer feeds the Arbiter, which schedules the updating of statistics in the Statistics Storage. The statistics subsystem usually operates on the host system microprocessor clock,

which means that accesses to the statistics storage by the host are automatically synchronized. However, the transmit and receive statistics vector latch pulse must be synchronized to the host system clock because the transmit and receive functions operate on their own clocks.

#### 1.5.1.3 Host Processor Interface

The host system processor has the following connections to the E-110 MAC:

- MII Data Interface (or optional SMII Data Interface)

- Random Number Generator Interface

- Control Interface

- Statistics Interface

**MII Data Interface** – The E-110 MAC sends and receives data to the MII-supported PHY by means of the MII or optional SMII Transmit Data and Receive Data signal lines, over which the MAC passes transmit and receive nibbles.

Random Number Generator Interface – The E-110 MAC contains a random number generator that is used for transmit *backoff* in the event of a collision. The host may optionally load an 11-bit seed value into the random number generator. By loading different seed values into each E-110 MAC in a multiple-MAC system, you can guarantee that the backoff timers in each MAC are not synchronized to each other, which avoids the problem of two or more MACs colliding repeatedly while attempting to transmit. If you do not load a seed value in the random number generator, there is a chance that two MACs might have the same backoff timer value.

**Control Interface** – The host control interface allows the host to directly control the operation of the E-110 MAC. The host must provide either a 25 or 33 MHz clock (HCLK) to the core. The core uses the clock select (CLKS) input signal from the host to determine how to divide HCLK to create the MIIM Data Clock (MDC) signal. The host provides a variety of control signals to the MAC function to control the following:

Interpacket gaps (see Section 3.2.1.1, "MAC Transmit Function," and the signal descriptions for IPGR1[6:0], IPGR2[6:0], and IPGT[6:0] in Chapter 2).

E-110 MAC Core 1-17

- Padding of packets (see the subsection entitled "IPG Full-Duplex Operation" and the signal descriptions for NOPRE and PADEN in Chapter 2).

- Preamble (see the subsection entitled "IPG Full-Duplex Operation" and the signal description for NOPRE in Chapter 2).

- Full duplex operation (see the subsection entitled "IPG Full-Duplex Operation" the signal description for FULLD under Section 2.1.4, "SMII/MII to PHY Signals," and the signal description for FULLD in Chapter 2).

- Frame check sequence (FCS) checking (see the subsection entitled "IPG Full-Duplex Operation" Section 3.2.1.2, "MAC Receive Function," the subsection entitled "Receive Function to Host Interface" and the signal descriptions for CRCO[9:1], CRCG, CRCEN, and NOPRE in Chapter 2).

- Maximum packet length (see the subsection entitled "IPG Full-Duplex Operation" Section 3.2.1.2, "MAC Receive Function," and the signal description for HUGEN in Chapter 2).

- Late collisions (see the subsection entitled "IPG Full-Duplex Operation" and the signal description for TPAB and RTRYL in Chapter 2).

- 10 or 100 Mbit/s operation (see Table 3.2).

**Statistics Interface** – The E-110 MAC function provides receive and transmit statistics data that can be latched by a device external to the function and then read by the host. The MAC function provides the information on a parallel interface along with strobe signals.

# 1.5.2 MAC Multiple Channel Operation

While the E-110 MAC function can be used in a single-channel environment as shown in Figure 1.6, the same design can also be used for multiple channel applications as shown in Figure 1.9.

MII PHY E-110 MAC MII E-110 MAC PHY MII E-110 MAC PHY MII E-110 MAC PHY Common Functions<sup>1</sup> MII E-110 MAC PHY MII E-110 MAC PHY MII PHY E-110 MAC MII E-110 MAC PHY Common Host Interface

Figure 1.9 Multiple Channel Application

1. Data transport, address recognition, and statistics collection.

The exact nature of the common sections in Figure 1.9 is highly application dependent. The SMII/MII signal lines are only logical implementations without the line driving capability.

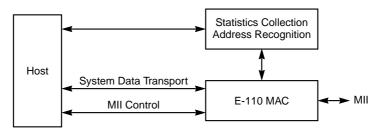

#### 1.5.3 MAC External Interfaces

The E-110 MAC operates at either 10 Mbits/s or 100 Mbits/s between an SMII/MII on one side and a system data transport on the other. The system designer can design the E-110 MAC into both end station, switch, and hub environments. For system efficiency in multiple MAC situations, you may provide a module external to the MAC function to collect statistics on MAC events and perform receive packet address recognition. Statistics collection and receive packet address recognition are customer defined for use with the E-110 MAC. Figure 1.10 illustrates the connections to the E-110 MAC function.

E-110 MAC Core 1-19

Figure 1.10 External Connections to the E-110 MAC

For simplicity of application, all per packet interactions (for example, start of frame and end of frame) between the E-110 MAC and the system take place through the system data transport. Using the system data transport eliminates the need for involvement of a processor at 100 Mbits/s because the E-110 MAC takes over the per packet data transfer responsibility.

The E-110 MAC conforms to existing IEEE 802.3 standards for 10 Mbit/s operation and IEEE 802.3u standards for 100 Mbit/s operation. It is expected that a common application of the E-110 MAC will be as a part of a larger system in user-specific ASICs. The E-110 MAC therefore imposes very little system personality regarding word size, byte order, data flow methodology, or management conventions. Alternatively, the E-110 MAC can be combined with a minimum of logic circuitry connected to off-chip interfaces to configure a unique MAC device.

To allow for a variety of network media types and methods of connection to the media, the SMII/MII standard has been adopted for the E-110 MAC. The E-110 MAC uses the SMII/MII on a logical basis only. Any implementation of the E-110 MAC can be used to connect copper wire or fiber media by means of a PHY. The PHY can reside either within the same ASIC as the E-110 MAC or external to the ASIC, as long as the PHY interface to the E-110 MAC is SMII/MII-compatible.

The E-110 MAC function transmits and receives nibbles of data to and from the media over the SMII/MII signal lines. The function handles independent receive and transmit byte streams between SMII/MII devices and the host. On the host side of the E-110 MAC, the byte streams can be directed into a system memory or bus structure in a variety of ways, such as shared or separate DMA channels or direct access to multiple port memories and FIFOs. The byte streams can also be assembled into system words as desired.

Management statistics collection is not included in the E-110 MAC. To facilitate statistics collection, the MAC function incorporates statistics vector circuitry to simplify the accumulation of event statistics. If statistics collection logic is desired, internal or external to the ASIC, it must be designed and implemented by the end user.

To allow for simple end station and complex switching hub environments, you may add receive packet address recognition logic external to the MAC function. LSI Logic does not supply the address recognition logic. For end station applications, a simple single station address comparison module can be attached to the receive byte stream. A *hashing multicast* capability can also be included in this module to detect sets of destination addresses. For switching hub applications, a central source and destination address filter block is often the preferred solution. The E-110 MAC function transmit and receive byte streams can interact with such a block.

### 1.5.4 MAC SMII/MII

The E-110 MAC operates with the MII or optional SMII signal lines connecting to physical media interface (PHY) devices. The SMII/MII is a logical data interface only. The designer must provide line drivers and receivers to meet cable interface or AUI requirements.

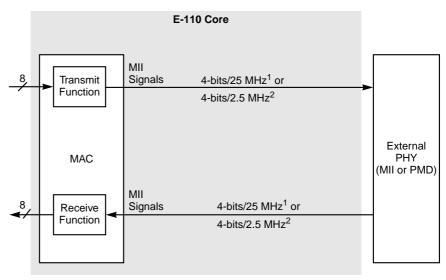

Figure 1.11 shows that a processor can control a PHY through an E-110 MAC that incorporates an MII function.

E-110 MAC Core 1-21

Figure 1.11 MII Function

#### Notes:

- 1. 4-bits/25 MHz means that the data path is 4-bits wide (a nibble) and that the clock rate is 25 MHz, which yields 100 Mbits/s

- 2. 4-bits/2.5 MHz means that the data path is 4-bits wide (a nibble) and that the clock rate is 2.5 MHz, which yields 10 Mbits/s

As new MII PHYs become available, they can be attached to the E-110 MAC, providing increased capability at both 10 Mbits/s and 100 Mbits/s. You can continue to interface to the PHYs by means of the E-110 MAC's built-in MII function.

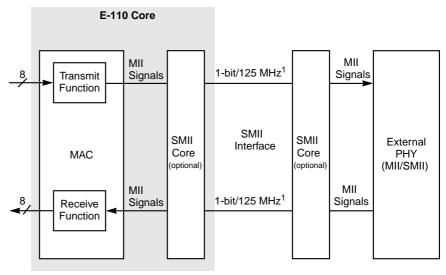

Figure 1.12 shows that a processor can control a PHY through an E-110 MAC that incorporates an optional SMII core.

Figure 1.12 SMII Core (Optional)

#### Notes:

1. The SMII interface operates at a clock rate of 125 MHz for both the 10 Mbit/s and 100 Mbit/s modes. Transmit and receive operations consist of 10-bit segments (2 control bits and 8 data bits). In 10 Mbit/s mode, each 10-bit segment repeats 10 times and the MAC can sample any of the 10 segments. In 100 Mbit/s mode, there is a single 10-bit segment transferred.

# 1.5.5 MAC Backoff Operation

When a data collision occurs, the MAC must perform a backoff operation, which causes the MAC to wait for a time and then try retransmitting. The MAC implements two selectable backoff methods:

- Stop Backoff

- Truncate Backoff

## 1.5.5.1 Stop Backoff

The Stop Backoff feature is implemented with the TBOFF\_SEL input pin. The TBOFF\_SEL input, driven by the host, controls whether the E-110 core uses the Binary Exponential Backoff algorithm during collisions. See Chapter 2 for a detailed signal description.

The stop backoff implementation does not conform to the IEEE 802.3/802.3u standard, but may be useful for test purposes.

E-110 MAC Core 1-23

#### 1.5.5.2 Truncate Backoff

The truncate backoff feature is implemented with the BKOFF\_LIMIT[1:0] input pins, which are driven by the host. The truncate backoff feature gives the user some flexibility in achieving a performance advantage in some native applications. With the truncate backoff feature, the E-110 core can be configured for either more or less aggressive backoff behavior, depending on the user's choice. See Chapter 2, for a detailed signal description.

# 1.5.6 MAC Backpressure Feature

The MAC core implements a backpressure feature, which is implemented with the False Carrier Sense (FLS\_CRS) input pin. The pin is driven by the host, and is applicable when the E-110 MAC core is used in a half-duplex switched port design.

When using a switch (rather than a repeater) as the hub for an Ethernet LAN, it is possible for traffic to arrive at a switched port faster than the switch is able to transmit the traffic out to the target destination port. Making the channel appear busy to the transmitter is an effective and efficient way of stopping the transmitter from flooding the receiver's buffers. The use of the FLS\_CRS signal is especially clean when only one end station is connected to each switch port—in these cases, FLS\_CRS throttles the end station as needed.

See Chapter 2, for a detailed signal description of the FLS\_CRS signal.

# 1.6 MAC Control Module Core

The MAC control module is an optional core that interfaces the E-110 core to the host and implements full-duplex flow control.

In full-duplex Ethernet, neither False Carrier Sense nor forced collision algorithms solve congestion control problems. A full-duplex Ethernet station does not implement *collision detection* and ignores Carrier Sense for deferring transmissions. A full-duplex Ethernet implementation therefore requires an explicit flow control mechanism to allow a switch to throttle a congesting end station. Clause 31 in the IEEE 802.3/802.3u standard defines the frame-based flow control scheme implemented in the MAC control module core.

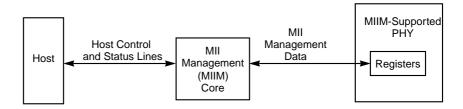

## 1.7 MIIM Core

For 10 Mbit/s and 100 Mbit/s operation, the optional MIIM core allows the host to write control data to and read status information from any of 32 registers in any of 32 PHYs using the MIIM interface. Only one register in one PHY can be addressed at the same time.

For 10 Gbit/s operation, the MIIM core allows the host to write control data to and read status information from 10 Gbit/s PHYS. The MIIM core can select up to 32 ports with up to 32 unique PHY devices per port. There can also be up to 64 K registers<sup>1</sup> per PHY.

The MIIM interface is a 16-bit parallel interface on the MIIM core's host side and a serial interface on the core's MII side. The MIIM Interface allows the host to send control data and receive status information from PHYs over the MAC MIIM interface.

For more details on the communication from the host to the PHYs, refer to the "Reconciliation Sublayer and Media Independent Interface Specifications" section of the IEEE 802.3u specification, 100BASE-T Fast Ethernet. The host sends control data to the PHY and receives status information from the PHY through the optional MIIM module, as shown in Figure 1.13.

Figure 1.13 MIIM Core

MIIM Core 1-25

<sup>1.</sup> At the time of this writing, the 10 Gbit PHY register definitions have not been finalized.

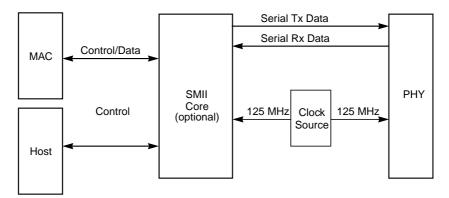

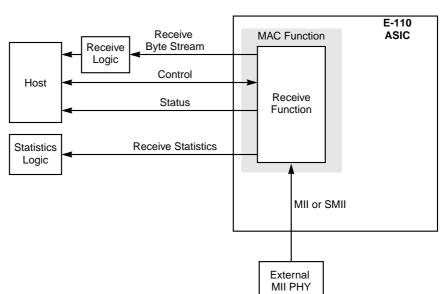

# 1.8 SMII Core

The optional Serial Media Independent Interface (SMII) core is designed to satisfy the following requirements:

- Convey complete standard MII information between a 10/100 PHY and MAC with two pins per port

- Allow a multiport MAC/PHY communication with one system clock.

- Operate in both half- and full-duplex

- Per packet switching between 10 Mbits and 100 Mbits/s data rates.

- Allow direct MAC to MAC communication

- Optional source synchronous mode

The MAC sends and receives data and control to and from the SMII core. The SMII core uses a single Tx Data line to send 10-bit data segments to the PHY. The Tx Data segment includes 8 bits of data and two MII control bits (TX\_ER and TX\_EN). The core also uses a single Rx Data line to receive 10-bit data segments from the PHY. The Rx Data segment includes 8 bits of data and two MII status bits (CRS and RX\_DV). An external clock provides 125 MHz clock signals to the SMII core and to the PHY. Figure 1.14 shows how the SMII core interfaces to the MAC and PHY devices.

Figure 1.14 SMII Core

# **Chapter 2 Signal Descriptions**

This chapter provides detailed descriptions of the signals for the E-110 core. These signal descriptions are useful for designers who will be interfacing the E-110 core with other core logic or external logic. This chapter contains the following sections:

- Section 2.1, "MAC Core Signals," page 2-1

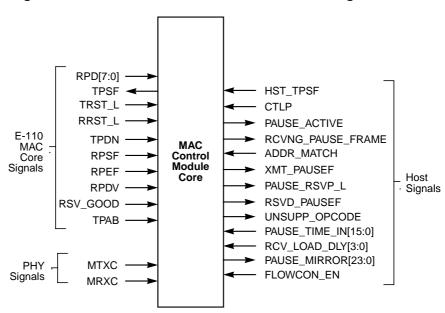

- Section 2.2, "MAC Control Module Signals," page 2-31

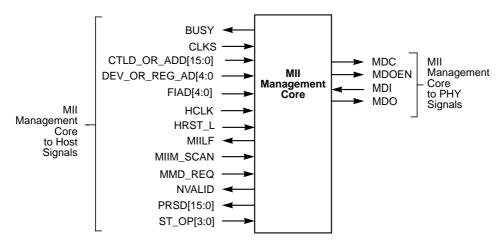

- Section 2.3, "MIIM Core Signals," page 2-39

- Section 2.4, "SMII Core Signals," page 2-45

Please see the subsection entitled "Conventions Used in This Manual" on page iv of this manual for a description of how signals are named.

# 2.1 MAC Core Signals

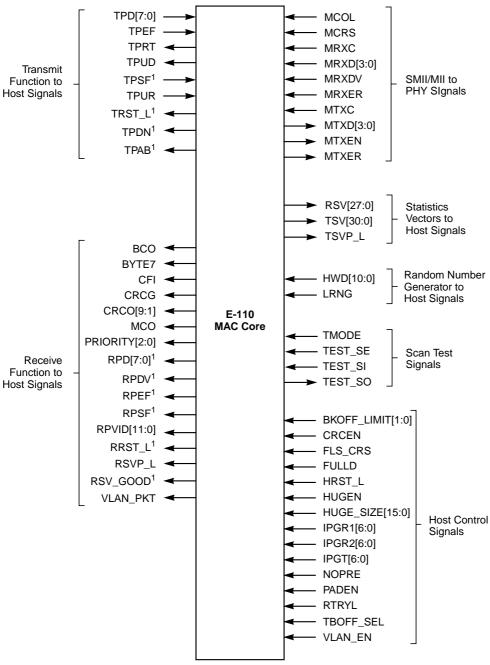

The interface diagram for the E-110 MAC core is shown in Figure 2.1. The MAC signals fall into the following groups:

- Transmit Function to Host

- Receive Function to Host

- MAC Control Module

- SMII/MII to PHY

- Host Control

- Statistics Vector to Host

- Random Number Generator to Host

- Scan Test

Figure 2.1 E-110 MAC Core Interface Diagram

1. These signals are also connected to the optional MAC control module core, if it is used.

# 2.1.1 Transmit Function to Host Signals

Below is a list of the signals between the E-110 MAC transmit function and the host transmit buffer. All signals are active HIGH unless otherwise noted. All signals are synchronous with the rising edge of the MII PHY transmit clock (MTXC). Signal direction is with respect to the transmit function block. See Section 3.2.1.1, "MAC Transmit Function," on page 3-5 for further details on transmit buffer and transmit function interaction.

### TPAB Transmit Packet Abort

Output

When asserted, the TPAB signal indicates that the transmission was discontinued. TPAB remains asserted until the E-110 MAC function receives a request to transmit, which is indicated when the MAC control module asserts TPSF. When deasserted, TPAB indicates that the transmission was not aborted. The following circumstances cause the transmission to be halted:

- Excess deferrals, which occur when the media is busy longer than twice the maximum frame length (greater than 24,288<sup>1</sup> bits when the HUGEN signal is deasserted or greater than 524,288<sup>2</sup> bits when HUGEN is asserted)

- Late collision (use RTRYL to avoid aborting)

- Multiple collisions (greater than 15)

- Transmit underrun

- Larger than normal packet, which is 1518 bytes (see also the HUGEN signal description)

The TPAB signal is also connected to the optional MAC control module core.

# TPD[7:0] Transmit Packet Data

Input

The TPD[7:0] signals are the transmit data bus. The host must hold the TPD[7:0] signals valid for exactly two MTXC clock cycles.

<sup>1. 24,288</sup> bits = 1518 bytes x 8 bits/byte x 2 (242.88 μs for 100 Mbit/s operation or 2.4288 ms for 10 Mbit/s operation)

<sup>2.</sup> 524,288 bits = 32 Kbytes x 8 bits/byte x 2 ( $5242.88 \mu s$  for 100 Mbit/s operation or 52.43 ms for 10 Mbit/s operation)

# TPDN Transmit Packet Done

Output

When asserted, the TPDN signal indicates successful completion of the packet transmit process. The MAC keeps TPDN asserted until the MAC receives a fresh request to transmit, which is indicated when the MAC control module asserts the TPSF signal. The TPDN signal is also connected to the optional MAC control module core.

#### TPEF Transmit Packet End of Frame

Input

The host asserts the TPEF signal to indicate the last byte of the transmit packet is available from the host. TPEF must be valid for two MTXC clock periods before it is deasserted.

# TPRT Transmit Packet Retry

Output

The MAC asserts the TPRT signal to indicate that the MAC function encountered at least one collision during a transmit attempt. The MAC asserts TPRT until the MAC receives a fresh request to transmit, which is indicated when the MAC control module asserts TPSF.

# TPSF Transmit Packet Start Of Frame

Input

The MAC control module, if implemented, asserts the TPSF signal to request the E-110 core to transmit a new packet. If the MAC control module is not implemented, the host must assert the TPSF signal.

This paragraph describes how the host must control the TPSF signal. The host interface asserts the TPSF signal to request the MAC to transmit a new packet. The host must keep the TPSF signal asserted for one transmit clock period after the E-110 core asserts the TPUD signal. The TPSF signal is synchronous to MTXC.

For a description of how the MAC control module controls the TPSF signal, see Section 2.1.3, "MAC Control Module Signals (Optional)" on page 2-9.

#### TPUD Transmit Packet Data Used

Output

The E-110 MAC function asserts the TPUD signal to indicate that the preamble has been transmitted. Every two clocks thereafter, the host must place the TPD[7:0] signals on the bus for the MAC. The MAC keeps TPUD asserted until the MAC accepts all the data bytes in the transmit packet from the host.

# TPUR Transmit Packet Data Underrun

Input

When the TPUR signal is asserted, the E-110 MAC function discontinues transmission. If the host is unable to supply transmit packet data bytes in a timely manner to the E-110 core (an underrun condition), the host must assert TPUR.

The host must assert TPUR for at least two MTXC clock cycles. The MAC asserts TPAB and MTXER in the very next clock cycle and deasserts MTXEN one cycle after TPAB and MTXER are asserted. MTXEN deasserted indicates the end of transmission.

#### TRST L Transmit Reset

Output

Other modules in an ASIC can use the TRST\_L signal as a host reset synchronized to the transmit clock (MTXC). Because the MTXC clock can be slow with respect to a host reset pulse, or even stopped, the host reset signal (HRST\_L) is captured in the E-110 MAC transmit function. The transmit function asserts TRST\_L asynchronously to MTXC when the HRST\_L signal occurs and deasserts TRST\_L synchronously on the positive transition of MTXC. Modules can use TRST\_L to initialize transmit logic. The TRST\_L signal is also connected to the optional MAC control module core.

# 2.1.2 Receive Function to Host Signals

Below is a list of the signals between the E-110 MAC receive function and the host receive logic. All signals are active HIGH unless otherwise noted. All signals are synchronous with the MRXC rising edge. Signal direction is with respect to the receive function block. See Section 3.2.1.2, "MAC Receive Function," on page 3-13 for further details on receive buffer and receive function interaction by means of these signals.

#### BCO Broadcast Out

Output

When asserted, the BCO signal indicates that the received packet is a *broadcast packet*. A broadcast packet has the destination address field set to all ones, which indicates it is being sent to all destinations on the network. When deasserted, BCO indicates that the received packet is not a broadcast packet. BYTE7 must be asserted for this output to be valid.

# BYTE7 Byte 7

When asserted, the BYTE7 signal indicates that the BCO and MCO bits are valid. When deasserted, the BYTE7 signal indicates that the BCO and MCO signals are not valid.

# CFI Canonical Format Indicator Output

The CFI signal, when asserted, indicates that the RIF field is present in the tag header. When the CFI signal is asserted, the NCFI bit in the RIF field determines whether any MAC address information in the MAC header is in noncanonical or canonical format. VLAN\_PKT must be asserted for CFI to be valid.

When deasserted, the CFI signal indicates that the RIF field is not present in the tag header, and that all MAC address information in the MAC header is in canonical format.

The CFI signal is extracted from the TCI field of the current received packet.

For more information regarding the RIF field in the tag header and the NCFI bit in that field, see the IEEE P802.1Q document.

#### CRCG CRC Good

Output

Output

The CRCG signal, when asserted, indicates that the CRCO[9:1] signals are valid. The CRCG signal, when deasserted, indicates that the CRCO[9:1] signals are not valid.

# CRCO[9:1] CRC Out

Output

The CRCO[9:1] signals reflect the state of the receive function FCS register after the first six bytes of the receive packet have been received. When the destination address bits that are received in the frame contain a multicast address, the E-110 core uses its built-in FCS generator to compute a nine-bit polynomial (the nine MSBs of the 32-bit FCS generator) from the incoming address. The value of this polynomial can be used as an index into an external multicast filter hash table. External logic can decide to either accept or reject the incoming frame.

#### MCO Multicast Out

When asserted, the MCO signal indicates that the received packet is a multicast packet (a packet that is being sent to selected stations on the network). When deasserted, MCO indicates that the received packet is not a multicast packet, which means that it could be an individual or broadcast packet. BYTE7 must be asserted

# PRIORITY[2:0]

# **User Priority**

for MCO to be valid.

Output

This field contains the user priority of the current received packet, extracted from the tag control information (TCI) field. VLAN\_PKT must be asserted for PRIORITY[2:0] to be valid.

#### RPD[7:0] Receive Packet Data

Output

The RPD[7:0] signals are the receive data bus. The signals hold the received data byte for two MRXC clock cycles. The RPD[7:0] signals are also connected to the optional MAC control module core.

### RPDV Receive Packet Data Valid

Output

A packet transmission from the receive function to the host receive control logic (see Figure 1.6 on page 1-12) begins when the receive function asserts the RPSF and RPDV signals at the first byte of received packet data on RPD[7:0] after removing the preamble and SFD. For subsequent data bytes, the receive function asserts only the RPDV signal until the last byte, when it asserts both RPDV and RPEF. See Figure 4.1 on page 4-2 for receive packet timing. The RPDV signal is also connected to the optional MAC control module core.

#### RPEF Receive Packet End of Frame

Output

Output

The MAC asserts the RPEF signal for one MRXC clock cycle to indicate that the last byte of the receive packet is available to the MAC control module on RPD[7:0]. The RPEF signal is also connected to the optional MAC control module core.

#### RPSF F

Receive Packet Start of Frame

The MAC asserts the RPSF signal for one MRXC clock cycle to indicate that the first byte of a receive packet is

available to the host on RPD[7:0]. The RPSF signal is also connected to the optional MAC control module core.

### RRST L Receive Reset

Output

Other modules in an ASIC can use the RRST\_L signal as a host reset synchronized to the receive clock (MRXC). Because the MRXC clock can be slow with respect to a host reset pulse, or even stopped, the host reset signal (HRST\_L) is captured in the E-110 MAC receive function, which asserts RRST\_L asynchronously to MRXC when HRST\_L occurs and deasserts RRST\_L synchronously on the positive transition of MRXC. The RRST\_L signal is also connected to the optional MAC control module core.

# RPVID[11:0] Received Packet VLAN ID

Output

This field contains the VLAN identifier extracted from the tag control information (TCI) field of the current received packet. If RPVID[11:0] is 0 and VLAN\_PKT is asserted, the current received packet is a priority-tagged frame. VLAN\_PKT must be asserted for RPVID[11:0] to be valid.

# RSVP\_L Receive Statistics Vector Pulse

Output

The RSVP\_L signal is active LOW. When the MAC asserts RSVP\_L, it indicates that the RSV[27:0] signals have been updated with a new receive statistics vector. When deasserted, it indicates that there has been no update. The RSVP\_L signal is also connected to the optional MAC control module core.

#### VLAN PKT VLAN Packet

Output

The MAC asserts the VLAN\_PKT signal to indicate that the current received packet has a valid Ethernet-encoded Tag Protocol Identifier (TPID). The encoded TPID for the MAC is 81-00. Assertion of VLAN\_PKT also indicates that the CFI, PRIORITY[2:0], and RPVID[11:0] signals are valid. The MAC deasserts VLAN\_PKT at the beginning of the next packet.

# 2.1.3 MAC Control Module Signals (Optional)

Below is a list of the signals that interface between the E-110 core and the optional MAC control module core. (See also Section 2.2, "MAC Control Module Signals," on page 2-31.) All signals are active HIGH unless otherwise noted. Signal direction is with respect to the E-110 core.

# RPD[7:0] Receive Packet Data

The RPD[7:0] signals are the receive data bus. The signals hold the received data byte for two MRXC clock cycles. The RPD[7:0] signals are also connected to the host.

# RPDV Receive Packet Data Valid Output

A packet transmission from the receive function to the host receive control logic (see Figure 1.6 on page 1-12) begins when the receive function asserts the RPSF and RPDV signals at the first byte of received packet data on RPD[7:0] after removing the preamble and SFD. For subsequent data bytes, the receive function asserts only the RPDV signal until the last byte, when it asserts both RPDV and RPEF. See Figure 4.1 on page 4-2 for receive packet timing. The RPDV signal is also connected to the host.

### RPEF Receive Packet End of Frame Output

The MAC asserts the RPEF signal for one MRXC clock cycle to indicate that the last byte of the receive packet is available to the MAC control module on RPD[7:0]. The RPEF signal is also connected to the host.

### RPSF Receive Packet Start of Frame Output

The MAC asserts the RPSF signal for one MRXC clock cycle to indicate that the first byte of a receive packet is available to the host on RPD[7:0]. The RPSF signal is also connected to the host.

### RRST L Receive Reset Output

Other modules in an ASIC can use the RRST\_L signal as a host reset synchronized to the receive clock (MRXC). Because the MRXC clock can be slow with respect to a host reset pulse, or even stopped, the host reset signal (HRST\_L) is captured in the E-110 MAC receive function, which asserts RRST\_L asynchronously

Output

to MRXC when HRST\_L occurs and deasserts RRST\_L synchronously on the positive transition of MRXC. The RRST\_L signal is also connected to the host.

# RSV\_GOOD Receive Statistics Vector Good Output

At the end of a receive frame, the MAC updates the Receive Statistics Vector (RSV[27:0]). The MAC asserts the RSV\_GOOD signal, which reflects the RSV24 bit, if the received frame has no errors. The MAC deasserts the signal if the received frame contains errors.

# TPAB Transmit Packet Abort Output

When asserted, the TPAB signal indicates that the transmission was discontinued. TPAB remains asserted until the E-110 MAC function receives a request to transmit, which is indicated when the MAC control module asserts TPSF. When deasserted, TPAB indicates that the transmission was not aborted. The following circumstances cause the transmission to be halted:

- Excess deferrals, which occur when the media is busy longer than twice the maximum frame length (greater than 24,288<sup>1</sup> bits when the HUGEN signal is deasserted or greater than 524,288<sup>2</sup> bits when HUGEN is asserted)

- Late collision (use RTRYL to avoid aborting)

- Multiple collisions (greater than 15)

- Transmit underrun

- Larger than normal packet, which is 1518 bytes (see also see the HUGEN signal description)

The TPAB signal is also connected to the host.

# TPDN Transmit Packet Done Output

When asserted, the TPDN signal indicates successful completion of the packet transmit process. The MAC keeps TPDN asserted until the MAC receives a fresh request to transmit, which is indicated when the MAC

<sup>1. 24,288</sup> bits = 1518 bytes x 8 bits/byte x 2 (242.88 μs for 100 Mbit/s operation or 2.4288 ms for 10 Mbit/s operation)

<sup>2.</sup> 524,288 bits = 32 Kbytes x 8 bits/byte x 2 ( $5242.88 \mu s$  for 100 Mbit/s operation or 52.43 ms for 10 Mbit/s operation)

control module asserts the TPSF signal. The TPDN signal is also connected to the host.

### TPSF Transmit Packet Start Of Frame

Input

The MAC control module asserts the TPSF signal to request the E-110 Core to transmit a new packet. Once asserted, TPSF is kept asserted as long as the HST\_TPSF signal from the host is asserted. On a data packet transmit request from the host (HST\_TPSF asserted and CTLP deasserted), TPSF is asserted by the MAC control module only if PAUSE\_ACTIVE is deasserted. The MAC control module does not enter the pause state because either the pause counter has counted down to zero or the counter is currently loaded with a zero value. If the PAUSE\_ACTIVE signal is asserted, TPSF is not asserted until PAUSE\_ACTIVE is deasserted.

If the FLOWCON\_EN signal is deasserted, the MAC control module does not assert the TPSF signal for host control packet transmit requests. If the FLOWCON\_EN signal is deasserted, the TPSF signal is asserted for host data packet transmit requests. When FLOWCON\_EN is asserted, TPSF is asserted one clock after HST\_TPSF is asserted for a data or a control packet transmit request. When FLOWCON\_EN is deasserted, TPSF is asserted at the same clock as when HST\_TPSF is asserted for a data packet request. The MAC control module does not interpret the transmit data in any way and transmit data is routed from the host to the E-110 MAC directly.

### TRST L Transmit Reset

Output

Other modules in an ASIC can use the TRST\_L signal as a host reset synchronized to the transmit clock (MTXC). Because the MTXC clock can be slow with respect to a host reset pulse, or even stopped, the host reset signal (HRST\_L) is captured in the E-110 MAC transmit function. The transmit function asserts TRST\_L asynchronously to MTXC when the HRST\_L signal occurs and deasserts TRST\_L synchronously on the positive transition of MTXC. Modules can use TRST\_L to initialize transmit logic. The TRST\_L signal is also connected to the host.

# 2.1.4 SMII/MII to PHY Signals

The signals that interface the MAC MII to the PHY (not including the MIIM interface) are listed below. All signals are active HIGH. Signal direction is with respect to the MAC MII function. See IEEE 802.3u standard documentation for further information. The standard IEEE MII signal name references are shown in brackets.

#### MCOL Collision Detected

Input

The PHY asserts the MCOL [COL] signal asynchronously with minimum delay from the start of a collision on the media. The PHY deasserts MCOL to indicate no collision. MCOL is internally synchronized to the MTXC clock and in the worst case may take up to two clock cycles to be detected by the MAC transmit function.

#### MCRS Carrier Sense

Input

The PHY asserts the MCRS [CRS] signal asynchronously with minimum propagation delay from the detection of a nonidle medium. The PHY deasserts MCRS when it detects an idle medium. The PHY also asserts MCRS with minimum propagation delay in response to MTXEN [TX\_EN].

The PHY ensures that MCRS remains asserted throughout the duration of a collision condition.

#### **MRXC**

# **Receive Nibble or Symbol Clock**

Input

The MRXC [RX\_CLK] signal is a continuous clock that provides a timing reference for transfer of the MRXDV [RX\_DV], MRXD[3:0] [RXD], and MRXER [RX\_ER] signals from the PHY to the E-110 MAC. MRXC is an input from the PHY.

As long as the PHY is receiving a continuous signal from the medium and can recover the MRXC clock reference and supply MRXC, the PHY does not need to make a switch from the recovered clock reference to a nominal clock reference (for example, the MTXC [TX\_CLK] continuous clock signal from the PHY). However, if the loss of a receive signal causes the PHY to lose the recovered clock reference, the PHY must source MXRC from a nominal clock reference.

If the PHY needs to make a switch from recovered clock to nominal clock, it deasserts the MRXDV signal. During

the interval between MCRS and the assertion of MRXDV at the beginning of a frame, the PHY may extend a cycle of the MRXC clock by holding it in either the HIGH or LOW condition until the PHY has successfully locked onto the recovered clock. Successive cycles of MRXC must meet the duty cycle requirement.

While MRXDV is asserted, the PHY recovers MRXC from the received data. MRXC has a frequency equal to 25% of the data rate of the received signal and is synchronous to recovered data. The duty cycle is between 35% and 60% and is nominally 50%. For 100 Mbit/s operation, MRXC is nominally 25 MHz  $\pm$ 100 ppm, and the minimum MRXC HIGH and LOW times are 14 ns. For 10 Mbit/s operation, MRXC is nominally 2.5 MHz  $\pm$  100 ppm, and the minimum MRXC HIGH and LOW times are 140 ns.

When the MCRS signal is deasserted, the PHY provides MRXC at the PHY's nominal clock rate (for example, the MTXC clock signal) and with nominal duty cycle. The minimum HIGH and LOW times are each 35% of the nominal MRXC period except for the transition between recovered clock frequency and nominal clock frequency, which occurs while MRXDV is deasserted. Following the transition from MRXDV asserted to MRXDV deasserted, the PHY can keep MRXC in either the HIGH or LOW condition to extend the MRXC clock by one cycle until the PHY is ready to provide MRXC from a nominal clock source. The maximum HIGH or LOW time for MRXC during this transition is two times the nominal clock period (a total of 80 ns for 25 MHz operation).

# MRXD[3:0] Receive Nibble Data

Input

MRXD[3:0] [RXD] consists of four data signals that the PHY drives synchronously to the rising edge of the MRXC clock. For each MRXC period in which MRXDV is asserted, the PHY transfers four bits of data over the MRXD[3:0] signals to the E-110 MAC. MRXD[0] is the least significant bit. When MRXDV is deasserted, the MRXD[3:0] signals have no effect on the E-110 MAC.

For a frame to be correctly interpreted by the E-110 MAC, a completely formed SFD must be passed across the interface. A completely formed SFD is the octet

0b1010.1011, which follows seven identical octets of preamble (0b1010.1010).

### MRXDV Receive Data Valid

Input

The PHY asserts the MRXDV [RX\_DV] signal to indicate that the PHY is presenting recovered and decoded nibbles on the MRXD[3:0] [RXD[3:0]] signals and that MRXC is synchronous to the recovered data. The PHY asserts MRXDV synchronously to the rising edge of MRXC. The PHY keeps MRXDV asserted from the first recovered nibble of the frame through the final recovered nibble and deasserts it prior to the first MRXC that follows the final nibble. MRXDV encompasses the frame, starting no later than the SFD and excluding any *end of frame delimiter*. The PHY may also assert MRXDV for transferring a validly decoded preamble.

#### MRXER Receive Error

Input

The PHY asserts the MRXER [RX\_ER] signal to indicate to the E-110 MAC that a media error (for example, a coding error) was detected somewhere in the frame presently being transferred from the PHY to the E-110 MAC. The PHY asserts MRXER synchronously to the rising edge of MRXC for one or more MRXC periods and then deasserts it. The PHY must assert MRXER for at least one MRXC clock period during the frame.

#### MTXC

# **Transmit Nibble or Symbol Clock**

Input

The MTXC [TX\_CLK] signal operates at a frequency of 25 or 2.5 MHz. MTXC is a continuous clock that provides a timing reference for transfer of the MTXEN [TX\_EN], MTXD[3:0] [TXD[3:0]], and MTXER [TX\_ER] signals from the E-110 MAC to the PHY. The PHY provides MTXC.

The MTXC frequency is 25% of the transmit data rate. A PHY operating at 100 Mbits/s provides an MTXC frequency of 25 MHz  $\pm$  100 ppm. A PHY operating at 10 Mbits/s provides a TX\_CLK frequency of 2.5 MHz  $\pm$  100 ppm. The duty cycle of the TX\_CLK signal is between 35% and 60%, inclusively.

### MTXD[3:0]

### **Transmit Nibble Data**

Output

The MTXD[3:0] signals are synchronous to the rising edge of MTXC.

MTXD[3:0] [TXD[3:0]] consists of four data signals that are synchronous to MTXC. For each MTXC period in which MTXEN is asserted, the PHY accepts the MTXD[3:0] signals for transmission. MTXD[0] is the least significant bit. When MTXEN is deasserted, the MTXD[3:0] signals have no effect on the PHY.

### MTXEN Transmit Enable

Output

The MTXEN [TX\_EN] signal indicates that the E-110 MAC is presenting MTXD[3:0] nibbles on the MII for transmission. The MAC asserts MTXEN synchronously with the first nibble of the preamble. MTXEN remains asserted while all nibbles to be transmitted are presented to the MII. The MAC deasserts MTXEN prior to the first MTXC following the final nibble of a frame. MTXEN is synchronous to the rising edge of MTXC, and the PHY samples MTXEN synchronously.

# MTXER Transmit Coding Error

Output

The E-110 MAC function asserts the MTXER [TX\_ER] signal synchronously to the rising edge of MTXC, and the PHY samples MTXER synchronously. When the MAC asserts MTXER for one MTXC clock period while MTXEN is also asserted, MTXER causes the PHY to transmit one or more symbols that are not part of the valid data or delimiter set somewhere in the frame being transmitted to indicate that there has been a transmit coding error. If the MAC asserts the MTXER signal when a PHY is operating at 10 Mbits/s or when MTXEN is deasserted, the PHY must not allow the transmission of data to be affected.

# 2.1.5 Host Control Signals

The control lines from the host to the MAC core are listed below. All signals are active HIGH unless otherwise indicated. Signal direction is with respect to the MAC function. These signals are not synchronized on a packet boundary within the E-110 MAC. That is, any change in these signals is immediate, and changing the state of the signals during a packet can cause unexpected results.

### BKOFF\_LIMIT[1:0]

# **Backoff Limit**

Input

The BKOFF\_LIMIT[1:0] signals determine the number of transmission attempts the E-110 MAC core makes after

a collision and the integer number of slot times<sup>1</sup> the core waits before rescheduling a transmission attempt (during retries after a collision).

When a transmission attempt has terminated due to a collision, the MAC core retries until either the transmission is successful or the maximum number of attempts (16) have been made and all have terminated due to collisions. The MAC core waits an integer number of slot times (backoff) before each attempt to retransmit. The backoff delay, r, before each retransmission attempt is chosen as a uniformly distributed random integer in the range:

$$0 \le r \le 2^k$$

The variable *k* is the retry counter value and is calculated as follows:

$$k = min\langle n, 10 \rangle$$

The variable n is the current number of retransmissions. The retry counter value is held to the lesser of the current number of retransmissions or the value 10.

The following table illustrates the relationship between the backoff delay and the maximum retry counter value.

| BKOFF_ | _LIMIT | Maximum<br>Backoff<br>Delay in Slot | Retry Counter (k) |

|--------|--------|-------------------------------------|-------------------|

| 1      | 0      | Times                               | Maximum Value     |

| 0      | 0      | 0–1023                              | 10                |

| 0      | 1      | 0–255                               | 8                 |

| 1      | 0      | 0–15                                | 4                 |

| 1      | 1      | 0–3                                 | 2                 |

As an example, if the BKOFF\_LIMIT[1:0] value is 0b10, the maximum retry counter value is 4. The E-110 MAC core retry counter value is zero before any collisions occur. When a collision occurs, the retry counter increments to one, and the backoff delay is set to a value between 0 and 1 slot times. When the backoff delay

<sup>1.</sup> One slot time equals 512-bit times.