# MV66030 64-WORD x 9-BIT FIRST-IN FIRST-OUT MEMORY

The MV66030 is an asynchronous first-in first-out memory. organised as 64 9-bit words. The device accepts a 9-bit parallel word, D0 - D8, under control of the shift in (SI) input. Multiple devices can be used in parallel to satisfy wider data requirements or can be cascaded to any depth to give more words of storage. Data entered into the FIFO ripples through the device to the outputs Q0 - Q8. Up to 64 words may be entered before any words are read from the memory. The stored words stack up at the output in the order in which they were entered

Activating the shift out control (SO) causes the next to the last word of data to move to the output and all data shifts one place down the stack. Input ready (IR) and output ready (OR) signals respectively indicate that the device can accept new data or that the output contains valid data. If the input ready output remains inactive, the device is full. If the output ready signal remains inactive, the device is empty.

Since reading and writing operations are completely independent, the device can be used as a buffer between two digital systems operating asynchronously and with widely differing clock frequencies.

### **FEATURES**

- 25MHz Guaranteed Data Rate when Cascaded (MV66030-25)

- < 200mW at 25MHz

- < 55mW Standby

- Industrial Operating Temperature Range: -40°C to +85°C

- Single 5V Supply, ±10% Tolerance

- Tri-State Outputs

# **APPLICATIONS**

- Asynchronous Buffer between Digital Systems

- I/O Formatting in DSP Systems

- Video Time Base Correction

- Printer Buffers

- Disk or Tape Interfaces

#### ASSOCIATED PRODUCTS

MV66401/2/3/4 64x4/5, Bistate/Tristate Cascadable FIFOs MJ2812/13 32x8/9 Cascadable FIFOs MJ2841 64x4 Cascadable FIFO

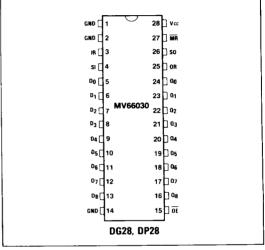

Fig.1 Pin connections - top view

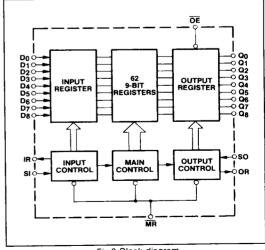

Fig.2 Block diagram

#### FIFO OPERATION

The MV66030 FIFO contain 64 nine bit data registers. Data is initially loaded from the data inputs D0 - D8 by applying a low to high transition on the shift in (SI) input. IR goes low indicating that data has been entered into the first data register and the input is now 'busy' unable to accept more data. When SI next goes low the fall-through process begins, (assuming that at least the second location is empty). The data in the first register is copied into the second and the IR goes high indicating the inputs are available for another data word.

The data falling through the registers stacks up at the output end. A high on OR indicates there is valid data on the data outputs Q0 - Q8. A shift out (SO) can then be used to shift the data out of the FIFO. A low to high transition on SO causes OR to go low, indicating that the data on the outputs may no longer be valid. When SO goes low, the data in the next to last register position moves into the last register position and on to the outputs. If the memory is emptied by reading out all of the data, then, when the last word is being read out and SO goes high, OR will go low as before. When SO next goes low however, there is no data to move into the last location so OR will remain low until more data is entered. Similarly, when the memory is full, data written into the first location will not shift into the second when SI goes low, and IR will remain low instead of returning to a high state.

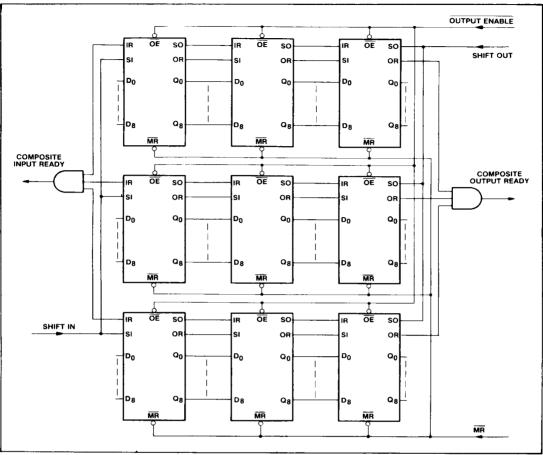

The data word can be extended in width by using more than one FIFO as shown in Fig.10. The status flags must be gated as shown to allow for possible delay variations between devices.

The depth of the FIFO can be extended by tying the data outputs of one device to the data inputs of the next, as shown in Fig. 10, the IR input of the receiving device is connected to SO pin of the sending device. Similarly the OR pin of the sending device is connected to the SI pin of the receiving device.

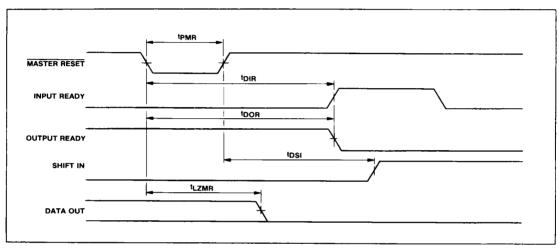

An overriding master reset (MR) is used to reset all control register bits and remove the data from the output (i.e. reset the output to all low).

#### **ELECTRICAL CHARACTERISTICS**

Test conditions (unless otherwise stated):

Under Recommended operating conditions

# **DC Characteristics**

|                                                   |        | INDUSTRIAL |       |      |        |      |                                                 |

|---------------------------------------------------|--------|------------|-------|------|--------|------|-------------------------------------------------|

| Characteristic                                    | Symbol | MV660      | 30-10 | MV66 | 030-25 | Unit | Conditions                                      |

|                                                   |        | Min.       | Max.  | Min. | Max.   |      |                                                 |

| Output high level VIN = VIH or VIL, IOH = -1mA    | Vон    | 2.4        |       | 2.4  |        | V    |                                                 |

| Output low level  VIN = VIH or VIL, FOL = 8mA     | Vol    |            | 0.5   |      | 0.5    | V    |                                                 |

| Input leakage VIN = VIH or VIL                    | Lin    | -10        | +10   | -10  | +10    | μΑ   |                                                 |

| Output leakage GND ≤ Vout ≤ Vcc<br>Vcc = Vcc max. | loz    | -50        | +50   | -50  | +-50   | μΑ   |                                                 |

| Short circuit current                             | los    |            | 100   |      | 100    | mΑ   | Note 2                                          |

| Supply current                                    | Icc    |            | 30    |      | 40     | mA   | Vcc = max.                                      |

| Standby ourrent                                   |        |            |       |      |        |      | Tamb = 85°C<br>ILOAD = 0mA                      |

| Standby current                                   |        |            | 10    |      | 10     | mA   | Vcc — max.<br>ILOAD == 0mA<br>All inputs at Vil |

#### ABSOLUTE MAXIMUM RATINGS

| Supply voltage Vcc               | -0.5V to 7.0V      |

|----------------------------------|--------------------|

| Input voltage V in (see Note 3)  | -0.9V to Vcc +0.9V |

| DC voltage applied to output     |                    |

| when high impedance              | -0.5V to 7.0V      |

| Clamp diode current per pin (see | Note 2) + 18mA     |

| Storage temperature Ts           | -65 °C to +150 °C  |

| Ambient temperature with power   |                    |

| applied Tamb                     | -55 °C to +125 °C  |

| Package power dissipation DP     | 450mW              |

| DG                               | 1000mW             |

#### NOTES

- 1. Exceeding these ratings may cause permanent damage Functional operation under these conditions is not implied

- Maximum dissipation or 1 second should not be exceeded, only one output to be tested at any one time.

- Input voltages more negative than -0.9V cause clamp diode current to flow. The maximum negative voltage depends on the source impedance.

# RECOMMENDED OPERATING CONDITIONS

| Supply voltage Vcc       | 5V ± 10%        |

|--------------------------|-----------------|

| Min. input high level V⊪ | + 2V            |

| Max. input low level Vı∟ | + 0.8V          |

| Ambient temperature      | -40 °C to 85 °C |

# AC Characteristics - Using test circuit, except where stated.

|                             | Symbol        | INDUSTRIAL |      |            |      |      |                     |

|-----------------------------|---------------|------------|------|------------|------|------|---------------------|

| Characteristic              |               | MV66030-10 |      | MV66030-25 |      | Unit | Condition           |

|                             |               | Min.       | Max. | Min.       | Max. |      |                     |

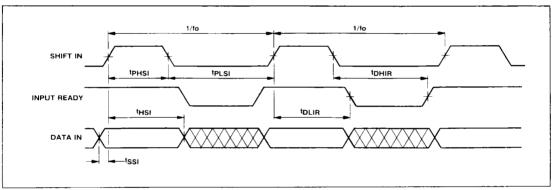

| Maximum operating frequency | fo            | 10         |      | 25         |      | MHz  | Note 4              |

| SI HIGH time                | <b>t</b> PHSI | 30         |      | 15         |      | ns   | +85°C, 4.5V Note 11 |

| SI LOW time                 | <b>t</b> PLSI | 40         |      | 20         |      | ns   |                     |

| Data setup to SI            | tssı          | 0          |      | 0          |      | ns   | Note 5              |

| Data hold from SI           | t HSI (a)     | 50         |      | 30         |      | ns   | Note 5,6            |

|                             | thsi (b)      | tPHSI +5   |      | tPHSI +5   |      | ns   |                     |

| Delay, SI HIGH to IR LOW    | t DLIR        | '          | 30   |            | 18   | ns   | Note 10             |

| Delay, SI LOW to IR HIGH    | t DHIR        |            | 40   | i l        | 22   | ns   | Note 10             |

| SO HIGH time                | tphso         | 30         |      | 12         |      | ns   | +85°C, 4.5V Note 11 |

| SO LOW time                 | tPLSO         | 40         |      | 20         |      | ns   |                     |

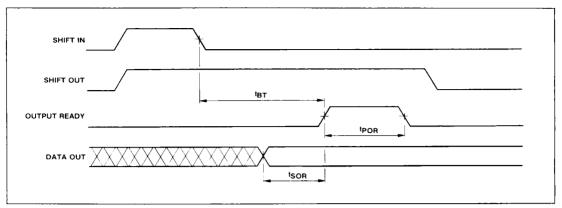

| Delay, SO HIGH to OR LOW    | tolor         |            | 30   |            | 18   | ns   | Note 10             |

| Delay, SO LOW to OR HIGH    | tonor         |            | 40   |            | 22   | ns   | Note 10             |

| Data setup to OR HIGH       | tson          | -20        |      | -15        |      | ns   |                     |

| Data hold from SO LOW       | tHSO          | 10         |      | 8          |      | ns   |                     |

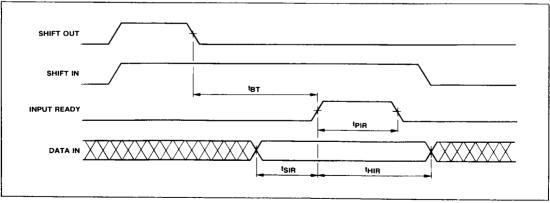

| IR pulse HIGH               | <b>t</b> PIR  | 9          |      | 6          |      | ns   | -40°C, 5.5V Note 11 |

| OR pulse HIGH               | tPOR          | 10         |      | 7          |      | ns   | -40°C, 5.5V Note 11 |

| Data setup to IR            | tsia          | 0          |      | 0          |      | ns   | Note 8              |

| Data hold from IR           | this          | 50         |      | 30         |      | ns   | Note 8              |

| Bubble through time         | tвт           | 1          | 2400 |            | 1200 | ns   |                     |

| MR pulse width              | t PMR         | 60         |      | 50         |      | ns   | Note 9              |

| MR HIGH to SI transition    | tosi          | 60         |      | 50         |      | ns   |                     |

| MR LOW to OR LOW            | t DOR         |            | 60   | 1          | 50   | ns   |                     |

| MR LOW to IR HIGH           | t DIR         |            | 60   |            | 50   | ns   |                     |

| MR LOW to output LOW        | t∟zmr         | l          | 60   | 1          | 50   | ns   | Note 7              |

| Output valid from OE LOW    | tooe          |            | 60   |            | 40   | ns   |                     |

| Output HIGH-Z from OE HIGH  | tHZOE         |            | 60   |            | 40   | ns   |                     |

#### NOTES

- 4. 1/fo > tensi + tonia, 1/fo > tenso + tonoa.

- tssi and this apply when memory is not full.

- Hold time is the lesser of the two parameters (a) and (b).

All data outputs will be at LOW level after reset goes high until data is entered into the FIFO.

These times apply when the device is full and SI is held high.

- 9. For cascade applications, tPMR must be double that specified.

- 10. Under cascade conditions.

- 11. Plessey devices are guaranteed to cascade at 25MHz (under typical operating conditions tens) = 10ns, tens = 13ns, tens = 8ns, tens = 12ns).

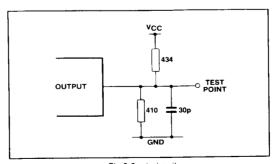

Fig.3 Test circuit

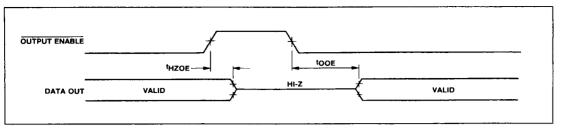

Fig.4 Output enable timing

Fig.5 Master reset timing

Fig.6 Data Out to Data In bubble through time

Fig.7 Data In to Data Out fall through time

Fig.8 Switching waveforms - Data In timing

Fig.9 Switching waveforms - Data Out timing

FIFOs are expandable in depth and width. However, in forming wider words two external gates are required to generate composite Input and Output Ready flags. This need is due to the variation of delays of the FIFOs.

Fig.10 192 x 27 application

# **USER NOTES**

- When the memory is empty the last word read will remain on the outputs until the master reset is strobed or a new data word falls through to the output. However, OR will remain LOW, indicating data at the output is not valid.

- When the output changes as a result of a pulse on SO, the OR signal always goes LOW before there is any change in output data.

- 3. If SO is held HIGH while the memory is empty and a word is written into the input, that word will ripple through the memory to the output. OR will go HIGH for one internal cycle (tpon) and then go back LOW again. The stored word will remain on the outputs. If more words are written into the FIFO, they will line up behind the first word and will not appear on the outputs until SO has been brought LOW.

- 4. When the master reset is brought LOW, the outputs are cleared to LOW, IR goes HIGH and OR goes LOW. If SI is HIGH when the master reset goes HIGH then the data on the inputs will be written into the memory and IR will return to the LOW state until SI is brought LOW. If SI is LOW when the master reset is ended, the IR will go HIGH, but the data on the inputs will not enter the memory until SI goes HIGH.

- 5. All MV66XXX FIFO's will cascade with other MV66XXX devices, but may not cascade with pin compatible devices from other manufacturers.

- 6. The IR and OR signals are provided to ensure that data is written into, or read out of, the FIFO correctly. If SI or SO are clocked without reference to these flags, the memory may corrupt and lock out any further data input. The memory should be reset to restore normal operation.

# MV66030

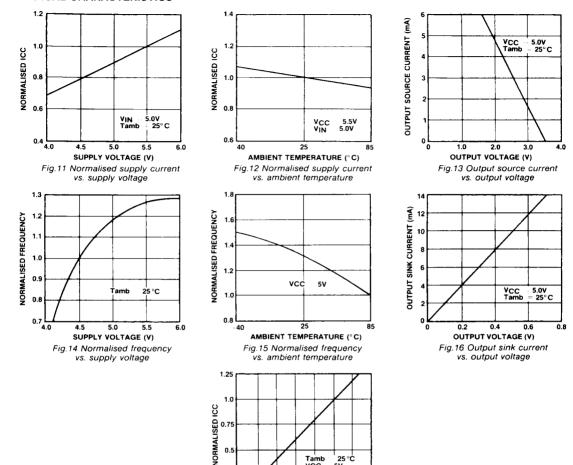

#### TYPICAL CHARACTERISTICS

Tamb VCC

15 20 25

FREQUENCY (MHz) Fig.17 Normalised Icc vs. frequency

25 °Ċ 5V

# ORDERING INFORMATION

MV66030-10 B0 DG (Industrial - Ceramic DIL package) MV66030-25 B0 DG (Industrial - Ceramic DIL package) MV66030-10 B0 DP (Industrial - Plastic DIL package) MV66030-25 B0 DP (Industrial - Plastic DIL package)

0.5

0.25

00