# 80C300

Full Duplex CMOS Ethernet 10/100 Mega Bit/Sec Data Link Controller

This document is an LSI Logic document. Any reference to SEEQ Technology should be considered LSI Logic.

### Features

- Low Power CMOS Technology

- 10/100 MBit Ethernet Controller Optimized for Switching Hub, Multiport Bridge/Router, & Server Applications

- Meets ANSI/IEEE 802.3 and ISO 8802-3 Standards for Ethernet (10Base-5) Thin Net (10Base-2) (10Base-T) and the Proposed 100Base-T4, 100Base-TX Standards

- 10 MHz Serial/Parallel Conversion in 10 MBit/sec Serial Mode.

- Standard 10MBit/sec Serial Mode or Programmable MII Ethernet Interface for 10/100 MBit/sec Applications

- Programmability of Double Word Threshold Count for Space Available/Data Available Ready Condition for Transmit/Receive FIFOs

- Auto Retransmit Upon Collision Sense

- Preamble Generation and Removal

- Automatic 32-Bit FCS (CRC) Generation and Checking

- Collision Handling, Transmission Deferral and Retransmission with Automatic Jam and Backoff Functions

- Error Interrupt and Status Generation

- Selectable Little Endian/Big Endian Transmit Byte Ordering for FIFO Interface for Intel/Motorola Compatibility

- Single 5 V±5% Power Supply

- Standard CPU and Peripheral Interface Control Signals

- 128/128 Byte Independent Transmit/Receive FIFOs with 32 Bit Data Path Interface

- 1 G Bits/sec (133 M Bytes/sec) Peak Data Rate in 32 Bit Mode.

- Loopback Capability for Diagnostics

- 32 Bit FIFO Data Path

Note: Check for latest Data Sheet revision before starting any designs.

SEEQ Data Sheets are now on the Web, access SEEQ Home Page www.seeq.com

- or -

LSI Logic at www.lsilogic.com

- Inputs and Outputs TTL Compatible

- The Following Additional Features can be Programmed for the 80C300

- 64 bit Multicast Filter

- Reports Status of "SQE" During Transmits

- Transmit No CRC Mode

- Transmit No Preamble Mode

- Transmit Packet Autopadding Mode

- Receive CRC Mode

- Disable Self-Receive on Transmit Mode

- Disable Further Transmissions when Both Transmit Status Registers are Full

- Disable Loading the Transmit Status for Successfully Transmitted Packets

- Disable the Receive Interrupts Independent of the Receive Command Register Setting

- Successful Packet Transmit Completion Feature

- Full Duplex Operation

- Provides 20/200 Mbps Bandwidthfor Switched Networks

- Supports AutoDUPLEX Mode for Automatic Full Duplex Operation

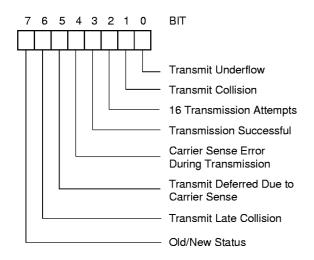

- Transmit Status on a Per Packet Basis Reports the Following

- Occurrence of a Transmit FIFO Underflow

- Transmit Collision Occurrence

- 16 Collision Occurrence

- Carrier Sense Error During Transmission

- 10/100 Mbit/sec Transmit Clock Detect

- Late Collision Occurrence

- Transmission Successful

- Transmission Deferred

Hurricane is a trademark of SEEQ Technology Inc.

- Management Counters for

- Alignment Errors

- FCS Errors

- Runt Receive Frames

- Short Receive Events

- Oversized Receive Packets

- Transmit Collisions

- Receive Collisions

- Very Long Transmit Events

- Excessive Transmit Deferral

- Late Transmit Collisions

- Transmit Excessive Collisions

- Symbol Errors (100 MBit/sec Ethernet Only)

- Total Octets Received

- Total Octets Transmitted

- Receive FIFO Overflows

- Total Rx Multicast, Unicast and Broadcast Frames

- Total Tx Multicast, Unicast and Broadcast Frames

- Tx Defer Count

- Number of Retransmit Attempts

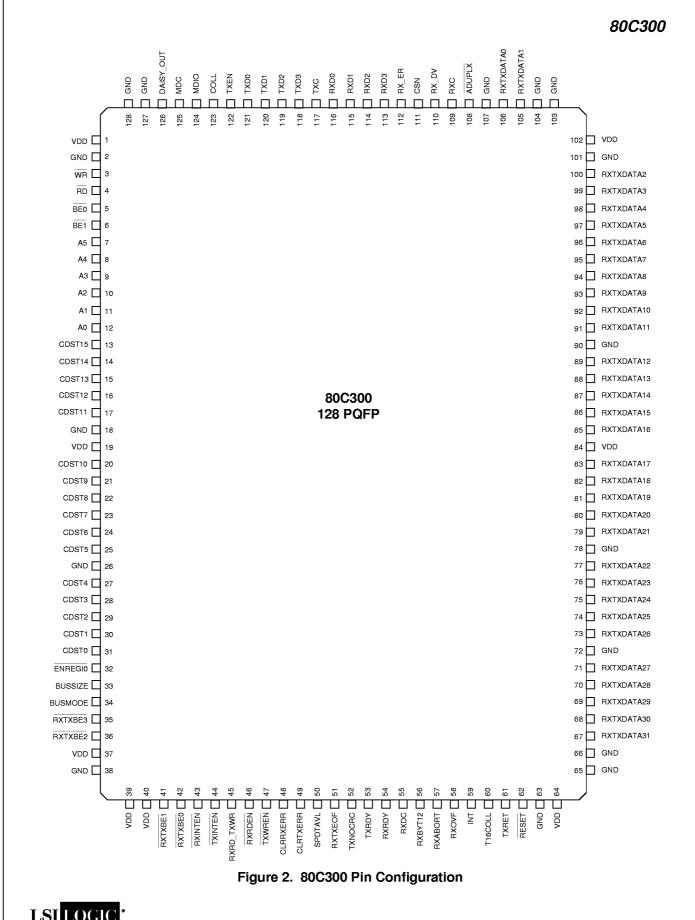

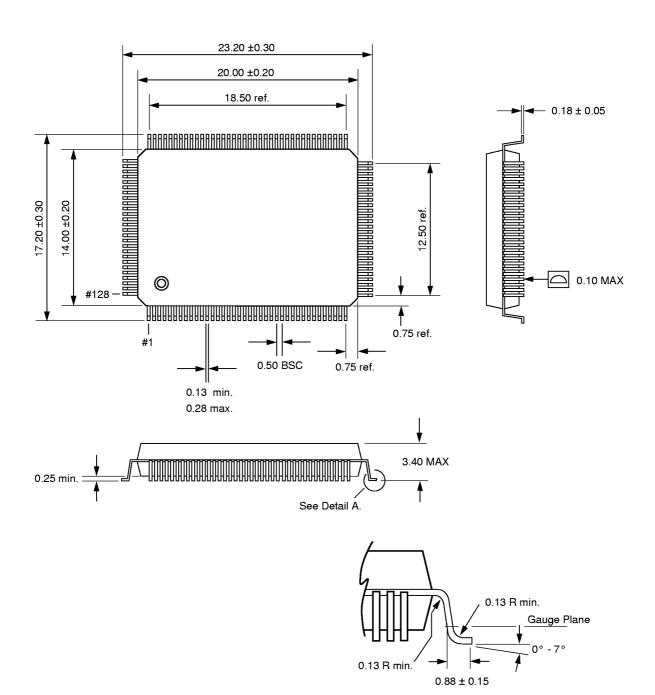

- 128 Pin PQFP package

## Table of Contents

- 1.0 Pin Description

- 2.0 Introduction

- 3.0 Functional Description

- 3.1 Frame Format

- 3.2 Packet Transmission

- 3.2.1 Controlling Transmit Packet Encapsulation

- 3.2.2 Transmission Initiation/Deferral

- 3.2.3 Collision on Transmit

- 3.2.4 Transmit Termination Conditions

- 3.2.5 Error Conditions That Will Cause TXRET to go HIGH

- 3.2.6 Detection and Clearing of a Transmit Retry Condition

- 3.3 Packet Reception

- 3.3.1 Preamble Processing

- 3.3.2 Address Matching

- 3.3.3 Conditions of Receive Termination

- 3.3.4 Using Rxabort to Terminate Reception

- 3.3.5 Receive Discard Conditions

- 3.4 System Interface

- 3.5 FIFO Interface

- 3.5.1 Little and Big Endian Format

- 3.5.2 Transmit FIFO Interface

- 3.5.3 Receive FIFO Interface

- 3.5.4 Special Conditions on RXRD\_TXWR

Clock Input

- 3.6 Register Interface

- 3.6.1 Internal Channel Register Addressing Table

- 3.6.2 Station Address Register

- 3.6.3 Transmit Command Register

- 3.6.4 Receive Command Register

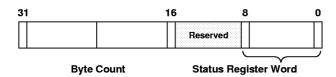

- 3.6.5 Transmit Status Register

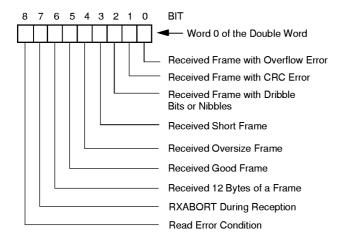

- 3.6.6 Receive Status Register

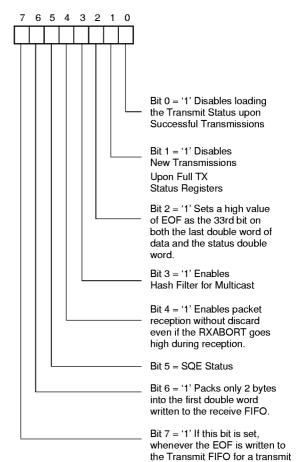

- 3.6.7 Configuration Registers

- 3.6.8 FIFO Threshold Register

3.6.8.1 FIFO Threshold Register

Address Settings Table

- 3.6.9 Defer Register Calculations for 80C300

- 3.7 Management Interface of the MII

- 3.8 Counters

- 4.0 DC Characteristics

- 5.0 AC Characteristics

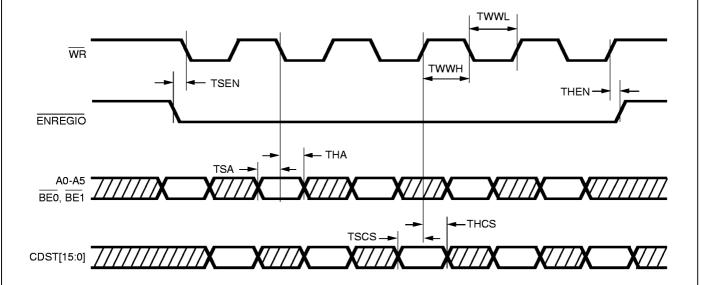

- 5.01 Command/Status Interface Read Timing

- 5.02 Command/Status Interface Write Timing

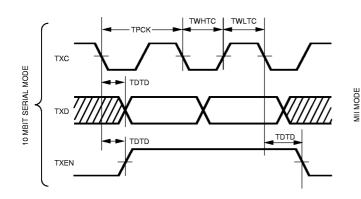

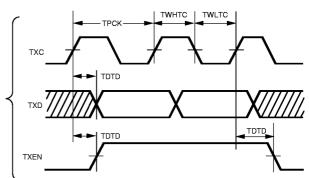

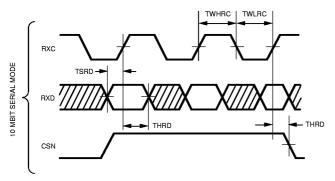

- 6.0 Ethernet Transmit and Receive Interface Timing

- 6.01 Ethernet Transmit Interface Timing 6.02 Ethernet Receive Interface Timing

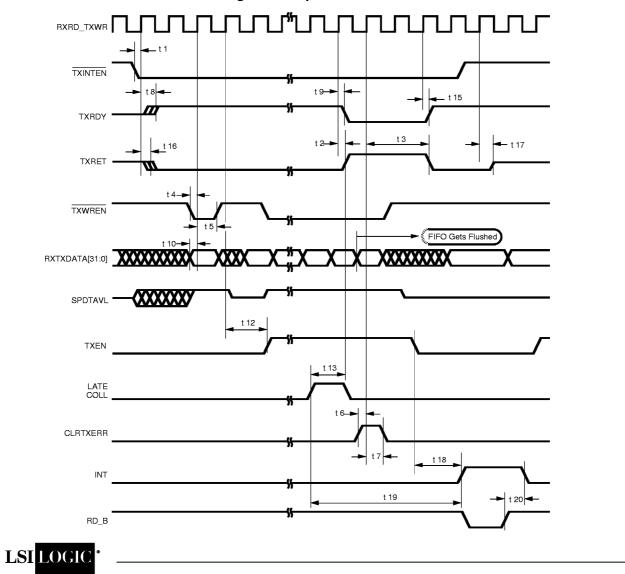

- 7.0 Transmit Data Interface Timing

7.01 Transmit Data Interface Write Timing 1 7.02 Transmit Data Interface Write Timing 2

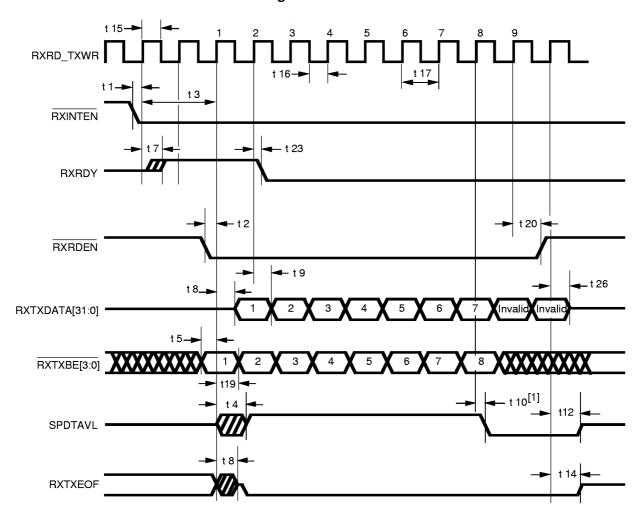

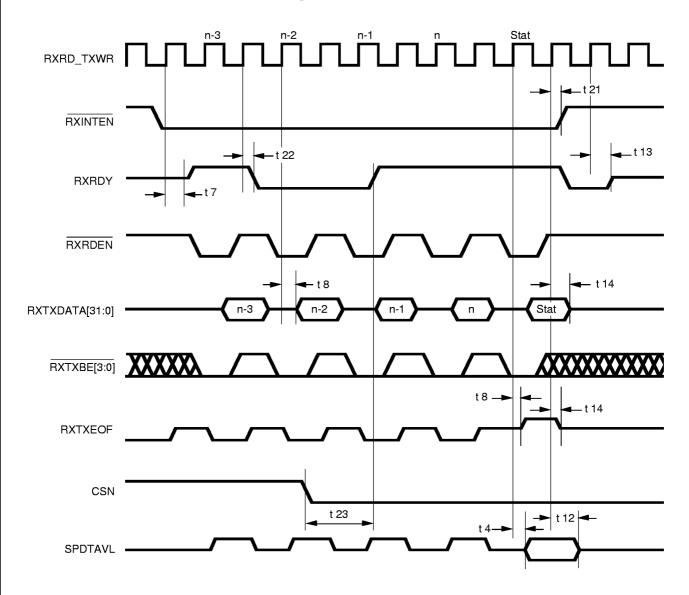

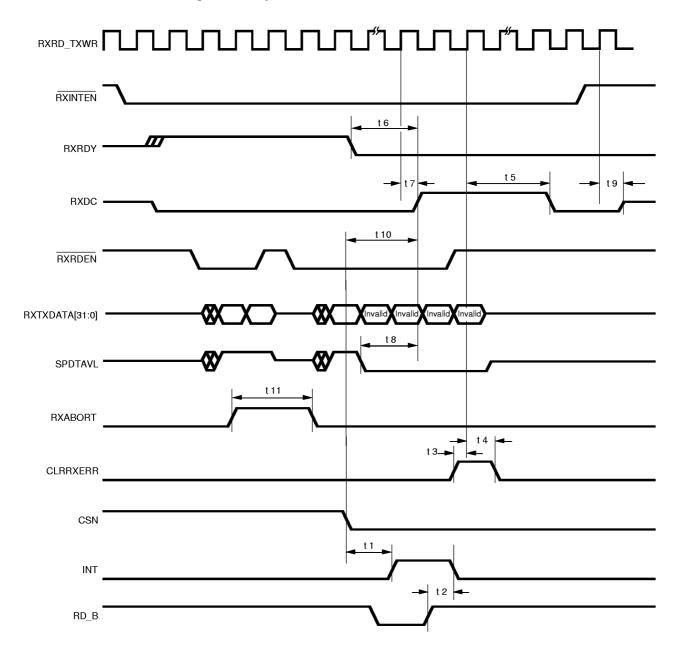

- 8.0 Receive Data Interface Timing

- 8.01 Receive Data Interface Read Timing 1 8.02 Receive Data Interface Read Timing 2

- 9.0 Transmit Data Interface Timing on Exception Conditions

- 10.0 Receive Data Interface Timing on Exception Conditions

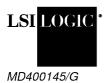

- 11.0 Reset Timing

## Illustrations

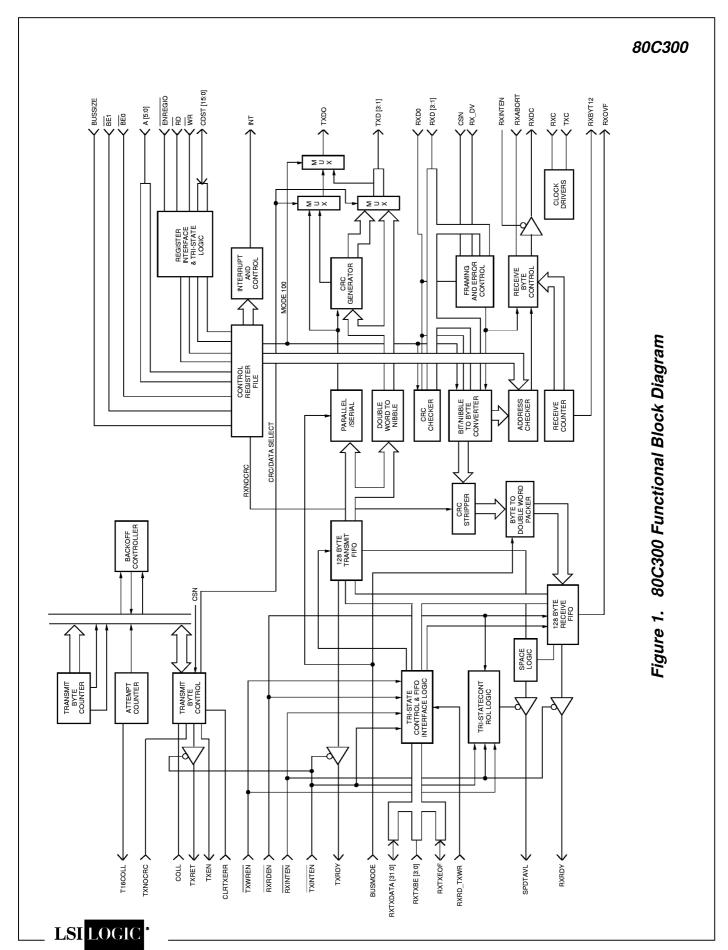

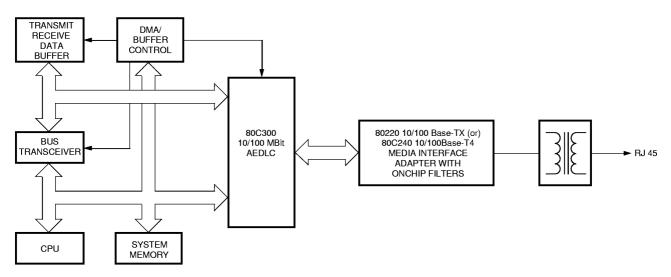

- Figure 1. Functional Block Diagram of the 80C300

- Figure 2. 80C300 Pin Configuration

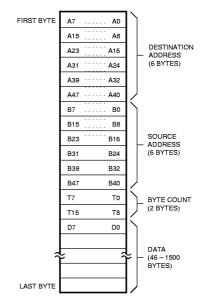

- Figure 3. Typical Application Example

## 1.0 PIN DESCRIPTION

| Pin                     | Pin Name       | I/O  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|-------------------------|----------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Chip Register Interface |                |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

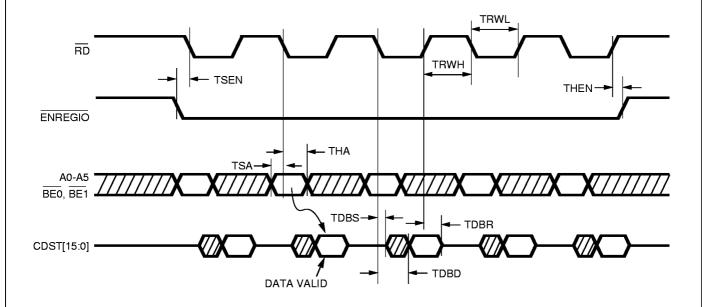

| 32                      | ENREGIO        | I    | This active low input enables the chip for register operations. This input must be low before any registers can be written or read.                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| 3                       | WR             | I    | Within the chip, this input acts as a write strobe for one of the registers and the register is addressed through the A[5:0] address inputs. The data being written appears on the CDST[15:0] data lines and must be set up relative to the rising edge of the write strobe. This input is active low.                                                                                                                                                                                   |  |  |  |  |  |

| 4                       | RD             | I    | This input acts as a read strobe for one of the registers and the register is addressed through the A[5:0] address inputs. When the read strobe is active low, the output drivers for CDST[15:0] data bus are enabled. Valid register data appears on the data bus a specified time before the rising edge of the read strobe.                                                                                                                                                           |  |  |  |  |  |

| 7-12                    | A[5:0]         | I    | These inputs are the address lines used to select which register is being read or written.                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| 33                      | BUSSIZE        | ı    | This input when HIGH sets the register interface of the 80C300 to 16-bit mode and when LOW to 8-bit mode. In 8-bit mode only CDST[7:0] of the CDST data bus is used for register accesses.                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| 6, 5                    | BE[1:0]        | Ι    | These inputs are active LOW byte enables to enable byte wide register accesses when the 80C300's register interface is in 16-bit mode.                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| 13-17<br>20-25<br>27-31 | CDST[15:0]     | I/O  | These bidirectional lines carry register data to or from the internal registers of the chip.  These lines are nominally high impedance until their output drivers are enabled by the RD and ENREGIO input pins being driven low.                                                                                                                                                                                                                                                         |  |  |  |  |  |

| 59                      | INT            | 0    | This output is driven high by a variety of transmit and receive interrupt conditions. It remains high until the status register containing the reason for the interrupt is read.                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| 62                      | RESET          | I    | This input is an active low asynchronous chip reset. After reset, all registers except the Hash and Station Address registers are reset to zero, all FIFOs are cleared, all counters are reset to zero.                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| Receiv                  | e and Transmit | FIFO | Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| 34                      | BUSMODE        | I    | This input when HIGH sets the FIFO interface to Big Endian mode. In this mode data written to the transmit FIFO is transmitted most significant byte first. When this pin is LOW, Little Endian transmit order is used.                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| 43                      | RXINTEN        | I    | This is an active low input that acts as a chip enable to enable the receiver interface. Driving this pin active, enables the output drivers for the RXDC, RXRDY pins. Also, this pin must be driven active before receive FIFO reads can be performed.                                                                                                                                                                                                                                  |  |  |  |  |  |

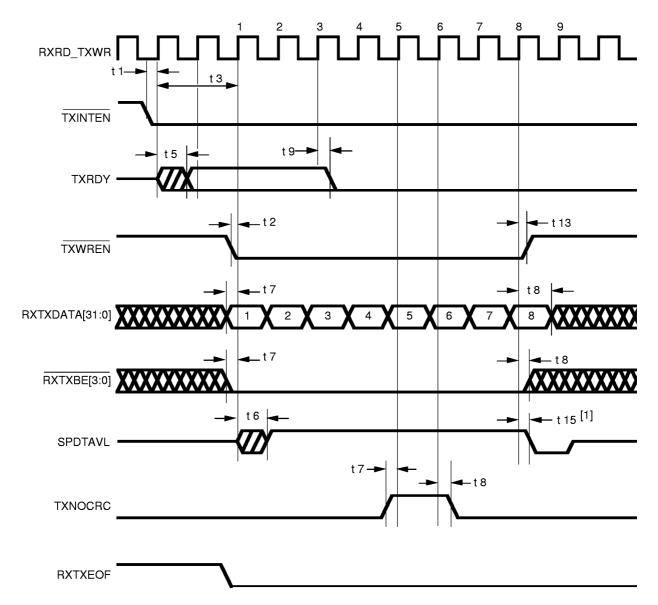

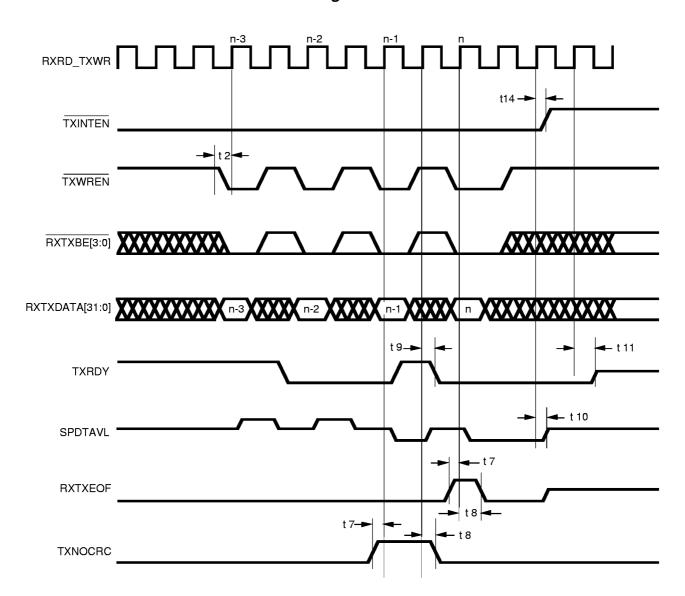

| 44                      | TXINTEN        | I    | This is an active low input that acts as a chip enable to enable the transmitter interface. Driving this pin active enables the output drivers for the TXRET, TXRDY pins. Also, this pin must be driven active before transmit FIFO writes can be performed.                                                                                                                                                                                                                             |  |  |  |  |  |

| 46                      | RXRDEN         | I    | This is an active low input that, when driven active with the RXINTEN pin, enables read operations from the receive FIFO within the chip.                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| 47                      | TXWREN         | I    | This is an active low input that, when driven active with the TXINTEN pin, enables write operations to the transmit FIFO within the chip.                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| 45                      | RXRD_TXWR      | I    | This is the system clock acting as the chip's read/write strobe to receive/transmit FIFO. With the TXINTEN and TXWREN inputs active low, this input becomes the write strobe for writing transmit data to the chip's transmit FIFO. Similarly, with the RXINTEN and RXRDEN inputs active low, this input becomes the read strobe for reading receive data from one of the chip's receive FIFO. This input must be connected to a continuous clock whose maximum frequency can be 33 MHz. |  |  |  |  |  |

| Pin                                                    | Pin Name         | I/O      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------------------------------|------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Receive a                                              | and Transmit FIF | O Interf | ace                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 35,36,41<br>42                                         | RXTXBE [3:0]     | I        | These are active low inputs that determine which bytes of the double word for a receive FIFO read are driven with valid data or which bytes of a double word being written to a transmit FIFO contain valid data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 53                                                     | TXRDY            | 0        | This is an active high tristate output. When enabled, this output functions as a flag that indicates whether the transmit FIFO has enough space available to meet the threshold value programmed in the FIFO threshold register. When enabled, a high value on the output indicates that the transmit FIFO has greater than or equal to the threshold number of double word spaces available in the FIFO and a low value indicates it does not. The tristate driver for the output is enabled by a low value on the TXINTEN input pin.                                                                                                                                                          |

| 54                                                     | RXRDY            | 0        | This is an active high tristate output. When enabled, this output functions as a flag that indicates whether the receive FIFO has enough data available to meet the threshold value programmed in the FIFO threshold register. When enabled, a high value on the output indicates that the receive FIFO has greater than or equal to the threshold number of double words available in the FIFO or has a completed receive packet in the FIFO as indicated by the packets status double word being in the FIFO. The tristate driver for the output is enabled by a low value on the RXINTEN input pin.                                                                                          |

| 50                                                     | SPDTAVL          | 0        | This is an active high output that can be used for validating reads from the receive FIFO during a read operation and preventing over writes to the transmit FIFO during a write operation. For further details, please refer to the Transmit Data Write Timing and the Receive Data Read Timing diagrams.                                                                                                                                                                                                                                                                                                                                                                                      |

| 51                                                     | RXTXEOF          | I/O      | This is a bidirectional pin that is used to signal the last double word of a transmit or receive packet. During receive FIFO reads this pin is enabled as an output and when detected high indicates that the last double word, and or the status double word, of a receive packet has been read from the receive FIFO. During transmit FIFO writes this pin is an input and when asserted high during a write, it indicates that this is the final double word of a transmit packet. In the transmit FIFO write case, the value of this signal is stored as the 33rd bit in the FIFO. In the receive FIFO read case, the value of this signal is read out as the 33rd bit of the receive FIFO. |

| 52                                                     | TXNOCRC          | I        | This active high input is used to control appending of a CRC to a transmit packet. A transmit packet can be made to exclude appending a CRC value if this input is held high during the first double word write of transmit data to the transmit FIFO.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

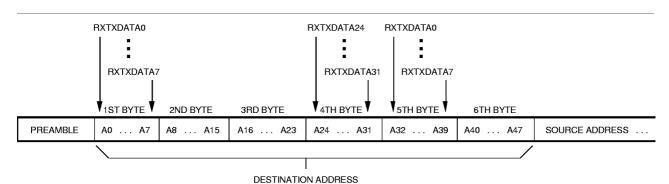

| 67-71<br>73-77<br>79-83<br>85-89<br>91-100<br>105, 106 | RXTXDATA[31:0]   | I/O      | This is the bidirectional 32 bit data bus for reads or writes to the chip's receive or transmit FIFOs. For receive FIFO reads, it is enabled as an output with the assertion of the RXINTEN, RXRDEN, and a low value on the RXRD_TXWR input strobe. Otherwise, it is used as an input.                                                                                                                                                                                                                                                                                                                                                                                                          |

| Pin     | Pin Name         | I/O     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------|------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transmi | t and Receive Ex | ception | Indicators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 61      | TXRET            | 0       | This is an active high tristate output. This output pin is driven by tristate drivers enabled by an active low being driven onto the TXINTEN input pin. Once enabled, a high value on this input indicates that the chip could not complete transmission of a packet due to one of the following conditions and that a retransmission of the packet is requested:                                                                                                                                                                                               |

|         |                  |         | A late collision occurred during transmission.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|         |                  |         | <ol><li>Carrier sense never went high or dropped out<br/>during transmission.</li></ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|         |                  |         | 3. During a transmission attempt, a transmit FIFO underflow error occurred.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         |                  |         | <ol> <li>16 attempts to transmit the packet all resulting<br/>in transmit collisions.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|         |                  |         | Internally, the TXRET signal will remain high until it is cleared by the CLRTXERR pin, (See the text on clearing error conditions). As long as the internal TXRET signal remains high, the transmit FIFO will remain cleared and no new transmissions can occur.                                                                                                                                                                                                                                                                                                |

| 60      | T16COLL          | 0       | This is an active high tristate output. This output pin is driven by tristate drivers enabled by an active low being driven onto the TXINTEN input pin. Once enabled, a high value on this input indicates that 16 attempts to transmit a packet failed due to 16 collisions. This output is cleared the same way the TXRET is cleared by using the CLRTXERR input.                                                                                                                                                                                             |

| 55      | RXDC             | 0       | This is an active high tristate output. This pin driven by tristate drivers enabled by a low value being driven onto the RXINTEN input pin. Once enabled, a high value on the input indicates that the chip discarded reception of a packet due to one of the possible receive discard conditions. Internally, a RXDC signal will remain high until it is cleared by the CLRRXERR pin, (See the text on clearing error conditions). As long as the internal RXDC signal remains high, the receive FIFO will remain cleared and no new packets will be received. |

| Special | Purpose Pins     |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 49      | CLRTXERR         | I       | This active high input is used to clear transmit retry flags within the chip. See the "Detecting and Clearing a Transmit Retry Condition" section for how this input is used.                                                                                                                                                                                                                                                                                                                                                                                   |

| 48      | CLRRXERR         | I       | This active high input is used to clear Receive Discard flags within the chip. See the "Detecting and Clearing a Receive Discard Condition" section for how this input is used.                                                                                                                                                                                                                                                                                                                                                                                 |

| 57      | RXABORT          | I       | This input when pulsed high causes the chip to abort reception of a receive frame and clear the Receive FIFO. It can be asserted at any time during the reception of a frame.                                                                                                                                                                                                                                                                                                                                                                                   |

| 108     | ADUPLX           | I       | This active low input is used to set the chip into Full Duplex Mode. In this mode the transmitter will not defer to an active carrier sense signal.                                                                                                                                                                                                                                                                                                                                                                                                             |

| 56      | RXBYT12          | 0       | This is an active high output that when high indicates that at least the first 12 bytes of a packet are available within the receive FIFO. Internally this signal is reset to 0 upon Carrier Sense, or Receive Data Valid in MII mode, going low. This is synchronized with respect to the high going edge of the RXRD_TXWR clock.                                                                                                                                                                                                                              |

| 58      | RXOVF            | 0       | This is an active high output that when pulsed high indicates that the receive FIFO overflowed. This signal is pulsed high for one byte time, (two RXC clock periods in MII mode or eight RXC clock periods in 10 Mbit/sec serial mode).                                                                                                                                                                                                                                                                                                                        |

| 126     | DAISY_OUT        | NC      | This pin should not be connected to any signals externally                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Pin       | Pin Name                          | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

|-----------|-----------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Media Ind | Media Independent Interface (MII) |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 117       | TXC                               | I   | This is the transmit clock input for the chip. In standard 10 Mbit/sec Serial Mode, this is a 10 Mhz, 50% duty cycle transmit clock used to synchronize the transmit data from the chip to the encoder. In this mode, transmit data appears serially on the TXD0 output and all transitions of transmit data and the TXEN output occur from the falling edge of the clock. In MII mode, this is a 2.5/25 Mhz, 50% duty cycle clock, and the transmit data appears on the TXD0 through TXD3 outputs. In this mode transitions of transmit data and the TXEN output occur from the rising edge of the clock. |  |  |  |  |  |  |

| 112       | RXER                              | I   | This input is internally connected to an 8 bit counter used for counting symbol errors coming in from the PHY.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| 118-121   | TXD[3:0]                          | 0   | In standard 10 Mbit/sec Serial Mode, TXD0 is the serial transmit data output from the chip to the encoder. In MII mode, these outputs drive a nibble of transmit data every leading edge of the TXC clock from the chip to the encoder.                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| 122       | TXEN                              | 0   | This output from the chip is used to activate the encoder. In standard 10 Mbit/sec Serial Mode, it becomes active when the first bit of the Preamble is transmitted and inactive when the last bit of the frame is transmitted. In 100 Mbit/sec mode, this output becomes active when the first nibble of the Preamble is transmitted and inactive when the last nibble of the frame is transmitted. This output is active high.                                                                                                                                                                           |  |  |  |  |  |  |

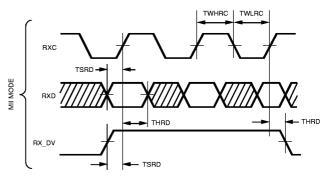

| 109       | RXC                               | I   | In standard 10Mbit/sec Serial Mode, this input is a 10Mhz, 50% duty cycle nominal receive clock which is used to synchronize incoming data from the decoder to the chip. In 10Mbit/sec Serial Mode CSN and RXD0 are assumed to transition from the leading edge of this clock. In MII mode this clock is a 2.5/25 Mhz, 50% duty cycle receive clock that synchronizes incoming nibble wide data from the decoder to the chip. In MII mode data and the RXDV signal are assumed to transition from the falling edge of the clock.                                                                           |  |  |  |  |  |  |

| 113-116   | RXD[3:0]                          | ı   | In standard 10 Mbit/sec Serial Mode, RXD0 is the serial input data to the chip from the decoder. In this mode pins RXD[3:1] can have any logic value but must not be left floating. In MII mode, these inputs are driven with a nibble of receive data every falling edge of the RXC clock from the encoder to the chip.                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| 111       | CSN                               | ı   | This is the carrier sense input which indicates there is traffic on the transmission medium. Carrier sense becomes active with the first bit of the Preamble received, and inactive one bit time after the last bit of the frame is received. This is an active high input.                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| 110       | RX_DV                             | I   | In MII mode this input is receive data valid. Receive data valid becomes active with the first nibble of synchronized and decoded Preamble or SFD appearing on the RXD[3:0] lines and goes inactive one clock time after the last nibble of the frame is received. In 10 Mbit/sec Serial Mode this input is not used and can have any logic value but must not be left floating. This is an active high input.                                                                                                                                                                                             |  |  |  |  |  |  |

| 123       | COLL                              | I   | This input indicates that a transmission contention has occurred on the transmission medium. Collision is indicated to the chip by an active high pulse on the COLL input and is automatically reset at the end of the JAM sequence transmission.                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| Pin                                                                               | Pin Name             | I/O | Description                                                                                                                                      |  |  |  |  |  |

|-----------------------------------------------------------------------------------|----------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Managen                                                                           | Management Interface |     |                                                                                                                                                  |  |  |  |  |  |

| 125                                                                               | MDIC                 | 0   | This is the clock source from the 80C300 to the PHY and acts as a timing reference for transfer of information on the MDIO signal.               |  |  |  |  |  |

| 124                                                                               | MDIO                 | I/O | This is a bidirectional pin used to transfer data to and from the PHY. Data is transferred out to the PHY synchronously with respect to the MDC. |  |  |  |  |  |

| 1, 19,<br>37, 39<br>40, 64<br>84, 102                                             | V <sub>DD</sub>      | _   | Positive Supply 5V ± 5%                                                                                                                          |  |  |  |  |  |

| 2, 18<br>26, 38<br>63, 65<br>66, 72<br>78, 90<br>101, 103<br>104, 107<br>127, 128 | GND                  | _   | Ground 0 Volts                                                                                                                                   |  |  |  |  |  |

MD400145/G

## 2.0 Introduction

The 80C300 is an Ethernet Media Access Controller (MAC) with a rich set of operating modes and features. It is manufactured as a single-chip VLSI device to simplify and enhance the development of multi-port Ethernet embedded systems such as bridges, switches, and routers.

Two input/output paths are provided for interfacing to physical layer devices. In IEEE-standard MII mode, the 80C300 provides an industry standard interface supporting both 10Mbit/sec and 100Mbit/sec data rates. This interface will directly connect with physical layer devices such as SEEQ's 80C240 100Base-T4 PHY without additional glue logic. In Serial mode, the chip supports the standard Ethernet CSMA/CD protocol via a serial interface for transmit and receive data. Support for both Half and Full Duplex operation is provided in all interface modes.

The 80C300 is feature compatible with SEEQ's 84C300A Ethernet Media Access Controller. These features include: 64 bit Multicast filter, Transmit no CRC, Transmit no Preamble, Transmit Packet Autopadding, Receive CRC, Receive Own Transmit Disable, Receive Group Address Mode, Fast Receive Discard Mode, and Full Duplex Mode. Additionally, the 80C300 supports: programmable defer time between transmit packets, appending value of FCS on a packet-by-packet basis, and pin-controllable per-port receive packet abort.

A high-bandwidth universal system interface is provided which is compatible with many microprocessor or system busses, easing the integration of the 80C300 into many system architectures. Its 32-bit data path width is provided to provide the bandwidth necessary to maintain Full Duplex wire speed communications. Two 128 byte FIFOs are provided to ease bus multiplexing and interfacing to different clock domains.

## 3.0 Functional Description

## **NOTE:** Field length in bytes in parentheses.

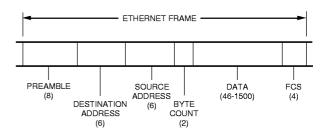

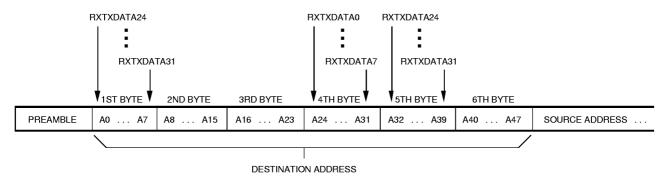

#### 3.1 FRAME FORMAT

On an Ethernet communication network, information is transmitted and received in packets or frames. An Ethernet frame consists of a preamble, two address fields, a byte-count field, a data field and a frame check sequence (FCS). Each field has a specific format which is described in detail below. An Ethernet frame has a minimum length of 64 bytes and a maximum length of 1518 bytes exclusive of the preamble. The Ethernet frame format is shown in the figure above.

Typical Frame Buffer Format for Byte-Organized Memory

**Preamble:** The preamble is a 64-bit field consisting of 62 alternating "1"s and "0"s followed by a "11" End-of-Preamble indicator.

**Destination Address:** The Destination Address is a 6-byte field containing either a specific Station Address, a Broadcast Address, or a Multicast Address to which this frame is directed.

**Source Address:** The Source Address is a 6-byte field containing the specific Station Address from which this frame originated.

Byte-Count Field: The Byte-Count Field consists of two bytes providing the number of valid data bytes in the Data Field, 46 to 1500. This field is uninterpreted at the Data Link Layer, and is passed through the EDLC chip to be handled at the Client Layer.

**Data Field:** The Data Field consists of 46 to 1500 bytes of information which are fully transparent in the sense that any arbitrary sequence of bytes may occur.

Frame Check Sequence: The Frame Check Sequence (FCS) field is a 32-bit cyclic redundancy check (CRC) value computed as a function of the Destination Address Field, Source Address Field, Type Field and Data Field. The FCS is appended to each transmitted frame, and used at reception to determine if the received frame is valid.

## 3.2 PACKET TRANSMISSION

The transmit data stream consists of the Preamble, four information fields, and the FCS which is computed in real time by the chip and automatically appended to the frame at the end of the data. The Preamble is also generated by the chip and transmitted immediately prior to the Destination Address. Destination Address, Source Address, Type Field and Data Field are prepared in the buffer memory prior to initiating transmission. The chip encapsulates these fields into an Ethernet frame by inserting a preamble prior to these information fields and appending a CRC after the information fields. The chip can be programmed to exclude inclusion of the preamble and/or the FCS from the transmit data stream. In this case, it is assumed that the preamble and FCS are provided as part of the data written to the channel.

### 3.2.1 Controlling Transmit Packet Encapsulation

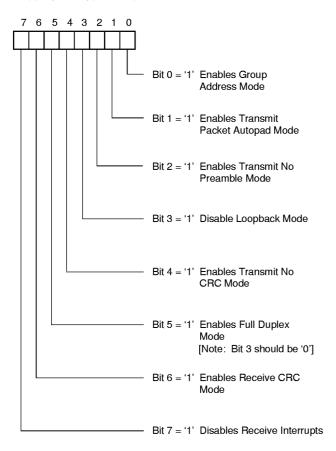

As was mentioned in the previous paragraph, the chip can be programmed for exclusion of the FCS and/or the preamble when transmitting a packet. To program the chip for transmitting a packet without creating a preamble, bit #2 of the Configuration Register #1 should be written high. Once this bit is set, all packets transmitted by the chip will not include a preamble pattern unless it is part of the data written to the transmit FIFO by the system. Similarly, the chip can be prevented from appending an FCS value to a packet by setting bit #4 of the Configuration Register #1. As long as this bit is high, any packet transmitted will not include an FCS value unless it is written as part of the transmit data written to the transmit FIFO. Appending of a FCS value can be controlled on a packet per packet basis by using the TXNOCRC pin as long as the TXNOCRC TX-RX Configuration register bit has not been set high. If the TXNOCRC pin is held high (or) if the TXNOCRC bit is set anytime during the duration of a packet write to the transmit FIFO, that particular packet will not be appended with a CRC value.

| Transm     | it No CRC                | CRC Appendage |

|------------|--------------------------|---------------|

| H/W Pin 52 | S/W Bit 4<br>of Config 1 | To the Packet |

| 0          | 0                        | Yes           |

| 0          | 1                        | No            |

| 1          | 0                        | No            |

| 1          | 1                        | No            |

Please note that both the H/W pin and the software bit should be kept deasserted during the entire duration of the packet write to the transmit FIFO in order to transmit a packet with CRC.

# 3.2.2 Transmission Initiation in Full Duplex and CSMA/CD Networks

Packet transmission begins with one of the following conditions:

- Data in the transmit FIFO meets or exceeds a userdefined threshold value or,

- 2. An EOF is asserted with the last data word written into the transmit FIFO.

The transmit threshold value is controlled by programming bits 7 through 4 of the Configuration Register #3. The default value is 0 (zero), which enables the MAC to begin packet transmission with as little as one double word in the FIFO. The threshold, measured in double words, is equal to the number programmed into Transmit Control Register times 2. Thus, if the upper four bits of the register contain the value 3hex, then the transmission is deferred until there are at least 6 double words of data in the FIFO.

Packet transmission initiation is also dependent upon whether the 80C300 is in Full Duplex or CSMA/CD mode. If the Chip is in CSMA/CD mode, transmission may also be prevented or delayed due to activity on the shared network medium. If the network is not busy due to other data traffic,

transmission will begin after the appropriate defer time (from end of previous traffic) has expired. Otherwise, transmission is delayed until after current data transfers are complete, and the defer time requirements have been satisfied. Following the IEEE 802.3 specifications, the minimum defer time is split into two periods. The beginning of the defer time occurs upon the transmitter sensing carrier sense going LOW. Once this case occurs then if carrier sense is reasserted during the 1st period of the defer time, the transmitter will reset its defer time counter and restart the total defer timeout period from 0. If carrier sense is reasserted during the 2nd period of the total defer time interval, the transmitter will ignore carrier sense and start transmission as soon as the defer time is met. The 1st period of the total defer time is programmable through use of the transmit defer register. The second period of the defer time interval is either 3.2 μs or 0.32 μs depending on whether the chip is in 10Mbit/sec or 100Mbit/sec mode. The total default defer time for 10Mbit/sec serial mode is 9.6 µs as measured from TXEN going LOW to TXEN going High assuming the transmit defer register is at 00 hex and assuming that the TXEN going LOW to CSN going LOW delay of the physical device is less than 5 TXC clock periods. When the chip is in Full Dulex mode, transmission of data onto the network occurs independent of whether carrier sense indicates a busy network condition or not.

Because of the variability in delays given for TXEN going LOW to CSN going LOW for different 100Mbit/sec physical devices, the default defer time in 100 Mbit/sec MII mode has been set assuming full duplex conditions where carrier sense is not monitored by the transmitter. In this case the default is 0.96 µs from TXEN going LOW to TXEN going HIGH. To adjust the defer time to some other value, the programmable defer register can be set using the formulas given in the section describing the defer register. When transmission begins, the chip activates the transmit enable (TXEN) line concurrently with the transmission of the first bit, or first nibble in the MII case, of the Preamble and keeps it active for the duration of the transmission.

#### 3.2.3 Collision on transmit

On the occurrence of a transmit collision condition that does not represent the 16th transmission attempt for the packet or does not occur after 64 byte times into the transmission, the controller will automatically attempt to retransmit the packet. First, the controller will halt the transmission of data from the FIFO and begin transmitting a Jam pattern consisting of 5555555 hex. The controller will also reset the Transmit FIFO read address pointer back to the beginning of the transmit packet within the FIFO. At the end of transmitting the Jam pattern the controller will then begin the Backoff wait period. Once the backoff period is finished, the controller will automatically retransmit the packet. If a packet reaches 16 retransmission attempts without success due to collisions, or if a collision occurs later than 64 Byte times after the beginning

of a transmission, this is considered to represent a serious network error. Upon any one of these two error conditions occurring the Transmit FIFO will be cleared and the TXRET output will be driven HIGH. If the TXRET signal was driven HIGH due to 16 transmission attempts, the T16COLL signal will also be driven HIGH. When either of the two above error conditions occurs, retransmission of any packets that were in the transmit FIFO requires first clearing the TXRET error condition and then reloading the packet or packets in the Transmit FIFO.

Scheduling of retransmission is determined by a controlled randomization process called Truncated Binary Exponential Backoff. The chip waits a random interval between 0 and  $2^{\rm K}$  slot times (51.2  $\mu$ s per slot time for 10 Mbit Ethernet or 5.12  $\mu$ s per slot time for 100 Mbit Ethernet) before attempting retransmission, where "K" is the current transmission attempt number (not to exceed 10).

#### TXRET conditions that will reset the backoff counter

Case 1: During packet transmission, a carrier sense dropout occurs but no collision occurs.

Case 2: 16 attempts to transmit a packet failed due to collisions.

## 3.2.4 Transmit Termination Conditions

The chip will terminate transmission under the following conditions.

Normal: The frame has been transmitted successfully without contention. Loading of the last data byte into a Transmit FIFO is signaled to the chip by activation of its RxTxEOF signal concurrently with the last double word of data loaded into the Transmit FIFO. This line acts as the thirty-third bit in the Transmit FIFO. After the last valid byte of the last double word has been transmitted, if the chip is not in Transmit No CRC mode, then the CRC is appended and transmitted concluding frame transmission. The Transmission Successful bit of the Transmit Status Register will be set by a normal termination.

Collision: Transmission attempted by two or more Ethernet nodes. The Jam sequence is transmitted, the Collision status bit is set, transmit Collision Counter is updated, the Backoff interval begun, and the Transmit FIFO address is set to point to the beginning of the packet for retransmission automatically.

**Underflow:** Transmit data is not ready when needed for transmission. Once transmission has begun, the chip on average requires one transmit double word every 3200 ns for 10 Mbit Ethernet or 320 ns for 100 Mbit Ethernet in order to avoid Transmit FIFO underflow (starvation). If this condition occurs, it terminates the transmission, issues a TXRET signal, and sets the Transmit-Underflow status bit.

Figure 3. Typical Application Example

16 Transmission Attempts: If a Collision occurs for the sixteenth consecutive time, the 16-Transmission-Attempts status bit is set, the Collision status bit is set, the TXRET and TI6COLL signals are generated, and the Backoff interval is begun. The counter that keeps track of the number of collisions is modulo 16 and therefore rolls over on the 17th collision. The Transmit Attempt Register described on page 30 allows the user to determine how many transmission attempts were required to successfully transmit the packet.

Late Collision: If a Collision occurs greater than 64 byte times after the transmission begins, this is considered a late collision error. Upon this condition, the transmission is terminated, the TXRET output is driven HIGH, and the late collision status bit is set.

At the completion of every transmission or retransmission, new status information is loaded into the Transmit Status Register. Dependent upon the bits enabled in the Transmit Command Register, an interrupt will be generated for the just completed transmission.

# 3.2.5 Error Conditions That Will Cause TXRET to go HIGH

Detection of a HIGH value on the TXRET pin indicates that the chip could not complete transmission of a packet due to one or more of the following conditions:

- A transmit FIFO underflow occurred while transmitting the packet.

- 2. A late collision occurred while transmitting the packet.

- 3. Carrier sense never went active during transmission or went from an active to inactive state during transmission.

4. 16 attempts to transmit the packet all resulting in transmit collisions.

Any of the above conditions will cause the chip to flush the transmit FIFO and initiate a transmit retry request. With initiation of a transmit Retry Request, the TXRDY output will go low and stay low until the TXRET flag is cleared. Similar to the receive discard signal, the transmit retry signal going to the external TXRET pin is latched upon a transmit retry condition and held high until cleared. Until the transmit retry signal is cleared, no new transmit packets can be written to the transmit FIFO.

# 3.2.6 Detection and Clearing a Transmit Retry Condition

To enable the output driver for the TXRET pin, the TXINTEN input is driven low. Once a Tx retry condition is detected, the internal Tx retry signal should be cleared. Then by driving the TXINTEN input low and then pulsing the CLRTXERR input high for a minimum of one RXRD\_TXWR clock cycle, the TXRET signal is cleared. The TXINTEN input must not change during the high time of the CLRTXERR input.

#### 3.3 Packet Reception

The chip continuously monitors the network. When activity is recognized via the Carrier Sense (CSN) signal in 10 Mbit/sec Serial Mode, or through the Receive Data Valid (RX\_DV) signal in MII mode, the chip will then synchronize itself to the incoming data stream through recognition of the Start Frame Delimiter (SFD) at the end of Preamble. The destination address field of the frame is then examined. Depending on the Address Match Mode specified, the chip will either recognize the frame as being addressed to itself in a general or specific fashion or abort the frame reception.

#### 3.3.1 Preamble Processing

The chip recognizes activity on the Ethernet via its Carrier Sense (CSN) line in 10 Mbit/sec Serial Mode or through its Receive Data Valid (RX\_DV) line in MII mode. In 10 MBit/ sec Serial Mode, the end of preamble is detected by a double 1 serial receive data pattern preceded by 6 bits of alternating 1's and 0's. In MII mode, the end of preamble is recognized by the following nibble pattern:

|      | Logic Values |

|------|--------------|

| RXD3 | 0 1          |

| RXD2 | 1 1          |

| RXD1 | 0 0          |

| RXD0 | 1 1          |

In 10 MBit/sec Serial Mode, detection of a double 0 pattern 16 bit times after CSN goes high and before a proper Start Frame Delimiter pattern is received, will prevent reception of the packet by the receiver. In MII mode, when RX DV goes high the RXD[3:0] lines must be driven with 0 or more bytes of proper preamble pattern followed by one byte of proper SFD.

### 3.3.2 Address Matching

Ethernet addresses consist of two 6-byte fields. The first bit of the address signifies whether it is a Station Address or a Multicast/Broadcast Address.

| First Bit | Address                                  |

|-----------|------------------------------------------|

| 0         | Station Address (Physical)               |

| 1         | Multicast/Broadcast Address<br>(logical) |

Address matching occurs as follows:

Station Address: All destination address bytes must match the corresponding bytes found in the Station Address Register. If Group Address mode is enabled, the last 4 bits of the station address are masked out during address matching.

After computing the FCS on the first six bytes of the address field (Destination address), the chip uses bits 0 thru 5 as an address to its Multi-cast address filter register. Bit 0 of the FCS is assumed to be where receive data enters the FCS generation circuitry. If the corresponding bit addressed in the Multicast address filter register is a '1' the chip will receive the frame, otherwise it will discard the frame. Addressing of the Multicast address filter register occurs using bits 0 thru 2 to determine which byte is

selected and bits 3 thru 5 to determine which bit according to the following tables:

| FCS Bits<br>0 1 2 | Byte Selected | FCS Bits<br>3 4 5 | Bit Selected |

|-------------------|---------------|-------------------|--------------|

| 0 0 0             | Byte 0        | 0 0 0             | Bit 0        |

| 0 0 1             | Byte 1        | 0 0 1             | Bit 1        |

| 0 1 0             | Byte 2        | 0 1 0             | Bit 2        |

| 0 1 1             | Byte 3        | 0 1 1             | Bit 3        |

| 1 0 0             | Byte 4        | 100               | Bit 4        |

| 1 0 1             | Byte 5        | 1 0 1             | Bit 5        |

| 1 1 0             | Byte 6        | 1 1 0             | Bit 6        |

| 1 1 1             | Byte 7        | 1 1 1             | Bit 7        |

Multicast Address: If the first bit of the incoming address is a 1 and the chip is programmed to accept Multicast Addresses without using Hash filtering, the frame is received. The chip can also be programmed to use the hash filter for determining acceptance of multicast addresses.

Broadcast Address: The six incoming destination address bytes must all be FF hex. If the chip is programmed to accept Broadcast or Multicast Addresses, the frame will be received.

If the incoming frame is addressed to the chip specifically (Destination Address matches the contents of the Station Address Register), or is of general or group interest (Broadcast or Multicast Address), the chip will pass the frame exclusive of Preamble and FCS to the CPU buffer and indicate any error conditions at the end of the frame. If, however, the address does not match, as soon as the mismatch is recognized, the chip will terminate reception and discard the packet. All packet discards due to address mismatches are handled within the chip and will not cause the RXDC pin to go HIGH. This is true because determination of an address mismatch condition occurs before any portion of a receive packet is written to the receive FIFO.

The chip may be programmed via the Match Mode bits of the Receive Command Register to ignore all frames (Disable Receiver), accept all frames (Promiscuous mode), accept frames with the proper Station Address or the Broadcast Address (Station/Broadcast), or accept all frames with the proper Station Address, the Broadcast Address, or all Multicast Addresses (Station/Broadcast/ Multicast).

## 3.6.1 Internal Channel Register Addressing Table

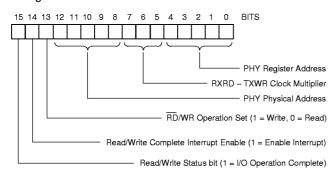

|           |            |       |       |       |           | Register Description <sup>[2]</sup>                        |                                    |  |  |  |

|-----------|------------|-------|-------|-------|-----------|------------------------------------------------------------|------------------------------------|--|--|--|

|           |            |       |       |       |           | BUSSIZE = 1, BE1 = 0, BE0 = 0                              |                                    |  |  |  |

| Config. 3 | R          | egist | er Ad | ddres | s         | BUSSIZE = 1, BE1 = 0, BE0 = 1                              | BUSSIZE = 1, BE1 = 1, BE0 = 0      |  |  |  |

| Bit 0     | <b>A</b> 5 | Α4    | А3    | A2    | <b>A1</b> | BUSSIZE = 0, A0 = 1                                        | BUSSIZE = 0, A0 = 0                |  |  |  |

| 0         | 0          | 0     | 0     | 0     | 0         | Transmit Late Collision Counter Transmit Excessive Defer C |                                    |  |  |  |

| 0         | 0          | 0     | 0     | 0     | 1         | Over Flow Rx Error Counter Attempt Counter                 |                                    |  |  |  |

| 0         | 0          | 0     | 0     | 1     | 0         | Unused                                                     | Unused                             |  |  |  |

| Χ         | 0          | 0     | 0     | 1     | 1         | Tx Command/Status Register <sup>[1]</sup>                  | Rx Command/Status Register[1]      |  |  |  |

| Χ         | 0          | 0     | 1     | 0     | 0         | Hash Register 1                                            | Hash Register 0                    |  |  |  |

| Х         | 0          | 0     | 1     | 0     | 1         | Hash Register 3                                            | Hash Register 2                    |  |  |  |

| Х         | 0          | 0     | 1     | 1     | 0         | Hash Register 5                                            | Hash Register 4                    |  |  |  |

| Х         | 0          | 0     | 1     | 1     | 1         | Hash Register 7                                            | Hash Register 6                    |  |  |  |

| Х         | 0          | 1     | 0     | 0     | 0         | Product I.D. Register[4]                                   | Configuration Register #3          |  |  |  |

| Х         | 0          | 1     | 0     | 0     | 1         | Configuration Register #2[3]                               | FIFO Threshold Register            |  |  |  |

| Χ         | 0          | 1     | 0     | 1     | 0         | Defer Count Register                                       | Configuration Register #1          |  |  |  |

| 0         | 0          | 1     | 0     | 1     | 1         | Tot Rx Multicast Hi Byte                                   | Tot Rx Multicast Lo Byte           |  |  |  |

| 0         | 0          | 1     | 1     | 0     | 0         | CRC Error Counter Hi Byte                                  | CRC Error Counter Lo Byte          |  |  |  |

| 0         | 0          | 1     | 1     | 0     | 1         | Runt Frame Counter Hi Byte                                 | Runt Frame Counter Lo Byte         |  |  |  |

| 0         | 0          | 1     | 1     | 1     | 0         | Short Event Counter Hi Byte                                | Short Event Counter Lo Byte        |  |  |  |

| 0         | 0          | 1     | 1     | 1     | 1         | Tot Rx Broadcast Hi Byte                                   | Tot RX Broadcast Lo Byte           |  |  |  |

| 0         | 1          | 0     | 0     | 0     | 0         | Alignment Error Counter Hi Byte                            | Alignment Error Counter Lo Byte    |  |  |  |

| 0         | 1          | 0     | 0     | 0     | 1         | Receive Collision Counter Hi Byte                          | Receive Collision Counter Lo Byte  |  |  |  |

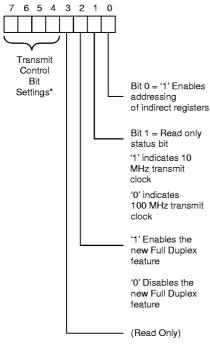

| 0         | 1          | 0     | 0     | 1     | 0         | MII Management Interface Data Re                           | gister                             |  |  |  |

| 0         | 1          | 0     | 0     | 1     | 1         | MII Management Interface Comma                             | nd/Status Register                 |  |  |  |

| 0         | 1          | 0     | 1     | 0     | 0         | Tot Rx Unicast Hi Byte                                     | Tot Rx Unicast Lo Byte             |  |  |  |

| 0         | 1          | 0     | 1     | 0     | 1         | Transmit Collision Counter Hi Byte                         | Transmit Collision Counter Lo Byte |  |  |  |

| 0         | 1          | 0     | 1     | 1     | 0         | ReceiveOversizeFrameCounter                                | Very Long Event Counter            |  |  |  |

| 0         | 1          | 0     | 1     | 1     | 1         | Tx Defer Count Hi Byte                                     | Tx Defer Count Lo Byte             |  |  |  |

| 0         | 1          | 1     | 0     | 0     | 0         | Tx Unicast Pkt Count Hi Byte                               | Tx Unicast Pkt Count Lo Byte       |  |  |  |

| 0         | 1          | 1     | 0     | 0     | 1         | TX Excessive Collision Counter                             | RXERR Error Counter                |  |  |  |

| 0         | 1          | 1     | 0     | 1     | 0         | Tx Broadcast Pkt Count Hi Byte                             | Tx Broadcast Pkt Count Lo Byte     |  |  |  |

| 0         | 1          | 1     | 0     | 1     | 1         | Tx Mcast Pkt Count Hi Byte                                 | Tx Mcast Pkt Count Lo Byte         |  |  |  |

| 0         | 1          | 1     | 1     | 0     | 0         | Rx Byt Count Byte 1                                        | Rx Byt Count Byte 0                |  |  |  |

| 0         | 1          | 1     | 1     | 0     | 1         | Rx Byt Count Byte 3                                        | Rx Byt Count Byte 2                |  |  |  |

| 0         | 1          | 1     | 1     | 1     | 0         | Tx Byt Count Byte 1                                        | Tx Byt Count Byte 0                |  |  |  |

| 0         | 1          | 1     | 1     | 1     | 1         | Tx Byt Count Byte 3                                        | Tx Byt Count Byte 2                |  |  |  |

| 1         | 0          | 0     | 0     | 0     | 0         | Station Addrs Reg 1                                        | Station Addrs Reg 0                |  |  |  |

| 1         | 0          | 0     | 0     | 0     | 1         | Station Addrs Reg 3                                        | Station Addrs Reg 2                |  |  |  |

| 1         | 0          | 0     | 0     | 1     | 0         | Station Addrs Reg 5                                        | Station Addrs Reg 4                |  |  |  |

Notes: 1. These registers when written are the Transmit & Receive Command Registers and when read are the Transmit & Receive Status Registers.

- 3. Bit 0 of this register is write only and will always read back as a ZERO.

- 4. The product I.D. Register is an 8 Bit read only register (please refer to Revision Comparison MD400168 for details). It can be read as described in the above table.

All the counter registers are read only. All other registers except for the Transmit and Receive Command/Status Registers and the MII Management Interface Registers are both readable and writable.

#### 3.3.3 Conditions of Receive Termination

Reception is terminated when either of the following conditions occur:

Carrier Sense or Receive Data Valid Inactive: Indicates that traffic is no longer present on the Ethernet cable.

**Overflow:** The host node for some reason is not able to empty the Receive FIFO as rapidly as it is filled, and an error occurs as frame data is lost. On an average, the Receive FIFO must be serviced every 3200 ns for 10 Mbit Ethernet or 320 ns for 100 Mbit Ethernet to avoid this condition.

## 3.3.4 Using RXABORT pin to Terminate Reception

By pulsing the RXABORT pin high for a minimum of 1.5 RXC cycles, reception of a packet can be terminated. When reception of a packet is terminated this way, the Receive FIFO will be cleared and will stay cleared until carrier sense in 10 MBit Serial Mode or Receive Data Valid in MII mode, transitions from high to low or from low to high indicating either the end of the packet being aborted or the beginning of a new receive packet. It is important to note that RXABORT will cause the RXDC pin to go HIGH based on the conditions described in the section "Conditions that Cause the RXDC Pin to go High".

The assertion of RXDC is done so that an external processor will always have an indication of a packet abortion irrespective of whether its aborted by the user or by an external PHY. However, the assertion of the RXDC signal can be avoided by setting bit 4 of configuration register #2. This will enable the reception of any packet irrespective of whether the RXABORT pin goes HIGH during packet reception.

## 3.3.5 Receive Discard Conditions

Receive packets can be discarded for not meeting the minimum IEEE 802.3 requirements for a good packet, for address mismatches when the chip is not in promiscuous mode, and by either user intervention or symbol errors occurring from a 100 Mbit/sec physical device. in the case of discards due to oversized packets, address mismatches, or the assertion of the RXABORT pin during packet reception, further writing of receive packet data to the receive FIFO is halted once the mismatch, receive abort or oversized packet condition is determined.

Except for discards due to address mismatches and oversized packets, all packet discards occur after carrier sense, or Receive Data Valid in MII mode, deasserts. The discarding of receive packets for error conditions can be controlled through bits 0 through 3 of the receive command register, and through bit 4 of configuration register #2. Listed below are the required conditions for a receive discard to be produced:

1. Bit 0 of the Rx command register is LOW and a receive FIFO overflow occurred during reception.

- 2. Bit 1 of the Rx command register is LOW and a packet with a CRC error was received.

- 3. Bit 2 of the Rx command register is LOW and an oversized packet is received.

- 4. Bit 3 of the Rx command register is LOW and a packet with less than 64 bytes of data was received.

- 5. The Receiver is not in promiscuous mode and a address mismatch occurs.

- 6. Bit 4 of Configuration register 2 is LOW and the RXABORT pin is driven high while CSN is high.

Discarding of a receive packet will cause any packet data that was written to the receive FIFO to be flushed from the FIFO. If no completely received packets are in the receive FIFO at the time a receive discard occurs, the receive FIFO will be completely flushed of data. If however a completely received packet, as indicated by the packet's status double word having been written to the FIFO, is in the receive FIFO at the time of a receive discard, the FIFO will be flushed only up to the last completely received packet. To prevent a receive packet from being discarded due to an error condition, you can selectively enable the reception of errored packets as described in the section "Receive Command Register".

## Conditions that Cause the RXDC Pin to go HIGH

As packets are discarded due to the receive packet error conditions given in the section "Receive Discard Conditions", the RXDC pin may or may not assert. If a receive packet's status has been written to the receive FIFO and the packet's status has not yet been read from the FIFO, discards caused by following packets with errors are handled within the chip and the RXDC pin will not go HIGH. If all status double words for all packets written to the FIFO have been read out, then the RXDC pin will go HIGH under the following condition:

- Enough of a receive packet has been written to the FIFO to cause RXRDY to go HIGH before the packet is discarded due to an error condition.

- 2. If there are no status double words in the receive FIFO and if RXRDY goes HIGH just before a discard condition occurs, RXRDY may go LOW again before any FIFO reads have occurred. This is due to the receive discard clearing the FIFO of any receive bytes already written to the FIFO. In this case, RXRDY is guaranteed to remain HIGH for at least one RXRD\_TXWR clock cycle.

Detecting and Clearing a Receive Discard Condition

To enable the output driver for the RXDC pin, the

RXINTEN input must be driven low. Once a discard

condition is detected, the receive discard can be cleared