# Oki, Network Solutions for a Global Society

# **OKI Semiconductor**

# PEDL9204-02

# Issue Date: Oct. 12, 2004

# **ML9204-xx**

# **Preliminary**

5×7 Dot Character × 24-Digit × 2-Line Display Controller/Driver with Character RAM (Built-in Key Scan)

#### **GENERAL DESCRIPTION**

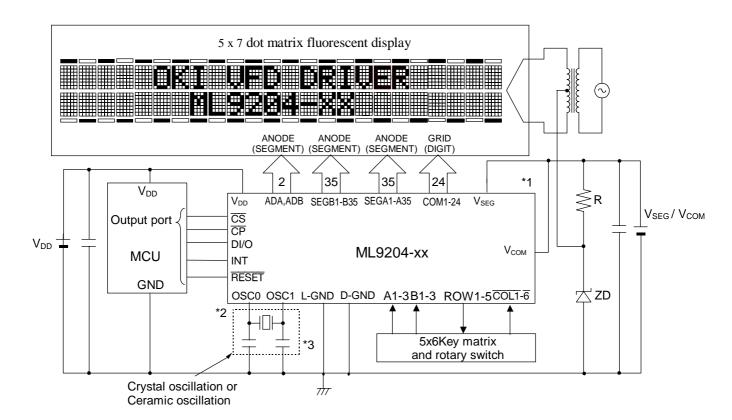

The ML9204-xx is a  $5 \times 7$  dot matrix type vacuum fluorescent display tube controller driver IC which displays characters, numerics and symbols of a maximum of 24 digits  $\times$  2 lines.

Dot matrix vacuum fluorescent display tube drive signals are generated by serial data sent from a micro-controller. A display system is easily realized by internal ROM and RAM for character display.

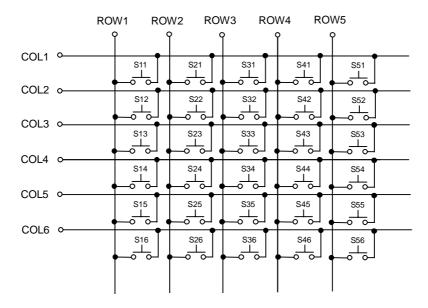

Built-in key scan for 3-channel encoder type rotary switch and  $5 \times 6$  matrix key switch allow the user to receive each switch input.

The ML9204-xx has low power consumption since it is made by CMOS process technology.

-01 is available as a general-purpose code.

Custom codes are provided on customer's request.

#### **FEATURES**

• Logic power supply ( $V_{DD}$ ) : 3.3 V±10% or 5.0 V±10%

VFD tube drive power supply (V<sub>SEG</sub>, V<sub>COM</sub>): 20 to 60 V

• VFD driver output current

(VFD driver output can be connected directly to the VFD tube. No pull-down resistor is required.)

• Segment driver (SEGA1 to A35, SEGB1 to B35)

Only one driver output is high  $:-5 \text{ mA } (V_{SEG}=60 \text{ V})$ All the driver outputs are high  $:-350 \text{ mA } (V_{SEG}=60 \text{ V})$ • Segment driver (ADA, ADB)  $:-15 \text{ mA } (V_{SEG}=60 \text{ V})$ • Grid driver (COM1 to 24)  $:-25 \text{ mA } (V_{COM}=60 \text{ V})$

• Content of display

SEGA1 to SEGA35 and ADA

CGROM\_A

CGRAM\_A

CGRAM\_A

240 types (character data)

5 × 7 dots

16 types (character data)

ADRAM\_A

24 (display digit)× 1 bit (symbol data; can be used for a cursor.)

DCRAM\_A

24 (display digit) × 8 bits (register for character data display)

SEGB1 to SEGB35 and ADB

CGROM\_B

CGRAM\_B

CGRAM\_B

240 types (character data)

5 × 7 dots

16 types (character data)

ADRAM\_B

24 (display digit)× 1 bit (symbol data; can be used for a cursor.)

DCRAM\_B

24 (display digit) × 8 bits (register for character data display)

• Display control function

• GCRAM : Simultaneous output of COM1 to 24 can be set in 1 grid.

• Display digits : 1 to 24 digits (9- to 24-bit arbitrary setting)

• Display duty (brightness adjustment) : 0/1024 to 960/1024 stages

• All lights ON/OFF

• 5 interfaces with microcontroller:DI/O,  $\overline{CS}$ ,  $\overline{CP}$ ,  $\overline{RESET}$ , INT

• Built-in key scan circuit for  $5 \times 6$  matrix key switch

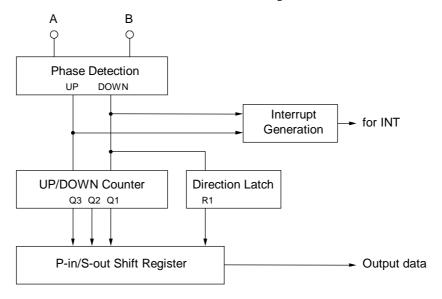

• Built-in key scan circuit for 3-channel encoder type rotary switch

• Built-in oscillation circuit

Crystal oscillation or ceramic oscillation: 4.0 MHz (Typ)

Standby function

Inhibiting the oscillator circuit provides low power consumption.

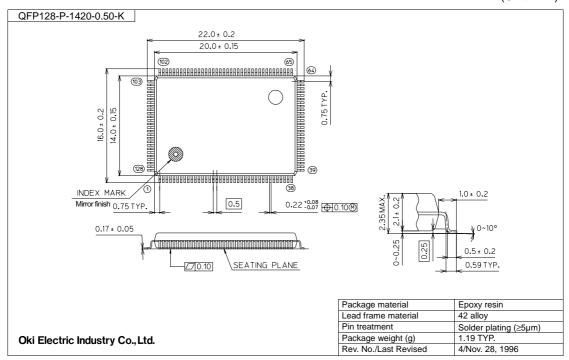

• Package options:

128-pin plastic QFP (QFP128-P-1420-0.50-K) (ML9204-xxGA)

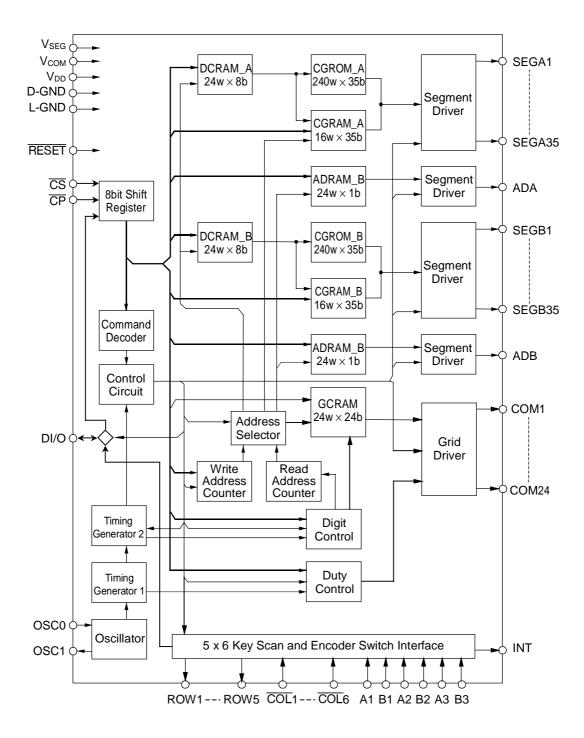

# **BLOCK DIAGRAM**

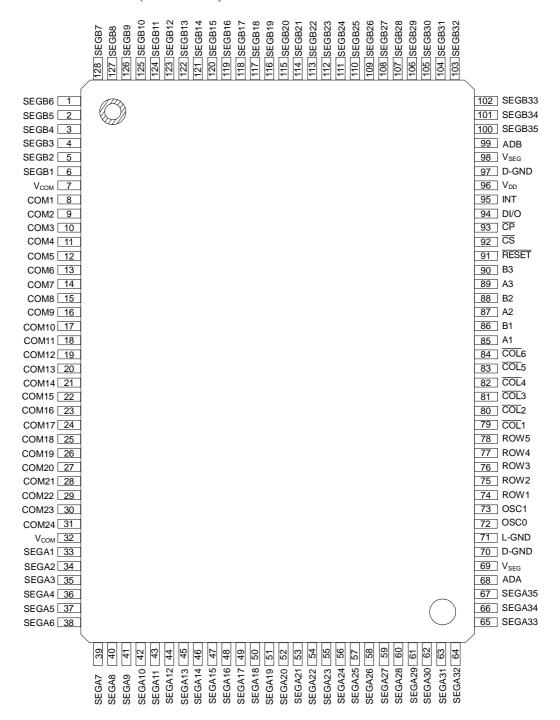

#### PIN CONFIGURATION (TOP VIEW)

128-Pin Plastic QFP

# PIN DESCRIPTION

| Pin                                 | Symbol                       | Туре | Connects to                                                                                          | Description                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

|-------------------------------------|------------------------------|------|------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 33 to 67<br>1 to 6<br>100 to<br>128 | SEGA1 to A35<br>SEGB1 to B35 | 0    | VFD tube anode electrode                                                                             | VFD tube anode electrode drive output.  Directly connected to fluorescent display tube and a pull-down resistor is not necessary. I <sub>OH</sub> < -5 mA                                                                                                                                                                                                  |  |  |  |  |  |  |

| 8 to 31                             | COM1 to 24                   | 0    | VFD tube grid electrode                                                                              | VFD tube grid electrode drive output.  Directly connected to fluorescent display tube and a pull-down resistor is not necessary. I <sub>OH</sub> < -25 mA                                                                                                                                                                                                  |  |  |  |  |  |  |

| 68                                  | ADA                          | 0    | VFD tube anode                                                                                       | VFD tube anode electrode drive output.  Directly connected to fluorescent display tube and a                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| 99                                  | ADB                          | U    | electrode                                                                                            | pull-down resistor is not necessary. I <sub>OH</sub> < -15 mA                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| 96                                  | $V_{DD}$                     |      |                                                                                                      | V <sub>DD</sub> -L-GND are power supplies for internal logic.                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| 71                                  | L-GND                        |      |                                                                                                      | V <sub>COM</sub> -D-GND are power supplies for driving VFD tube                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 7,32                                | V <sub>СОМ</sub>             | _    | Power supply                                                                                         | grid. V <sub>COM</sub> -D-GND are power supplies for driving VFD tube                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| 69,98                               | $V_{SEG}$                    |      |                                                                                                      | anode.                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| 70,97                               | D-GND                        |      |                                                                                                      | Use the same power supply for L-GND and D-GND.                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| 94                                  | DI/O                         | I/O  | Micro controller                                                                                     | Serial data input-output (positive logic).  Data is input and output to sift register synchronized with the rise of shift clock.  When Inputting data input from the LSB.                                                                                                                                                                                  |  |  |  |  |  |  |

| 93                                  | CP                           | I    | I Micro controller Shift clock input. Serial data is shifted on the rising edge of $\overline{CP}$ . |                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 92                                  | <u>cs</u>                    | I    | Micro controller                                                                                     | Chip select input. Serial data transfer is disabled when $\overline{\text{CS}}$ pin is "H" level.                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

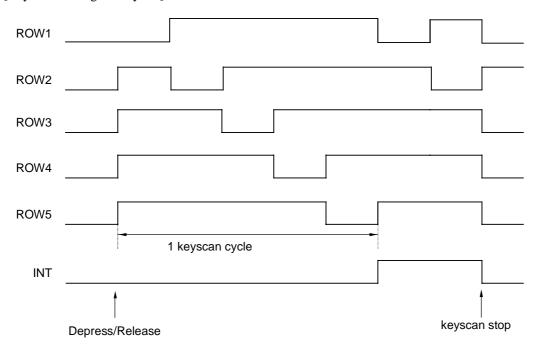

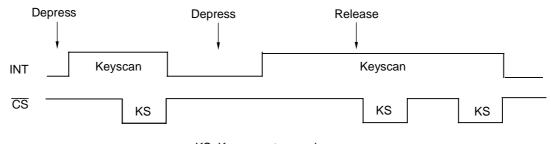

| 95                                  | INT                          | 0    | Micro controller                                                                                     | Output pin for interrupt signal to micro controller. When depression or release of key matrix switch is detected, key scanning starts and when 1 cycle is completed, this pin becomes high level. Upon receiving encoder type rotary switch input, this pin becomes high level. The INT pin remains at high level until the key scan stop mode is selected |  |  |  |  |  |  |

| 85,86<br>87,88<br>89,90             | A1,B1<br>A2,B2<br>A3,B3      | I    | Rotary switch                                                                                        | Encoder type rotary switch input pins.  All inputs possess chattering absorption function of 256us period.  Those inputs must be tied to ground when they are not used.                                                                                                                                                                                    |  |  |  |  |  |  |

| 79 to 84                            | COL1 to 6                    | I    | Key matrix                                                                                           | Input pins for return signal from key matrix with built-in pull-up resister.  When input is low level, the key matrix switch is regarded as being pressed.  Dose not have chattering absorption function.                                                                                                                                                  |  |  |  |  |  |  |

|          |           |   | 1                  |                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |

|----------|-----------|---|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 74 to 78 | ROW1 to 5 | 0 | Key matrix         | Key matrix scan signal output pins.  Normally low level is output.  Key scanning starts by detecting depression or release of key matrix switch and continues until selection of key scan stop mode.  When key scan stop mode is selected, all outputs of ROW1 to 5 return to low level. |  |  |  |  |  |  |  |

| 91       | RESET     | I | Micro controller   | Reset input.  "Low" initializes all the functions. Initial status is as follows.  • Address of each RAM                                                                                                                                                                                  |  |  |  |  |  |  |  |

| 72       | OSC0      | I | Crystal or ceramic | Pins for self-oscillation. (Do not apply external clocks to these pins.) Connect these pins to the crystal and capacitors or to the ceramic resonator and capacitors. The target oscillation frequency is 4.0MHz. (The device has an internal feedback resister.)                        |  |  |  |  |  |  |  |

| 73       | OSC1      | 0 | resonator          | V <sub>DD</sub> Typical  3.3V 1Mohm  5.0V 0.4Mohm  * For information regarding the oscillator contact the manufacturer of the oscillator.  * As regards the circuit, refer to the Application Circuit.                                                                                   |  |  |  |  |  |  |  |

# ABSOLUTE MAXIMUM RATINGS

| Parameter           | Symbol           | Condition                           | Rating                       | Unit |

|---------------------|------------------|-------------------------------------|------------------------------|------|

| Supply Voltage (1)  | $V_{DD}$         | _                                   | -0.3 to +6.5                 | V    |

| Supply Voltage (2)  | $V_{SEG}$        | _                                   | -0.3 to +70                  | V    |

| Supply Voltage (2)  | V <sub>COM</sub> | _                                   | -0.3 to +70                  | V    |

| Input Voltage       | $V_{IN}$         | _                                   | -0.3 to V <sub>DD</sub> +0.3 | V    |

| Power Dissipation   | P <sub>D</sub>   | Ta ≤ 85°C                           | 470 *1)                      | mW   |

| Storage Temperature | T <sub>STG</sub> | _                                   | -55 to +150                  | °C   |

|                     | l <sub>01</sub>  | COM1 to COM24                       | -50 to +2.0                  | mA   |

|                     | l <sub>O2</sub>  | ADA, ADB                            | -30 to +2.0                  | mA   |

| Output Current      | I <sub>O3</sub>  | SEGA1 to SEGA35,<br>SEGB1 to SEGB35 | -10 to +2.0                  | mA   |

|                     | I <sub>04</sub>  | ROW1 to 5 / INT                     | -2.0 to +2.0                 | mA   |

<sup>\*1)</sup> When use two or more COM, be careful of the following things.

# RECOMMENDED OPERATING CONDITIONS

| Parameter             | Symbol           | Condition                                     | Min. | Тур. | Max. | Unit |

|-----------------------|------------------|-----------------------------------------------|------|------|------|------|

| Supply Voltage (1)    | $V_{DD}$         | When the power supply voltage is 5.0 V (typ.) | 4.5  | 5.0  | 5.5  | V    |

| Supply Voltage (1)    | V DD             | When the power supply voltage is 3.3 V (typ.) | 3.0  | 3.3  | 3.6  | V    |

| Supply Voltage (2)    | V <sub>SEG</sub> | _                                             | 20   | _    | 60   | V    |

| Supply Voltage (2)    | V <sub>COM</sub> | _                                             | 20   | _    | 60   | V    |

| Operating Frequency   | fosc             | Oscillation                                   | 3.5  | 4.0  | 4.5  | MHz  |

| Frame Frequency       | f <sub>FR</sub>  | DIGIT = 1 to 24, oscillation                  | 142  | 163  | 183  | Hz   |

| Operating Temperature | T <sub>OP</sub>  | _                                             | -40  | _    | +85  | °C   |

The junction temperature which can be found by the following formula does not exceed 120.

$Tj = (Px 85^{\circ}C/W)+Ta$  (P is the maximum power consumption of IC.)

# **ELECTRICAL CHARACTERISTICS**

# DC Characteristics ( $V_{DD} = 5.0 \text{ V} \pm 10\%$ )

$(V_{DD} = 5.0 \text{ V} \pm 10\%, V_{SEG} \text{ and } V_{COM} = 20 \text{ to } 60 \text{ V}, Ta = -40 \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise specified})$

| Parameter                    | Symbol             | Applied pin                         |                        | Condition                                  | Min.                   | Max.         | Unit |

|------------------------------|--------------------|-------------------------------------|------------------------|--------------------------------------------|------------------------|--------------|------|

| High Level Input Voltage     | V <sub>IH</sub>    | *1                                  | $V_{DD}$               | = 5.0 V±10%                                | 0.7 V <sub>DD</sub>    | _            | V    |

| Low Level Input Voltage      | V <sub>IL</sub>    | *1                                  | $V_{DD}$               | = 5.0 V±10%                                | _                      | $0.3~V_{DD}$ | V    |

| High Level Input Current     | I <sub>IH</sub>    | *1                                  |                        | $V_{IH} = V_{DD}$                          | -1.0                   | +1.0         | μΑ   |

| Low Lovel Input Current      | I <sub>IL1</sub>   | *2                                  | ,                      | V <sub>IL</sub> = 0.0 V                    | -1.0                   | +1.0         | μΑ   |

| Low Level Input Current      | I <sub>IL2</sub>   | COL1 to 6                           | $V_{DD} = 5.0$         | $V\pm 10\%,\ V_{IL}=0.0\ V$                | -450                   | -100         | μΑ   |

|                              | $V_{OH1}$          | COM1 to 24                          | $V_{COM} = 6$          | 0 V, $I_{OH1} = -25 \text{ mA}$            | $V_{COM} - 2.0$        | _            | V    |

| High Level Output<br>Voltage | V <sub>OH2</sub>   | ADA, ADB                            | $V_{SEG} = 6$          | 0 V, $I_{OH2} = -15 \text{ mA}$            | $V_{SEG} - 2.0$        | _            | V    |

|                              | V <sub>ОНЗ</sub>   | SEGA1 to A35<br>SEGB1 to B35        | V <sub>SEG</sub> = 6   | 60 V, I <sub>OH3</sub> = -5 mA             | V <sub>SEG</sub> – 2.0 | _            | V    |

|                              | V <sub>OH4</sub>   | INT, ROW1 to 5                      | $V_{DD} = 5.0$         | V±10%, $I_{OH4} = -450$ $\mu A$            | V <sub>DD</sub> - 0.2  | _            | V    |

| Low Level Output             | V <sub>OL1</sub>   | *3                                  | _                      |                                            | _                      | 1.0          | V    |

| Voltage                      | $V_{OL2}$          | INT, ROW1 to 5                      | V <sub>DD</sub> =5.0 V | $t/\pm 10\%$ , $I_{OL2} = 450 \mu\text{A}$ | _                      | 0.2          | V    |

|                              | I <sub>DD1</sub>   | $V_{DD}$                            | $V_{DD} = 5.0$         | V±10%, f <sub>OSC</sub> = 4.0<br>MHz       | _                      | 6.0          | mA   |

| Supply Current (1)           | I <sub>DISP1</sub> |                                     | $f_{OSC} = 4.0$        | All output lights ON                       | _                      | 1.0          | mA   |

|                              | I <sub>DISP2</sub> | V <sub>SEG</sub> , V <sub>COM</sub> | MHz,<br>no load        | All output lights OFF                      | _                      | 200          | μΑ   |

| Supply Current (2)           | I <sub>DDS</sub>   | $V_{DD}$                            | In c                   | standby mode                               | _                      | 1.0          | μΑ   |

| Supply Current (2)           | I <sub>DISPS</sub> | $V_{\text{SEG}}, V_{\text{COM}}$    | 111 8                  | stationly induc                            | _                      | 20.0         | μΑ   |

<sup>\*1)</sup>  $\overline{CS}$ ,  $\overline{CP}$ , DI/O,  $\overline{RESET}$ ,  $\overline{COL}$ 1 to 6 \*2)  $\overline{CS}$ ,  $\overline{CP}$ , DI/O,  $\overline{RESET}$ \*3) SEGA1 to A35, SEGB1 to B35, ADA, ADB, COM1 to 24

# DC Characteristics ( $V_{DD} = 3.3 \text{ V} \pm 10\%$ )

$(V_{DD} = 3.3 \text{ V} \pm 10\%, \text{ V}_{SEG} \text{ and } \text{V}_{COM} = 20 \text{ to } 60 \text{ V}, \text{ Ta} = -40 \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise specified})$

|                              |                    |                                  |                         | = -40 to +65 C, un                        | 1                      |                | <del></del> |

|------------------------------|--------------------|----------------------------------|-------------------------|-------------------------------------------|------------------------|----------------|-------------|

| Parameter                    | Symbol             | Applied pin                      |                         | Condition                                 | Min.                   | Max.           | Unit        |

| High Level Input Voltage     | $V_{IH}$           | *1                               | $V_{DD}$                | = 3.3 V±10%                               | $0.8 V_{DD}$           | _              | V           |

| Low Level Input Voltage      | V <sub>IL</sub>    | *1                               | $V_{DD}$                | = 3.3 V±10%                               | _                      | $0.2$ $V_{DD}$ | V           |

| High Level Input Current     | I <sub>IH</sub>    | *1                               |                         | $V_{\text{IH}} = V_{\text{DD}}$           | -1.0                   | +1.0           | μΑ          |

| Low Level Input Current      | I <sub>IL1</sub>   | *2                               | ,                       | V <sub>IL</sub> = 0.0 V                   | -1.0                   | +1.0           | μΑ          |

| Low Level Input Current      | I <sub>IL3</sub>   | COL1 to 6                        | $V_{DD} = 3.3$          | $V\pm 10\%,\ V_{IL}=0.0\ V$               | -120                   | -25            | μΑ          |

|                              | V <sub>OH1</sub>   | COM1 to 24                       | $V_{COM} = 6$           | 0 V, I <sub>OH1</sub> = -25 mA            | $V_{COM} - 2.0$        | _              | V           |

| High Level Output<br>Voltage | V <sub>OH2</sub>   | ADA, ADB                         | $V_{SEG} = 6$           | 0 V, I <sub>OH2</sub> = -15 mA            | $V_{SEG} - 2.0$        | _              | V           |

|                              | V <sub>OH3</sub>   | SEGA1 to A35<br>SEGB1 to B35     | V <sub>SEG</sub> = 6    | 60 V, I <sub>OH3</sub> = -5 mA            | V <sub>SEG</sub> – 2.0 | _              | V           |

|                              | V <sub>OH5</sub>   | INT, ROW1 to 5                   | $V_{DD} = 3.3$          | $V\pm 10\%$ , $I_{OH5} = -120$ $\mu A$    | V <sub>DD</sub> - 0.2  | _              | V           |

| Low Level Output             | $V_{OL1}$          | *3                               |                         | _                                         | _                      | 1.0            | V           |

| Voltage                      | V <sub>OL2</sub>   | INT, ROW1 to 5                   | V <sub>DD</sub> = 3.3 \ | $/\pm 10\%$ , $I_{OL3} = 120 \mu\text{A}$ | _                      | 0.2            | V           |

|                              | I <sub>DD2</sub>   | $V_{DD}$                         | $V_{DD} = 3.3$          | 3 V±10%, f <sub>OSC</sub> = 4.0<br>MHz    | _                      | 4.0            | mA          |

| Supply Current (1)           | I <sub>DISP1</sub> |                                  | $f_{OSC} = 4.0$         | All output lights ON                      | _                      | 1.0            | mΑ          |

|                              | I <sub>DISP2</sub> | $V_{SEG,}V_{COM}$                | MHz,<br>no load         | All output lights OFF                     | _                      | 200            | μΑ          |

| Supply Current (2)           | I <sub>DDS</sub>   | $V_{DD}$                         | ln c                    | standby mada                              | _                      | 1.0            | μΑ          |

| Supply Current (2)           | I <sub>DISPS</sub> | $V_{\text{SEG}}, V_{\text{COM}}$ | III S                   | standby mode                              | _                      | 20.0           | μΑ          |

<sup>\*1)</sup>  $\overline{CS}$ ,  $\overline{CP}$ , DI/O,  $\overline{RESET}$ ,  $\overline{COL}$ 1 to 6 \*2)  $\overline{CS}$ ,  $\overline{CP}$ , DI/O,  $\overline{RESET}$

<sup>\*3)</sup> SEGA1 to A35, SEGB1 to B35, ADA, ADB, COM1 to 24

#### **AC Characteristics**

$(V_{DD} = 5.0 \text{ V} \pm 10\%, \text{ or } V_{DD} = 3.3 \text{ V} \pm 10\%, V_{SEG} \text{ and } V_{COM} = 20 \text{ to } 60 \text{ V}, Ta = -40 \text{ to } +85^{\circ}\text{C} \text{ unless otherwise specified})$

| 1 = 1 0 7 0 , 1 3 L G 0 | 2110 VCOW - 20 10 C                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                             |                                                        |                                                        | <del>, , , , , , , , , , , , , , , , , , , </del>     |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|-------------------------------------------------------|

| Symbol                  | Co                                                                                                                                                                                                                | ondition                                                                                                                                                                                                                                                                                                                                                                    | Min.                                                   | Max.                                                   | Unit                                                  |

| f <sub>C</sub>          |                                                                                                                                                                                                                   | _                                                                                                                                                                                                                                                                                                                                                                           | _                                                      | 2.0                                                    | MHz                                                   |

| t <sub>CW</sub>         |                                                                                                                                                                                                                   | _                                                                                                                                                                                                                                                                                                                                                                           | 200                                                    |                                                        | ns                                                    |

| t <sub>DS</sub>         |                                                                                                                                                                                                                   | _                                                                                                                                                                                                                                                                                                                                                                           | 200                                                    | _                                                      | ns                                                    |

| t <sub>DH</sub>         |                                                                                                                                                                                                                   | _                                                                                                                                                                                                                                                                                                                                                                           | 200                                                    | 1                                                      | ns                                                    |

| t <sub>CSS</sub>        |                                                                                                                                                                                                                   | _                                                                                                                                                                                                                                                                                                                                                                           | 200                                                    | _                                                      | ns                                                    |

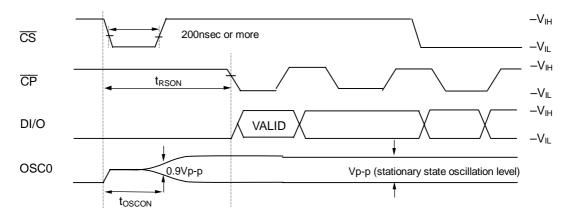

| t <sub>CSH</sub>        | Oscill                                                                                                                                                                                                            | ating state                                                                                                                                                                                                                                                                                                                                                                 | 8                                                      | _                                                      | μs                                                    |

| t <sub>CSW</sub>        |                                                                                                                                                                                                                   | _                                                                                                                                                                                                                                                                                                                                                                           | 200                                                    | 1                                                      | ns                                                    |

| t <sub>DOFF</sub>       | Oscill                                                                                                                                                                                                            | ating state                                                                                                                                                                                                                                                                                                                                                                 | 4                                                      |                                                        | μs                                                    |

| t <sub>WRES</sub>       |                                                                                                                                                                                                                   | •                                                                                                                                                                                                                                                                                                                                                                           | 200                                                    | l                                                      | ns                                                    |

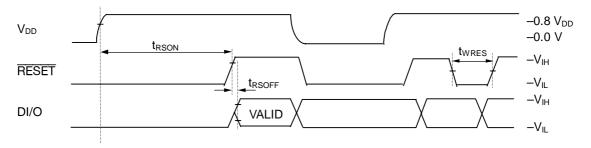

| t <sub>RSON</sub>       |                                                                                                                                                                                                                   | _                                                                                                                                                                                                                                                                                                                                                                           | toscon                                                 |                                                        |                                                       |

| t <sub>RSOFF</sub>      |                                                                                                                                                                                                                   | _                                                                                                                                                                                                                                                                                                                                                                           | 200                                                    |                                                        | ns                                                    |

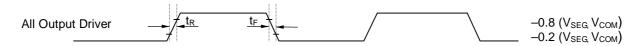

| t <sub>R</sub>          | C. – 100 pF                                                                                                                                                                                                       | $t_R = 20 \text{ to } 80\%$                                                                                                                                                                                                                                                                                                                                                 |                                                        | 2.0                                                    | μs                                                    |

| t <sub>F</sub>          | C <sub>1</sub> = 100 pr                                                                                                                                                                                           | $t_F = 80 \text{ to } 20\%$                                                                                                                                                                                                                                                                                                                                                 |                                                        | 2.0                                                    | μs                                                    |

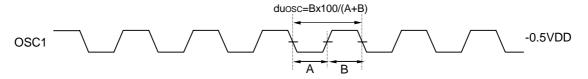

| du <sub>OSC</sub>       |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                             | 40                                                     | 60                                                     | %                                                     |

| toscon                  | <del>-</del> *1                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                             |                                                        |                                                        |                                                       |

|                         | Symbol  f <sub>C</sub> t <sub>CW</sub> t <sub>DS</sub> t <sub>DH</sub> t <sub>CSS</sub> t <sub>CSH</sub> t <sub>CSW</sub> t <sub>DOFF</sub> t <sub>WRES</sub> t <sub>RSOFF</sub> t <sub>R</sub> du <sub>OSC</sub> | $ \begin{array}{c c} Symbol & Co \\ \hline f_C & \\ \hline t_{CW} & \\ \hline t_{DS} & \\ \hline t_{DH} & \\ \hline t_{CSS} & \\ \hline t_{CSH} & Oscill \\ \hline t_{CSW} & \\ \hline t_{DOFF} & Oscill \\ \hline t_{WRES} & When \overline{RESET} \\ \hline microcontro \\ \hline t_{RSOF} & \\ \hline t_R & \\ \hline t_F & \\ \hline du_{OSC} & \\ \hline \end{array} $ | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

<sup>\*1</sup> t<sub>OSCON</sub> (oscillation rise time) differs with the oscillator pin used. As regards oscillation rise time, refer to the data of oscillator used.

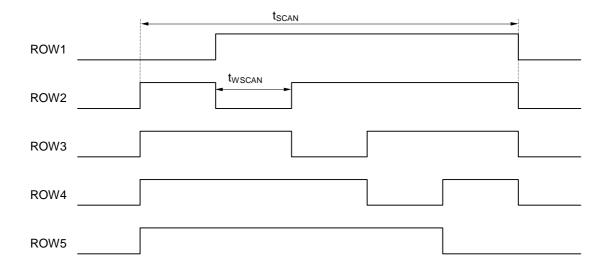

# **Key Scan Characteristics**

$(V_{DD} = 5.0V \pm 10\%, \text{ or } V_{DD} = 3.3V \pm 10\%, V_{SEG} \text{ and } V_{COM} = 20 \text{ to } 60 \text{ V}, Ta = -40 \text{ to } +85^{\circ}\text{C} \text{ unless otherwise specified})$

| Parameter            | Symbol             | Condition                         | Min.  | Тур. | Max.  | Unit |

|----------------------|--------------------|-----------------------------------|-------|------|-------|------|

| Key Scan Time        | t <sub>SCAN</sub>  | f 2.5 to 4.5 MHz                  | 142.2 | 160  | 182.8 | μs   |

| Key Scan Pulse Width | t <sub>WSCAN</sub> | f <sub>OSC</sub> = 3.5 to 4.5 MHz | 28.4  | 32   | 36.6  | μs   |

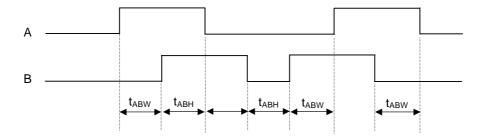

# **Rotary Switch Characteristics**

$(V_{DD} = 5.0V \pm 10\%$ , or  $V_{DD} = 3.3V \pm 10\%$ ,  $V_{SEG}$  and  $V_{COM} = 20$  to 60 V,  $T_{A} = -40$  to +85°C unless otherwise specified)

| Parameter              | Symbol           | Condition                         | Min. | Тур. | Max. | Unit |

|------------------------|------------------|-----------------------------------|------|------|------|------|

| Phase Input Time       | t <sub>ABW</sub> | f 2 5 to 4 5 MHz                  | 1.2  |      |      | me   |

| Phase Input Fixed Time | t <sub>ABH</sub> | f <sub>OSC</sub> = 3.5 to 4.5 MHz | 1.2  | _    |      | ms   |

# TIMING DIAGRAMS

| Symbol          | $V_{DD} = 5.0 \text{ V} \pm 10\%$ | $V_{DD} = 3.0 \text{ V} \pm 10\%$ |  |  |  |  |  |

|-----------------|-----------------------------------|-----------------------------------|--|--|--|--|--|

| V <sub>IH</sub> | 0.7 V <sub>DD</sub>               | 0.8 V <sub>DD</sub>               |  |  |  |  |  |

| V <sub>IL</sub> | 0.3 V <sub>DD</sub>               | 0.2 V <sub>DD</sub>               |  |  |  |  |  |

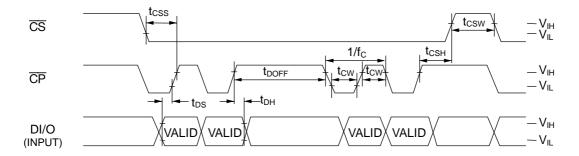

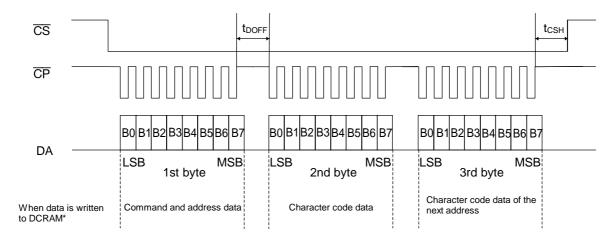

# **Data Input Timing**

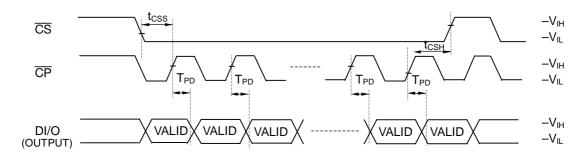

# **Data Output Timing**

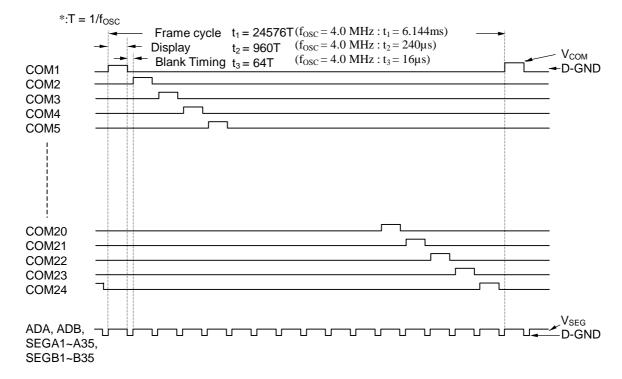

# **Output Timing**

# **OSC Timing**

# **Standby Mode Release Timing**

# **Reset Timing**

\* After a VDD injection should surely input a reset signal.

# **Key Scan Timing**

# **Rotary Switch Input Timing**

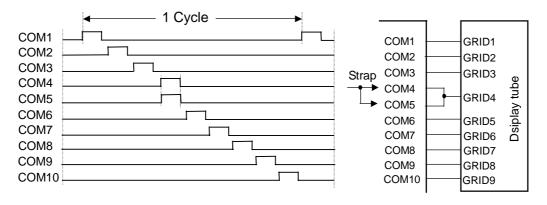

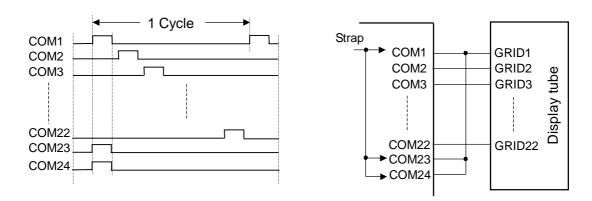

# Digit Output Timing (24-Digit,960/1024-Duty)

# **FUNCTIONAL DESCRIPTION**

#### **Commands List**

| Con | Command              |    | LSB<br>MSB |    |    |    |    | 1st k | oyte | LSB 2nd byte MSB |     |             |     | oyte |     |     |     |          |

|-----|----------------------|----|------------|----|----|----|----|-------|------|------------------|-----|-------------|-----|------|-----|-----|-----|----------|

|     |                      | В0 | B1         | B2 | ВЗ | B4 | B5 | B6    | В7   | B0               | B1  | B2          | ВЗ  | B4   | B5  | B6  | В7  |          |

| 1   | DCRAM_A data write   | *  | *          | *  | *  | 1  | 0  | 0     | 0    | C0               | C1  | C2          | СЗ  | C4   | C5  | C6  | C7  |          |

|     |                      |    |            |    |    |    |    |       |      | C0               | C5  | C10         | C15 | C20  | C25 | C30 | *   | 2nd byte |

|     |                      |    |            |    |    |    |    |       |      | C1               | C6  | C11         | C16 | C21  | C26 | C31 | *   | 3rd byte |

| 2   | CGRAM_A data write   | 0  | 0          | 0  | 0  | 0  | 1  | 0     | 0    | C2               | C7  | C12         | C17 | C22  | C27 | C32 | *   | 4th byte |

|     |                      |    |            |    |    |    |    |       |      | C3               | C8  | C13         | C18 | C23  | C28 | C33 | *   | 5th byte |

|     |                      |    |            |    |    |    |    |       |      | C4               | C9  | C14         | C19 | C24  | C29 | C34 | *   | 6th byte |

| 3   | ADRAM_A data write   | *  | *          | *  | *  | 1  | 1  | 0     | 0    | C0               | *   | *           | *   | *    | *   | *   | *   |          |

|     |                      |    |            |    |    |    |    |       |      | C0               | C1  | C2          | C3  | C4   | C5  | C6  | C7  |          |

| 4   | GCRAM data write     | *  | *          | *  | *  | 0  | 0  | 1     | 0    | C8               | C9  | C10         | C11 | C12  | C13 | C14 | C15 |          |

|     |                      |    |            |    |    |    |    |       |      | C16              | C17 | C18         | C19 | C20  | C21 | C22 | C23 |          |

| 5   | Display duty set     | D0 | D1         | *  | *  | 1  | 0  | 1     | 0    | D2               | D3  | D4          | D5  | D6   | D7  | D8  | D9  |          |

| 6   | Number of digits set | K0 | K1         | K2 | K3 | 0  | 1  | 1     | 0    |                  |     |             |     |      |     |     |     |          |

| 7   | All lights ON/OFF    | L  | Н          | *  | *  | 1  | 1  | 1     | 0    |                  |     |             |     |      |     |     |     |          |

| 9   | DCRAM_B data write   | *  | *          | *  | *  | 1  | 0  | 0     | 1    | C0               | C1  | C2          | C3  | C4   | C5  | C6  | C7  |          |

|     |                      |    |            |    |    |    |    |       |      | C0               | C5  | C10         | C15 | C20  | C25 | C30 | *   | 2nd byte |

|     |                      |    |            |    |    |    |    |       |      | C1               | C6  | C11         | C16 | C21  | C26 | C31 | *   | 3rd byte |

| Α   | CGRAM_B data write   | 0  | 0          | 0  | 0  | 0  | 1  | 0     | 1    | C2               | C7  | C12         | C17 | C22  | C27 | C32 | *   | 4th byte |

|     |                      |    |            |    |    |    |    |       |      | C3               | C8  | C13         | C18 | C23  | C28 | C33 | *   | 5th byte |

|     |                      |    |            |    |    |    |    |       |      | C4               | C9  | C14         | C19 | C24  | C29 | C34 | *   | 6th byte |

| В   | ADRAM_B data write   | *  | *          | *  | *  | 1  | 1  | 0     | 1    | C0               | *   | *           | *   | *    | *   | *   | *   |          |

| С   | Key scan stop        | *  | *          | *  | *  | 0  | 0  | 1     | 1    |                  |     |             |     |      |     |     |     |          |

| D   | Key data output      | *  | *          | *  | *  | 1  | 0  | 1     | 1    |                  |     | iter<br>des |     |      | omm | and | and |          |

| F   | Standby mode         | *  | *          | *  | *  | 1  | 1  | 1     | 1    |                  |     |             |     |      |     |     |     |          |

| 0   | Test Mode(Note)      |    |            |    |    | 0  | 0  | 0     | 0    |                  |     |             |     |      |     |     |     |          |

When data is written to RAM (DCRAM, CGRAM, ADRAM, and GCRAM) continuously, addresses are internally incremented automatically.

Therefore it is not necessary to specify the 1st byte to write RAM data for the 2nd and later bytes.

Note: The test mode is used for inspection before shipment. It is not a user function. The user cannot use this command. Enter commands 1 to 7, 9 to D, and F alone in the way described on the next page and the following pages. (The operation of this device cannot be guaranteed if other commands are used.

: Don't care

Xn: Address specification for each RAM

Cn: Character code specification for each RAM

Dn : Display duty specification

Kn : Number of digits specification

H : All lights ON instruction

L : All lights OFF instruction

#### Positional Relationship Between SEGn and ADn (one digit)

#### **Data Transfer Method and Command Write Method**

Display control command and data are written by an 8-bit serial transfer.

Write timing is shown in the figure below.

Setting the  $\overline{CS}$  pin to "Low" level enables a data transfer.

Data is 8 bits and is sequentially input into the DI/O pin from LSB (LSB first).

As shown in the figure below, data is read by the shift register at the rising edge of the shift clock, which is input into the  $\overline{CP}$  pin. If 8-bit data is input, internal load signals are automatically generated and data is written to each register and RAM.

Therefore it is not necessary to input load signals from the outside.

Setting the  $\overline{CS}$  pin to "High" disables data transfer. Data input from the point when the  $\overline{CS}$  pin changes from "High" to "Low" is recognized in 8-bit units.

<sup>\*</sup> When data is written to RAM (DCRAM, ADRAM, CGRAM, GCRAM) continuously, addresses are internally incremented automatically.

Therefore it is not necessary to specify the 1st byte to write RAM data for the 2nd and later bytes.

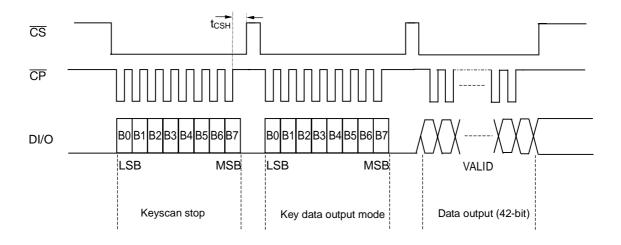

# **Data Outputting and Command Writing**

In an operation to read key scan data, when  $\overline{CS}$  goes "Low" after Key Data Output Mode is entered, the DI/O pin changes modes to OUTPUT and key data is output in synchronization with the rise of Shift Lock.

The waveforms to read key data are shown blow.

The DI/O pin enters the INPUT mode when the  $\overline{CS}$  pin is set to "High" after key data is output.

### **Reset Function**

Reset is executed when the  $\overline{RESET}$  pin is set to "L", (when turning power on, for example) and initializes all functions.

Initial status is as follows.

| • Address of each RAM          | address "00"H                |

|--------------------------------|------------------------------|

| • Data of each RAM             | All contents are undefined   |

| • Display digit                | 24 digits                    |

| • Brightness adjustment        | 0/1024                       |

| • All display lights ON or OFF | OFF mode                     |

| • Segment output               | All segment outputs go "Low" |

| • AD output                    | All AD outputs go "Low"      |

| • ROW1 to 5                    | All ROW outputs go "Low"     |

| • INT                          | INT goes "Low."              |

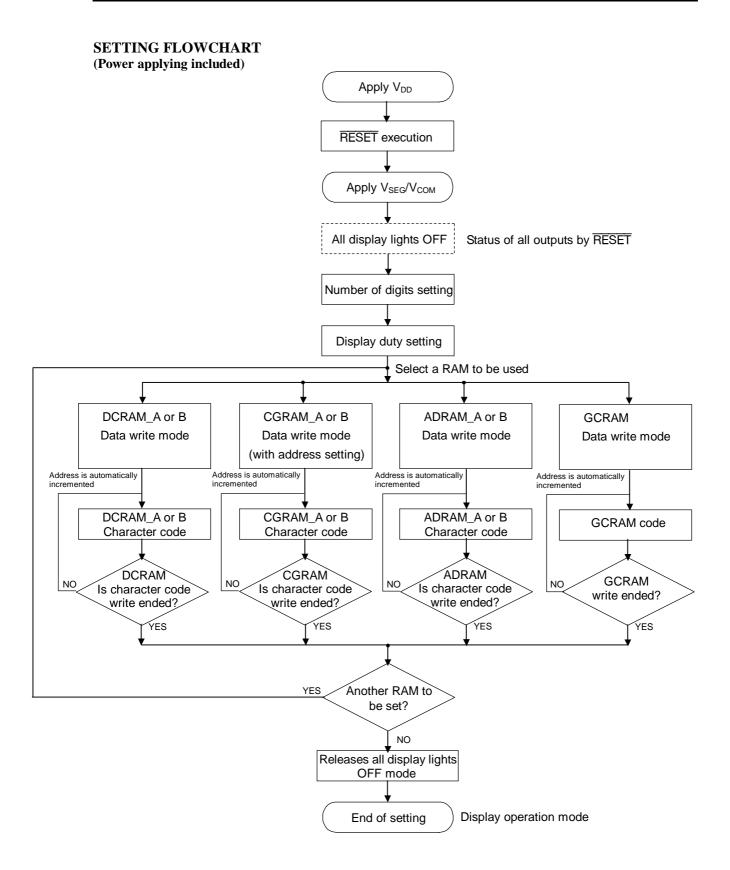

Be sure to execute the reset operation when turning power on and set again according to "Setting Flowchart" after reset.

#### **Description of Commands and Functions**

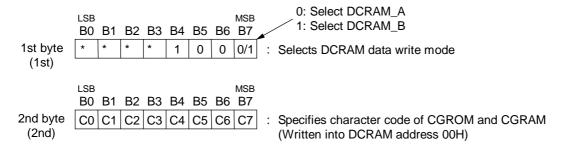

#### 1,9. DCRAM data write

(Writes the character code of CGROM and CGRAM.)

DCRAM (Data Control RAM) has a 5-bit address to store character code of CGROM and CGRAM.

The character code specified by DCRAM is converted to a  $5 \times 7$  dot matrix character pattern via CGROM or CGRAM.

(The DCRAM can store 24 characters.)

#### [Command format]

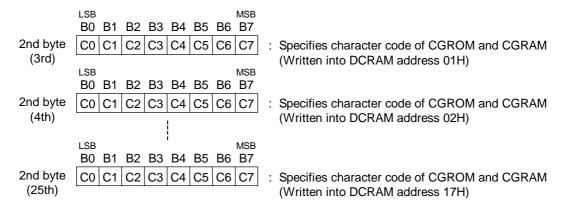

To specify the character code of CGROM and CGRAM continuously to the next address, specify only character code as follows

The addresses of DCRAM are automatically incremented. Specification of an address is unnecessary.

A character code setup of CGROM to 24-Digit and CGRAM is completion in the above work.

Furthermore, you have to specify the character codes of a dummy to be DCRAM and 18H-1FH to perform a character code setup from DCRAM address 00H continuously.

(In order to carry out the increment of the address of DCRAM automatically and to set a DCRAM address to 00H.)

| 2nd byte<br>(26th) | LSB                     | : CGROM of a dummy and the character code of CGRAM are specified. (It is not written in a DCRAM address.) |

|--------------------|-------------------------|-----------------------------------------------------------------------------------------------------------|

| 2nd byte<br>(33th) | LSB                     | : CGROM of a dummy and the character code of CGRAM are specified. (It is not written in a DCRAM address.) |

| 2nd byte<br>(34th) | C0 C1 C2 C3 C4 C5 C6 C7 | : Character code of CGROM and CGRAM is specified. (DCRAM address 00H are rewritten.)                      |

C0 (LSB) to C7 (MSB): Character code of CGROM and CGRAM (8 bits: 256 characters) \*: Don't Care

# [COM positions and set DCRAM addresses]

| DCRAM address<br>(HEX) | СОМ   | DCRAM address<br>(HEX) | СОМ   | DCRAM address<br>(HEX) | СОМ               |

|------------------------|-------|------------------------|-------|------------------------|-------------------|

| 00                     | COM1  | 0C                     | COM13 | 18                     | Dummy             |

| 01                     | COM2  | 0D                     | COM14 | 19                     | Dummy             |

| 02                     | COM3  | 0E                     | COM15 | 1A                     | Dummy             |

| 03                     | COM4  | 0F                     | COM16 | 1B                     | Dummy             |

| 04                     | COM5  | 10                     | COM17 | 1C                     | Dummy             |

| 05                     | COM6  | 11                     | COM18 | 1D                     | Dummy             |

| 06                     | COM7  | 12                     | COM19 | 1E                     | Dummy             |

| 07                     | COM8  | 13                     | COM20 | 1F                     | Dummy             |

| 08                     | COM9  | 14                     | COM21 |                        |                   |

| 09                     | COM10 | 15                     | COM22 |                        | to set up a DCRAM |

| 0A                     | COM11 | 16                     | COM23 | address from 00H       | I continuously.   |

| 0B                     | COM12 | 17                     | COM24 | •                      |                   |

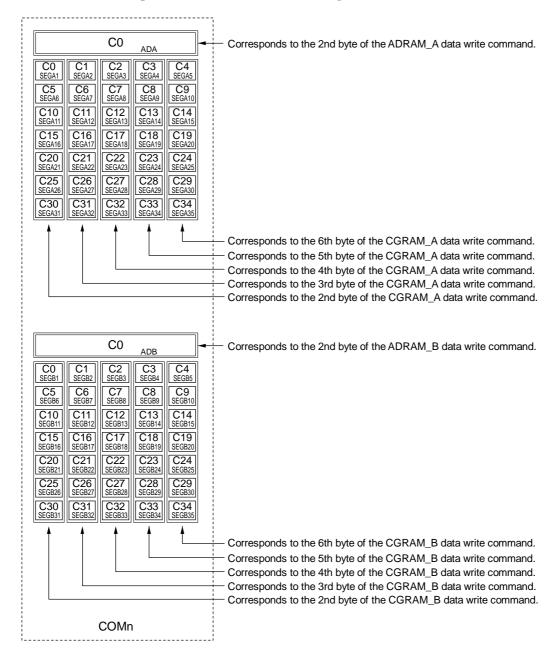

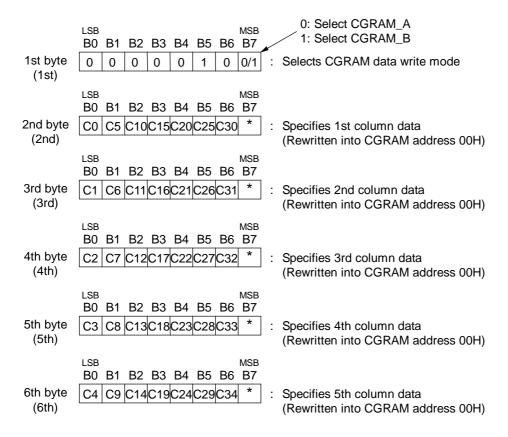

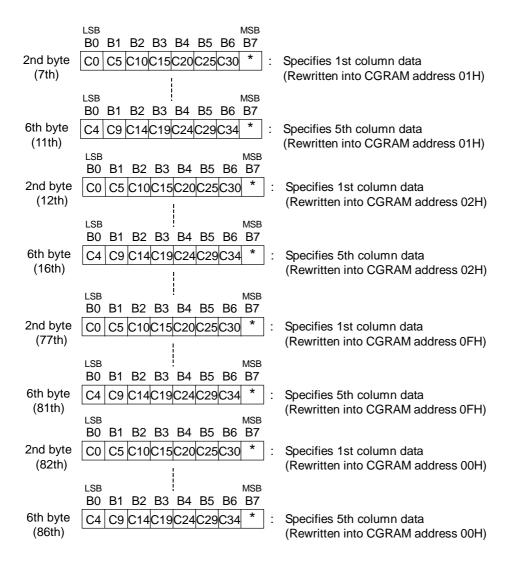

#### 2,A. CGRAM data write

(CGRAM writes character pattern data.)

CGRAM (Character Generator RAM) has a 4-bit address to store 5x 7 dot matrix character patterns.

A character pattern stored in CGRAM can be displayed by specifying the character code (address) by DCROM.

The address of CGRAM is assigned to 00H to 0FH. (All the other addresses are the CGROM addresses.) (The CGRAM can store 16 types of character patterns.)

#### [Command format]

To specify character pattern data continuously to the next address, specify only character pattern data as follows. The addresses of CGRAM are automatically incremented. Specification of an address is unnecessary. The 2nd to 6th byte (character pattern data) are regarded as one data item, so 200 ns is sufficient for  $t_{DOFF}$  time between bytes.

X0 (LSB) to X3 (MSB): CGRAM addresses (4 bits: 16 characters)

C0 (LSB) to C34 (MSB): Character pattern data (35 bits: 35 outputs per digit)

\* : Don't care

#### [CGROM addresses and set CGRAM addresses]

#### Refer to ROM code tables.

| HEX | X0 | X1 | X2 | Х3 | CGROM address     | HEX | X0 | X1 | X2 | Х3 | CGROM address     |

|-----|----|----|----|----|-------------------|-----|----|----|----|----|-------------------|

| 00  | 0  | 0  | 0  | 0  | RAM00 (00000000B) | 08  | 0  | 0  | 0  | 1  | RAM08 (00001000B) |

| 01  | 1  | 0  | 0  | 0  | RAM01 (00000001B) | 09  | 1  | 0  | 0  | 1  | RAM09 (00001001B) |

| 02  | 0  | 1  | 0  | 0  | RAM02 (00000010B) | 0A  | 0  | 1  | 0  | 1  | RAM0A (00001010B) |

| 03  | 1  | 1  | 0  | 0  | RAM03 (00000011B) | 0B  | 1  | 1  | 0  | 1  | RAM0B (00001011B) |

| 04  | 0  | 0  | 1  | 0  | RAM04 (00000100B) | 0C  | 0  | 0  | 1  | 1  | RAM0C (00001100B) |

| 05  | 1  | 0  | 1  | 0  | RAM05 (00000101B) | 0D  | 1  | 0  | 1  | 1  | RAM0D (00001101B) |

| 06  | 0  | 1  | 1  | 0  | RAM06 (00000110B) | 0E  | 0  | 1  | 1  | 1  | RAM0E (00001110B) |

| 07  | 1  | 1  | 1  | 0  | RAM07 (00000111B) | 0F  | 1  | 1  | 1  | 1  | RAM0F (00001111B) |

### Positional relationship between the output area of CGRAM

Note: CGROM\_A and CGROM\_B (Character Generator ROM A, B) have an 8-bit address to generate  $5 \times 7$  dot matrix character patterns.

Each of CGROM\_A and CGROM\_B can store 240 types of character patterns.

The contents of CGROM\_A and CGROM\_B can be set separately.

General-purpose code -01 is available (see ROM code tables) and custom codes are provided on customer's request.

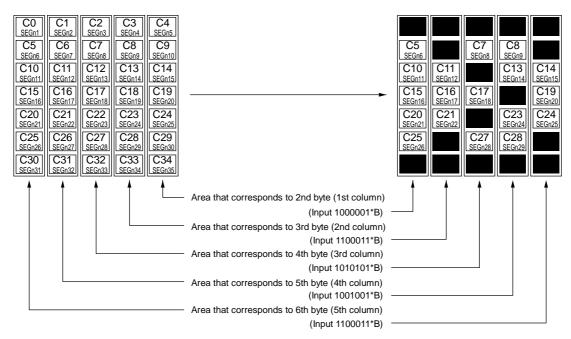

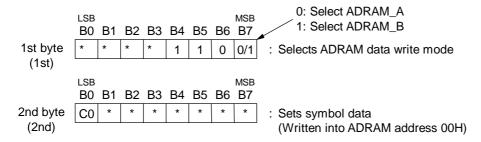

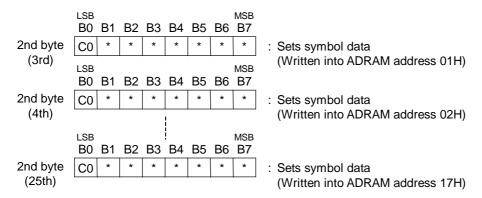

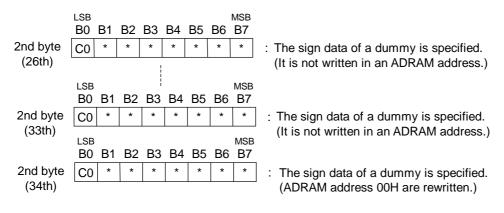

# 3,B. ADRAM data write (ADRAM writes symbol data)

ADRAM (Additional Data RAM) has a 1-bit address to store symbol data. Symbol data specified by ADRAM is directly output without CGROM and CGRAM. (The ADRAM can store 1 type of symbol patterns for each digit.)

The terminal to which the contents of ADRAM are output can be used as a cursor.

#### [Command format]

To specify symbol data continuously to the next address, specify only character data as follows. The address of ADRAM is automatically incremented. Specification of addresses is unnecessary.

A character code setup of 24-Digit is completion in the above work.

Furthermore, you have to specify the character codes of a dummy to be ADRAM and 18H-1FH to perform a character code setup from ADRAM address 00H continuously.

(In order to carry out the increment of the address of ADRAM automatically and to set a ADRAM address to 00H.)

C0: Symbol data (1 bit: 1-symbol data per digit)

\*: Don't care

# [COM positions and ADRAM addresses]

| ADRAM address<br>(HEX) | СОМ   | ADRAM address<br>(HEX) | СОМ   | ADRAM address<br>(HEX)           | СОМ               |

|------------------------|-------|------------------------|-------|----------------------------------|-------------------|

| 00                     | COM1  | 0C                     | COM13 | 18                               | Dammy             |

| 01                     | COM2  | 0D                     | COM14 | 19                               | Dammy             |

| 02                     | COM3  | 0E                     | COM15 | 1A                               | Dammy             |

| 03                     | COM4  | 0F                     | COM16 | 1B                               | Dammy             |

| 04                     | COM5  | 10                     | COM17 | 1C                               | Dammy             |

| 05                     | COM6  | 11                     | COM18 | 1D                               | Dammy             |

| 06                     | COM7  | 12                     | COM19 | 1E                               | Dammy             |

| 07                     | COM8  | 13                     | COM20 | 1F                               | Dammy             |

| 08                     | COM9  | 14                     | COM21 |                                  |                   |

| 09                     | COM10 | 15                     | COM22 | Dummy is put in address from 00H | to set up a ADRAM |

| 0A                     | COM11 | 16                     | COM23 | addic55 from 001                 | i continuousiy.   |

| 0B                     | COM12 | 17                     | COM24 | •                                |                   |

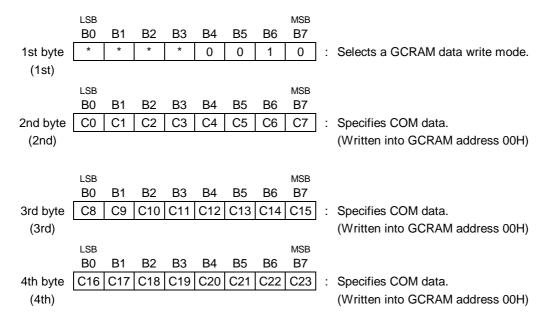

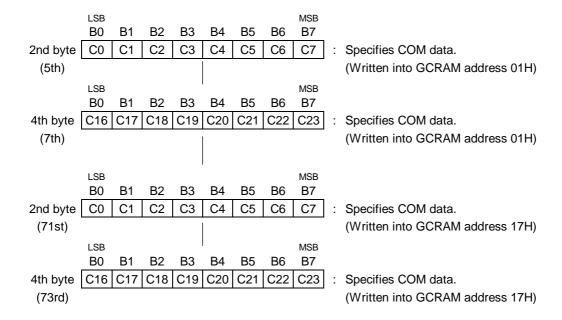

#### 4. GCRAM data write

(writes data by the number of COM outputs for digits)

GCRAM (Grid Control RAM) has a 5-bit address to control the number of COM outputs for digits.

GCRAM outputs specified data directly to COMn, allowing COM outputs to be controlled arbitrarily.

It is also possible to supply a large current by connecting a plurality of COMs outside the ML9204.

For example, when COM23 and COM24 are connected, the ML9204 has 23 display digits. In this case, the user specifies "23" as the number of display digits.

Write grid data at GCRAM addresses 00H and later.

Carry out this mode before putting-out-lights mode release.

Refer to a "setting operation flow chart" about the details of a setup.

Write COM data"0" in the GCRAM address which is not used for incorrect display prevention.

#### [Command format]

C0 (LSB) to C23 (MSB): Grid control data (24 bits)

\*: Don't Care

Note: To specify additional grid control data, specify the grid control data as shown below. The GCRAM addresses are automatically incremented.

The second byte to the fourth byte (for grid data) are treated as a single piece of element and the byte-byte  $t_{DOFF}$  can be 200 ns.

With the above operations, COM data of up to 24 digits are set. To set other COM data at GCRAM addresses 00H and later, specify dummy symbol data at GCRAM addresses 18H to 1FH (to automatically increment the GCRAM address and set the GCRAM address to 00H).

[GCRAM addresses (digit positions) and COM positions]

| GCRAM<br>address<br>(HEX) | 1(00) | 2(01) | 3(02) | 22(15) | 23(16) | 24(17) |

|---------------------------|-------|-------|-------|--------|--------|--------|

| COM1                      | C0    | C1    | C2    | C21    | C22    | C23    |

| COM2                      | C0    | C1    | C2    | C21    | C22    | C23    |

| COM3                      | C0    | C1    | C2    | C21    | C22    | C23    |

| COM4                      | C0    | C1    | C2    | C21    | C22    | C23    |

| COM5                      | C0    | C1    | C2    | C21    | C22    | C23    |

|                           |       |       |       |        |        |        |

| COM20                     | C0    | C1    | C2    | C21    | C22    | C23    |

| COM21                     | C0    | C1    | C2    | C21    | C22    | C23    |

| COM22                     | C0    | C1    | C2    | C21    | C22    | C23    |

| COM23                     | C0    | C1    | C2    | C21    | C22    | C23    |

| COM24                     | C0    | C1    | C2    | C21    | C22    | C23    |

# [GCRAM output example]

1. When 4-digit of the 9-digit display requires an output current of 40 mA <Setup>

Number setup of display beams: 9-digit GCRAM setup:4-digit of COM4 and COM5 \* Write "0" also in the beam which is not used.

|         |       | ,,,,  | 10 0  | a150 111 | the ee | WIII ***I | 11011 15 | not as | -     |        |        |            |        |

|---------|-------|-------|-------|----------|--------|-----------|----------|--------|-------|--------|--------|------------|--------|

| GCRAM   |       |       |       |          |        |           |          |        |       |        |        |            |        |

| address | 1(00) | 2(01) | 3(02) | 4(03)    | 5(04)  | 6(05)     | 7(08)    | 8(07)  | 9(08) | 11(09) | 11(0A) | <br>23(16) | 24(17) |

| (HEX)   |       |       |       |          |        |           |          |        |       |        |        |            |        |

| COM1    | 1     | 0     | 0     | 0        | 0      | 0         | 0        | 0      | 0     | 0      | 0      | 0          | 0      |

| COM2    | 0     | 1     | 0     | 0        | 0      | 0         | 0        | 0      | 0     | 0      | 0      | 0          | 0      |

| COM3    | 0     | 0     | 1     | 0        | 0      | 0         | 0        | 0      | 0     | 0      | 0      | 0          | 0      |

| COM4    | 0     | 0     | 0     | 1        | 0      | 0         | 0        | 0      | 0     | 0      | 0      | <br>0      | 0      |

| COM5    | 0     | 0     | 0     | 1        | 0      | 0         | 0        | 0      | 0     | 0      | 0      | 0          | 0      |

| COM6    | 0     | 0     | 0     | 0        | 1      | 0         | 0        | 0      | 0     | 0      | 0      | 0          | 0      |

| COM7    | 0     | 0     | 0     | 0        | 0      | 1         | 0        | 0      | 0     | 0      | 0      | 0          | 0      |

| COM8    | 0     | 0     | 0     | 0        | 0      | 0         | 1        | 0      | 0     | 0      | 0      | 0          | 0      |

| COM9    | 0     | 0     | 0     | 0        | 0      | 0         | 0        | 1      | 0     | 0      | 0      | 0          | 0      |

| COM10   | 0     | 0     | 0     | 0        | 0      | 0         | 0        | 0      | 1     | 0      | 0      | 0          | 0      |

<sup>\*</sup> Strapping COM4 and COM5 brings display digits to 9 digits, and a current of 50 mA can be supplied.

2. When only one digit of the 22-digit display requires an output current of 60 mA <Setup>

Number setup of display beams:22-digit GCRAM setup:1-digit of COM1 and COM23 and COM24 \* Write "0" also in the beam which is not used.

|                           |       |       |       |       | 1110  | *************************************** |       | WIIICI | 1 10 1100 |        |  |        |        |        |

|---------------------------|-------|-------|-------|-------|-------|-----------------------------------------|-------|--------|-----------|--------|--|--------|--------|--------|

| GCRAM<br>address<br>(HEX) | 1(00) | 2(01) | 3(02) | 4(03) | 5(04) | 6(05)                                   | 7(08) | 8(07)  | 9(08)     | 11(09) |  | 22(15) | 23(16) | 24(17) |

| COM1                      | 1     | 0     | 0     | 0     | 0     | 0                                       | 0     | 0      | 0         | 0      |  | 0      | 0      | 0      |

| COM2                      | 0     | 1     | 0     | 0     | 0     | 0                                       | 0     | 0      | 0         | 0      |  | 0      | 0      | 0      |

| COM3                      | 0     | 0     | 1     | 0     | 0     | 0                                       | 0     | 0      | 0         | 0      |  | 0      | 0      | 0      |

|                           |       |       |       |       |       |                                         |       |        |           |        |  |        |        |        |

| COM22                     | 0     | 0     | 0     | 0     | 0     | 0                                       | 0     | 0      | 0         | 0      |  | 1      | 0      | 0      |

| COM23                     | 1     | 0     | 0     | 0     | 0     | 0                                       | 0     | 0      | 0         | 0      |  | 0      | 0      | 0      |

| COM24                     | 1     | 0     | 0     | 0     | 0     | 0                                       | 0     | 0      | 0         | 0      |  | 0      | 0      | 0      |

<sup>\*</sup> Strapping COM1, COM23 and COM24 brings display digits to 22 digits, and a current of 75 mA can be supplied.

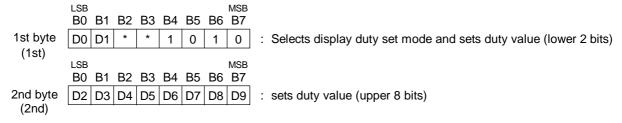

# 5. Display duty set

(writes display duty value to duty cycle register)

Display duty adjusts brightness in 1024 stages using 10-bit data.

When power is turned on or when the  $\overline{RESET}$  signal is input, the duty cycle register value is "0". Always execute this instruction before turning the display on, then set a desired duty value.

#### [Command format]

D0 (LSB) to D9 (MSB) : Display duty data (10 bits: 1024 stages)

\*: Don't care

[Relation between setup data and controlled COM duty]

| •             | HEX | D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 | D8 | D9 | COM duty                                |

|---------------|-----|----|----|----|----|----|----|----|----|----|----|-----------------------------------------|

| ightharpoonup | 000 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0/1024                                  |

|               | 001 | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1/1024                                  |

|               | 002 | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 2/1024                                  |

|               |     |    |    |    |    |    |    |    |    |    |    | *************************************** |

|               | 3BE | 0  | 1  | 1  | 1  | 1  | 1  | 0  | 1  | 1  | 1  | 958/1024                                |

|               | 3BF | 1  | 1  | 1  | 1  | 1  | 1  | 0  | 1  | 1  | 1  | 959/1024                                |

|               | 3C0 | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 1  | 1  | 960/1024                                |

|               | 3C1 | 1  | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 1  | 1  | 960/1024                                |

|               |     |    |    |    |    |    |    |    |    |    |    |                                         |

|               | 3FF | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 960/1024                                |

The state when power is turned on or when RESET signal is input.

### 6. Number of digits set

(writes the number of display digits to the display digit register)

The number of digits set can display 9 to 24 digits using 4-bit data.

When power is turned on or when a  $\overline{RESET}$  signal is input, the number of digit register value is "0". Always execute this instruction to change the number of digits before turning the display on.

#### [Command format]

K0 (LSB) to K3 (MSB): Number of digit data (4 bits: 24 digits)

\*: Don't care

[Relation between setup data and controlled COM]

\* When the number of COM is one at 1 digit

| •        | HEX | K0 | K1 | K2 | K3 | Number of digits of COM | HEX | K0 | K1 | K2 | K3 | Number of digits of COM |

|----------|-----|----|----|----|----|-------------------------|-----|----|----|----|----|-------------------------|

| <b>_</b> | 0   | 0  | 0  | 0  | 0  | 1-24(COM1 to 24)        | 0   | 0  | 0  | 0  | 1  | 1-16(COM1 to 16)        |

|          | 1   | 1  | 0  | 0  | 0  | 1-9(COM1 to 9)          | 1   | 1  | 0  | 0  | 1  | 1-17(COM1 to 17)        |

|          | 2   | 0  | 1  | 0  | 0  | 1-10(COM1 to 10)        | 2   | 0  | 1  | 0  | 1  | 1-18(COM1 to 18)        |

|          | 3   | 1  | 1  | 0  | 0  | 1-11(COM1 to 11)        | 3   | 1  | 1  | 0  | 1  | 1-19(COM1 to 19)        |

|          | 4   | 0  | 0  | 1  | 0  | 1-12(COM1 to 12)        | 4   | 0  | 0  | 1  | 1  | 1-20(COM1 to 20)        |

|          | 5   | 1  | 0  | 1  | 0  | 1-13(COM1 to 13)        | 5   | 1  | 0  | 1  | 1  | 1-21(COM1 to 21)        |

|          | 6   | 0  | 1  | 1  | 0  | 1-14(COM1 to 14)        | 6   | 0  | 1  | 1  | 1  | 1-22(COM1 to 22)        |

|          | 7   | 1  | 1  | 1  | 0  | 1-15(COM1 to 15)        | 7   | 1  | 1  | 1  | 1  | 1-23(COM1 to 23)        |

The state when power is turned on or when RESET signal is input.

# 7. All display lights ON/OFF set (turns all display lights ON or OFF)

All display lights ON is used primarily for display testing.

All display lights OFF is primarily used for display blink and to prevent malfunction when power is turned on.

# [Command format]

L, H: Display operation data

\*: Don't care

[Set data and display state of SEG and AD]

| L | Ι | Display state of SEG and AD |

|---|---|-----------------------------|

| 0 | 0 | Normal display              |

| 1 | 0 | Sets all outputs to Low     |

| 0 | 1 | Sets all outputs to High    |

| 1 | 1 | Sets all outputs to High    |

<sup>\*</sup> Priority is given to an all-points light command.

#### C. Key scan stop

This command stops key scanning and makes ROW1 to ROW5 outputs "Low" and the INT output "Low".

#### [Command format]

|          | LSB |    |    |    |    |    |    | MSB |                       |

|----------|-----|----|----|----|----|----|----|-----|-----------------------|

|          | B0  | B1 | B2 | В3 | B4 | B5 | B6 | B7  |                       |

| 1st byte | *   | *  | *  | *  | 0  | 0  | 1  | 1   | : stops key scanning. |

\*: Don't Care

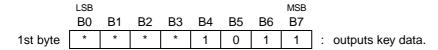

#### D. Key data output

This command puts the pin in the output mode and causes the pin to output the scanned switch data.

The DI/O pin outputs 42-bit switch data at the rise of a clock.

When the  $\overline{CS}$  pin goes high, the DI/O pin enters the output mode.

"R1, R2, R3 = 0" means turning a control knob clockwise.

"R1, R2, R3 = 1" means turning a control knob counterclockwise.

Contact count bits are Q11(LSB) to Q13(MSB), Q21(LSB) to Q23(MSB), and Q31(LSB) to Q33(MSB).

#### [Command format]

\*: Don't Care

# [COL input and ROW output key-switch matrix]

[Output Data Format] Output data: 42 bits

$5 \times 6$  push switch data: 30 bits Encoder switch data: 12 bits

| Bit         | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8   | 9   | 10  | 11  | 12  |

|-------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Output Data | S11 | S12 | S13 | S14 | S15 | S16 | S21 | S22 | S23 | S24 | S25 | S26 |

| Bit         | 13  | 14  | 15  | 16  | 17  | 18  | 19  | 20  | 21  | 22  | 23  | 24  |

| Output Data | S31 | S32 | S33 | S34 | S35 | S36 | S41 | S42 | S43 | S44 | S45 | S46 |

| Bit         | 25  | 26  | 27  | 28  | 29  | 30  | 31  | 32  | 33  | 34  | 35  | 36  |

| Output Data | S51 | S52 | S53 | S54 | S55 | S56 | R1  | Q11 | Q12 | Q13 | R2  | Q21 |

| Bit         | 37  | 38  | 39  | 40  | 41  | 42  |     |     |     |     |     |     |

| Output Data | Q22 | Q23 | R3  | Q31 | Q32 | Q33 |     |     |     |     |     |     |

Sij: i = ROW1 to 5; j = COL1 to 6 Sij = 1: switch ON Sij = 0: switch OFF

#### Keyscan

Keyscanning is started only when depression or release of any key is detected in order to minimize noise caused by scanning signal. Then, keyscanning is continued until the keyscan stop mode is sent from a microcomputer. The INT pin goes to the high level at the completion of 1-cycle scanning after the keyscan start, so the (high level) signal sent from the INT pin can be used as an interrupt signal.

# [Keyscan Timing and Cycles]

Keyscanning cannot be stopped by selecting the keyscan stop mode only once if:

- keyscanning is started after depression or release of any key is detected, and then

- a key is depressed or released again before the keyscan stop mode is selected.

To stop keyscanning, it is required to select the keyscan stop mode once again.

KS: Keyscan stop mode

The rotary encoder switch function

As Figure 1 shows, the rotary encoder switch circuit is consisted of Phase detection, Interrupt generation, Up/down counter, Direction latch and Parallel-in serial-out shift register.

The Rotary Encoder Switch Circuit

#### 1. Phase detection

#### 1-1. Clockwise rotation

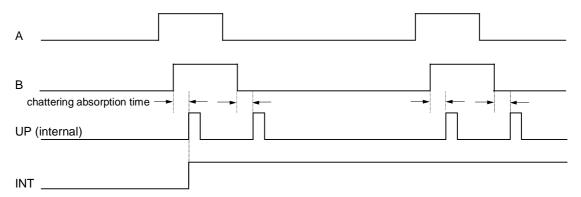

The input A and B have a chattering absorption circuit of  $256 \,\mu s$  period. When signal A and B input as shown below, the phase detection circuit outputs UP signal after the chattering absorption period. At this time, the output INT also goes to high level, so this signal can be used as an interrupt. The INT stays High level until the keyscan stop mode is selected.

The Input and Output Timing in the Case of Clockwise Rotation

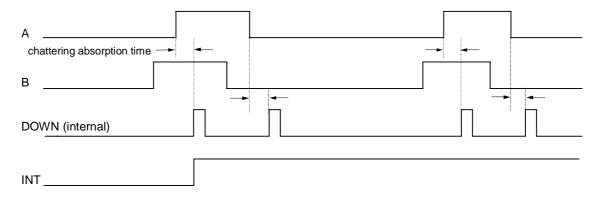

#### 1-2. Counterclockwise rotation

When signal A and B input as shown below, the phase detection circuit outputs Down signal after the chattering absorption period. At this time, the output INT also goes to High level. The INT stays High level until the keyscan stop mode is selected.

The Input and Output Timing in the Case of Counterclockwise Rotation

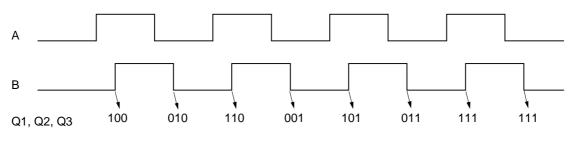

#### 2. UP/DOWN COUNTER

When the UP/DOWN COUNTER is input UP, it counts up and when it is input DOWN, it counts down. But if the UP/DOWN COUNTER is incremented beyond "111", it stays "111".

**Counter Overflow**

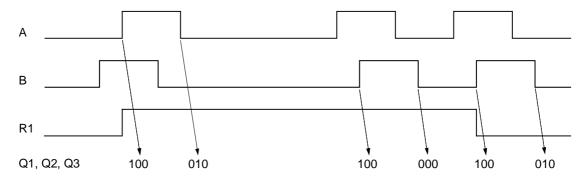

#### 3. Direction latch

When the Direction latch is input DOWN the output R1 goes "1". But if the UP pulse is input and the count value changes to a positive value, the output R1 goes to "0".

**Direction Latch**

#### F. Standby mode set

(Display all switched off and an oscillation stopped)

Standby mode realizes low power consumption of VDD, VSEG, and VCOM by all switching off a display, stopping an oscillation of an external (COM is fixed to Low) oscillation child, and stopping internal operation completely. All display lights OFF is primarily used for display blink and to prevent malfunction when power is turned on.

\* If a RESET signal is inputted during standby mode execution, standby mode is canceled, and keep in mind it that all states will be initialized.

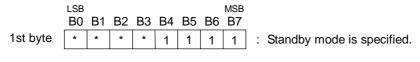

#### [Command format]

\*: Don't care

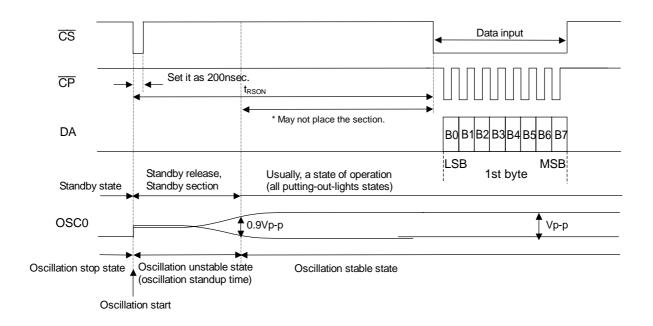

#### [Release standby mode]

Release in standby mode is performed in falling of  $\overline{CS}$ . (An oscillation child's oscillation is started)

Data input will become possible if an oscillation is stabilized. (Please return brought-down  $\overline{\text{CS}}$  high-level before data input)

When you display after standby mode release since it is all putting out lights although the setting state is held, please cancel all putting-out-lights modes (in usual mode).

\* Please do not input a shift clock into  $\overline{\mathsf{CP}}$  until an oscillation is stabilized. (Data will be given) tRSON (oscillation standup time) changes with oscillation children who use it. Please make reference an oscillation child's data to be used.

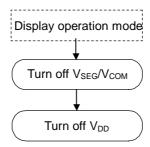

#### **POWER-OFF FLOWCHART**

#### APPLICATION CIRCUIT