# W65C816S DATA SHEET

WDC reserves the right to make changes at any time without notice in order to improve design and supply the best possible product. Information contained herein is provided gratuitously and without liability, to any user. Reasonable efforts have been made to verify accuracy of the information but no guarantee whatsoever is given as to the accuracy or as to its applicability to particular uses. In every instance, it must be the responsibility of the user to determine the suitability of the products for each application. WDC products are not authorized for use as critical components in life support devices or systems. Nothing contained herein shall be construed as a recommendation to use any product in violation of existing patents or other rights of third parties. The sale of any WDC product is subject to all WDC Terms and Conditions of Sales and Sales Policies, copies of which are available upon request.

Copyright (C) 1981-2001 by The Western Design Center, Inc. All rights reserved, including the right of reproduction in whole or in part in any form.

# **TABLE OF CONTENTS**

| INTRODUC' | ΓΙΟΝ                                                                  | 1  |

|-----------|-----------------------------------------------------------------------|----|

| SECTION 1 | W65C816S FUNCTIONAL DESCRIPTION                                       | 2  |

| 1 1       | Instantica Desistante d'Dese de                                       | 2  |

| 1.1       | Instruction Register and Decode                                       | 2  |

| 1.2       | Timing Control Unit                                                   | 2  |

| 1.3       | Arithmetic and Logic Unit                                             |    |

| 1.4       | Internal Registers                                                    |    |

| 1.5       | Accumulators                                                          |    |

| 1.6       | Data Bank Register                                                    | 3  |

| 1.7       | Direct                                                                |    |

| 1.8       | Index                                                                 | 3  |

| 1.9       | Processor Status                                                      | 3  |

| 1.10      | Program Bank Register                                                 | 3  |

| 1.11      | Program Counter                                                       | 4  |

| 1.12      | Stack Pointer                                                         | 4  |

|           | Figure 1-1 W65C816S Internal Architecture Simplified Block Diagram    | 5  |

|           | Figure 1-2 W65C816S Microprocessor Programming Model                  |    |

|           | Figure 1-3 W65C816S Status Register Coding                            | 6  |

| SECT      | ION 2 PIN FUNCTION DESCRIPTION         E:       0.1 NUCCORD (0.44 E): |    |

|           | Figure 2-1 W65C816S 44 Pin PLCC Pinout                                |    |

|           | Figure 2-2 W65C816S 40 Pin PDIP Pinout                                |    |

|           | Figure 2-3 W65C816S 44 PIN QFP Pinout                                 |    |

|           | Table 2-1   Pin Function Table                                        |    |

| 2.1       |                                                                       | 10 |

| 2.2       | Address Bus                                                           |    |

| 2.3       |                                                                       | 11 |

| 2.4       | Data/Address Bus                                                      |    |

| 2.5       |                                                                       | 11 |

| 2.6       | 1 1                                                                   | 11 |

| 2.7       | J                                                                     | 11 |

| 2.8       | Memory/Index Select Status                                            |    |

| 2.9       | Non-Maskable Interrupt                                                |    |

| 2.10      | Phase 2 In                                                            | 12 |

| 2.11      | Read/Write                                                            | 12 |

| 2.12      | Ready                                                                 | 12 |

| 2.13      | Reset                                                                 |    |

| 2.14      | Valid Data Address and Valid Program Address                          | 13 |

| 2.15      | VDD and VSS                                                           |    |

| 2.16      |                                                                       | 13 |

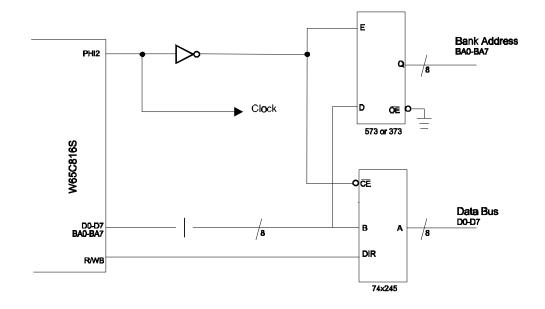

# SECTION 3 ADDRESSING MODES 14 3.1 Reset and Interrupt Vectors 14 3.2 3.3 3.4 3.5 Data Address Space 14 Table 3-2 Addressing Mode Summary 20 SECTION 4 TIMING, AC AND DC CHARACTERISTICS 21 4.1 Absolute Maximum Ratings 21 Table 4-1 Absolute Maximum Ratings 21 4.2 Table 4-2 DC Characteristics 22 4.3 AC Characteristics 23 Table 4-3 W65C816S AC Characteristics - 14 MHz23 SECTION 5 OPERATION TABLES 25 Table 5.1 W65C816S Instruction Set-Alphabetical Sequence 25 Table 5-2 Vector Locations 26 Table 5-3 OpCode Matrix 27 Table 5-4 Operation, Operation Codes and Status Register 29 Table 5-5 Instruction Operation 33 Figure 5-1 Bank Address Latching Circuit 41 SECTION 6 RECOMMENDED W65C816S ASSEMBLER SYNTAX STANDARDS., 42

| 6.1 | Directives                        | 42 |

|-----|-----------------------------------|----|

|     | Comments                          |    |

|     | The Source Line                   |    |

|     | Table 6-1 Alternate Mnemonics     |    |

|     | Table 6-2 Address Mode Formats    |    |

|     | Table 6-3 Byte Selection Operator | 45 |

|     | • •                               |    |

| <b>SECTION 7</b> | CAVEATS                                                               | 46 |

|------------------|-----------------------------------------------------------------------|----|

|                  | Table 7-1 W65C816S Compatibility Issues                               | 46 |

| 7.1              | Stack Addressing                                                      |    |

| 7.2              | Direct Addressing                                                     |    |

| 7.3              | Absolute Indexed Addressing                                           |    |

| 7.4              | ABORTB Input                                                          |    |

| 7.5              | VDA and VPA Valid Memory Address Output Signals                       | 50 |

| 7.6              | Apple II, IIe, IIc and II+ Disk Systems                               |    |

| 7.7              | DB/BA operation when RDY is Pulled Low                                | 50 |

| 7.8              | MX Output                                                             | 50 |

| 7.9              | All OpCodes Function in All Modes of Operation                        | 50 |

| 7.10             | Indirect Jumps                                                        |    |

| 7.11             | Switching Modes                                                       |    |

| 7.12             | How Hardware Interrupts, BRK, and COP Instructions Affect the Program |    |

|                  | Bank and the Data Bank Registers                                      | 51 |

| 7.13             | Binary Mode                                                           |    |

| 7.14             | WAI Instruction                                                       |    |

| 7.15             | The STP Instruction                                                   |    |

| 7.16             | COP Signatures                                                        |    |

| 7.17             | WDM OpCode Use                                                        |    |

| 7.18             | RDY Pulled During Write                                               |    |

| 7.19             | MVN and MVP Affects on the Data Bank Register                         |    |

| 7.20             | Interrupt Priorities                                                  |    |

| 7.21             | Transfers from 8-Bit to 16-Bit, or 16-Bit to 8-Bit Registers          |    |

| 7.22             | Stack Transfers                                                       |    |

| 7.23             | BRK Instruction                                                       |    |

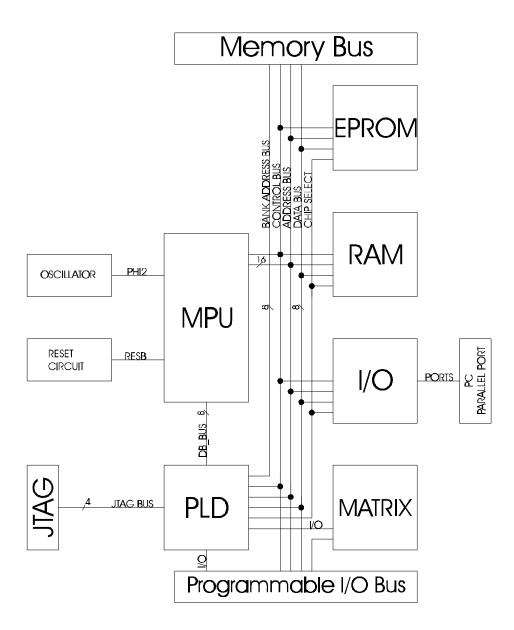

| SECTION 8        | W65C816 DEVELOPER BOARD                                               | 53 |

| 8.1              | W65C816S Developer Board Block Diagram                                | 53 |

| SECTION 9        | HARD CORE MODEL                                                       | 55 |

| 9.1              | W65C816 Core information                                              | 55 |

| SECTION 1        | ) SOFT CORE RTL MODEL                                                 | 56 |

| SECTION 1        | I FIRM CORE MODEL                                                     | 57 |

| SECTION 12 O     | RDERING INFORMATION                                                   | 58 |

#### W65C816S

## **INTRODUCTION**

The WDC W65C816S is a fully static CMOS 16-bit microprocessor featuring software compatibility\* with the 8-bit NMOS and CMOS 6500-series predecessors. The W65C816S extends addressing to a full 16 megabytes. These devices offer the many advantages of CMOS technology, including increased noise immunity, higher reliability, and greatly reduced power requirements. A software switch determines whether the processor is in the 8-bit "emulation" mode, or in the native mode, thus allowing existing systems to use the expanded features.

As shown in the processor programming model, Figure 1-1, the Accumulator, ALU, X and Y Index registers, and Stack Pointer register have all been extended to 16 bits. A new 16-bit Direct Page register augments the Direct Page addressing mode (formerly Zero Page addressing). Separate Program Bank and Data Bank registers allow 24-bit memory addressing with segmented or linear addressing.

Four new signals provide the system designer with many options. The ABORT input can interrupt the currently executing instruction without modifying internal register, thus allowing virtual memory system design. Valid Data Address (VDA) and Valid Program Address (VPA) outputs facilitate dual cache memory by indicating whether a data segment or program segment is accessed. Modifying a vector is made easy by monitoring the Vector Pull (VP) output. Future Microprocessors will support all current W65C816S operating modes for both index and offset address generation.

The information included in this data sheet reflects a standard 5 volt power supply specification. The testing process can be modified to meet most custom needs for power supply voltage, temperature or timing.

#### KEY FEATURES OF THE W65C816S

- Advanced fully static CMOS design for low power consumption and increased noise immunity

- Single 1.2-6.0 volt power supply, as specified

- Emulation mode allows complete hardware and software compatibility with 6502 designs

- 24-bit address bus allows access to 16 MBytes of memory space

- Full 16-bit ALU, Accumulator, Stack Pointer and Index Registers

- Valid Data Address (VDA) and Valid Program Address (VPA) output allows dual cache and cycle steal DMA implementation

- Vector Pull (VP) output indicates when interrupt vectors are being addressed; may be used to implement vectored interrupt design

- Abort (ABORT) input and associated vector supports virtual memory system design

- Low power consumption (2mA @ 1MHz) allows battery-powered operation (1FA) standby current.

- Separate program and data bank registers allow program segmentation or full 16 MByte linear addressing

- New Direct Register and stack relative addressing provides capability for re-entrant, re-cursive and re-locatable programming

- 24 addressing modes 13 original 6502 modes with 92 instructions using 256 OpCodes

- Wait-for-Interrupt (WAI) and Stop-the-Clock (STP) instructions further reduce power consumption, decrease interrupt latency and allows synchronization with external events

- Co-Processor (COP) instruction with associated vector supports co-processor configurations, i.e., floating point processors

- Block move ability

\*Except for the bit manipulation instructions which do not exist for the W65C816S

# **SECTION 1**

# W65C816S FUNCTIONAL DESCRIPTION

The W65C816S provides the design engineer with upward mobility and software compatibility in applications where a 16-bit system configuration is desired. The W65C816S's 16-bit hardware configuration, coupled with current software, allows a wide selection of system applications. In the Emulation mode, the W65C816S offers many advantages, including full software compatibility with 6502 coding. In addition, the W65C816S's powerful instruction set and addressing modes make it an excellent choice for new 16-bit designs.

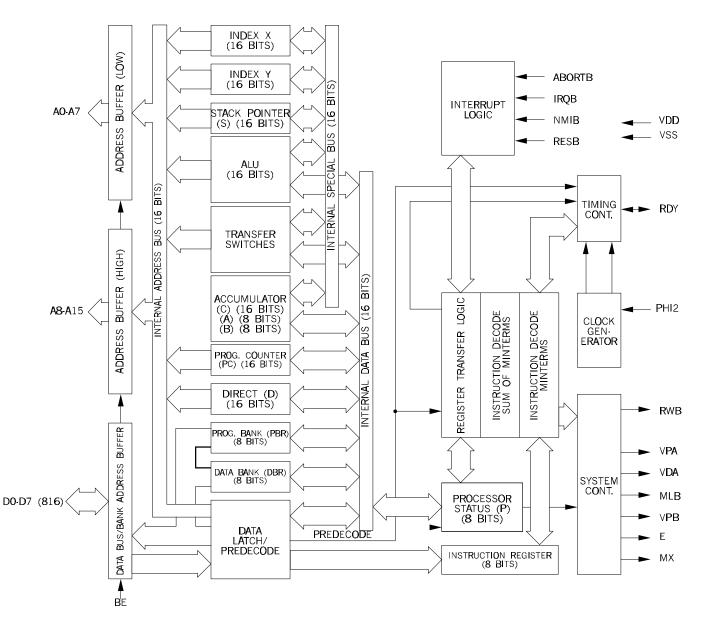

Internal organization of the W65C816S can be divided into two parts: 1) The Register Section and 2) The Control Section. Instructions (or OpCodes) obtained from program memory are executed by implementing a series of data transfers within the Register Section. Signals that cause data transfers to be executed are generated within the Control Section. The W65C816S has a 16-bit internal architecture with an 8-bit external data bus.

#### 1.1 Instruction Register and Decode (IR)

An OpCode enters the processor on the Data Bus, and is latched into the Instruction Register during the instruction fetch cycle. This instruction is then decoded, along with timing and interrupt signals, to generate the various Instruction Register control signals.

#### 1.2 Timing Control Unit (TCU)

The Timing Control Unit keeps track of each instruction cycle as it is executed. The TCU is set to zero each time an instruction fetch is executed, and is advanced at the beginning of each cycle for as many cycles as is required to complete the instruction. Each data transfer between registers depends upon decoding the contents of both the Instruction Register and the Timing Control Unit.

1.3 Arithmetic and Logic Unit (ALU)

All arithmetic and logic operations take place within the 16-bit ALU. In addition to data operations, the ALU also calculates the effective address for relative and indexed addressing modes. The result of a data operation is stored in either memory or an internal register. Carry, Negative, Overflow and Zero flags may be updated following the ALU data operation.

- 1.4 Internal Registers (Refer to Programming Model)

- 1.5 Accumulators (A,B,C)

The Accumulator is a general purpose register which stores one of the operands, or the result of most arithmetic and logical operations. In the Native mode (E=0), when the Accumulator Select Bit (M) equals zero, the Accumulator is established as 16 bits wide (A, B=C). When the Accumulator Select Bit (M) equals one, the Accumulator is 8 bits wide (A). In this case, the upper 8 bits (B) may be used for temporary storage in conjunction with the Exchange Accumulator (XBA) instruction.

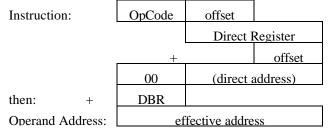

# 1.6 Data Bank Register (DBR)

During modes of operation, the 8-bit Data Bank Register holds the default bank address for memory transfers. The 24-bit address is composed of the 16-bit instruction effective address and the 8-bit Data Bank address. The register value is multiplexed with the data value and is present on the Data/Address lines during the first half of a data transfer memory cycle for the W65C816S. The Data Bank Register is initialized to zero during Reset.

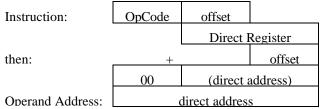

#### 1.7 Direct (D)

The 16-bit Direct Register provides an address offset for all instructions using direct addressing. The effective bank zero address is formed by adding the 8-bit instruction operand address to the Direct Register. The Direct Register is initialized to zero during Reset.

#### 1.8 Index (X and Y)

There are two Index Registers (X and Y) which may be used as general purpose registers or to provide an index value for calculation of the effective address. When executing an instruction with indexed addressing, the microprocessor fetches the OpCode and the base address, and then modifies the address by adding the Index Register contents to the address prior to performing the desired operation. Pre-indexing or post-indexing of indirect addresses may be selected. In the Native mode (E=0), both Index Registers are 16 bits wide (providing the Index Select Bit (X) equals zero). If the Index Select Bit (X) equals one, both registers will be 8 bits wide, and the high byte is forced to zero.

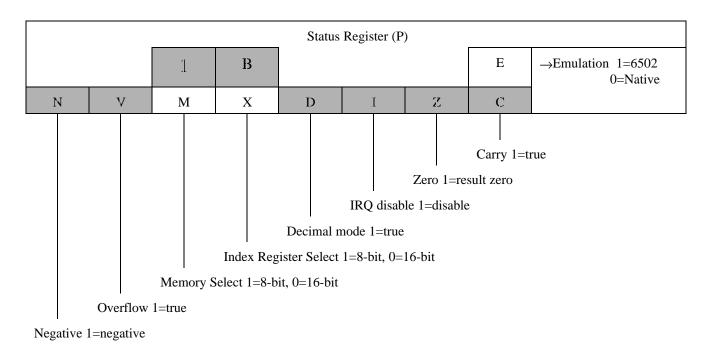

#### 1.9 Processor Status (P)

The 8-bit Processor Status Register contains status flags and mode select bits. The Carry (C), Negative (N), Overflow (V), and Zero (Z) status flags serve to report the status of most ALU operations. These status flags are tested by use of Conditional Branch instructions. The Decimal (D), IRQ Disable (I), Memory/Accumulator (M), and Index (X) bits are used as mode select flags. These flags are set by the program to change microprocessor operations.

The Emulation (E) select and the Break (B) flags are accessible only through the Processor Status Register. The Emulation mode select flag is selected by the Exchange Carry and Emulation Bits (XCE) instruction. Table 8-1, W65C816S Compatibility Information, illustrates the features of the Native (E=0) and Emulation (E=1) modes. The M and X flags are always equal to one in the Emulation mode. When an interrupt occurs during the Emulation mode, the Break flag is written to stack memory as bit 4 of the Processor Status Register.

# 1.10 Program Bank Register (PBR)

The 8-bit Program Bank Register holds the bank address for all instruction fetches. The 24-bit address consists of the 16-bit instruction effective address and the 8-bit Program Bank address. The register value is multiplexed with the data bus and presented on the Data bus lines during the first half of a program memory cycle. The Program Bank Register is initialized to zero during Reset. The PHK instruction pushes the PBR register onto the Stack.

# 1.11 Program Counter (PC)

The 16-bit Program Counter Register provides the addresses which are used to step the microprocessor through sequential program instructions. The register is incremented each time an instruction or operand is fetched from program memory.

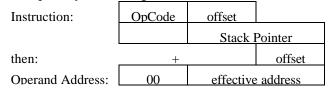

#### 1.12 Stack Pointer (S)

The Stack Pointer is a 16-bit register which is used to indicate the next available location in the stack memory area. It serves as the effective address in stack addressing modes as well as subroutine and interrupt processing. The Stack Pointer allows simple implementation of nested subroutines and multiple-level interrupts. During the Emulation mode, the Stack Pointer high-order byte (SH) is always equal to one. The bank address for all stack operations is Bank zero.

Figure 1-1 W65C816S Internal Architecture Simplified Block Diagram

| 8 BITS                         | 8 BITS               | 8 BITS               |  |

|--------------------------------|----------------------|----------------------|--|

| Data Bank Register<br>(DBR)    | X Register (XH)      | X Register (XL)      |  |

| Data Bank Register<br>(DBR)    | Y Register (YH)      | Y Register (YL)      |  |

| 00                             | Stack Register (SH)  | Stack Register (SL)  |  |

|                                | Accumulator (B)      | Accumulator (A)      |  |

| Program Bank Register<br>(PBR) | Program (PCH)        | Counter (PCL)        |  |

| 00                             | Direct Register (DH) | Direct Register (DL) |  |

Shaded blocks = 6502 registers

# Figure 1-2 W65C816S Microprocessor Programming Model

Figure 1-3 W65C816S Status Register Coding

# **SECTION 2**

# **PIN FUNCTION DESCRIPTION**

(1) added for improved performance.

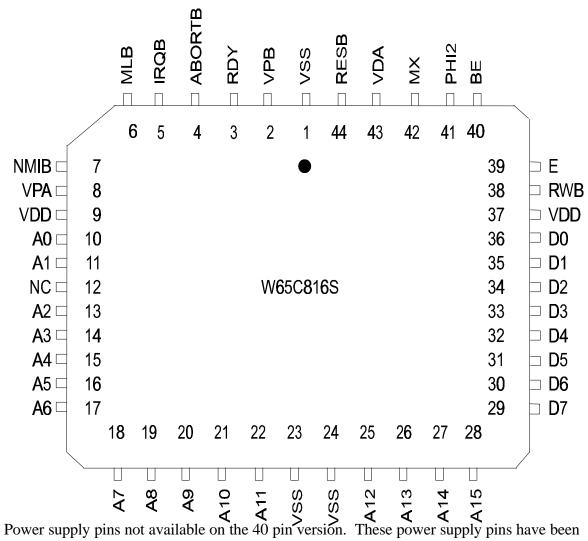

Figure 2-1 W65C816S 44 Pin PLCC Pinout

| VPB        | 1  |          | 40 | RESB |

|------------|----|----------|----|------|

| RDY        | 2  |          | 39 | VDA  |

| ABORTB     | 3  |          | 38 | MX   |

| IRQB       | 4  |          | 37 | PHI2 |

| MLB        | 5  |          | 36 | BE   |

| NMIB       | 6  |          | 35 | E    |

| VPA        | 7  |          | 34 | RWB  |

| VDD        | 8  |          | 33 | D0   |

| AO         | 9  |          | 32 | D1   |

| A1         | 10 | W65C816S | 31 | D2   |

| A2         | 11 | 00000100 | 30 | D3   |

| A3         | 12 |          | 29 | D4   |

| A4         | 13 |          | 28 | D5   |

| <b>A</b> 5 | 14 |          | 27 | D6   |

| A6         | 15 |          | 26 | D7   |

| A7         | 16 |          | 25 | A15  |

| A8         | 17 |          | 24 | A14  |

| A9         | 18 |          | 23 | A13  |

| A10        | 19 |          | 22 | A12  |

| A11        | 20 |          | 21 | VSS  |

|            |    |          |    |      |

Figure 2-2 W65C816S 40 Pin PDIP Pinout

|                                                                    | MLB                                                               | IRQB | ARBORTB | RDY              | VPB     | VSS (1)          | RESB            | VDA | MX  | PHI2 | BE                                                                   |                                                                     |

|--------------------------------------------------------------------|-------------------------------------------------------------------|------|---------|------------------|---------|------------------|-----------------|-----|-----|------|----------------------------------------------------------------------|---------------------------------------------------------------------|

| NMIB<br>VPA<br>VDD<br>A0<br>A1<br>NC<br>A2<br>A3<br>A4<br>A5<br>A6 | 44<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12 | 43   | 42      | <b>4</b> 1<br>15 | 40<br>W | 39<br>65C8<br>17 | 38<br>16S<br>18 | 37  | 36  | 35   | 34<br>32<br>31<br>30<br>29<br>28<br>27<br>26<br>25<br>24<br>23<br>22 | E<br>RWB<br>VDD (1)<br>D0<br>D1<br>D2<br>D3<br>D4<br>D5<br>D6<br>D7 |

|                                                                    | A7                                                                | A8   | A9      | A10              | A11     | (1) VSS          | VSS             | A12 | A13 | A14  | A15                                                                  |                                                                     |

(1) Power supply pins not available on the 40 pin version. These power supply pins have been added for improved performance.

Figure 2-3 W65C816S 44 PIN QFP

| Pin       | Description                      |

|-----------|----------------------------------|

| A0-A15    | Address Bus                      |

| ABORTB    | Abort Input                      |

| BE        | Bus Enable                       |

| PHI2      | Phase 2 In Clock                 |

| D0-D7/BA7 | Data Bus/Bank Address Bus        |

| Е         | Emulation Select                 |

| IRQB      | Interrupt Request                |

| MLB       | Memory Lock                      |

| MX        | Mode Select                      |

| NC        | No Connect                       |

| NMIB      | Non-Maskable Interrupt           |

| RDY       | Ready                            |

| RESB      | Reset                            |

| RWB       | Read/Write                       |

| VDA       | Valid Data Address               |

| VPB       | Vector Pull                      |

| VPA       | Valid Program Address            |

| VDD       | Positive Power Supply (+5 volts) |

| VSS       | Internal Logic Ground            |

# Table 2-1 Pin Function Table

# 2.1 Abort (ABORTB)

The Abort input is used to abort instructions (usually due to an Address Bus condition). A negative transition will inhibit modification of any internal register during the current instruction. Upon completion of this instruction, an interrupt sequence is initiated. The location of the aborted OpCode is stored as the return address in stack memory. The Abort vector address is 00FFF8,9 (Emulation mode) or 00FFE8,9 (Native mode). Note that ABORTB is a pulse-sensitive signal; i.e., an abort will occur whenever there is a negative pulse (or level) on the ABORTB pin during a PHI2 clock.

# 2.2 Address Bus (A0-A15)

These sixteen output lines form the Address Bus for memory and I/O exchange on the Data Bus. When using the W65C816S, the address lines may be set to the high impedance state by the Bus Enable (BE) signal.

# 2.3 Bus Enable (BE)

The Bus Enable input signal allows external control of the Address and Data Buffers, as well as the RWB signal. With Bus Enable high, the RWB and Address Buffers are active. The Data/Address Buffers are active during the first half of every cycle and the second half of a write cycle. When BE is low, these buffers are disabled. Bus Enable is an asynchronous signal.

#### 2.4 Data/Address Bus (D0-D7/BA7)

These eight lines multiplex address bits BA0-BA7 with the data value. The address is present during the first half of a memory cycle, and the data value is read or written during the second half of the memory cycle. Two memory cycles are required to transfer 16-bit values. These lines may be set to the high impedance state by the Bus Enable (BE) signal.

#### 2.5 Emulation Status (E)

The Emulation Status output reflects the state of the Emulation (E) mode flag in the Processor Status (P) Register. This signal may be thought of as an OpCode extension and used for memory and system management.

#### 2.6 Interrupt Request (IRQB)

The Interrupt Request input signal is used to request that an interrupt sequence be initiated. When the IRQB Disable (I) flag is cleared, a low input logic level initiates an interrupt sequence after the current instruction is completed. The Wait-for-Interrupt (WAI) instruction may be executed to ensure the interrupt will be recognized immediately. The Interrupt Request vector address is 00FFFE,F (Emulation mode) or 00FFEE,F (Native mode). Since IRQB is a level-sensitive input, an interrupt will occur if the interrupt source was not cleared since the last interrupt. Also, no interrupt will occur if the interrupt source is cleared prior to interrupt recognition. The IRQB signal going low causes 3 bytes of information to be pushed onto the stack before jumping to the interrupt handler. The first byte is the high byte in the Program Counter. The second byte is the Program Counter low byte. The third byte is the status register valve. These valves are used to return the processor to it's original state prior to the IRQ interrupt.

#### 2.7 Memory Lock (MLB)

The Memory Lock output may be used to ensure the integrity of Read-Modify-Write instructions in a multiprocessor system. Memory Lock indicates the need to defer arbitration of the next bus cycle. Memory Lock is low during the last three or five cycles of ASL, DEC, INC, LSR, ROL, ROR, TRB, and TSB memory referencing instructions, depending on the state of the M flag.

#### 2.8 Memory/Index Select Status (MX)

This multiplexed output reflects the state of the Accumulator (M) and Index (X) elect flags (bits 5 and 4 of the Processor Status (P) Register. Flag M is valid during the Phase 2 clock negative transition and Flag X is valid during he Phase 2 clock positive transition. These bits may be thought of as OpCode extensions and may be used for memory and system management.

#### 2.9 Non-Maskable Interrupt (NMIB)

A negative transition on the NMIB input initiates an interrupt sequence. A high-to-low transition initiates an interrupt sequence after the current instruction is completed. The Wait for Interrupt (WAI) instruction may be executed to ensure that the interrupt will be recognized immediately. The Non-Maskable Interrupt vector address is 00FFFA,B (Emulation mode) or 00FFEA,B (Native mode). Since NMIB is an edge-sensitive input, an interrupt will occur if there is a negative transition while servicing a previous interrupt. Also, no interrupt will occur if NMIB remains low. The NMIB signal going low causes 3 bytes of information to be pushed onto the stack before jumping to the interrupt handler. The first byte is the high byte in the Program Counter. The second byte is the Program Counter low byte. The third byte is the status register valve. These valves are used to return the processor to it's original state prior to the NMI interrupt.

#### 2.10 Phase 2 In (PHI2)

This is the system clock input to the microprocessor internal clock generator (equivalent to PHI0(IN) on the 6502). During the low power Standby Mode, PHI2 can be held in either state to preserve the contents of internal registers.

#### 2.11 Read/Write (RWB)

When the RWB output signal is in the high state, the microprocessor is reading data from memory or I/O. When in the low state, the Data Bus contains valid data from the microprocessor which is to be stored at the addressed memory location. When using the W65C816S, the RWB signal may be set to the high impedance state by Bus Enable (BE).

#### 2.12 Ready (RDY)

This bi-directional signal indicates that a Wait for Interrupt (WAI) instruction has been executed allowing the user to halt operation of the microprocessor. A low input logic level will halt the microprocessor in its current state. Returning RDY to the active high state allows the microprocessor to continue following the next Phase 2 In Clock negative transition. The RDY signal is internally pulled low following the execution of a Wait for Interrupt (WAI) instruction, and then returned to the high state when a RESB, ABORTB, NMIB, or IRQB external interrupt is provided. This feature may be used to eliminate interrupt latency by placing the WAI instruction at the beginning of the IRQB servicing routine. If the IRQB Disable flag has been set, the next instruction will be executed when the IRQB occurs. The processor will not stop after a WAI instruction if RDY has been forced to a high state. The Stop (STP) instruction has no effect on RDY. The RDY pin has an active pull-up. When outputting a low level, the pull-up is disabled. The RDY pin can still be wired ORed.

#### 2.13 Reset (RESB)

The Reset input is used to initialize the microprocessor and start program execution. The Reset input buffer has hysteresis such that a simple R-C timing circuit may be used with the internal pullup device. The RESB signal must be held low for at least two clock cycles after VDD reaches operating voltage. Ready (RDY) has no effect while RESB is being held low. The stack pointer must be initialized by the user's software. During the Reset conditioning period, the following period, the following processor initialization takes place:

|                |    |      |   | Regist | ers |   |   |     |                   |

|----------------|----|------|---|--------|-----|---|---|-----|-------------------|

|                | D= | 0000 |   |        |     |   |   | SH= | 01                |

|                | DB | R=00 |   |        |     |   |   | XH= | :00               |

|                | PR | B=00 |   |        |     |   |   | YH= | :00               |

|                | Ν  | V    | М | Х      | D   | Ι | Ζ | C/E |                   |

| $\mathbf{P} =$ | *  | *    | 1 | 1      | 0   | 1 | * | */1 | *=not initialized |

STP and WAI instructions are cleared.

| Signals |

|---------|

| VDA=0   |

| VPB =1  |

| VPA=0   |

|         |

When Reset is brought high, an interrupt sequence is initiated:

- RWB remains in the high state during the stack address cycles.

- The Reset vector address is 00FFFC,D.

#### 2.14 Valid Data Address and Valid Program Address (VDA and VPA)

These two output signals indicate valid memory addresses when high and must be used for memory or I/O address qualification.

#### VDA VPA

| , |   |                                                                                    |

|---|---|------------------------------------------------------------------------------------|

| 0 | 0 | Internal Operation-Address and Data Bus available. The Address Bus may be invalid. |

| 0 | 1 | Valid program address-may be used for program cache control.                       |

| 1 | 0 | Valid data address-may be used for data cache control.                             |

| 1 | 1 | OpCode fetch-may be used for program cache control and single step control         |

|   |   |                                                                                    |

#### 2.15 VDD and VSS

VDD is the positive supply voltage and VSS is system logic ground.

#### 2.16 Vector Pull (VPB)

The Vector Pull output indicates that a vector location is being addressed during an interrupt sequence. VPB is low during the last two interrupt sequence cycles, during which time the processor reads the interrupt vector. The VPB signal may be used to select and prioritize interrupts from several sources by modifying the vector addresses.

#### W65C816S

# **SECTION 3**

#### **ADDRESSING MODES**

The W65C816S is capable of directly addressing 16 MBytes of memory. This address space has special significance within certain addressing modes, as follows:

3.1 Reset and Interrupt Vectors

The Reset and Interrupt Vectors use the majority of the fixed addresses between 00FFE0 and 00FFFF.

3.2 Stack

The Stack may be use memory from 000000 to 00FFFF. The effective address of Stack and Stack Relative addressing modes will be always be within this range.

3.3 Direct

The Direct addressing modes are usually used to store memory registers and pointers. The effective address generated by Direct, Direct, X and Direct, Y addressing modes is always in Bank 0 (000000-00FFFF).

3.4 Program Address Space

The Program Bank register is not affected by the Relative, Relative Long, Absolute, Absolute Indirect, and Absolute Indexed Indirect addressing modes or by incrementing the Program Counter from FFFF. The only instructions that affect the Program Bank register are: RTI, RTL, JML, JSL, and JMP Absolute Long. Program code may exceed 64K bytes although code segments may not span bank boundaries.

#### 3.5 Data Address Space

The Data Address space is contiguous throughout the 16 MByte address space. Words, arrays, records, or any data structures may span 64 KByte bank boundaries with no compromise in code efficiency. The following addressing modes generate 24-bit effective addresses:

- Direct Indexed Indirect (d,x)

- Direct Indirect Indexed (d),y

- Direct Indirect (d)

- Direct Indirect Long [d]

- Direct Indirect Long Indexed [d],y

- Absolute a

- Absolute a,x

- Absolute a,y

- Absolute Long al

- Absolute Long Indexed al,x

- Stack Relative Indirect Indexed (d,x),y

#### W65C816S

The following addressing mode descriptions provide additional detail as to how effective addresses are calculated. Twenty-four addressing modes are available for the W65C816S.

#### 3.5.1 Immediate Addressing-#

The operand is the second byte (second and third bytes when in the 16-bit mode) of the instruction.

#### 3.5.2 Absolute-a

With Absolute addressing the second and third bytes of the instruction form the low-order 16 bits of the effective address. The Data Bank Register contains the high-order 8 bits of the operand address.

| Instruction: | OpCode | addrl | addrh |

|--------------|--------|-------|-------|

| Operand      | DBR    | addrh | addrl |

#### 3.5.3 Absolute Long-al

The second, third and fourth byte of the instruction form the 24-bit effective address.

| Instruction:     | OpCode | addrl | addrh | baddr |  |

|------------------|--------|-------|-------|-------|--|

| Operand Address: | baddr  | addrh | addrl |       |  |

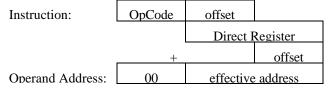

#### 3.5.4 Direct-d

The second byte of the instruction is added to the Direct Register (D) to form the effective address. An additional cycle is required when the Direct Register is not page aligned (DL not equal 0). The Bank register is always 0.

#### 3.5.5 Accumulator-A

This form of addressing always uses a single byte instruction. The operand is the Accumulator.

#### 3.5.6 Implied-i

Implied addressing uses a single byte instruction. The operand is implicitly defined by the instruction.

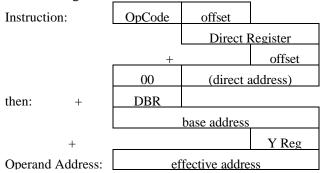

#### 3.5.7 Direct Indirect Indexed-(d),y

This address mode is often referred to as Indirect, Y. The second byte of the instruction is added to the Direct Register (D). The 16-bit contents of this memory location is then combined with the Data Bank register to form a 24-bit base address. The Y Index Register is added to the base address to form the effective address.

# W65C816S

#### 3.5.8 Direct Indirect Long Indexed-[d],y

With this addressing mode, the 24-bit base address is pointed to by the sum of the second byte of the instruction and the Direct Register. The effective address is this 24-bit base address plus the Y Index Register.

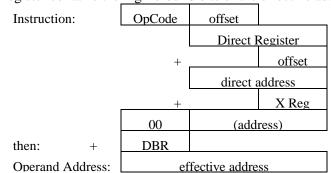

#### 3.5.9 Direct Indexed Indirect-(d,x)

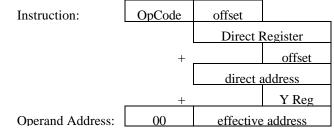

This address mode is often referred to as Indirect,X. The second byte of the instruction is added to the sum of the Direct Register and the X Index Register. The result points to the X low-order 16 bits of the effective address. The Data Bank Register contains the high-order 8 bits of the effective address.

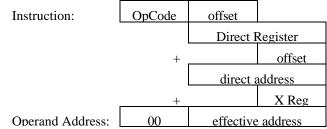

#### 3.5.10 Direct Indexed With X-d,x

The second byte of the instruction is added to the sum of the Direct Register and the X Index Register to form the 16-bit effective address. The operand is always in Bank 0.

#### 3.5.11 Direct Indexed With Y-d,y

The second byte of the instruction is added to the sum of the Direct Register and the Y Index Register to form the 16-bit effective address. The operand is always in Bank 0.

#### W65C816S

#### 3.5.12 Absolute Indexed With X-a,x

The second and third bytes of the instruction are added to the X Index Register to form the low-order 16-bits of the effective address. The Data Bank Register contains the high-order 8 bits of the effective address.

| Instruction: | OpCo | OpCo addrl        |       |  |  |

|--------------|------|-------------------|-------|--|--|

|              | DBR  | addrh             | addrl |  |  |

|              | +    | + X I             |       |  |  |

| Operand      | ef   | effective address |       |  |  |

#### 3.5.13 Absolute Long Indexed With X-al,x

The second, third and fourth bytes of the instruction form a 24-bit base address. The effective address is the sum of this 24-bit address and the X Index Register.

| Instruction: | OpCo addrl |       | addrh | baddr |

|--------------|------------|-------|-------|-------|

|              | baddr      | addrh | addrl |       |

|              | +          |       | X Reg |       |

| Operand      | effe       |       |       |       |

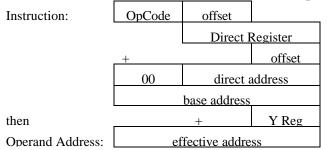

#### 3.5.14 Absolute Indexed With Y-a,y

The second and third bytes of the instruction are added to the Y Index Register to form the low-order 16 bits of the effective address. The Data Bank Register contains the high-order 8 bits of the effective address.

| Instruction: | OpCo              | addrh |  |  |

|--------------|-------------------|-------|--|--|

|              | DBR               | addrl |  |  |

|              | + Y Reg           |       |  |  |

| Operand      | effective address |       |  |  |

#### 3.5.15 Program Counter Relative-r

This address mode, referred to as Relative Addressing, is used only with the Branch instructions. If the condition being tested is met, the second byte of the instruction is added to the Program Counter, which has been updated to point to the OpCode of the next instruction. The offset is a signed 8-bit quantity in the range from -128 to 127. The Program Bank Register is not affected.

#### 3.5.16 Program Counter Relative Long-rl

This address mode, referred to as Relative Long Addressing, is used only with the Unconditional Branch Long instruction (BRL) and the Push Effective Relative instruction (PER). The second and third bytes of the instruction are added to the Program Counter, which has been updated to point to the OpCode of the next instruction. With the branch instruction, the Program Counter is loaded with the result. With the Push Effective Relative instruction, the result is stored on the stack. The offset is a signed 16-bit quantity in the range from -32768 to 32767. The Program Bank Register is not affected.

#### 3.5.17 Absolute Indirect-(a)

The second and third bytes of the instruction form an address to a pointer in Bank 0. The Program Counter is loaded with the first and second bytes at this pointer. With the Jump Long (JML) instruction, the Program Bank Register is loaded with the third byte of the pointer.

| Instruction:      | OpCode | addrl | addrh |       |

|-------------------|--------|-------|-------|-------|

| Indirect Address: |        | 00    | addrh | addrl |

New PC = (indirect address) with JML: New PC = (indirect address) New PBR = (indirect address +2)

#### W65C816S

#### 3.5.18 Direct Indirect-(d)

The second byte of the instruction is added to the Direct Register to form a pointer to the low-order 16 bits of the effective address. The Data Bank Register contains the high-order 8 bits of the effective address.

#### 3.5.19 Direct Indirect Long-[d]

The second byte of the instruction is added to the Direct Register to form a pointer to the 24-bit effective address.

#### 3.5.20 Absolute Indexed Indirect-(a,x)

The second and third bytes of the instruction are added to the X Index Register to form a 16-bit pointer in Bank 0. The contents of this pointer are loaded in the Program Counter. The Program Bank Register is not changed.

| Instruction: | OpCode | addrl   | addrh |

|--------------|--------|---------|-------|

|              |        | addrh   | addrl |

|              |        | X Reg   |       |

|              | PBR    | address |       |

then: PC = (address)

#### 3.5.21 Stack-s

Stack addressing refers to all instructions that push or pull data from the stack, such as Push, Pull, Jump to Subroutine, Return from Subroutine, Interrupts, and Return from Interrupt. The bank address is always 0. Interrupt Vectors are always fetched from Bank 0.

#### 3.5.22 Stack Relative-d,s

The low-order 16 bits of the effective address is formed from the sum of the second byte of the instruction and the stack pointer. The high-order 8 bits of the effective address is always zero. The relative offset is an unsigned 8-bit quantity in the range of 0 to 255.

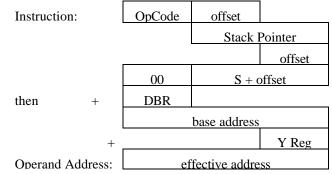

#### 3.5.23 Stack Relative Indirect Indexed-(d,s),y

The second byte of the instruction is added to the Stack Pointer to form a pointer to the low-order 16-bit base address in Bank 0. The Data Bank Register contains the high-order 8 bits of the base address. The effective address is the sum of the 24-bit base address and the Y Index Register.

#### 3.5.24 Block Source Bank, Destination Bank-xyc

This addressing mode is used by the Block Move instructions. The second byte of the instruction contains the high-order 8 bits of the destination address. The Y Index Register contains the low-order 16 bits of the destination address. The third byte of the instruction contains the high-order 8 bits of the source address. The X Index Register contains the low-order bits of the source address. The C Accumulator contains one less than the number of bytes to move. The second byte of the block move instructions is also loaded into the Data Bank Register.

| Instruction:    | OpCode | dstbnk | srcbnk |     |

|-----------------|--------|--------|--------|-----|

|                 |        | dstbnk | y DBR  |     |

| Source Address: |        | srcbnk | XI     | Reg |

| Dest. Address;  |        | DBR    | ΥI     | Reg |

Increment (MVN) or decrement (MVP) X and Y. Decrement C (if greater than zero), then PC+3 6 PC.

| Address Mode                                                | Instruction T               | imes in Memory<br>Cycle | Memory Utilization in<br>Number of Program Sequence<br>Bytes |                     |  |

|-------------------------------------------------------------|-----------------------------|-------------------------|--------------------------------------------------------------|---------------------|--|

|                                                             | Original 8-bit<br>NMOS 6502 | New W65C816S            | Original 8-bit<br>NMOS 6502                                  | New<br>W65C816<br>S |  |

| 1. Immediate                                                | 2                           | 2 (3)                   | 2                                                            | 2 (3)               |  |

| 2. Absolute                                                 | 4 (5)                       | 4 (3,5)                 | 3                                                            | 3                   |  |

| 3. Absolute Long                                            | -                           | 5 (3)                   | -                                                            | 4                   |  |

| 4. Direct                                                   | 3 (5)                       | 3 (3,4,5)               | 2                                                            | 2                   |  |

| 5. Accumulator                                              | 2                           | 2                       | 1                                                            | 1                   |  |

| 6. Implied                                                  | 2                           | 2                       | 1                                                            | 1                   |  |

| 7. Direct Indirect Indexed (d),y                            | 5 (1)                       | 5 (1,3,4)               | 2                                                            | 2                   |  |

| 8. Direct Indirect Indexed Long [d],y                       | -                           | 6 (3,4)                 | -                                                            | 2                   |  |

| 9. Direct Indexed Indirect (d,x)                            | 6                           | 6 (3,4)                 | 2                                                            | 2                   |  |

| 10. Direct, X                                               | 4 (5)                       | 4 (3,4,5)               | 2                                                            | 2                   |  |

| 11. Direct, Y                                               | 4                           | 4 (3,4)                 | 2                                                            | 2                   |  |

| 12. Absolute, X                                             | 4 (1,5)                     | 4 (1,3,5)               | 3                                                            | 3                   |  |

| 13. Absolute Long, X                                        | -                           | 5 (3)                   | -                                                            | 4                   |  |

| 14. Absolute, Y                                             | 4 (1)                       | 4 (1,3)                 | 3                                                            | 3                   |  |

| 15. Relative                                                | 2 (1,2)                     | 2 (2)                   | 2                                                            | 2                   |  |

| 16. Relative Long                                           | -                           | 3 (2)                   | -                                                            | 3                   |  |

| 17. Absolute Indirect (Jump)                                | 5                           | 5                       | 3                                                            | 3                   |  |

| 18. Direct Indirect                                         | -                           | 5 (3,4)                 | -                                                            | 2                   |  |

| 19. Direct Indirect Long                                    | -                           | 6 (3,4)                 | -                                                            | 2                   |  |

| 20. Absolute Indexed Indirect (Jump)                        | -                           | 6                       | -                                                            | 3                   |  |

| 21. Stack                                                   | 3-7                         | 3-8                     | 1-3                                                          | 1-4                 |  |

| 22. Stack Relative                                          |                             | 4 (3)                   | -                                                            | 2                   |  |

| 23. Stack Relative Indirect Indexed                         | -                           | 7 (3)                   | -                                                            | 2                   |  |

| 24. Block Move X,Y,C (Source,<br>Destination, Block Length) | -                           | 7                       | -                                                            | 3                   |  |

Table 3-2 Addressing Mode Summary

Notes (these are indicated in parentheses):

- 1. Page boundary, add 1 cycle if page boundary is crossed when forming address.

- 2. Branch taken, add 1 cycle if branch is taken.

- 3. M = 0 or X = 0, 16 bit operation, add 1 cycle, add 1 byte for immediate.

- 4. Direct register low (DL) not equal zero, add 1 cycle.

- 5. Read-Modify-Write, add 2 cycles for M = 1, add 3 cycles for M = 0.

# **SECTION 4**

# TIMING, AC AND DC CHARACTERISTICS

#### 4.1 Absolute Maximum Ratings

| Rating              | Symbol | Value             |

|---------------------|--------|-------------------|

| Supply Voltage      | VDD    | -0.3 to +7.0V     |

| Input Voltage       | VIN    | -0.3 to VDD +0.3V |

| Storage Temperature | TS     | -55°C to +150°C   |

Table 4-1 Absolute Maximum Ratings

This device contains input protection against damage due to high static voltages or electric fields; however, precautions should be taken to avoid application of voltages higher than the maximum rating.

Note: Exceeding these ratings may result in permanent damage. Functional operation under these conditions is not implied.

# 4.2 DC Characteristics VDD = 5.0V + 5%, VSS = 0V, TA = $0^{\circ}C$ to $+70^{\circ}C$

| Parameter                                                                                                                                                                                                                   | Symbol     | Min               | Max           | Unit           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------------|---------------|----------------|

| Input High Voltage<br>RDY, IRQB, Data, PHI2,<br>NMIB, ABORTB, BE, RESB                                                                                                                                                      | Vih        | 0.8VDD            | VDD+0.3       | V              |

| Input Low Voltage<br>RDY, IRQB, Data, PHI2,<br>NMIB, ABORTB, BE, RESB                                                                                                                                                       | Vil        | VSS-0.3           | 0.2VDD        | V              |

| Input Leakage Current (Vin=0.4 to 2.4)<br>RDY, (Active Pullup)<br>PHI2<br>Address, Data, RWB, (Off state, BE=0), All other<br>inputs                                                                                        | Iin        | -100<br>-1<br>-10 | 10<br>1<br>10 | μΑ<br>μΑ<br>μΑ |

| Output High Voltage (Ioh=-100FA)<br>Data, Address, RWB, MLB, VPB,<br>MX, E, VDA, VPA                                                                                                                                        | Voh        | 0.7VDD            | -             | V              |

| Output Low Voltage (Iol=1.6mA)<br>Data, Address, RWB, MLB, VPB,<br>MX, E, VDA, VPA                                                                                                                                          | Vol        | -                 | 0.4           | V              |

| Supply Current (no load)                                                                                                                                                                                                    | Idd        |                   | 3             | mA/MH<br>z     |

| Standby Current (No Load, Data Bus = VSS or VDD)<br>RESB, NMIB, IRQB, BE, ABORTB, PHI2=VDD                                                                                                                                  | Isby       | -                 | 5             | μA             |

| Capacitance (Vin=0V, TA=25EC, f=2MHz)<br>PHI2, MX, VDA, RESB, VPB, RDY, ABORTB,<br>IRQB, MLB, NMIB, VPA, E, BE<br>Address, Data, R/W- (Off state)<br>* Not inspected during production test; verified on a<br>sample basis. | Cin<br>Cts | -                 | 10<br>15      | pF<br>pF       |

Table 4-2DC Characteristics

|  | 4.3 | AC Characteristics | VDD = 5.0V + | /- 5%, | VSS = 0V, | $TA = 0^{\circ}C$ to | $+70^{\circ}C$ (1) |

|--|-----|--------------------|--------------|--------|-----------|----------------------|--------------------|

|--|-----|--------------------|--------------|--------|-----------|----------------------|--------------------|

| Parameter                    | Symbol | 14 N | MHz | Unit |

|------------------------------|--------|------|-----|------|

|                              |        | Min  | Max |      |

| Cycle Time                   | tCYC   | 70   | DC  | nS   |

| Clock Pulse Width Low        | tPWL   | 35   | -   | nS   |

| Clock Pulse Width High       | tPWH   | 35   | -   | nS   |

| Fall Time, Rise Time         | tF,tR  | -    | 5   | nS   |

| A0-A15 Hold Time             | tAH    | 10   | -   | nS   |

| A0-A15 Setup Time            | tADS   | -    | 30  | nS   |

| BA0-BA7 Hold Time            | tBH    | 10   | -   | nS   |

| BA0-BA7 Setup Time           | tBAS   | -    | 33  | nS   |

| Access Time                  | tACC   | 30   | -   | nS   |

| Read Data Hold Time          | tDHR   | 10   | -   | nS   |

| Read Data Setup Time         | tDSR   | 10   | -   | nS   |

| Write Data Delay Time        | tMDS   | -    | 30  | nS   |

| Write Data Hold Time         | tDHW   | 10   | -   | nS   |

| Processor Control Setup Time | tPCS   | 10   | -   | nS   |

| Processor Control Hold Time  | tPCH   | 10   | -   | nS   |

| E, MX Output Hold Time       | tEH    | 5    | -   | nS   |

| E, MX Output Setup Time      | tES    | 10   | -   | nS   |

| Capacitive Load (2)          | CEXT   | -    | 35  | pF   |

| BE to Valid Data (3)         | tBVD   | -    | 25  | nS   |

Table 4-3 W65C816S AC Characteristics - 14 MHz

1. Custom testing available covering full, voltage range 1.2-6.0 volts, temperature and timing

2. Applied to Address, Data, RWB

3. BE to High Impedance State is not testable but should be the same amount of time as BE to Valid Data.

W65C816S

Timing Notes:

1. Timing measurement points are 1.5V and 1.5V for VDD = 5V.

Figure 4-1 General Timing Diagram

# **SECTION 5**

# **OPERATION TABLES**

Table 5-1 W65C816S Instruction Set-Alphabetical Sequence (continued on following page)

| ADC | Add Memory to Accumulator with Carry      | INY | Increment Index Y by One                                                      |

|-----|-------------------------------------------|-----|-------------------------------------------------------------------------------|

| AND | "AND" Memory with Accumulator             | JML | Jump Long                                                                     |

| ASL | Shift One Bit Left, Memory or Accumulator | JMP | Jump to New Location                                                          |

| BCC | Branch on Carry Clear (Pc=0)              | JSL | Jump Subroutine Long                                                          |

| BCS | Branch on Carry Set (Pc=1)                | JSR | Jump to News Location Saving Return                                           |

| BEQ | Branch if Equal (Pz=1)                    | LDA | Load Accumulator with Memory                                                  |

| BIT | Bit Test                                  | LDX | Load Index X with Memory                                                      |

| BMI | Branch if Result Minus (Pn=1)             | LDY | Load Index Y with Memory                                                      |

| BNE | Branch if Not Equal (Pz=0)                | LSR | Shift One Bit Right (Memory or Accumulator)                                   |

| BPL | Branch if Result Plus (Pn=0)              | MVN | Block Move Negative                                                           |

| BRA | Branch Always                             | MVP | Block Move Positive                                                           |

| BRK | Force Break                               | NOP | No Operation                                                                  |

| BRL | Branch Always Long                        | ORA | "OR" Memory with Accumulator                                                  |

| BVC | Branch on Overflow Clear (Pv=0)           | PEA | Push Effective Absolute Address on Stack (or Push<br>Immediate Data on Stack) |

| BVS | Branch on Overflow Set (Pv=1)             | PEI | Push Effective Absolute Address on Stack ( Or Push<br>Direct Data on Stack)   |

| CLC | Clear Carry Flag                          | PER | Push Effective Program Counter Relative Address on Stack                      |

| CLD | Clear Decimal Mode                        | PHA | Push Accumulator on Stack                                                     |

| CLI | Clear Interrupt Disable Bit               | PHB | Push Data Bank Register on Stack                                              |

| CLV | Clear Overflow Flag                       | PHD | Push Direct Register on Stack                                                 |

| CMP | Compare Memory and Accumulator            | PHK | Push Program Bank Register on Stack                                           |

| COP | Coprocessor                               | PHP | Push Processor Status on Stack                                                |

| СРХ | Compare Memory and Index X                | PHX | Push Index X on Stack                                                         |

| СРҮ | Compare Memory and Index Y                | PHY | Push Index Y on Stack                                                         |

| DEC | Decrement Memory or Accumulator by One    | PLA | Pull Accumulator from Stack                                                   |

| DEX | Decrement Index X by One                  | PLB | Pull Data Bank Register from Stack                                            |

| DEY | Decrement Index Y by One                  | PLD | Pull Direct Register from Stack                                               |

| EOR | "Exclusive OR" Memory with Accumulator    | PLP | Pull Processor Status from Stack                                              |

| INC | Increment Memory or Accumulator by One    | PLX | Pull Index X from Stack                                                       |

| INX | Increment Index X by One                  | PLY | Pull Index Y from Stack                                                       |

W65C816S

| REP | Reset Status Bits                            | TAY | Transfer Accumulator to Index Y                  |

|-----|----------------------------------------------|-----|--------------------------------------------------|

| ROL | Rotate One Bit Left (Memory or Accumulator)  | TCD | Transfer C Accumulator to Direct Register        |

| ROR | Rotate One Bit Right (Memory or Accumulator) | TCS | Transfer C Accumulator to Stack Pointer Register |

| RTI | Return from Interrupt                        | TDC | Transfer Direct Register to C Accumulator        |

| RTL | Return from Subroutine Long                  | TRB | Test and Reset Bit                               |

| RTS | Return from Subroutine                       | TSB | Test and Set Bit                                 |

| SBC | Subtract Memory from Accumulator with Borrow | TSC | Transfer Stack Pointer Register to C Accumulator |

| SEP | Set Processor Status Bit                     | TSX | Transfer Stack Pointer Register to Index X       |

| SEC | Set Carry Flag                               | TXA | Transfer Index X to Accumulator                  |

| SED | Set Decimal Mode                             | TXS | Transfer Index X to Stack Pointer Register       |

| SEI | Set Interrupt Disable Status                 | TXY | Transfer Index X to Index Y                      |

| STA | Store Accumulator in Memory                  | TYA | Transfer Index Y to Accumulator                  |

| STP | Stop the Clock                               | TYX | Transfer Index Y to Index X                      |

| STX | Store Index X in Memory                      | WAI | Wait for Interrupt                               |

| STY | Store Index Y in Memory                      | WDM | Reserved for future use                          |

| STZ | Store Zero in Memory                         | XBA | Exchange B and A Accumulator                     |

| TAX | Transfer Accumulator in Index X              | XCE | Exchange Carry and Emulation Bits                |

# Table 5-2 Vector Locations

| $\mathbf{E} = 1$ |            |                   | $\mathbf{E} = 0$ |            |          |

|------------------|------------|-------------------|------------------|------------|----------|

| 00FFFE,F-        | IRQB/BRK   | Hardware/Software | 00FFEE,F-        | IRQB       | Hardware |

| 00FFFC,D-        | RESETB     | Hardware          | 00FFEC,D-        | (Reserved) |          |

| 00FFFA,B-        | NMIB       | Hardware          | 00FFEA,B-        | NMIB       | Hardware |

| 00FFF8,9-        | ABORTB     | Hardware          | 00FFE8,9-        | ABORTB     | Hardware |

| 00FFF6,7-        | (Reserved) |                   | 00FFE6,7-        | BRK        | Software |

| 00FFF4,5-        | COP        | Software          | 00FFE4,5-        | COP        | Software |

The VP output is low during the two cycles used for vector location access. When an interrupt is executed, D=0 and I=1 in Status Register P.

| D∾Z |   | 0                      | -                       | 2                          | e                    | 4                                     | a                     | Ŷ                       | 7                        | æ                  | ٥                         | A                | æ                    | U                |                      | ш                              | ш                           |   |

|-----|---|------------------------|-------------------------|----------------------------|----------------------|---------------------------------------|-----------------------|-------------------------|--------------------------|--------------------|---------------------------|------------------|----------------------|------------------|----------------------|--------------------------------|-----------------------------|---|

|     | F | Otadi<br>4 * 5         | ORA al,×<br>4 * 5       | AND di<br>4 * 5            | AND al.x<br>1 * 5    | EOR al<br>4 * 5                       | EOR al × 5<br>4 * 5   | ADC.cl<br>4 * 5         | ADC CIX<br>4 * 5         | STA CI<br>4 * 5    | STA al.x<br>4 * 5         | LDA al<br>4 * 5  | LDA c1,x<br>4 * 5    | CMP al<br>4 * 5  | CMP cl/x<br>4 * 5    | SBC d<br>4 * 5                 | SBC al.x<br>4 * 5           | Ľ |

|     | Э | ASL a<br>3 6           | ASL <b>a</b> . ×<br>3 7 | ROLa<br>3 b                | ROL a.x<br>3 7       | LSR <b>a</b><br>3 <b>6</b>            | LSR a.x<br>3 7        | 3 6 CR C                | ROR ax<br>3 7            | STX a<br>3 4       | STZ a,x<br>3 • 5          | LDX a<br>3 4     | LDX a,v<br>3 4       | DECα<br>3 6      | DEC ax<br>3 7        | 3 б а<br>3 б                   | INC a.x<br>3 7              | ш |

|     | ۵ | ORA a<br>3 4           | ОРА а, х<br>3 4         | AND <b>a</b><br>3 <b>4</b> | AND a.x<br>3 1       | EOR a<br>3 4                          | EOR a.x<br>3 <b>4</b> | ADC a<br>3 4            | ADC a,x<br>3 4           | STAC<br>3 4        | STA c.×<br>3 5            | LDA a<br>3 4     | LDA CIX<br>3 4       | CMP a<br>3 4     | CMP a.x<br>3 4       | sBca<br>3.4                    | SBC CLX<br>3 4              | ٥ |

|     | C | 3•6<br>3               | 3.6<br>3.6              | BII d<br>3 4               | BIT C,X<br>3 • 4     | 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 | JMP al<br>4 * 4       | JMP (a)<br>3 5          | JMP (Q,X;<br>3 • 5       | STV а<br>3 4       | STZ C<br>3 • 4            | 3 <b>4 0</b>     | LDV a.x<br>3 4       | СРУ а<br>3 4     | JML (a)<br>3 * 6     | CPX a<br>3 4                   | JSR ( <b>a</b> .x)<br>3 * 6 | С |

|     | 8 | PHD s<br>1 * 1         | TCS  <br>  * 2          | PLD s<br>1 * 5             | TSC  <br>  * 2       | PHK s<br>1 * 3                        | TCD <br>1 * 2         | RTL s<br>1 * <b>6</b>   | DC <br>1*2               | PHBs<br>1 * 3      | 1XY i<br>1 * 2            | PLB s<br>1 * 4   | TXX<br>1 * 2         | WALI<br>1 • 3    | srp i<br>1 • 3       | X <b>B</b> A <b>I</b><br>1 * 3 | XCE  <br>1 * 2              | 8 |

|     | A | ASLA<br>1 2            | INC A                   | ROLA<br>1 2                | DECA<br>1•2          | LSR A<br>1 2                          | PHY s<br>1•3          | RORA<br>1 2             | PL≺s<br>1•4              | TXAI<br>1 2        | TXS<br>1 2                | IAXI<br>1 2      | TSX<br>1 2           | DEXI<br>1 2      | PHX s<br>1•3         | - 20<br>- 2                    | PLX s<br>1•4                | A |

|     | 6 | 0RA#<br>2_2            | ORA a,y<br>3 4          | AND#                       | AND α.γ<br>3 4       | EOR#<br>2 2                           | EOR a.y<br>3          | ADC #                   | ADC ay<br>3 Z            | BIT#<br>2•2        | STA 0,V<br>3 5            | ⊔DA#<br>2 2 2    | LDA a,y<br>3 z       | CMP#<br>2 2      | CMPa.y<br>3 z        | 8 <b>B</b> C #<br>2 2          | sBC a.v<br>3 <b>z</b>       | ó |

| ß   | œ | PHP S<br>1 3           | CLC                     | PLP s                      | SEC  <br>1 2         | PHA s<br>1 3                          | cui<br>1 2            | PLAs<br>14              | SEI<br>1 2               | DEY I<br>1 2       | 1 2 I                     | IAVI<br>1 2      | CLV  <br>1 2         | 1 2<br>1 2       | CLDI<br>12           | NX -                           | SED  <br>1 2                | œ |

|     | 7 | 0RA [d]<br>2 * 6       | ORA [d],y<br>2 * 6      | AND [d]<br>2 * 6           | AND [d],y<br>2 * 6   | EOR [d]<br>2 * 6                      | EOR [d],y<br>2 * 6    | ADC [d]<br>2 * <b>6</b> | ADC [d],y<br>2 * 6       | SIA [d]<br>2 * 6   | STA [d],y<br>2 * <b>6</b> | LDA [d]<br>2 * 6 | LDA [d],y<br>2 * 6   | CMP [d]<br>2 * 6 | CMP [d'.y<br>2 * 6   | SBC [d]<br>2 * 6               | SBC [d],v<br>2 * 6          | 7 |

|     | 9 | ASL d<br>2 5           | ASI d'x<br>2 6          | ROLd<br>25                 | 2 <b>6</b>           | LSR d<br>2 5                          | LSR dX<br>2 6         | RORd<br>2.5             | ROR d.x<br>2 6           | STX d<br>2 3       | STX dy<br>2 * 4           | DX d             | LDX d.v<br>2 4       | DEC d<br>2 5     | DEC d×<br>2 <b>6</b> | NC d                           | NC d,x<br>2 <b>6</b>        | Ş |

|     | 5 | 0RAd<br>2 3            | ORA dix<br>2 4          | ANDd<br>2 3                | AND dix<br>2 1       | EORd<br>2 3                           | 2 d X                 | ADCd<br>2 3             | ADC dix<br>2 4           | SIAd<br>23         | STA d'x<br>2 <b>4</b>     | 2 3 d            | LDA d,x<br>2 4       | CMPd<br>2 3      | CMP dix<br>2 4       | SBC cl<br>2 3<br>3             | SBC d,x<br>2 4              | £ |

|     | 4 | 75 <b>B d</b><br>2 • 5 | TR <b>B d</b><br>2•5    | BIT d<br>2 3               | BIT d,x<br>2 • 4     | MVP xyc<br>3 * 7                      | MVN xyc<br>3 * 7      | STZ <b>d</b><br>2•3     | 512 <b>c</b> ,x<br>2 • 4 | ۲۷ <b>ط</b><br>2 3 | SIY d,x<br>2 4            | LDV ط<br>2 3     | LDV d.x<br>2 4       | CPY d<br>2 3     | ₽⊞s<br>2 * <b>6</b>  | 2 3 CPX d                      | PEAs<br>3 * 5               | ٢ |

|     | e | ORAd.s<br>2 * 1        | ORA (d,s),y<br>2 * 7    | ANDd.s<br>2 * 4            | AND (d.s),v<br>2 * 7 | EOR d,s<br>2 * <b>4</b>               | EOR (d.s),y<br>2 * 7  | ADC d/s<br>2 * 4        | ADC (d.s).y<br>2 * 7     | STActs<br>2 * 4    | STA (d.s),y<br>2 * 7      | LDA d.s<br>2 * 4 | LDA (d,s),y<br>2 * 7 | CMP d/s<br>2 * 4 | CMP (d,s),y<br>2 * 7 | sBc d,s<br>2 * 4               | SBC (d,s),y<br>2 * 7        | ę |

|     | 2 | 2*7<br>2*7             | ORA (d)<br>2 • 5        | JSL α<br>4 * 8             | AND (d)<br>2 • 5     | 2 * 2                                 | EOR (d)<br>2 • 5      | PERs<br>3 * <b>6</b>    | ADC (d)<br>2 • 5         | BRL ri<br>3 * 3    | STA (d)<br>2 • 5          | 50X#<br>10X#     | LDA (d)<br>2 • 5     | REP#             | CMP (d)<br>2 • 5     | SEP#<br>2 * 3                  | 88C (d)<br>2 • 5            | 2 |

|     | - | 0RA (d.x)<br>2 6       | ORA (d),y<br>2 5        | AND (d.x)<br>2 <b>6</b>    | AND (d),y<br>2 5     | EOR (d,x)<br>2 <b>6</b>               | EOR (d),y<br>2 5      | ADC(d,x)<br>2 <b>6</b>  | ADC (d),y<br>2 5         | SIA (d.x)<br>2 6   | stA (d),y<br>2 <b>6</b>   | LDA (d.x)<br>2 6 | LDA (d),v<br>2 5     | CMP (d.x)<br>2 6 | CMP (d),v<br>2 5     | 8BC [d,X]<br>2 <b>6</b>        | SBC (d),y<br>2 5            | - |

|     | C | BRK s<br>2 7           | BPLr<br>222             | JSR a<br>3 6               | BMIr<br>222          | RT S<br>1 7                           | BVCr<br>2 2           | RTS s<br>1 <b>6</b>     | BVS r<br>2 2             | BRA r<br>2•3       | BCCr<br>2 2               | 2 2 #            | BCSr<br>2 2          | CP₹#<br>CP₹#     | BNE .<br>2 2         | CPX #<br>2 2 2                 | BEQr<br>2 2                 | 0 |

| ≥∞D |   | 0                      | -                       | N                          | e                    | 4                                     | Ð                     | Ŷ                       | 7                        | ω                  | σ                         | A                | ഫ                    | υ                | ۵                    | ш                              | ц                           |   |

MarchpC2000Matrix (continued on following page)

| Symbol | Addressing Mode               | Symbol  | Addressing Mode                 |

|--------|-------------------------------|---------|---------------------------------|

| #      | immediate                     | [d]     | direct indirect long            |

| А      | accumulator                   | [d],y   | direct indirect long<br>indexed |

| r      | program counter relative      | а       | absolute                        |

| rl     | program counter relative long | a,x     | absolute indexed (with x)       |

| Ι      | implied                       | a,y     | absolute indexed (with y)       |

| S      | stack                         | al      | absolute long                   |

| d      | direct                        | al,x    | absolute long indexed           |

| d,x    | direct indexed (with x)       | d,s     | stack relative                  |

| d,y    | direct indexed (with y)       | (d,s),y | stack relative indirect indexed |

| (d)    | direct indirect               | (a)     | absolute indirect               |

| (d,x)  | direct indexed indirect       | (a,x)   | absolute indexed indirect       |

| (d),y  | direct indirect indexed       | хус     | block move                      |

# Op Code Matrix Legend

| INSTRUCTION<br>MNEMONIC |                                                                                                                | ADDRESSING<br>MODE |

|-------------------------|----------------------------------------------------------------------------------------------------------------|--------------------|

|                         | <ul> <li>*= New W65C816S OpCodes</li> <li>• = New W65C02 OpCodes</li> <li>Blank = NMOS 6502 OpCodes</li> </ul> |                    |

| BASE NO. BYTES          |                                                                                                                | BASE NO.<br>CYCLES |

|                                                  | Operation                                                                                                                                                  |            |                |                       |                          |    |                      |          |          |                  |                        |    |                |                  |             | essor<br>Cod | e                  |                       |        |

|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------------|-----------------------|--------------------------|----|----------------------|----------|----------|------------------|------------------------|----|----------------|------------------|-------------|--------------|--------------------|-----------------------|--------|

| ouic                                             |                                                                                                                                                            |            |                |                       |                          |    |                      | >        | ~        |                  |                        |    |                | 7 <b>6</b> 5     | 4           | 3            | 2                  | 1                     | 0      |

| Mnemonic                                         | A AND<br>V OR                                                                                                                                              | *          | σ              | σ                     | σ                        | ۲  | _                    | (d), v   | [d]`<    | (C)              | ğ                      | ά  | х<br>Х         | N V M            | Х           |              |                    |                       | С      |

|                                                  | ⊻ Exclusive OR                                                                                                                                             | 1          | 2              | 3                     | 4                        | 5  | 6                    | 7        | 8        | 9                | 10                     | 11 | 12             | NVI              | В           | D            |                    | Z                     | С      |

| ADC<br>AND<br>ASL<br>BCC<br>BCS                  | $\begin{array}{l} A + M + C \rightarrow A \\ A \wedge M \rightarrow A \\ C \leftarrow 15/7  0 \\ \text{Branch If C=0} \\ \text{Branch If C=1} \end{array}$ | 69<br>29   | 6D<br>2D<br>OE | <b>6F</b><br>2F       | 65<br>25<br>06           | 0A |                      | 71<br>31 | 77<br>37 | <b>6</b> 1<br>21 | 75<br>35<br>1 <b>6</b> |    | 7D<br>3D<br>1E | N V<br>N<br>N    | •           | •            | •                  | Z<br>Z<br>Z           | c<br>c |

| beq<br>Bit<br>Bine<br>Bine<br>Bine               | Branch if Z=1<br>A/M (Note 1)<br>Branch if N=1<br>Branch if Z=0<br>Branch if N=0                                                                           | 89         | 2C             |                       | 24                       |    |                      |          |          |                  | 34                     |    | 3C             | M7 M6            | •           | •            | •                  | Z                     |        |