19-3954; Rev 2; 6/07

#

# **21-Bit Deserializers with Programmable** Spread Spectrum and DC Balance

٠

### **General Description**

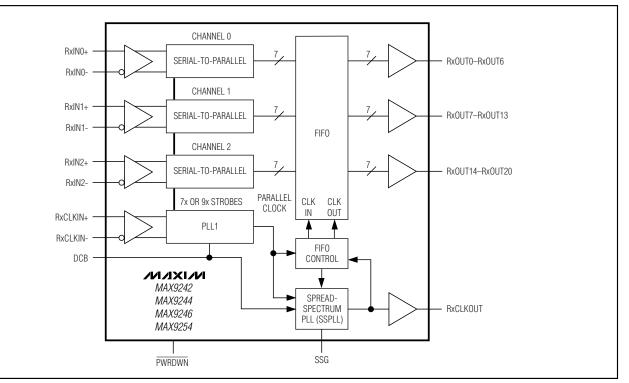

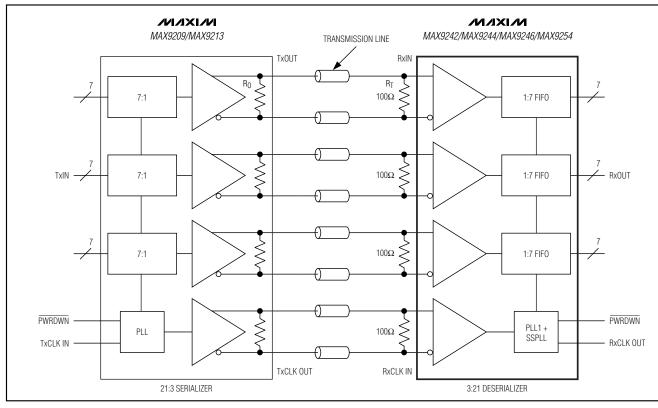

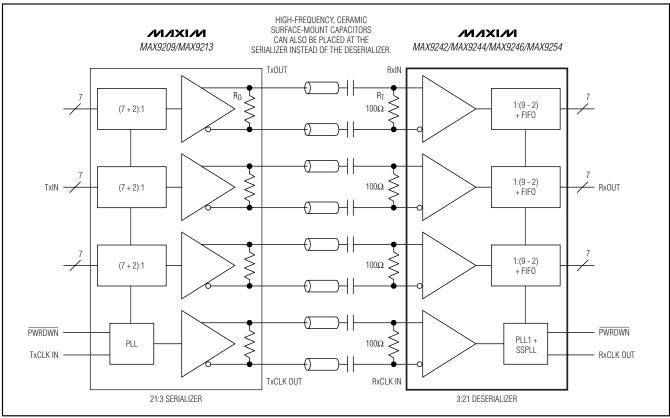

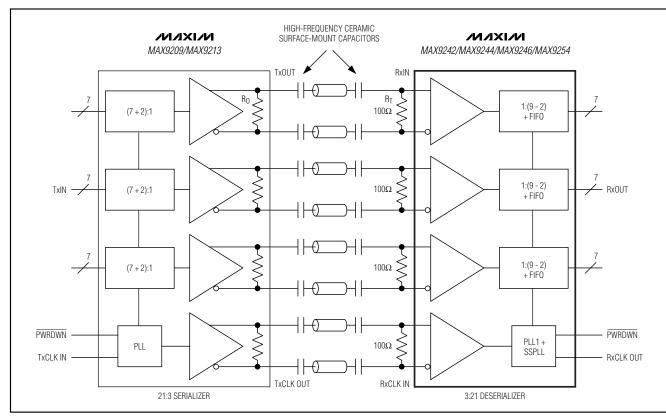

The MAX9242/MAX9244/MAX9246/MAX9254 deserialize three LVDS serial-data inputs into 21 single-ended LVC-MOS/ LVTTL outputs. A separate parallel-rate LVDS clock provides the timing for deserialization. The MAX9242/ MAX9244/MAX9246/MAX9254 feature spread-spectrum capability, allowing the output data and clock frequency to spread over a specified range to reduce EMI. The single-ended data and clock outputs are programmable for a frequency spread of ±2%, ±4%, or no spread. The spread-spectrum function is also available when the MAX9242/MAX9244/MAX9246/MAX9254 operate in non-DC-balanced mode. The modulation rate of the spread is 32kHz for a 33MHz LVDS clock input and scales linearly with frequency. The single-ended outputs have a separate supply, allowing +1.8V to +5V output logic levels.

The MAX9254 features high output drive current for both data and clock outputs for faster transition times in the presence of heavy capacitive loads.

The MAX9242/MAX9244/MAX9246/MAX9254 feature program-mable DC balance, allowing isolation between a serializer and deserializer using AC-coupling. The MAX9242/MAX9244/MAX9246/MAX9254 operate with the MAX9209/MAX9213 serializers and are available with a rising-edge strobe (MAX9242) or falling-edge strobe (MAX9244/MAX9246/MAX9254). The LVDS inputs meet ISO 10605 ESD specifications with ±30kV Air-Gap Discharge and ±6kV Contact Discharge ratings.

Applications

Automotive Navigation Systems Automotive DVD Entertainment Systems **Digital Copiers** Laser Printers

|         |                |                   | FREQUENC                   | CY RANGE               |

|---------|----------------|-------------------|----------------------------|------------------------|

| PART    | STROBE<br>EDGE | OVER-<br>SAMPLING | NON-DC<br>BALANCE<br>(MHz) | DC<br>BALANCE<br>(MHz) |

| MAX9242 | Rising         | Yes               | 20 to 40                   | 16 to 34               |

| MAX9244 | Falling        | Yes               | 20 to 40                   | 16 to 34               |

| MAX9246 | Falling        | No                | 8 to 20                    | 6 to 18                |

| MAX9254 | Falling        | Yes               | 20 to 40                   | 16 to 34               |

### **Selector Guide**

M/X/M Maxim Integrated Products 1

Features Programmable ±4%, ±2%, or OFF Spread-Spectrum Programmable DC-Balanced or Non-DC-Balanced

- Modes DC Balance Allows AC-Coupling for Wider Input Common-Mode Voltage Range

- Spread Spectrum Operates in DC-Balanced or Non-DC-Balanced Mode

- High Output Drive (MAX9254)

Output for Reduced EMI

- $\pi$  / 4 Deskew by Oversampling (MAX9242/MAX9244/MAX9254)

- 16MHz-to-34MHz (DC-Balanced) and 20MHz-to-40MHz (Non-DC-Balanced) Operation (MAX9242/MAX9244/MAX9254)

- ♦ 6MHz-to-18MHz (DC-Balanced) and 8MHz-to-20MHz (Non-DC-Balanced) Operation (MAX9246)

- Rising-Edge (MAX9242) or Falling-Edge (MAX9244/MAX9246/MAX9254) Output Strobe

- ♦ High-Impedance Outputs when PWRDWN is Low Allow Output Busing

- Separate Output Supply Allows Interface to +1.8V, +2.5V, +3.3V, and +5V Logic

- LVDS Inputs Meet ISO 10605 ESD Protection at ±30kV Air-Gap Discharge and ±6kV Contact Discharge

- LVDS Inputs Meet IEC 61000-4-2 Level 4 ESD Protection at ±15kV Air-Gap Discharge and ±8kV Contact Discharge

- LVDS Inputs Conform to ANSI TIA/EIA-644 Standard

- +3.3V Main Power Supply

### **Ordering Information**

| PART       | TEMP RANGE      | PIN-PACKAGE | PKG<br>CODE |

|------------|-----------------|-------------|-------------|

| MAX9242EUM | -40°C to +85°C  | 48 TSSOP    | U48-1       |

| MAX9242GUM | -40°C to +105°C | 48 TSSOP    | U48-1       |

| MAX9244EUM | -40°C to +85°C  | 48 TSSOP    | U48-1       |

| MAX9244GUM | -40°C to +105°C | 48 TSSOP    | U48-1       |

| MAX9246EUM | -40°C to +85°C  | 48 TSSOP    | U48-1       |

| MAX9246GUM | -40°C to +105°C | 48 TSSOP    | U48-1       |

| MAX9254EUM | -40°C to +85°C  | 48 TSSOP    | U48-1       |

Devices are available in lead-free packaging. Specify lead free by adding a + symbol at the end of the part number when orderina.

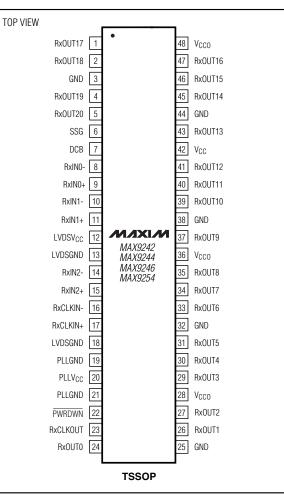

Pin Configuration appears at end of data sheet.

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

### **ABSOLUTE MAXIMUM RATINGS**

(All voltages referenced to GND.)

| () in voltages references to arve.)            |                                   |             |

|------------------------------------------------|-----------------------------------|-------------|

| Vcc, LVDSVcc, PLLVcc                           | 0.5V to +4.0V                     | LVDS Inp    |

| V <sub>CCO</sub>                               | 0.5V to +6.0V                     | LVDS Inp    |

| RxIN_, RxCLKIN                                 | 0.5V to +4.0V                     | ISO 10605   |

| PWRDWN                                         | -0.5V to +6.0V                    | LVDS Inp    |

| SSG, DCB                                       | 0.5V to (V <sub>CC</sub> + 0.5V)  | LVDS Inp    |

| RxOUT_, RxCLKOUT                               | 0.5V to (V <sub>CCO</sub> + 0.5V) | Operating T |

| Continuous Power Dissipation (T <sub>A</sub> = | +70°C)                            | Storage Ter |

| 48-Pin TSSOP (derate 16mW/°C a                 | above +70°C)1282mW                | Junction Te |

| ESD Protection                                 |                                   | Lead Temp   |

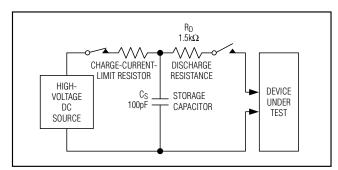

| Human Body Model ( $R_D = 1.5 k\Omega$ , (     | $C_{S} = 100 pF$ )                |             |

| All Pins to GND                                |                                   |             |

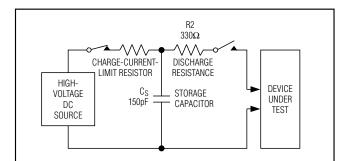

| IEC 61000-4-2 (R <sub>D</sub> = 330Ω, C <sub>S</sub> = 150pF) |               |

|---------------------------------------------------------------|---------------|

| LVDS Inputs to GND (Air-Gap Discharge)                        | ±15kV         |

| LVDS Inputs to GND (Contact Discharge)                        | ±8kV          |

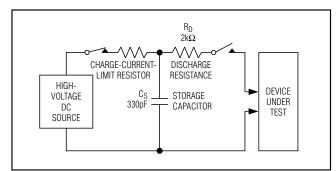

| ISO 10605 (R <sub>D</sub> = 2.0kΩ, C <sub>S</sub> = 330pF)    |               |

| LVDS Inputs to GND (Air-Gap Discharge)                        | ±30kV         |

| LVDS Inputs to GND (Contact Discharge)                        | ±6kV          |

| Operating Temperature Range40                                 | 0°C to +105°C |

| Storage Temperature Range65                                   | 5°C to +150°C |

| Junction Temperature                                          | +150°C        |

| Lead Temperature (soldering, 10s)                             | +300°C        |

|                                                               |               |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### DC ELECTRICAL CHARACTERISTICS

$(V_{CC} = LVDSV_{CC} = PLLV_{CC} = +3.0V$  to +3.6V,  $V_{CCO} = +3.0V$  to +5.5V,  $\overline{PWRDWN} = high$ ; SSG = high, open, or low; DCB = high or low, differential input voltage  $|V_{ID}| = 0.05V$  to 1.2V, input common-mode voltage  $V_{CM} = |V_{ID}| / 2|$  to 2.4V -  $|V_{ID}| / 2|$ , unless otherwise noted. Typical values are at  $V_{CC} = V_{CCO} = LVDSV_{CC} = PLLV_{CC} = +3.3V$ ,  $|V_{ID}| = 0.2V$ ,  $V_{CM} = +1.25V$ ,  $T_A = +25^{\circ}C$ .) (Notes 1, 2)

| PARAMETER                 | SYMBOL                                                           | CONDITIONS                                                                                |                                     |       | MIN | ТҮР | МАХ | UNITS |

|---------------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------|-------|-----|-----|-----|-------|

| POWER SUPPLY              |                                                                  | ·                                                                                         |                                     |       |     |     |     |       |

| Power-Supply Range        | V <sub>CC</sub> ,<br>LVDSV <sub>CC</sub> ,<br>PLLV <sub>CC</sub> |                                                                                           |                                     |       | 3.0 |     | 3.6 | V     |

| Output-Supply Range       | Vcco                                                             |                                                                                           |                                     |       | 1.8 |     | 5.5 | V     |

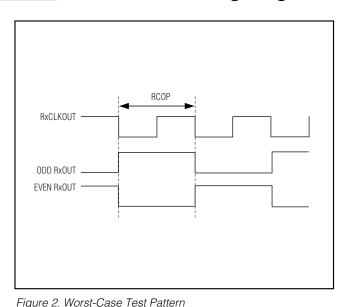

|                           |                                                                  |                                                                                           | DC-balanced                         | 16MHz |     | 45  | 61  |       |

|                           |                                                                  | C <sub>L</sub> = 8pF,<br>worst-case pattern,<br>V <sub>CC</sub> = V <sub>CCO</sub> = 3.0V | mode (SSG = low)                    | 34MHz |     | 72  | 96  |       |

|                           |                                                                  |                                                                                           | Non-DC-balanced<br>mode (SSG = low) | 20MHz |     | 59  | 79  |       |

|                           |                                                                  |                                                                                           |                                     | 33MHz |     | 80  | 106 |       |

| Morat Casa Susaly Current | 1                                                                |                                                                                           |                                     | 40MHz |     | 93  | 123 |       |

| Worst-Case Supply Current | ICCW                                                             | to 3.6V, Figure 2<br>(MAX9242,                                                            | DC-balanced mode                    | 16MHz |     | 57  | 78  | mA    |

|                           |                                                                  | MAX9244,                                                                                  | (SSG = high or open)                | 34MHz |     | 93  | 125 |       |

|                           |                                                                  | MAX9254)                                                                                  | Non-DC-balanced                     | 20MHz |     | 71  | 96  |       |

|                           |                                                                  |                                                                                           | mode                                | 33MHz |     | 98  | 129 |       |

|                           |                                                                  |                                                                                           | (SSG = high or open)                | 40MHz |     | 115 | 145 |       |

### DC ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC} = LVDSV_{CC} = PLLV_{CC} = +3.0V \text{ to } +3.6V, V_{CCO} = +3.0V \text{ to } +5.5V, \overline{PWRDWN} = \text{high}; SSG = \text{high}, \text{open}, \text{ or low}; DCB = \text{high or low}, differential input voltage |V_{ID}| = 0.05V \text{ to } 1.2V, \text{ input common-mode voltage } V_{CM} = |V_{ID}| / 2I \text{ to } 2.4V - |V_{ID}| / 2I, \text{ unless otherwise noted}. Typical values are at V_{CC} = V_{CCO} = LVDSV_{CC} = PLLV_{CC} = +3.3V, |V_{ID}| = 0.2V, V_{CM} = +1.25V, T_A = +25^{\circ}C.) (Notes 1, 2)$

| PARAMETER                 | SYMBOL          | C                                                        | ONDITIONS                           |             | MIN                        | ТҮР | MAX                   | UNITS |

|---------------------------|-----------------|----------------------------------------------------------|-------------------------------------|-------------|----------------------------|-----|-----------------------|-------|

|                           |                 |                                                          |                                     | 6MHz        |                            | 27  | 41                    |       |

|                           |                 |                                                          | DC-balanced                         | 8MHz        |                            | 30  | 45                    |       |

|                           |                 |                                                          | mode (SSG = lov                     | N)<br>18MHz |                            | 43  | 61                    |       |

|                           |                 |                                                          |                                     | 8MHz        |                            | 33  | 47                    |       |

|                           |                 | $C_L = 8pF$ ,                                            | Non-DC-balance<br>mode (SSG = lov   | 100/107     |                            | 37  | 52                    |       |

| Waret Case Supply Current |                 | worst-case pattern,                                      | 1100e (33G = 10)                    | 20MHz       |                            | 52  | 73                    |       |

| Worst-Case Supply Current | ICCW            | $V_{CC} = V_{CCO} = 3.0V$<br>to 3.6V, Figure 2           |                                     | 6MHz        |                            | 32  | 47                    | mA    |

|                           |                 | (MAX9246)                                                | DC-balanced mo<br>(SSG = high or op | 8N/H7       |                            | 38  | 57                    |       |

|                           |                 |                                                          | (SSG = Hightor op                   | 18MHz       |                            | 57  | 81                    |       |

|                           |                 |                                                          | Non-DC-balanced                     | 8MHz        |                            | 41  | 58                    |       |

|                           |                 |                                                          | mode                                | 10MHz       |                            | 46  | 65                    |       |

|                           |                 |                                                          | (SSG = high or op                   | en) 20MHz   |                            | 66  | 92                    |       |

| Power-Down Supply Current | Iccz            | $\overline{PWRDWN} = low$                                |                                     |             |                            |     | 50                    | μA    |

| 5V-TOLERANT LOGIC INPUT   | (PWRDWN)        |                                                          |                                     |             |                            |     |                       |       |

| High-Level Input Voltage  | VIH             |                                                          |                                     |             | 2.0                        |     | 5.5                   | V     |

| Low-Level Input Voltage   | VIL             |                                                          |                                     |             | -0.3                       |     | +0.8                  | V     |

| Input Current             | lin             | $\overline{PWRDWN}$ = high or                            | low level                           |             | -20                        |     | +20                   | μA    |

| Input Clamp Voltage       | V <sub>CL</sub> | I <sub>CL</sub> = -18mA                                  |                                     |             | -1.5                       |     |                       | V     |

| THREE-LEVEL LOGIC INPUTS  | G (DCB, SSG)    |                                                          |                                     |             |                            |     |                       | 1     |

| High-Level Input Voltage  | VIH             |                                                          |                                     |             | 2.5                        |     | V <sub>CC</sub> + 0.3 | V     |

| Mid-Level Input Current   | IIM             | DCB, SSG open or co<br>output in high-impeda             |                                     |             | -10                        |     | +10                   | μA    |

| Low-Level Input Voltage   | VIL             |                                                          |                                     |             | -0.3                       |     | +0.8                  | V     |

| Input Current             | lin             | $\frac{\text{DCB, SSG}}{\text{PWRDWN}} = \text{high or}$ |                                     |             | -20                        |     | +20                   | μA    |

| Input Clamp Voltage       | V <sub>CL</sub> | I <sub>CL</sub> = -18mA                                  |                                     |             | -1.5                       |     |                       | V     |

| SINGLE-ENDED OUTPUTS (R   |                 |                                                          |                                     |             |                            |     |                       |       |

|                           |                 | I <sub>OH</sub> = -100µA                                 |                                     |             | Vcco<br>- 0.1              |     |                       |       |

|                           |                 |                                                          | RxCLKOUT (N                         | lote 4)     | V <sub>CCO</sub><br>- 0.25 |     |                       |       |

| High-Level Output Voltage | VOH             | I <sub>OH</sub> = -2mA                                   |                                     |             | V <sub>CCO</sub><br>- 0.43 |     |                       | V     |

|                           |                 |                                                          | RxOUT                               | MAX9254     | V <sub>CCO</sub><br>- 0.25 |     |                       |       |

|                           |                 | $I_{OL} = 100 \mu A$                                     | I <sub>OL</sub> = 100μA             |             |                            |     | 0.1                   |       |

| Low-Level Output Voltage  | Vol             | $I_{OL} = 2mA$                                           | RxCLKOUT (Note 4)                   |             |                            |     | 0.2                   | v     |

|                           | *UL             |                                                          | RxOUT_                              |             |                            |     | 0.26                  | 26    |

|                           |                 |                                                          |                                     | MAX9254     |                            |     | 0.2                   |       |

### DC ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC} = LVDSV_{CC} = PLLV_{CC} = +3.0V \text{ to } +3.6V, V_{CCO} = +3.0V \text{ to } +5.5V, \overline{PWRDWN} = \text{high}; SSG = \text{high}, \text{open}, \text{ or low}; DCB = \text{high or low}, differential input voltage |V_{ID}| = 0.05V \text{ to } 1.2V, \text{ input common-mode voltage } V_{CM} = |V_{ID} / 2| \text{ to } 2.4V - |V_{ID} / 2|, \text{ unless otherwise noted}. Typical values are at V_{CC} = V_{CCO} = LVDSV_{CC} = PLLV_{CC} = +3.3V, |V_{ID}| = 0.2V, V_{CM} = +1.25V, T_A = +25^{\circ}C.) (Notes 1, 2)$

| PARAMETER                         | SYMBOL                                | CONDITIC                                                     | ONS                             | MIN | ТҮР | MAX        | UNITS |  |

|-----------------------------------|---------------------------------------|--------------------------------------------------------------|---------------------------------|-----|-----|------------|-------|--|

| High-Impedance Output Current     | Ioz                                   | $\overline{\text{PWRDWN}}$ = low, V <sub>OUT</sub> = -0.3    | 3V to (V <sub>CCO</sub> + 0.3V) | -30 |     | +30        | μA    |  |

|                                   |                                       | $V_{CCO} = 3.0V \text{ to } 3.6V,$                           | RxCLKOUT (Note 4)               | -10 |     | -40        |       |  |

| Output Short-Circuit Current      | los                                   | V <sub>OUT</sub> = 0V                                        | RxOUT_                          | -5  |     | -20        | mA    |  |

| (Note 5)                          | 105                                   | VCCO = 4.5V to 5.5V,                                         | RxCLKOUT (Note 4)               | -28 |     | -75        | IIIA  |  |

|                                   |                                       | VOUT = 0V                                                    | RxOUT_                          | -13 |     | -37        |       |  |

|                                   |                                       | V <sub>CCO</sub> = 3.0V to 3.6V,                             | RxOUT_                          | -16 |     | <b>F</b> 1 |       |  |

| Output Short-Circuit Current      | loo                                   | $V_{OUT} = 0V$                                               | RxCLKOUT (Note 4)               | -10 | -51 | -51        | mA    |  |

| (MAX9254) (Note 5)                | los                                   | VCCO = 4.5V  to  5.5V,                                       | RxOUT_                          | -34 | -93 |            |       |  |

|                                   |                                       | VOUT = 0V                                                    | RxCLKOUT (Note 4)               | -34 |     | -93        |       |  |

| LVDS INPUTS (RxIN_, RxCLKIN       | _)                                    |                                                              |                                 |     |     |            |       |  |

| Differential Input High Threshold | V <sub>TH</sub>                       | (Note 6)                                                     |                                 |     |     | 50         | mV    |  |

| Differential Input Low Threshold  | VTL                                   | (Note 6)                                                     |                                 | -50 |     |            | mV    |  |

| Input Current                     | I <sub>IN+</sub> , I <sub>IN-</sub>   | $\overline{PWRDWN}$ = high or low                            |                                 | -25 |     | +25        | μA    |  |

| Power-Off Input Current           | I <sub>INO+</sub> , I <sub>INO-</sub> | V <sub>CC</sub> = V <sub>CCO</sub> = 0V or open              |                                 | -40 |     | +40        | μA    |  |

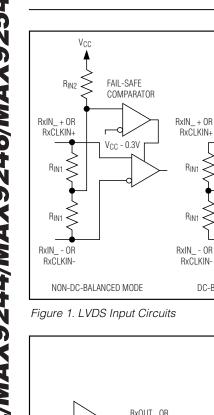

| Input Decistor 1                  | Duri                                  | $\overrightarrow{PWRDWN}$ = high or low,                     | -40°C to +85°C                  | 42  |     | 78         | kO    |  |

| Input Resistor 1                  | R <sub>IN1</sub>                      | V <sub>CC</sub> = V <sub>CCO</sub> = 0V or open,<br>Figure 1 | -40°C to +105°C                 | 42  |     | 85         | kΩ    |  |

| Input Decistor 0                  | Dute                                  | $\overline{PWRDWN}$ = high or low,                           | -40°C to +85°C                  | 246 | 410 |            | ko    |  |

| Input Resistor 2                  | R <sub>IN2</sub>                      | V <sub>CC</sub> = V <sub>CCO</sub> = 0V or open,<br>Figure 1 | -40°C to +105°C                 | 246 |     | 440        | kΩ    |  |

### AC ELECTRICAL CHARACTERISTICS

$(V_{CC} = LVDSV_{CC} = PLLV_{CC} = +3.0V \text{ to } +3.6V, V_{CCO} = +3.0V \text{ to } +3.6V, C_L = 8pF, \overline{PWRDWN} = \text{high}; SSG = \text{high}, \text{ open}, \text{ or low}; DCB = \text{high or low}, differential input voltage |V_{ID}| = 0.1V \text{ to } 1.2V, \text{ input common-mode voltage } V_{CM} = |V_{ID}| / 2| \text{ to } 2.4V - |V_{ID}| / 2|, \text{ unless otherwise noted}. Typical values are at V_{CC} = V_{CCO} = LVDSV_{CC} = PLLV_{CC} = +3.3V, |V_{ID}| = 0.2V, V_{CM} = +1.25V, T_A = +25^{\circ}C.) (Notes 6, 7, 8)$

| PARAMETER                  | SYMBOL | CONDITION                                                   | IS       | MIN  | ТҮР  | MAX  | UNITS |

|----------------------------|--------|-------------------------------------------------------------|----------|------|------|------|-------|

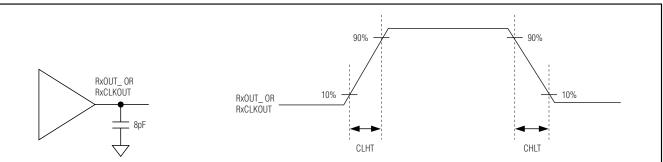

| Output Diss Time           | OLUT   | 0.1 x VCCO to 0.9 x VCCO,                                   | RxOUT_   | 2.9  | 4.7  | 6.5  |       |

| Output Rise Time           | CLHT   | Figure 3                                                    | RxCLKOUT | 2.0  | 3.3  | 4.1  | ns    |

| Output Fall Time           | CHLT   | 0.9 x VCCO to 0.1 x VCCO,                                   | RxOUT_   | 2.1  | 3.0  | 4.2  |       |

| Output Fall Time           | CHLI   | Figure 3                                                    | RxCLKOUT | 1.10 | 1.94 | 2.70 | ns    |

| Output Rise Time (MAX9254) | CLHT   | 0.1 x V <sub>CCO</sub> to 0.9 x V <sub>CCO</sub> , Figure 3 | RxOUT_   | 1.4  | 2.2  | 3.3  | ns    |

| Output Fall Time (MAX9254) | CHLT   | 0.9 x V <sub>CCO</sub> to 0.1 x V <sub>CCO</sub> , Figure 3 | RxCLKOUT | 1.1  | 1.8  | 2.8  | ns    |

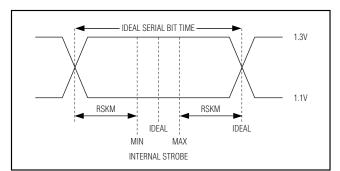

|                            |        | DC-balanced mode,                                           | 16MHz    | 2560 | 3142 |      |       |

| RxIN Skew Margin (Note 9)  | RSKM   | Figure 4                                                    | 34MHz    | 900  | 1386 |      |       |

|                            | NOVIN  | Non-DC-balanced mode,                                       | 20MHz    | 2500 | 3164 |      | ps    |

|                            |        | Figure 4                                                    | 40MHz    | 960  | 1371 |      |       |

M/IXI/M

### AC ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC} = LVDSV_{CC} = PLLV_{CC} = +3.0V$  to +3.6V,  $V_{CCO} = +3.0V$  to +3.6V,  $C_L = 8pF$ ,  $\overline{PWRDWN} = high$ ; SSG = high, open, or low; DCB = high or low, differential input voltage  $|V_{ID}| = 0.1V$  to 1.2V, input common-mode voltage  $V_{CM} = |V_{ID}| / 2I$  to  $2.4V - |V_{ID}| / 2I$ , unless otherwise noted. Typical values are at  $V_{CC} = V_{CCO} = LVDSV_{CC} = PLLV_{CC} = +3.3V$ ,  $|V_{ID}| = 0.2V$ ,  $V_{CM} = +1.25V$ ,  $T_A = +25^{\circ}C$ .) (Notes 6, 7, 8)

| PARAMETER                                              | SYMBOL    | CONDITI                   | ONS                         | MIN                            | ΤΥΡ                            | MAX                            | UNITS                          |                                |                                |  |

|--------------------------------------------------------|-----------|---------------------------|-----------------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|--|

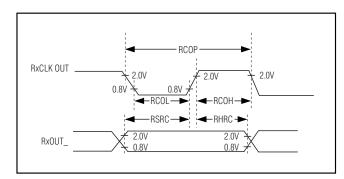

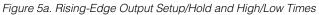

| RxCLKOUT High Time                                     | RCOH      | Figures 5a, 5b            |                             | 0.35 x<br>RCOP                 |                                |                                | ns                             |                                |                                |  |

| RxCLKOUT Low Time                                      | RCOL      | Figures 5a, 5b            |                             | 0.35 x<br>RCOP                 |                                |                                | ns                             |                                |                                |  |

| RxOUT Setup to RxCLKOUT                                | RSRC      | Figures 5a, 5b            |                             | 0.3 x<br>RCOP                  |                                |                                | ns                             |                                |                                |  |

| RxOUT Hold from RxCLKOUT                               | RHRC      | Figures 5a, 5b            |                             | 0.45 x<br>RCOP                 |                                |                                | ns                             |                                |                                |  |

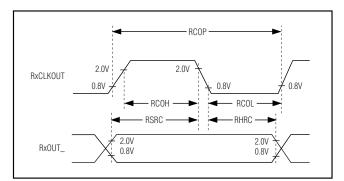

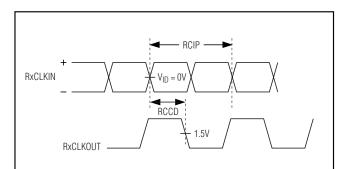

| RxCLKIN to RxCLKOUT Delay                              | RCCD      | SSG = low, Figures 6a, 6b |                             | 4.5 +<br>(RCIP / 2)            | 6.5 +<br>(RCIP / 2)            | 8.2 +<br>(RCIP / 2)            | ns                             |                                |                                |  |

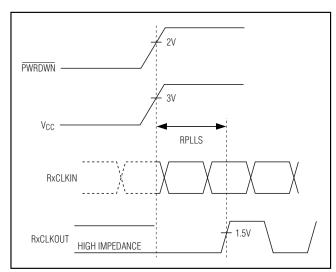

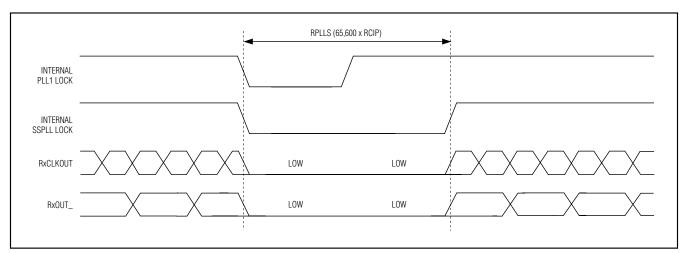

| Deserializer Phase-Locked-<br>Loop Set                 | RPLLS     | Figure 7                  |                             |                                |                                | 65,600 x<br>RCIP               | ns                             |                                |                                |  |

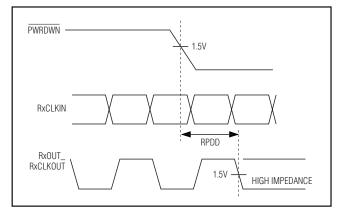

| Deserializer Power-Down Delay                          | RPDD      | Figure 8                  |                             |                                |                                | 100                            | ns                             |                                |                                |  |

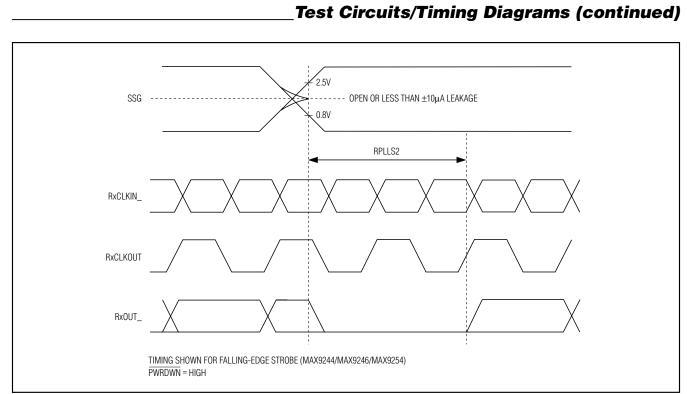

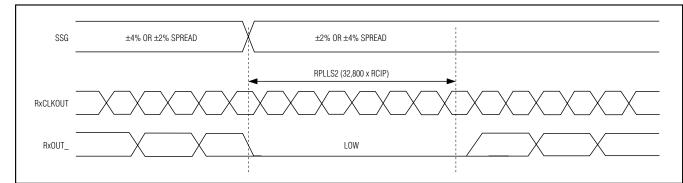

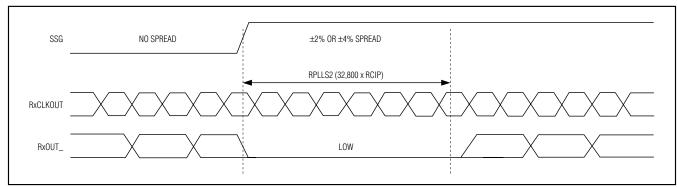

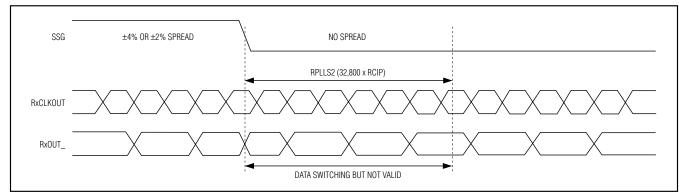

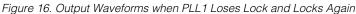

| Deserializer Phase-Locked-<br>Loop Set from SSG Change | RPLLS2    | Figure 9                  | Figure 9                    |                                |                                | 32,800 x<br>RCIP               | ns                             |                                |                                |  |

|                                                        |           | SSG = high,               | Maximum output<br>frequency | f <sub>RxCLKIN</sub><br>+ 3.6% | f <sub>RxCLKIN</sub><br>+ 4.0% | f <sub>RxCLKIN</sub><br>+ 4.4% |                                |                                |                                |  |

|                                                        |           |                           |                             |                                | Figure 10                      | Minimum output<br>frequency    | f <sub>RxCLKIN</sub><br>- 4.4% | f <sub>RxCLKIN</sub><br>- 4.0% | f <sub>RxCLKIN</sub><br>- 3.6% |  |

| Spread-Spectrum Output<br>Frequency                    | frxCLKOUT | SSG = open,               | Maximum output<br>frequency | f <sub>RxCLKIN</sub><br>+ 1.8% | f <sub>RxCLKIN</sub><br>+ 2.0% | f <sub>RxCLKIN</sub><br>+ 2.2% | MHz                            |                                |                                |  |

|                                                        |           | Figure 10                 | Minimum output<br>frequency | frxCLKIN<br>- 2.2%             | <sup>f</sup> RxCLKIN<br>- 2.0% | <sup>f</sup> RxCLKIN<br>- 1.8% |                                |                                |                                |  |

|                                                        | SSG = low |                           |                             | <b>f</b> RxCLKIN               |                                | <b>f</b> RxCLKIN               |                                |                                |                                |  |

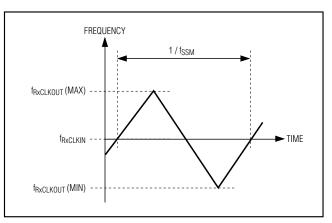

| Spread-Spectrum Modulation<br>Frequency                | fssm      | Figure 10                 |                             |                                | f <sub>RxCLKIN</sub> /<br>1016 |                                | Hz                             |                                |                                |  |

Note 1: Current into a pin is defined as positive. Current out of a pin is defined as negative. All voltages are referenced to ground, except V<sub>TH</sub> and V<sub>TL</sub>.

Note 2: Maximum and minimum limits over temperature are guaranteed by design and characterization. Devices are production tested at  $T_A = +25$  °C.

Note 3: To provide a mid level, leave the input open, or, if driven, put driver in high impedance. High-impedance leakage current must be less than ±10μA.

Note 4: RxCLKOUT limits are scaled based on RxOUT\_ measurements, design, and characterization data.

Note 5: One output shorted at a time. Current out of the pin.

- Note 6: V<sub>TH</sub>, V<sub>TL</sub>, and AC parameters are guaranteed by design and characterization, and are not production tested. Limits are set at ±6 sigma.

- **Note 7:** C<sub>L</sub> includes probe and test jig capacitance.

- Note 8: RCIP is the period of RxCLKIN. RCOP is the period of RxCLKOUT.

Note 9: RSKM is measured with less than 150ps cycle-to-cycle jitter on RxCLKIN.

21

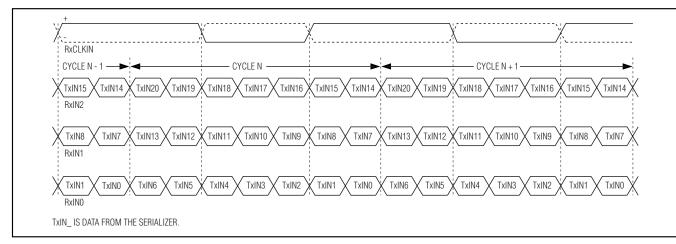

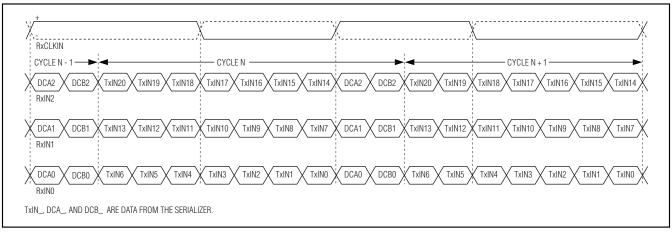

DC-BALANCED MODE

### Test Circuits/Timing Diagrams

Figure 3. Output Load and Transition Times

Figure 4. LVDS Receiver Input Skew Margin

Figure 5b. Falling-Edge Output Setup/Hold and High/Low Times

Figure 6b. Clock-IN to Clock-OUT Delay (MAX9242)

Figure 8. Power-Down Delay

### Test Circuits/Timing Diagrams (continued)

Figure 6a. Clock-IN to Clock-OUT Delay (MAX9244/MAX9246/ MAX9254)

Figure 7. Phase-Locked-Loop Set Time

Figure 9. Phase-Locked-Loop Set Time from SSG Change

Figure 10. Simplified Modulation Profile

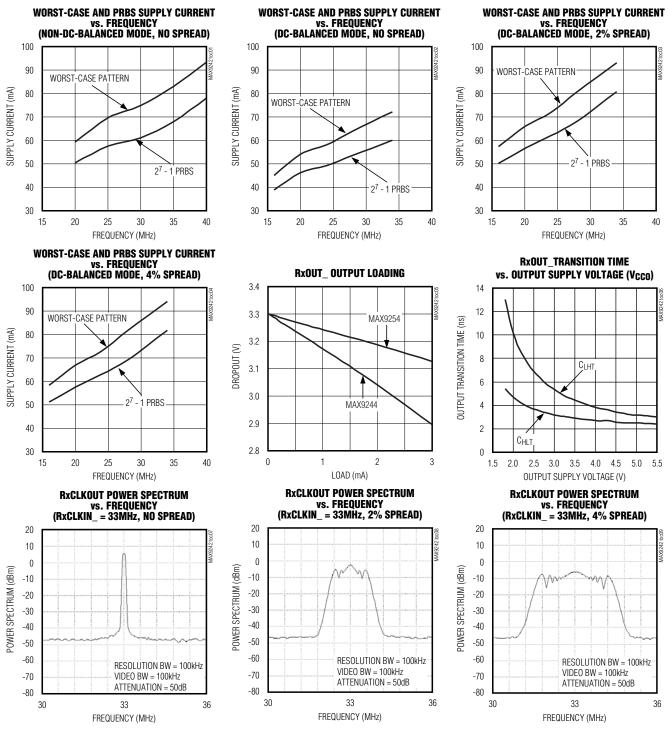

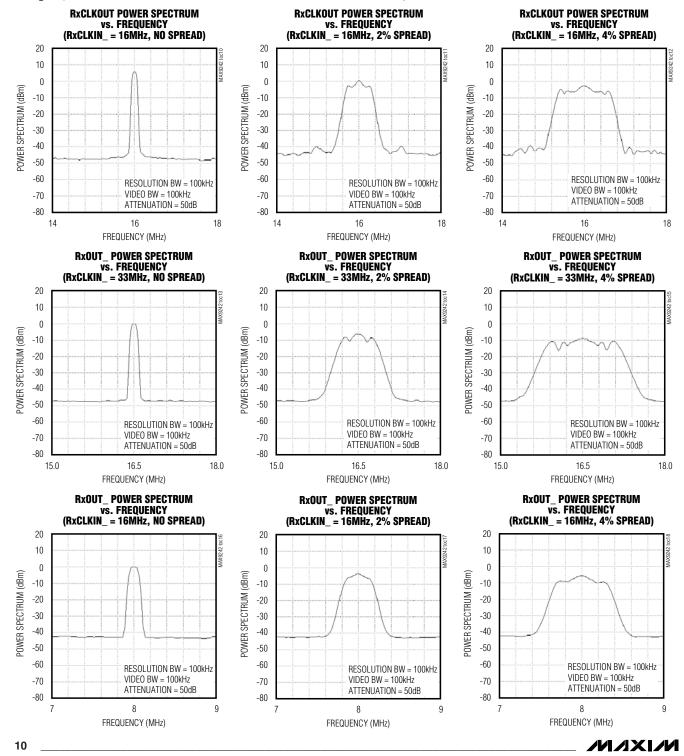

**Typical Operating Characteristics**

$(V_{CC} = PLLV_{CC} = LVDSV_{CC} = V_{CCO} = +3.3V, C_L = 8pF, \overline{PWRDWN} = high, differential input voltage |V_{ID}| = 0.2V, input common-mode voltage V_{CM} = 1.2V, T_A = +25°C, MAX9244/MAX9254, unless otherwise noted.)$

$(V_{CC} = PLLV_{CC} = LVDSV_{CC} = V_{CCO} = +3.3V, C_L = 8pF, \overline{PWRDWN} = high, differential input voltage |V_{ID}| = 0.2V, input common-mode voltage V_{CM} = 1.2V, T_A = +25°C, MAX9244/MAX9254, unless otherwise noted.)$

### \_Pin Description

| PIN     NAME     FUNCTION       1     Rx0U117     Channel 2 Single-Ended Outputs     Rx0U118       3, 25, 32, 38, 44     GND     Ground     Ground       4     Rx0U170     Channel 2 Single-Ended Outputs     Channel 2 Single-Ended Outputs       5     Rx0U170     Channel 2 Single-Ended Outputs     Channel 2 Single-Ended Outputs       6     SSG     Three-Level-Logic, Spread-Spectrum Generator Control Input. SSG selects the frequency spread of RxCLKOUT relative to RxCLKIN (see Table 3).       7     DCB     Three-Level-Logic, DC-Balance Control Input. DCB selects DC-balanced, non-DC-balanced, or reserved operation (see Table 1).       8     RxIN0-     Inverting Channel 0 LVDS Serial-Data Input       10     RxIN1-     Inverting Channel 1 LVDS Serial-Data Input       11     RxIN2-     Inverting Channel 2 LVDS Serial-Data Input       12     LVDSGND     LVDS Ground       14     RXIN2-     Inverting Channel 2 LVDS Serial-Data Input       15     RXIN2+     Inverting Channel 2 LVDS Serial-Data Input       16     RxCLKIN+     Inverting Channel 2 LVDS Serial-Data Input       17     RxCLKIN+     Inverting Channel 2 LVDS Serial-Data Input <t< th=""><th></th><th></th><th>Pin Description</th></t<>                                                                                                                        |            |                     | Pin Description                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------------|-----------------------------------------------|

| 2     RxOUT18     Channel 2 Single-Ended Outputs       3.25, 32,<br>38, 44     GND     Ground       4     RxOUT19     Channel 2 Single-Ended Outputs       5     RxOUT20     Channel 2 Single-Ended Outputs       6     SSG     Three-Level-Logic, Spread-Spectrum Generator Control Input. SSG selects the frequency spread of<br>RxCLKOUT relative to RxCLKIN (see Table 3).       7     DCB     Three-Level-Logic, DC-Balance Control Input. DCB selects DC-balanced, non-DC-balanced, or reserved<br>operation (see Table 1).       8     RxINO-     Norwering Channel 0 LVDS Serial-Data Input       9     RxINO-     Norwering Channel 1 LVDS Serial-Data Input       10     RxIN1-     Inverting Channel 1 LVDS Serial-Data Input       11     RxIN1+     Noninverting Channel 1 LVDS Serial-Data Input       12     LVDSGND     LVDS Ground       14     RXIN2+     Noninverting Channel 2 LVDS Serial-Data Input       15     RxIN2+     Noninverting Channel 2 LVDS Serial-Data Input       16     RxCLKIN+     Inverting Channel 2 LVDS Serial-Data Input       17     RxCLKIN+     Inverting Channel 2 LVDS Serial-Data Input       18     RxIN2+     Noninverting Channel 2 LVDS Serial-Data Inpu                                                                                                                                                       | PIN        | NAME                | FUNCTION                                      |

| 2   FX00118   FX0118     3, 25, 32, 38, 44   GND   Ground     4   FX0UT20   Channel 2 Single-Ended Outputs     5   FX0UT20   Three-Level-Logic, Spread-Spectrum Generator Control Input. SSG selects the frequency spread of RxCLKOUT relative to RxCLKIN (see Table 3).     7   DCB   Operation (see Table 1).     8   RxIN0-   Inverting Channel 0 LVDS Serial-Data Input     9   RxINN+   Noninverting Channel 0 LVDS Serial-Data Input     10   RxIN1+   Inverting Channel 1 LVDS Serial-Data Input     11   RxIN1+   Noninverting Channel 1 LVDS Serial-Data Input     12   LVDSVcc   LVDS Supply Voltage. Bypass LVDSVcc to GND with 0.1µF and 0.001µF capacitors in parallel as close to the pin as possible.     13, 18   LVDSSGND   LVDS Serial-Data Input     14   RxIN2+   Inverting Channel 2 LVDS Serial-Data Input     16   RxCLKINI-   Inverting LVDS Parallel-Rate Clock Input     17   RxCLKIN-   Noninverting LVDS Parallel-Rate Clock Input     19, 21   PLLGND   PLL Ground     22   PWRDWN   SV-Tolerant LVTTL/LVCMOS Power-Down Input. PWRDWN is internally pulled down to GND. Outputs are high impedance when PWRDWN = low or open. <td< td=""><td>1</td><td>RxOUT17</td><td>Channel 2 Single Ended Outputs</td></td<>                                                                                                                       | 1          | RxOUT17             | Channel 2 Single Ended Outputs                |

| 38, 44   Ground   Ground     4   RxOUT19   Channel 2 Single-Ended Outputs     5   RxOUT20   Three-Level-Logic, Spread-Spectrum Generator Control Input. SSG selects the frequency spread of RxCLKOUT relative to RxCLKIN (see Table 3).     7   DCB   Three-Level-Logic, DC-Balance Control Input. DCB selects DC-balanced, non-DC-balanced, or reserved operation (see Table 1).     8   RxIN0-   Inverting Channel 0 LVDS Serial-Data Input     9   RxIN1-   Inverting Channel 1 LVDS Serial-Data Input     10   RxIN1+   Noninverting Channel 1 LVDS Serial-Data Input     11   RxIN1+   Noninverting Channel 1 LVDS Serial-Data Input     12   LVDS Supply Voltage. Bypass LVDSVcc to GND with 0.1µF and 0.001µF capacitors in parallel as close to the pin as possible.     13.18   LVDSGND   LVDS Serial-Data Input     16   RxIN2+   Inverting Channel 2 LVDS Serial-Data Input     16   RxIN2+   Inverting Channel 2 LVDS Serial-Data Input     17   RxCLKIN+   Noninverting Channel 2 LVDS Serial-Data Input     16   RxIN2+   Inverting Channel 2 LVDS Serial-Data Input     17   RxCLKIN+   Noninverting Channel 2 LVDS Serial-Data Input     18   RvIN2+   Inverting Channel 2 LVDS Serial-Dat                                                                                                                                                           | 2          | RxOUT18             |                                               |

| 5     RXOUT20     Channel 2 Single-Ended Outputs       6     SSG     Three-Level-Level-Logic, Spread-Spectrum Generator Control Input. SSG selects the frequency spread of RxCLKOUT relative to RxCLKIN (see Table 3).       7     DCB     Three-Level-Logic, DC-Balance Control Input. DCB selects DC-balanced, non-DC-balanced, or reserved operation (see Table 1).       8     RxIN0-     Inverting Channel 0 LVDS Serial-Data Input       9     RxIN1+     Noninverting Channel 1 LVDS Serial-Data Input       10     RxIN1+     Noninverting Channel 1 LVDS Serial-Data Input       11     RxIN1+     Noninverting Channel 1 LVDS Serial-Data Input       12     LVDSVcc     LVDS Supply Voltage. Bypass LVDSVcc to GND with 0.1µF and 0.001µF capacitors in parallel as close to the pin as possible.       13, 18     LVDSGND     LVDS Foralle-Rate Clock Input       14     RxIN2+     Noninverting Channel 2 LVDS Serial-Data Input       15     RxIN2+     Noninverting LDS Parallel-Rate Clock Input       16     RxCLKIN+     Inverting LDS Parallel-Rate Clock Input       17     RxCLKIN+     Noninverting LVDS Parallel-Rate Clock Input       19, 21     PLLGND     PLL Ground       20     PLLGND     PLL Ground                                                                                                                                   |            | GND                 | Ground                                        |

| 5   RX0U120   Preschere     6   SSG   Three-Level-Logic, Spread-Spectrum Generator Control Input. SSG selects the frequency spread of RxCLKOUT relative to RxCLKIN (see Table 3).     7   DCB   Three-Level-Logic, DC-Balance Control Input. DCB selects DC-balanced, non-DC-balanced, or reserved operation (see Table 1).     8   RxIN0-   Inverting Channel 0 LVDS Serial-Data Input     9   RXIN0+   Noninverting Channel 1 LVDS Serial-Data Input     10   RxIN1+   Noninverting Channel 1 LVDS Serial-Data Input     11   RxIN0+   Noninverting Channel 1 LVDS Serial-Data Input     12   LVDSVcc   LVDS Supply Voltage. Bypass LVDSVcc to GND with 0.1µF and 0.001µF capacitors in parallel as close to the pin as possible.     13, 18   LVDSGND   LVDS Serial-Data Input     14   RxIN2+   Noninverting Channel 2 LVDS Serial-Data Input     16   RxCLKIN+   Inverting Channel 2 LVDS Serial-Data Input     16   RxCLKIN+   Noninverting Channel 2 LVDS Serial-Data Input     17   RxCLKIN+   Inverting LVDS Parallel-Rate Clock Input     19, 21   PLLGND   PLL Ground     20   PLLVcc   PLL Supply Voltage. Bypass PLLVcc to GND with 0.1µF and 0.001µF capacitors in parallel as close to the pin as possible.                                                                                                                                           | 4          | RxOUT19             | Channel 2 Single Ended Outputs                |

| b     SSG     RxCLKOUT relative to RxCLKIN (see Table 3).       7     DCB     Three-Level-Logic, DC-Balance Control Input. DCB selects DC-balanced, non-DC-balanced, or reserved operation (see Table 1).       8     RxIN0-     Inverting Channel 0 LVDS Serial-Data Input       10     RxIN1-     Inverting Channel 0 LVDS Serial-Data Input       11     RxIN1+     Noninverting Channel 1 LVDS Serial-Data Input       12     LVDSVcc     LVDS Supply Voltage. Bypass LVDSVcc to GND with 0.1µF and 0.001µF capacitors in parallel as close to the pin as possible.       13, 18     LVDSGND     LVDS Ground       14     RxIN2+     Inverting Channel 2 LVDS Serial-Data Input       15     RxIN2+     Noninverting Channel 2 LVDS Serial-Data Input       16     RxCLKIN-     Inverting Channel 2 LVDS Serial-Data Input       17     RxCLKIN-     Noninverting LVDS Parallel-Rate Clock Input       19, 21     PLLGND     PLL Ground       20     PLLVcc     PLL Supply Voltage. Bypass PLLVcc to GND with 0.1µF and 0.001µF capacitors in parallel as close to the pin as possible.       21     PLBOND     PLL Ground     PUL Ground       22     PWRDWN     Single-Ended Output. The MAX9242 has a rising-edge strobe. The MAX9244/MAX                                                                                                                     | 5          | RxOUT20             | Channel 2 Single-Ended Outputs                |

| 7   DDB   operation (see Table 1).     8   RxIN0-   Inverting Channel 0 LVDS Serial-Data Input     9   RxIN0+   Noninverting Channel 0 LVDS Serial-Data Input     10   RxIN1+   Inverting Channel 1 LVDS Serial-Data Input     11   RxIN1+   Noninverting Channel 1 LVDS Serial-Data Input     12   LVDSVcc   LVDS Ground 1 LVDS Serial-Data Input     13.18   LVDSGND   LVDS Ground 2     14   RxIN2-   Inverting Channel 2 LVDS Serial-Data Input     15   RxIN2-   Inverting Channel 2 LVDS Serial-Data Input     16   RxCLKIN-   Inverting Channel 2 LVDS Serial-Data Input     17   RxCLKIN+   Noninverting Channel 2 LVDS Serial-Data Input     18   LVDS Monitor Channel 2 LVDS Serial-Data Input   Inverting Channel 2 LVDS Serial-Data Input     17   RxCLKIN+   Noninverting LVDS Parallel-Rate Clock Input   Inverting Channel 2 LVDS Serial-Data Input     19, 21   PLLGND   PLL Ground   PLL Ground     20   PLLVcc   PLL Ground   PLWC     21   PWRDWN   SV-Tolerant LVTTL/LVCMOS Power-Down Input. PWRDWN is internally pulled down to GND. Outputs are high impedance when PWRDWN = low or open.     23<                                                                                                                                                                                                                                             | 6          | SSG                 |                                               |

| 9   RxIN0+   Noninverting Channel 0 LVDS Serial-Data Input     10   RxIN1-   Inverting Channel 1 LVDS Serial-Data Input     11   RxIN1+   Noninverting Channel 1 LVDS Serial-Data Input     12   LVDSVcc   LVDS Supply Voltage. Bypass LVDSVcc to GND with 0.1µF and 0.001µF capacitors in parallel as close to the pin as possible.     13, 18   LVDSGND   LVDS Ground     14   RxIN2-   Inverting Channel 2 LVDS Serial-Data Input     15   RxIN2+   Noninverting Channel 2 LVDS Serial-Data Input     16   RxCLKIN-   Inverting Channel 2 LVDS Serial-Data Input     17   RxCLKIN+   Noninverting Channel 2 LVDS Parallel-Rate Clock Input     19, 21   PLLGND   PLL Ground     20   PLLVcc   PLL Supply Voltage. Bypass PLLV <sub>CC</sub> to GND with 0.1µF and 0.001µF capacitors in parallel as close to the pin as possible.     21   PWRDWN   SV-Tolerant LVTTL/LVCMOS Power-Down Input. PWRDWN is internally pulled down to GND. Outputs are high impedance when PWRDWN = low or open.     23   RxCLKOUT   Parallel-Rate Clock Single-Ended Output. The MAX9242 has a rising-edge strobe. The MAX9244/MAX9246/<br>MAX9254 have a falling-edge strobe.     24   RxOUT0   Channel 0 Single-Ended Outputs     27   RxOUT2   Output Supply Voltage. Bypass e                                                                                                   | 7          | DCB                 |                                               |

| 10   RxIN1-   Inverting Channel 1 LVDS Serial-Data Input     11   RxIN1+   Noninverting Channel 1 LVDS Serial-Data Input     12   LVDSVcc   LVDS Supply Voltage. Bypass LVDSVcc to GND with 0.1µF and 0.001µF capacitors in parallel as close to the pin as possible.     13, 18   LVDSGND   LVDS Ground     14   RxIN2-   Inverting Channel 2 LVDS Serial-Data Input     15   RxILX+   Noninverting Channel 2 LVDS Serial-Data Input     16   RxCLKIN+   Inverting LVDS Parallel-Rate Clock Input     17   RxCLKIN+   Noninverting LVDS Parallel-Rate Clock Input     19, 21   PLLGND   PLL Ground     20   PLLVcc   PLL Supply Voltage. Bypass PLLVcc to GND with 0.1µF and 0.001µF capacitors in parallel as close to the pin as possible.     21   PWRDWN   SV-Tolerant LVTTL/LVCMOS Power-Down Input. PWRDWN is internally pulled down to GND. Outputs are high impedance when PWRDWN = low or open.     23   RxCLKOUT   Parallel-Rate Clock Single-Ended Output. The MAX9242 has a rising-edge strobe. The MAX9244/MAX9246/<br>MAX9254 have a falling-edge strobe.     24   RxOUT0   Channel 0 Single-Ended Outputs     27   RxOUT2   Output Supply Voltage. Bypass each Vcco to GND with 0.1µF and 0.001µF capacitors in parallel as close to the pin as possible.     29 </td <td>8</td> <td>RxIN0-</td> <td>Inverting Channel 0 LVDS Serial-Data Input</td> | 8          | RxIN0-              | Inverting Channel 0 LVDS Serial-Data Input    |

| 11   RxIN1+   Noninverting Channel 1 LVDS Serial-Data Input     12   LVDSVcc   LVDS Supply Voltage. Bypass LVDSVcc to GND with 0.1µF and 0.001µF capacitors in parallel as close to the pin as possible.     13, 18   LVDSGND   LVDS Ground     14   RxIN2+   Inverting Channel 2 LVDS Serial-Data Input     15   RxIN2+   Noninverting Channel 2 LVDS Serial-Data Input     16   RxCLKIN-   Inverting Channel 2 LVDS Parallel-Rate Clock Input     17   RxCLKIN+   Noninverting LVDS Parallel-Rate Clock Input     19, 21   PLLGND   PLL Ground     20   PLLVcc   PLL Supply Voltage. Bypass PLLVcc to GND with 0.1µF and 0.001µF capacitors in parallel as close to the pin as possible.     21   PWRDWN   SV-Tolerant LVTTL/LVCMOS Power-Down Input. PWRDWN is internally pulled down to GND. Outputs are high impedance when PWRDWN = low or open.     23   RxCLKOUT   Parallel-Rate Clock Single-Ended Output. The MAX9242 has a rising-edge strobe. The MAX9244/MAX9246/MAX9254 have a falling-edge strobe.     24   RxOUT0   Parallel-Rate Clock Single-Ended Outputs     27   RXOUT2   Channel 0 Single-Ended Outputs     29   RxOUT3   Output Supply Voltage. Bypass each V <sub>CCO</sub> to GND with 0.1µF and 0.001µF capacitors in parallel as close to the pin as possible.                                                                            | 9          | RxIN0+              | Noninverting Channel 0 LVDS Serial-Data Input |

| 12   LVDS Vcc   LVDS Supply Voltage. Bypass LVDSVcc to GND with 0.1µF and 0.001µF capacitors in parallel as close to the pin as possible.     13, 18   LVDS GND   LVDS Ground     14   RxIN2-   Inverting Channel 2 LVDS Serial-Data Input     15   RxIN2+   Noninverting Channel 2 LVDS Serial-Data Input     16   RxCLKIN-   Inverting LVDS Parallel-Rate Clock Input     17   RxCLKIN+   Noninverting LVDS Parallel-Rate Clock Input     19, 21   PLL Ground     20   PLLVcc   PLL Supply Voltage. Bypass PLLVcc to GND with 0.1µF and 0.001µF capacitors in parallel as close to the pin as possible.     21   PWRDWN   SV-Tolerant LVTTL/LVCMOS Power-Down Input. PWRDWN is internally pulled down to GND. Outputs are high impedance when PWRDWN = low or open.     22   PWRDWN   SV-Tolerant LVTTL/LVCMOS Power-Down Input. PWRDWN is internally pulled down to GND. Outputs are high impedance when PWRDWN = low or open.     23   RxCLKOUT   Parallel-Rate Clock Single-Ended Output. The MAX9242 has a rising-edge strobe. The MAX9244/MAX9246/<br>MAX9254 have a falling-edge strobe.     24   RxOUT0   Channel 0 Single-Ended Outputs     27   RxOUT2   Output Supply Voltage. Bypass each Vcco to GND with 0.1µF and 0.001µF capacitors in parallel as close to the pin as possible.     29   RxOUT3   Output Su                                        | 10         | RxIN1-              | Inverting Channel 1 LVDS Serial-Data Input    |

| 12   LVDSVCC   the pin as possible.     13, 18   LVDSGND   LVDS Ground     14   RxIN2-   Inverting Channel 2 LVDS Serial-Data Input     15   RxIN2+   Noninverting Channel 2 LVDS Serial-Data Input     16   RxCLKIN-   Inverting LVDS Parallel-Rate Clock Input     17   RxCLKIN+   Noninverting LVDS Parallel-Rate Clock Input     19, 21   PLL Ground   PLL Ground     20   PLLVcc   PLL Supply Voltage. Bypass PLLVcc to GND with 0.1µF and 0.001µF capacitors in parallel as close to the pin as possible.     21   PWRDWN   SV-Tolerant LVTTL/LVCMOS Power-Down Input. PWRDWN is internally pulled down to GND. Outputs are high impedance when PWRDWN = low or open.     23   RxCLKOUT   Parallel-Rate Clock Single-Ended Output. The MAX9242 has a rising-edge strobe. The MAX9244/MAX9246/MAX9246/MAX9254 have a falling-edge strobe.     24   RxOUT0   Channel 0 Single-Ended Outputs     27   RxOUT2   Output Supply Voltage. Bypass each Vcco to GND with 0.1µF and 0.001µF capacitors in parallel as close to the pin as possible.     29   RxOUT3   Output Supply Voltage. Bypass each Vcco to GND with 0.1µF and 0.001µF capacitors in parallel as close to the pin as possible.     29   RxOUT3   Annel 0 Single-Ended Outputs     30   RxOUT4 <td>11</td> <td>RxIN1+</td> <td>Noninverting Channel 1 LVDS Serial-Data Input</td>                    | 11         | RxIN1+              | Noninverting Channel 1 LVDS Serial-Data Input |

| 14   RxIN2-   Inverting Channel 2 LVDS Serial-Data Input     15   RxIN2+   Noninverting Channel 2 LVDS Serial-Data Input     16   RxCLKIN-   Inverting LVDS Parallel-Rate Clock Input     17   RxCLKIN+   Noninverting LVDS Parallel-Rate Clock Input     19, 21   PLLGND   PLL Ground     20   PLLVcc   PLL Supply Voltage. Bypass PLLVcc to GND with 0.1µF and 0.001µF capacitors in parallel as close to the pin as possible.     22   PWRDWN   SV-Tolerant LVTTL/LVCMOS Power-Down Input. PWRDWN is internally pulled down to GND. Outputs are high impedance when PWRDWN = low or open.     23   RxCLKOUT   Parallel-Rate Clock Single-Ended Output. The MAX9242 has a rising-edge strobe. The MAX9244/MAX9246/MAX9254 have a falling-edge strobe.     24   RxOUT0   Channel 0 Single-Ended Outputs     27   RxOUT2   Output Supply Voltage. Bypass each Vcco to GND with 0.1µF and 0.001µF capacitors in parallel as close to the pin as possible.     29   RxOUT3   Channel 0 Single-Ended Outputs     30   RxOUT4   Channel 0 Single-Ended Outputs     31   RxOUT3   Channel 0 Single-Ended Outputs                                                                                                                                                                                                                                                          | 12         | LVDSV <sub>CC</sub> |                                               |

| 15   RxIN2+   Noninverting Channel 2 LVDS Serial-Data Input     16   RxCLKIN-   Inverting LVDS Parallel-Rate Clock Input     17   RxCLKIN+   Noninverting LVDS Parallel-Rate Clock Input     19, 21   PLLGND   PLL Ground     20   PLLVCC   PLL Supply Voltage. Bypass PLLVCc to GND with 0.1µF and 0.001µF capacitors in parallel as close to the pin as possible.     22   PWRDWN   5V-Tolerant LVTTL/LVCMOS Power-Down Input. PWRDWN is internally pulled down to GND. Outputs are high impedance when PWRDWN = low or open.     23   RxCLKOUT   Parallel-Rate Clock Single-Ended Output. The MAX9242 has a rising-edge strobe. The MAX9244/MAX9246/<br>MAX9254 have a falling-edge strobe.     24   RxOUT0   Channel 0 Single-Ended Outputs     27   RxOUT2   Output Supply Voltage. Bypass each V <sub>CCO</sub> to GND with 0.1µF and 0.001µF capacitors in parallel as close to the pin as possible.     29   RxOUT3   Output Supply Voltage. Bypass each V <sub>CCO</sub> to GND with 0.1µF and 0.001µF capacitors in parallel as close to the pin as possible.     29   RxOUT3   Channel 0 Single-Ended Outputs     30   RxOUT4   Channel 0 Single-Ended Outputs     31   RxOUT5   Channel 0 Single-Ended Outputs                                                                                                                                           | 13, 18     | LVDSGND             | LVDS Ground                                   |

| 16   RxCLKIN-   Inverting LVDS Parallel-Rate Clock Input     17   RxCLKIN+   Noninverting LVDS Parallel-Rate Clock Input     19, 21   PLLGND   PLL Ground     20   PLLVcc   PLL Supply Voltage. Bypass PLLVcc to GND with 0.1µF and 0.001µF capacitors in parallel as close to the pin as possible.     22   PWRDWN   5V-Tolerant LVTTL/LVCMOS Power-Down Input. PWRDWN is internally pulled down to GND. Outputs are high impedance when PWRDWN = low or open.     23   RxCLKOUT   Parallel-Rate Clock Single-Ended Output. The MAX9242 has a rising-edge strobe. The MAX9244/MAX9246/<br>MAX9254 have a falling-edge strobe.     24   RxOUT0   Channel 0 Single-Ended Outputs     27   RxOUT2   Output Supply Voltage. Bypass each V <sub>CC0</sub> to GND with 0.1µF and 0.001µF capacitors in parallel as close to the pin as possible.     29   RxOUT3   Output Supply Voltage. Bypass each V <sub>CC0</sub> to GND with 0.1µF and 0.001µF capacitors in parallel as close to the pin as possible.     29   RxOUT3   Channel 0 Single-Ended Outputs     30   RxOUT4   Channel 0 Single-Ended Outputs     31   RxOUT5   Channel 0 Single-Ended Outputs                                                                                                                                                                                                           | 14         | RxIN2-              | Inverting Channel 2 LVDS Serial-Data Input    |

| 17   RxCLKIN+   Noninverting LVDS Parallel-Rate Clock Input     19, 21   PLLGND   PLL Ground     20   PLLV <sub>CC</sub> PLL Supply Voltage. Bypass PLLV <sub>CC</sub> to GND with 0.1µF and 0.001µF capacitors in parallel as close to the pin as possible.     22   PWRDWN   SV-Tolerant LVTTL/LVCMOS Power-Down Input. PWRDWN is internally pulled down to GND. Outputs are high impedance when PWRDWN = low or open.     23   RxCLKOUT   Parallel-Rate Clock Single-Ended Output. The MAX9242 has a rising-edge strobe. The MAX9244/MAX9246/<br>MAX9254 have a falling-edge strobe.     24   RxOUT0   Channel 0 Single-Ended Outputs     27   RxOUT2   Output Supply Voltage. Bypass each V <sub>CCO</sub> to GND with 0.1µF and 0.001µF capacitors in parallel as close to the pin as possible.     29   RxOUT3   Channel 0 Single-Ended Outputs     30   RxOUT4   Channel 0 Single-Ended Outputs     31   RxOUT5   Channel 0 Output Supply Voltage. Bypass each V <sub>CC0</sub> to GND with 0.1µF and 0.001µF capacitors in parallel as close to the pin as possible.                                                                                                                                                                                                                                                                                         | 15         | RxIN2+              | Noninverting Channel 2 LVDS Serial-Data Input |

| 19, 21   PLLGND   PLL Ground     20   PLLV <sub>CC</sub> PLL Supply Voltage. Bypass PLLV <sub>CC</sub> to GND with 0.1µF and 0.001µF capacitors in parallel as close to the pin as possible.     22   PWRDWN   5V-Tolerant LVTTL/LVCMOS Power-Down Input. PWRDWN is internally pulled down to GND. Outputs are high impedance when PWRDWN = low or open.     23   RxCLKOUT   Parallel-Rate Clock Single-Ended Output. The MAX9242 has a rising-edge strobe. The MAX9244/MAX9246/<br>MAX9254 have a falling-edge strobe.     24   RxOUT0   Channel 0 Single-Ended Outputs     26   RxOUT1   Channel 0 Single-Ended Outputs     27   RxOUT2   Output Supply Voltage. Bypass each V <sub>CCO</sub> to GND with 0.1µF and 0.001µF capacitors in parallel as close to the pin as possible.     29   RxOUT3   Channel 0 Single-Ended Outputs     30   RxOUT4   Channel 0 Single-Ended Outputs     31   RxOUT5   Channel 0 Single-Ended Outputs                                                                                                                                                                                                                                                                                                                                                                                                                             | 16         | RxCLKIN-            | Inverting LVDS Parallel-Rate Clock Input      |

| 20   PLLV <sub>CC</sub> PLL Supply Voltage. Bypass PLLV <sub>CC</sub> to GND with 0.1µF and 0.001µF capacitors in parallel as close to the pin as possible.     22   PWRDWN   5V-Tolerant LVTTL/LVCMOS Power-Down Input. PWRDWN is internally pulled down to GND. Outputs are high impedance when PWRDWN = low or open.     23   RxCLKOUT   Parallel-Rate Clock Single-Ended Output. The MAX9242 has a rising-edge strobe. The MAX9244/MAX9246/<br>MAX9254 have a falling-edge strobe.     24   RxOUT0   Ended Outputs     26   RxOUT1   Channel 0 Single-Ended Outputs     27   RXOUT2   Output Supply Voltage. Bypass each V <sub>CCO</sub> to GND with 0.1µF and 0.001µF capacitors in parallel as close to the pin as possible.     29   RxOUT3   Output Supply Voltage. Bypass each V <sub>CCO</sub> to GND with 0.1µF and 0.001µF capacitors in parallel as close to the pin as possible.     29   RxOUT3   Channel 0 Single-Ended Outputs     30   RxOUT4   Channel 0 Single-Ended Outputs                                                                                                                                                                                                                                                                                                                                                                    | 17         | RxCLKIN+            | Noninverting LVDS Parallel-Rate Clock Input   |

| 20   PLLVCC   the pin as possible.     22   PWRDWN   5V-Tolerant LVTTL/LVCMOS Power-Down Input. PWRDWN is internally pulled down to GND. Outputs are high impedance when PWRDWN = low or open.     23   RxCLKOUT   Parallel-Rate Clock Single-Ended Output. The MAX9242 has a rising-edge strobe. The MAX9244/MAX9246/ MAX9254 have a falling-edge strobe.     24   RxOUT0     26   RxOUT1     27   RxOUT2     28, 36, 48   Vcco     Output Supply Voltage. Bypass each Vcco to GND with 0.1µF and 0.001µF capacitors in parallel as close to the pin as possible.     29   RxOUT3     30   RxOUT4     31   RxOUT5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 19, 21     | PLLGND              | PLL Ground                                    |

| 22   PWRDWN   high impedance when PWRDWN = low or open.     23   RxCLKOUT   Parallel-Rate Clock Single-Ended Output. The MAX9242 has a rising-edge strobe. The MAX9244/MAX9246/     23   RxCLKOUT   Parallel-Rate Clock Single-Ended Output. The MAX9242 has a rising-edge strobe. The MAX9244/MAX9246/     24   RxOUT0   Channel 0 Single-Ended Outputs     26   RxOUT1   Channel 0 Single-Ended Outputs     27   RxOUT2   Channel 0 Single-Ended Outputs     28, 36, 48   Vcco   Output Supply Voltage. Bypass each Vcco to GND with 0.1µF and 0.001µF capacitors in parallel as close to the pin as possible.     29   RxOUT3   Annel 0 Single-Ended Outputs     30   RxOUT4   Channel 0 Single-Ended Outputs     31   RxOUT5   Channel 0 Output Supply Voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 20         | PLLV <sub>CC</sub>  |                                               |

| 23   HxCLKOUT   MAX9254 have a falling-edge strobe.     24   RxOUT0     26   RxOUT1     27   RxOUT2     28, 36, 48   Vcco     Output Supply Voltage. Bypass each Vcco to GND with 0.1µF and 0.001µF capacitors in parallel as close to the pin as possible.     29   RxOUT3     30   RxOUT4     31   RxOUT5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 22         | PWRDWN              |                                               |

| 26   RxOUT1   Channel 0 Single-Ended Outputs     27   RxOUT2   Channel 0 Single-Ended Outputs     28, 36, 48   V <sub>CCO</sub> Output Supply Voltage. Bypass each V <sub>CCO</sub> to GND with 0.1µF and 0.001µF capacitors in parallel as close to the pin as possible.     29   RxOUT3     30   RxOUT4     31   RxOUT5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 23         | RxCLKOUT            |                                               |

| 27   RxOUT2     28, 36, 48   V <sub>CCO</sub> Output Supply Voltage. Bypass each V <sub>CCO</sub> to GND with 0.1µF and 0.001µF capacitors in parallel as close to the pin as possible.     29   RxOUT3     30   RxOUT4     31   RxOUT5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 24         | RxOUT0              |                                               |

| 28, 36, 48   V <sub>CCO</sub> Output Supply Voltage. Bypass each V <sub>CCO</sub> to GND with 0.1µF and 0.001µF capacitors in parallel as close to the pin as possible.     29   RxOUT3     30   RxOUT4     31   RxOUT5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 26         | RxOUT1              | Channel 0 Single-Ended Outputs                |

| 28, 36, 48 VCCO close to the pin as possible.   29 RxOUT3   30 RxOUT4   31 RxOUT5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 27         | RxOUT2              |                                               |

| 30 RxOUT4   31 RxOUT5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 28, 36, 48 | Vcco                |                                               |

| 31 RxOUT5 Channel 0 Single-Ended Outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 29         | RxOUT3              |                                               |

| 31 RXOUI5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 30         | RxOUT4              | <br>  Objects al O Objects Finale al Outroute |

| 33 RxOUT6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 31         | RxOUT5              | - Unannei U Single-Ended Outputs              |