## INTRODUCTION

The KS0125 is a multistandard video encoder with line interpolation, crisping circuits, and on-screen-display (OSD) functions. These special functions make this encoder well suited for MPEG playback applications, such as video compact disk (VCD), and digital video disk (DVD).

# 80-PQFP

## **FEATURES**

- · Line interpolation

- · Crisping circuit to enhance horizontal resolution and to reduce MPEG mosquito effect

- 250 character ROM containing the English and Japanese alphabets, Korean characters, numbers, and symbols.

- 4 user selectable OSD character colors and 2 background colors

- CCIR 601 or CCIR 656 input

- NTSC-M or PAL-B,G,H output

- Master or slave timing operation with EAV support for CCIR 656 input

- Adjustable hue

- 3 10-bit DACs for simultaneous CVBS and S-video output

- DACs support power-down mode

## **ORDERING INFORMATION**

| Device | Package | Operating Temperature |

|--------|---------|-----------------------|

| KS0125 | 80-PQFP | 0 to +70°C            |

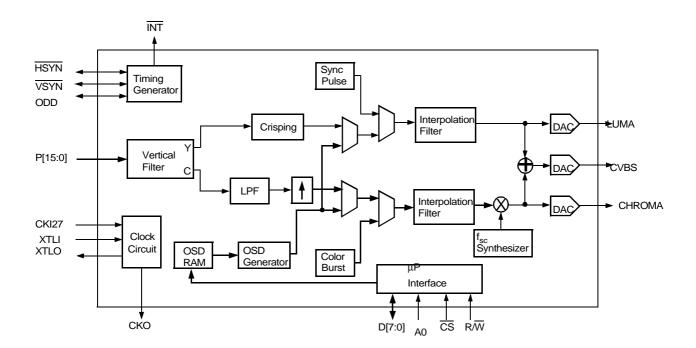

## **BLOCK DIAGRAM**

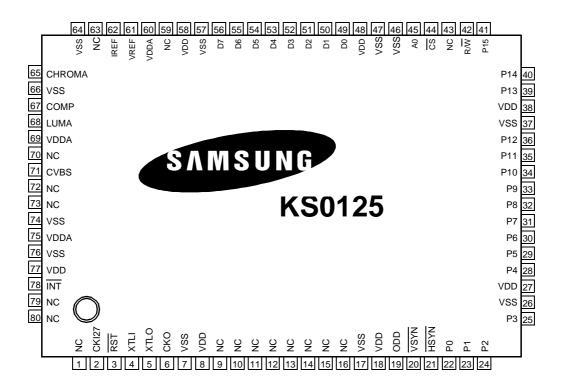

## **PIN ASSIGNMENT-80 PQFP**

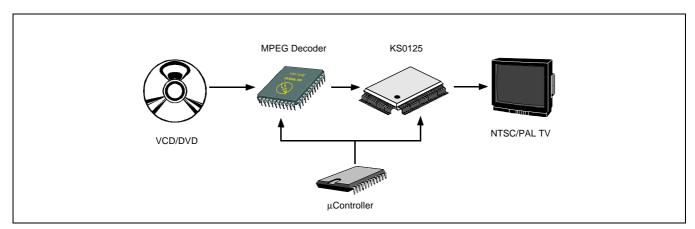

## **TYPICAL APPLICATION**

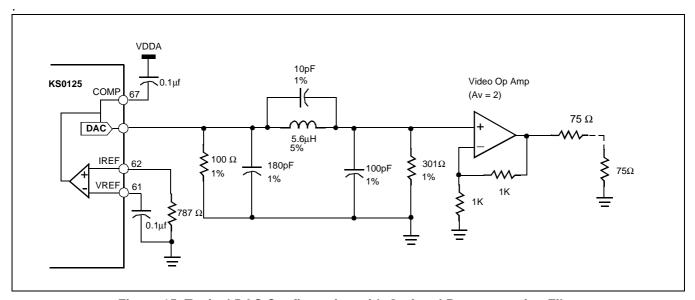

The KS0125 is shown in a typical VCD or DVD application

Figure 1. Typical Application

## PIN CROSS REFERENCE: ORDER BY PIN NUMBER

| Pin # | Pin Name | Pin # | Pin Name | Pin# | Pin Name | Pin# | Pin Name |

|-------|----------|-------|----------|------|----------|------|----------|

| 1     | NC       | 21    | HSYN     | 41   | P15      | 61   | VREF     |

| 2     | CKI27    | 22    | P0       | 42   | R/W      | 62   | IREF     |

| 3     | RST      | 23    | P1       | 43   | NC       | 63   | NC       |

| 4     | XTLI     | 24    | P2       | 44   | CS       | 64   | VSS      |

| 5     | XTLO     | 25    | P3       | 45   | A0       | 65   | CHROMA   |

| 6     | СКО      | 26    | VSS      | 46   | VSS      | 66   | VSS      |

| 7     | VSS      | 27    | VDD      | 47   | VSS      | 67   | COMP     |

| 8     | VDD      | 28    | P4       | 48   | VDD      | 68   | LUMA     |

| 9     | NC       | 29    | P5       | 49   | D0       | 69   | VDDA     |

| 10    | NC       | 30    | P6       | 50   | D1       | 70   | NC       |

| 11    | NC       | 31    | P7       | 51   | D2       | 71   | CVBS     |

| 12    | NC       | 32    | P8       | 52   | D3       | 72   | NC       |

| 13    | NC       | 33    | P9       | 53   | D4       | 73   | NC       |

| 14    | NC       | 34    | P10      | 54   | D5       | 74   | VSS      |

| 15    | NC       | 35    | P11      | 55   | D6       | 75   | VDDA     |

| 16    | NC       | 36    | P12      | 56   | D7       | 76   | VSS      |

| 17    | VSS      | 37    | VSS      | 57   | VSS      | 77   | VDD      |

| 18    | VDD      | 38    | VDD      | 58   | VDD      | 78   | INT      |

| 19    | ODD      | 39    | P13      | 59   | NC       | 79   | NC       |

| 20    | VSYN     | 40    | P14      | 60   | VDDA     | 80   | NC       |

# **PIN DESCRIPTION**

| Pin Name      | Pin Name         | I/O   | Description                                                                                                                               |

|---------------|------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------|

| DIGITAL VIDEO | PORT             |       |                                                                                                                                           |

| P0 – P7       | 22 – 25, 28 – 31 | I     | For CCIR 601 data, these pins are the inputs for C0 – C7. For CCIR 656 data, these pins are the inputs for YC0 – YC7.                     |

| P8 – P15      | 32 – 36, 39 – 41 | I     | These pins are for CCIR 601 Y0 - Y7 inputs only.                                                                                          |

| CLOCK AND TIM | /ING             |       |                                                                                                                                           |

| XTLI          | 4                | I     | 13.5MHz crystal input, or 13.5 MHz CMOS clock input.                                                                                      |

| XTLO          | 5                | 0     | 13.5MHz crystal output.                                                                                                                   |

| CKI27         | 2                | I     | 27MHz TTL clock input.                                                                                                                    |

| СКО           | 6                | 0     | 27MHz or 13.5MHz clock output(controlled by REGC bit4).                                                                                   |

| HSYN          | 21               | I/O   | Active low horizontal sync. It is an output in master mode; an input in slave mode(default).                                              |

| VSYN          | 20               | I/O   | Active low vertical sync. It is an output in master mode; an input in slave mode(default).                                                |

| ODD           | 19               | I/O   | Field flag. High for field 1; low for field 2. It is an output in master mode; an input in slave mode.                                    |

| INT           | 78               | 0     | Open drain, active low interrupt. It is triggered by the start of the vertical sync. Reset by software (VFLG bit0).                       |

| ANALOG VIDEO  | OUTPUT           |       |                                                                                                                                           |

| CVBS          | 71               | 0     | Composite base band output(controlled by REGD bit5).                                                                                      |

| CHROMA        | 65               | 0     | Chroma output(controlled by REGD bit6).                                                                                                   |

| LUMA          | 68               | 0     | Luma output(controlled by REGD bit6).                                                                                                     |

| DAC REFERENCE | E AND COMPENS    | SATIO | N                                                                                                                                         |

| VREF          | 61               | -     | Voltage reference. The chip contains a 1.235 V internal band gap reference. Connect a 0.1 μF capacitor to VSSA.                           |

| IREF          | 62               | -     | Current reference. A resistor with a nominal value of 787 $\Omega$ should be connected to this pin and ground.                            |

| COMP          | 67               | -     | Compensation capacitor for the DAC internal reference amplifier. A 0.1 $\mu F$ ceramic capacitor is required between this pin and ground. |

| HOST INTERFAC | CE               |       |                                                                                                                                           |

| A0            | 45               | I     | Address line.                                                                                                                             |

| D0 - D7       | 49 - 56          | I/O   | Bidirectional data lines.                                                                                                                 |

| CS            | 44               | I     | Chip select strobe for data read and write.                                                                                               |

# PIN DESCRIPTION (Continued)

| Pin Name    | Pin Name                                            | I/O | Description                                                                                                                                                      |

|-------------|-----------------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R/W         | 42                                                  | I   | This pin controls the data flow direction when CS is low. A high indicates that the data is read from the chip. A low indicates the data is written to the chip. |

| RST         | 3                                                   | I   | Active low chip reset.                                                                                                                                           |

| POWER AND G | ROUND                                               | ·   |                                                                                                                                                                  |

| VDD         | 8, 18, 27, 38, 48,<br>58, 77                        | +5V | Digital power supply.                                                                                                                                            |

| VDDA        | 60, 69, 75                                          | +5V | Analog power supply.                                                                                                                                             |

| VSS         | 7, 17, 26, 37, 46,<br>47, 57, 66, 74,<br>76         | GND | Common ground.                                                                                                                                                   |

| NO CONNECT  |                                                     |     |                                                                                                                                                                  |

| NC          | 1, 9 – 16, 43, 59,<br>62, 63, 70, 72,<br>73, 79, 80 | _   | These pins are reserved and should not be connected.                                                                                                             |

#### **FUNCTIONAL DESCRIPTION**

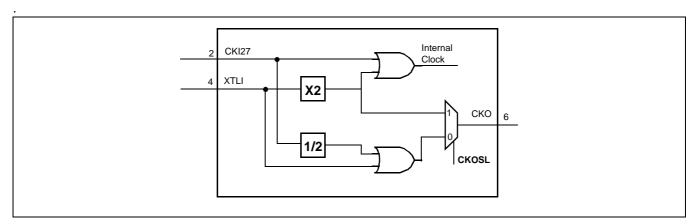

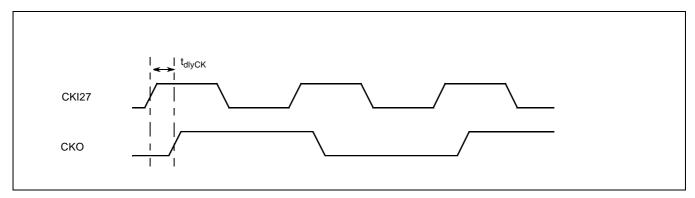

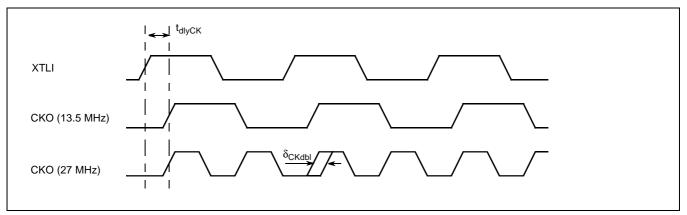

#### **CLOCK INPUT AND OUTPUT**

The KS0125 requires an external clock for its operation. It also outputs a clock (CKO) which can be used as a pixel clock for an external memory controller.

#### **CLOCK INPUT**

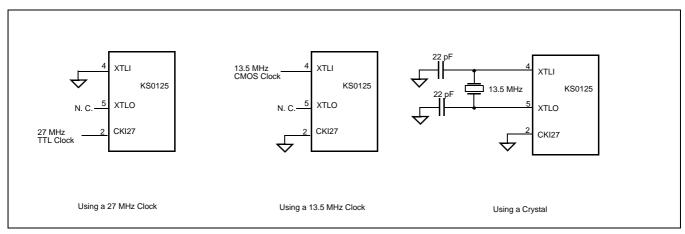

The KS0125 internally operates at 27 MHz. A 27 MHz TTL clock, a 13.5 MHz CMOS clock or a 13.5 MHz crystal can be used to supply the internal clock. Figure 4 shows the three possible external clock configurations. It is important that the unused clock input be grounded. The clock source should have no more than a 50 ppm frequency variation.

Figure 1. External Clock Configurations

#### **CLOCK OUTPUT**

The KS0125 provides an output clock (CKO) which can be used as a pixel clock. The frequency of the output clock can be either 27 MHz or 13.5 MHz, which is selected via the **CKOSL** bit in the **REGC** control register. Figure 2 shows the internal logic for this output clock

Figure 2. Output Clock Generation Logic

#### **RESET**

The KS0125 has a master reset pin  $\overline{\text{RST}}$ . This input is used to set the internal operation to a predefined state. During power up, the input on this pin must remain low until the power supply is stable. When the  $\overline{\text{RST}}$  is low, all the control registers are set to their default values.

#### **VIDEO TIMING**

The KS0<u>125 can oper</u>ate in either master or slave timing mode. There are three bidirectional synchronization signals: HSYN, VSYN, and ODD. In <u>master mode, these</u> three signals are outputs. In slave mode, the KS0125 synchronizes to externally generated HSYN, and VSYN or ODD. For CCIR 656 format, the KS0125 will synchronize to the embedded EAV.

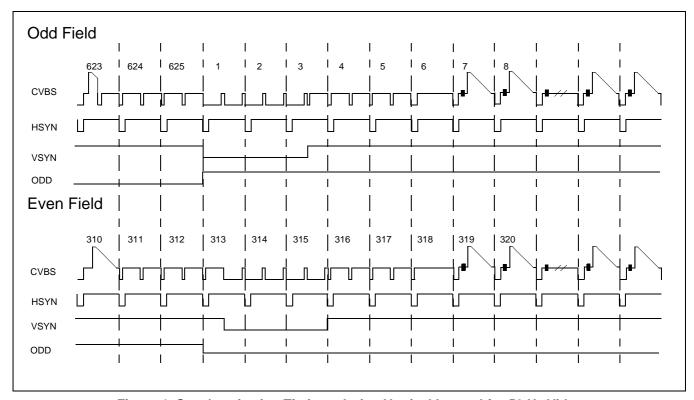

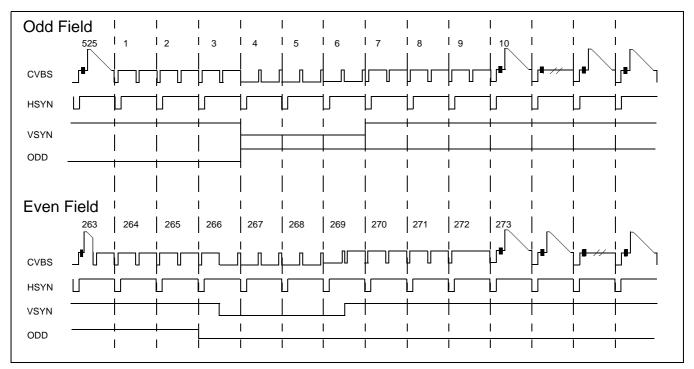

#### **MASTER MODE TIMING**

In master mode, the KS0125 generates three synchronization signals:  $\overline{\text{HSYN}}$ ,  $\overline{\text{VSYN}}$ , and ODD. Depending on the field rate, the KS0125 generates different synchronization timings for 50 Hz and 60 Hz video. For 50 Hz video, Figure 1 shows the three synchronization signals during the vertical interval. For 60 Hz video similar timing is shown in Figure 7. Depending on which field is active, the  $\overline{\text{VSYN}}$  transitions are either aligned to the falling edge of HSYN, or in the middle of a video line. ODD is always aligned to the falling edge of HSYN.

Figure 1. Synchronization Timings during Vertical Interval for 50 Hz Video

Figure 1. Synchronization Signals during Vertical Interval for 60 Hz Video.

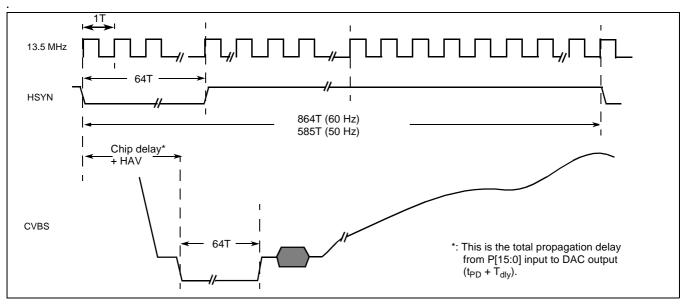

Figure 2 shows the line timing. Note that the pulse width for HSYN is the same as the CVBS horizontal sync

Figure 2. Video Line Timing

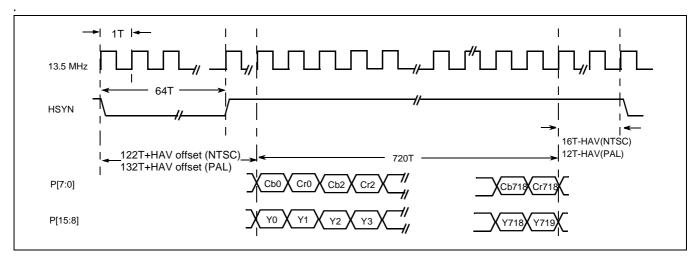

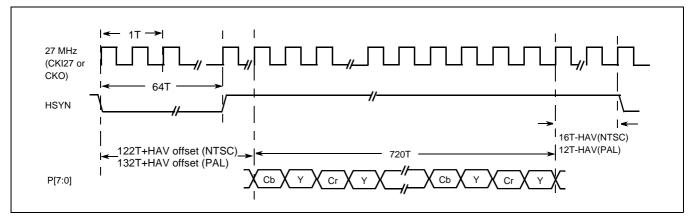

The active video input is synchronized to HSYN. To accommodate external data latency, the phase between the start of the active video input and the leading edge of HSYN can be adjusted via **HAV[2:0]** in control register **REGD**, and **SHFHAV** in control register **REGE**. Pixel data alignment for 16 bit and 8 bit inputs are shown in Figure 3 and Figure 10, respectively.

Figure 3. Pixel Data Alignment for 16 Bit Input

Figure 4. Pixel Data Alignment for 8 Bit Input

The reference point for pixel data setup and hold time is different for 27 MHz and 13.5 MHz clock inputs for 8 bit input data. If the 27 MHz clock input is used, the reference point is the rising edge of the CKI27 input. If the 13.5 MHz clock input is used, the reference point is the rising edge of the CKO output.

For CCIR 601 input, the setup and hold time is always referenced to the rising edge of the clock input.

#### **SLAVE MODE TIMING**

In slave mode operation, the KS0125 synchronizes to externally generated timing signals, or EAV timing reference codes embedded in the CCIR 656 data stream.

For CCIR 601 input, the internal horizontal timing counter is synchronized to the leading edge of the HSYN input. The KS0125 assumes the first active pixel input starts 122 pixel clocks (13.5 MHz) after the leading edge of HSYN for NTSC, or 132 pixel clocks for PAL. The line counter gets reset by the leading edge of VSYN. The internal field counter is synchronized to the leading edge of either VSYN or ODD input. The programmable **FLD** bit in the control

register **REGE** is used to select one of the two inputs for field synchronization.

For CCIR 656 input, synchronization is done through the EAV timing codes embedded in the digital video stream. The **EAV** bit in **REGE** must be set to a 1.

For 8-bit CbYCr input without EAV timing codes, The KS0125 synchronizes to the external timing signals. The **EAV** bit in **REGE** must be set to a 0.

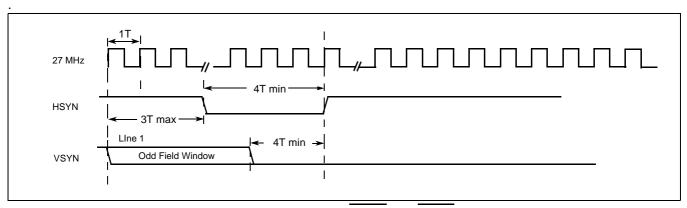

If the KS0125 is programmed to use  $\overline{\text{VSYN}}$  and  $\overline{\text{HSYN}}$  for identifying the odd field (the **FLD** bit in **REGE** is set to a 0), the timing shown in Figure 11 must be met. If the falling edge of the  $\overline{\text{VSYN}}$  falls outside of the window, the field is identified as an even field

Figure 5. Identifying Field Using HSYN and VSYN in Slave Mode

#### DIGITAL DATA PATH AND SIGNAL PROCESSING

#### **LUMINANCE DATA PATH**

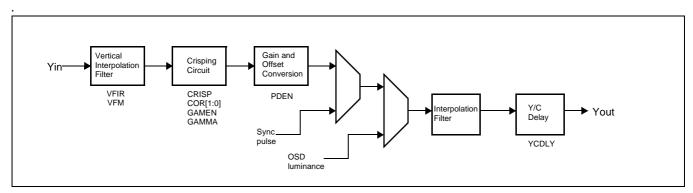

Figure 6 shows the functional block diagram for the luminance path

Figure 6. Luminance Processing Unit

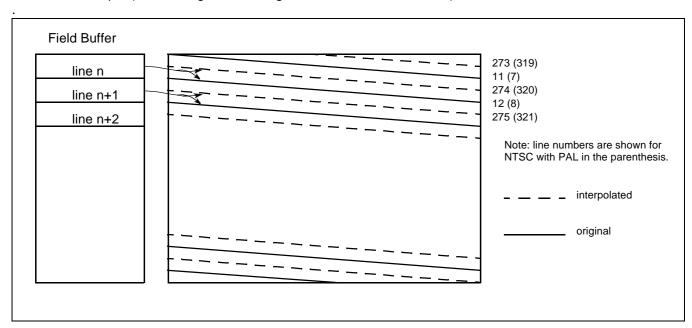

The KS0125 has a field interpolation filter which is very useful for single field input sources, such as MPEG 1. For single field video sources, the KS0125 uses the input for the odd field without change. The even field is interpolated from the input. The interpolation filter employs a proprietary algorithm to create the even field which results in a smooth edge along diagonal and vertical directions. The vertical interpolation filter generates the current line output using the current and previous line inputs. Figure 13 shows how interlaced video is displayed on a CRT. The vertical interpolation filter generates a line using the lines above and below it in the other field. This requires that pixel data for the line below the interpolated line be the input when the interpolated line is generated. For example, if line 274 in Figure 13 is the line being interpolated, pixel data used for video line 12 (line n in the field buffer) must be the current input (Refer to Figure 1 and Figure 7 for video line definition)

Figure 7. Field Interpolation Input Requirement

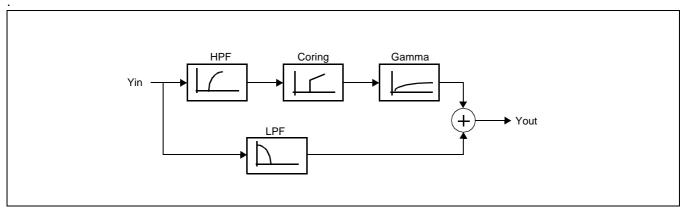

The crisping circuit further improves video quality. The crisping circuit is designed to reduce mosquito effect in MPEG 1 video. The functional block diagram is shown in Figure 8. It consists of a band separation circuit, a coring circuit, and a gamma correction ROM. The Y data is first separated into high and low frequency components. The high frequency component's low amplitude signals can optionally be suppressed by the coring circuit. The amplitude can be binary codes 1, 3, or 6, which is selected by programming the **COR[1:0]** bits in **REGA**. An additional gamma ROM can apply gamma correction to the high frequency component after the coring function. Two selections are provided for gamma correction. One has large peaking (**GAMMA** in **REGA** is set to a 1); the other has small peaking (**GAMMA** is set to a 0). The gamma correction can be disabled by programming the **GAMEN** bit in **REGA** to a 0. Finally, the high and low frequency components are recombined

Figure 8. Crisping Circuit Block Diagram

The luminance data is gain and offset adjusted so its output will be at the correct NTSC or PAL level. The sync and OSD are inserted after the gain and offset conversion stage.

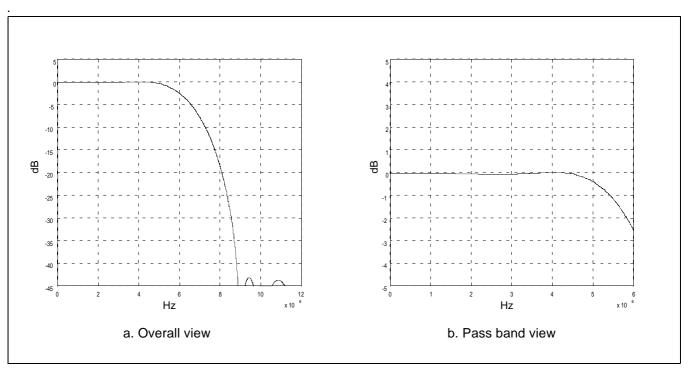

Before going to the DAC, the luminance data is interpolated to 27 MHz. This up sampling will simplify the external analog reconstruction filter. Figure 9 shows the characteristic of the interpolation filter. An optional one pipe line delay is also included to compensate for any YC delay in the reconstruction filter

Figure 9. Luminance Pixel Interpolation Filter Characteristic

#### **Chrominance Data Path**

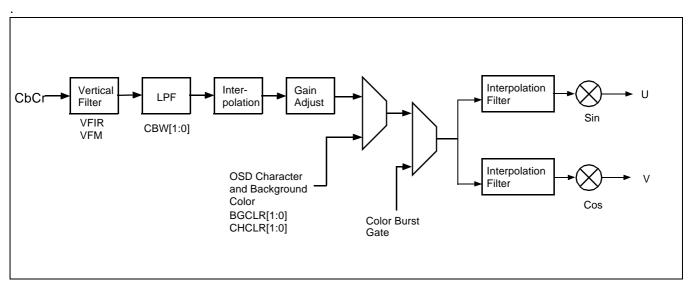

Figure 10 is the functional block diagram for the chrominance data path

Figure 10. Chrominance Data Path

The chrominance path also contains a field interpolation filter which serves the same purpose as the field interpolation filter in the luminance path. Both luma and chroma field interpolation filters are controlled by the two register bits **VFIR** and **VFM**.

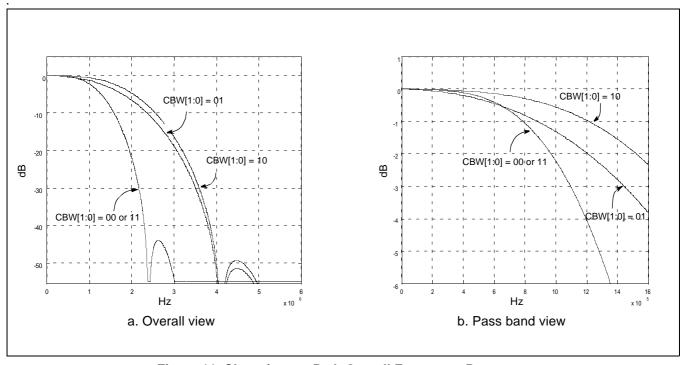

The chrominance data passes through a low pass filter whose bandwidth can be controlled via **CBW[1:0]** in **REGA**. The bandwidth can be 1.1 MHz, 1.45 MHz, or 1.75 MHz.

The Cb/Cr data is interpolated from 6.75 MHz to 13.5 MHz, and then gain adjusted. The Cb/Cr data is then demultiplexed to Cb and Cr paths.

OSD character and background colors are inserted into the Cb and Cr data paths. Two background colors (blue and black) or transparent background can be selected through **BGCLR[1:0]**, and four character colors (white, cyan, green, and magenta) can be selected via **CHCLR[1:0]**, both in **REGB**.

The color burst gate is inserted and the 13.5 MHz Cb and Cr data are up sampled to 27 MHz through an interpolation filter. Finally, the two color difference components are quadrature modulated by an internally generated subcarrier.

The overall frequency response of the chrominance path is shown in Figure 11

Figure 11. Chrominance Path Overall Frequency Response

## **ON-SCREEN-DISPLAY (OSD)**

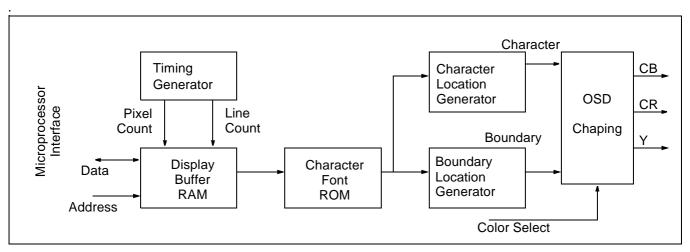

The On Screen Display (OSD) allows the user to Overlay characters over the video. The desired characters and their positions are programmed on the display screen via the 8-bit micorprocessor interface. Figure 15 shows a block diagram of the OSD. The OSD block consists of a character display buffer RAM, a character-generation font ROM, character location generation, character boundary location generation and OSD shaping circuits. The Timing Generator Pixel Counter and Line counter of the KS0125 generate controls to define the OSD display area. The RAM address defines where the character will be displayed. The RAM data output acts as the pointer to select a particular character from the Character font ROM. The character location generator converts the 12-bit character font ROM outputs to serial character streams, while the boundary location generator creates a boundary to surround the character. Finally, the OSD shaping circuits performs character color selection and background color selection. The OSD CB,CR and Y outputs are properly shaped by band-limited filters to reduce the ringing caused by the abrupt amplitude changes

Figure 12. On Screen Display Block Diagram

#### **OSD Color Selection And Background Color Selection**

The OSD supports four different colors for the character display and two different background colors. The color select ion for the character and the background and the background are controlled by the programmable REGB control register. Tables 1 and 2 describle the OSD color selection and background color selection.

Notics that the user is recommended to choose the color white for the OSD character, bacause the KS0125 creates less flicking effect at the character boundary when white is chosen.

| REGB     | Color     | Comments                      |

|----------|-----------|-------------------------------|

| BIT(6:5) | Selection |                               |

| 00       | WHITE     | Default, 80% Intensity        |

| 01       | CYAN      | 80% Intensity, 60% Saturation |

| 10       | GREEN     | 80% Intensity, 60% Saturation |

| 11       | MEAENTA   | 80% Intensity, 60% Saturation |

**Table 1. OSD Character Color Selection**

| REGB<br>BIT(6:5) | Background Color<br>Selection | Comments                          |  |  |  |  |

|------------------|-------------------------------|-----------------------------------|--|--|--|--|

| 0X               | WHITE                         | Character background is the video |  |  |  |  |

| 10               | GREEN                         | Video blanked                     |  |  |  |  |

| 11               | MEAENTA                       | Video blanked                     |  |  |  |  |

**Table 2. OSD Background Color Selection**

#### **OSD Display Area**

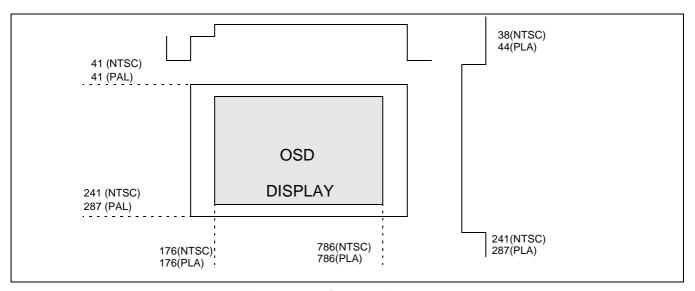

The OSD display area is illustrated in figure 15-1. The starting and ending position in the horizontal direction are 176 and 786 in terms of pixel counts for both NTSC and PAL. The starting and ending position in the vertical direction are 41 and 241 for NTSC, and 47. Therefore, there are 200 scan lines for NTSC and 240 scan lines for PAL.

Figure 13. On Screen Display Area

#### **OSD RAM Address**

The OSD display area can fit in 25 characters in the horizontal direction and 10 characters in the vertical direction. The OSD RAM address is used to assign a location for a display character in the OSD display area. Table 3 describes the OSD RAM address and the character location mapping. Notice that the OSD RAM addresses between the On-Screen Lines are not continuously incremented. Instead, each On-Screen Line starts from address 32n in decimal, where n=0,1,2,....,9.

When programming the OSD, even though each OSD display line can hold 25 characters (character 0 to character 24), the user is recommended to program an empty space (address 0AE Hex) for the last character for each OSD display line. This will avoid missing pixels at the last character position. In other words, the 25th character for each OSD line shall always be programmed as an empty space by using address 0AE for the OSD Font ROM.

.

**Table 3. OSD RAM Address Description**

| OSD RAM Address<br>(HEXADECIMAL) | Character Location On Screen                  |

|----------------------------------|-----------------------------------------------|

| 000–018                          | On-Screen line1, character 0 to character 24  |

| 020-038                          | On-Screen line2, character 0 to character 24  |

| 040–058                          | On-Screen line3, character 0 to character 24  |

| 060–078                          | On-Screen line4, character 0 to character 24  |

| 080–098                          | On-Screen line5, character 0 to character 24  |

| 0A0-0B8                          | On-Screen line6, character 0 to character 24  |

| 0C0-0D8                          | On-Screen line7, character 0 to character 24  |

| 0E0-0F8                          | On-Screen line8, character 0 to character 24  |

| 100–118                          | On-Screen line9, character 0 to character 24  |

| 120–138                          | On-Screen line10, character 0 to character 24 |

#### **OSD Font ROM**

The OSD Font ROM contains a total of 250 characters. These character addresses are continuously incremented from 0 to 250 in decimal, (or 000 to 0F9 in hexadecimal).

#### Addressing The OSD Font Rom By The OSD RAM Data

The OSD RAM data is used as the character pointer to select a particular character from the OSD font ROM. Each character in the OSD Font ROM is designated to fit within a 10 x 12 dot matrix. The pointer only points to the top left corner bit of each character matrix. When a character is selected by the OSD RAM data during a display scan, the OSD ROM control circuitry will automatically generate all necessary addresses to go through all bit locations of the 10 x12 character matrix. Table 26 shows the contents of the OSD Font ROM, along with their address locations.

## **OSD Character Boundary**

During the on screen display,the Boundary Location Generator generates a boundary to surround a character. The actual character size is 12 x 14 dot matrix. With the boundary surrounding a character, the character size becomes a 14 x 16 dot matrix.

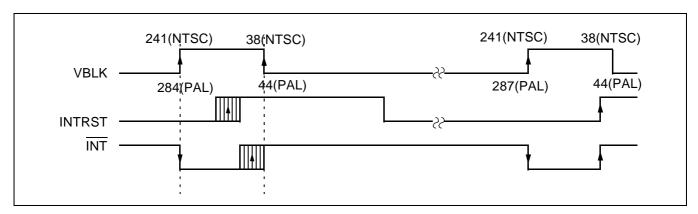

#### Valid Time to Access the OSD RAM

There are two way to access the OSD RAM. One of them is using it when VFIG bit 7 is high. The other is using INT(pin # 78), as follows.

## When INTEN=1

Figure 14.

When INTEN=1, INT=high

**Table 4. Font ROM Table**

| Font | Code | Font     | Code | Font     | Code | Font        | Code | Font | Code | Font      | Code | Font              | Code | Font     | Code |

|------|------|----------|------|----------|------|-------------|------|------|------|-----------|------|-------------------|------|----------|------|

| 0    | 00   | W        | 20   | 닫        | 40   | 팩           | 60   | 7    | 80   | <b>〈</b>  | A0   | 7                 | C0   | 1        | E0   |

| 1    | 01   | X        | 21   | 림        | 41   | 편           | 61   | 早    | 81   | =         | A1   | ħ                 | C1   | 3        | E1   |

| 2    | 02   | Υ        | 22   | 백        | 42   | 힘           | 62   | 무    | 82   | >         | A2   | 4                 | C2   | 5        | E2   |

| 3    | 03   | Z        | 23   | 램        | 43   | 한           | 63   | 주    | 83   | ٠.        | А3   | 2                 | С3   | Ú        | E3   |

| 4    | 04   | а        | 24   | 면        | 44   | ÖO          | 64   | 꾸    | 84   | ďB        | A4   | ケ                 | C4   | JL       | E4   |

| 5    | 05   | b        | 25   | 반        | 45   | Height      | 65   | 罟    | 85   | 심         | A5   |                   | C5   | レ        | E5   |

| 6    | 06   | С        | 26   | 刧        | 46   | İ           | 66   | ΗΟ   | 86   |           | A6   | サ                 | C6   |          | E6   |

| 7    | 07   | d        | 27   | 刧        | 47   | ㅁ           | 67   | 則    | 87   |           | A7   | <u>ئ</u>          | C7   | ŗ        | E7   |

| 8    | 80   | e        | 28   | 卽        | 48   | ㅁ           | 68   | 꽤    | 88   | 5         | A8   | ス                 | C8   | ٦        | E8   |

| 9    | 09   | f        | 29   | 퐌        | 49   | 겝           | 69   | 솸    | 89   | #         | A9   | せ                 | C9   | T        | E9   |

| Α    | 0A   | g        | 2A   | 성        | 4A   | 바           | 6A   | ᇛ    | 8A   | Δ         | AA   | ソ                 | CA   | 0        | EA   |

| В    | 0B   | h        | 2B   | ŻO       | 4B   | 긲           | 6B   | راه  | 8B   | IJ        | AB   | <u>夕</u>          | СВ   | ş        | EB   |

| С    | 0C   | İ        | 2C   | 색        | 4C   | 끅           | 6C   | 용    | 8C   |           | AC   | Ŧ                 | CC   | _        | EC   |

| D    | 0D   | j        | 2D   | 선        | 4D   | 01          | 6D   | 준    | 8D   | •         | AD   | "                 | CD   | Ť        | ED   |

| E    | 0E   | k        | 2E   | 션        | 4E   | Oł          | 6E   | 吾    | 8E   |           | AE   | <u>テ</u>          | CE   | 1        | EE   |

| F    | 0F   |          | 2F   | 일        | 4F   | 뀖           | 6F   |      | 8F   | <u>기</u>  | AF   | <u> </u>          | CF   | Э        | EF   |

| G    | 10   | m        | 30   | 열        | 50   | IJ          | 70   | 원    | 90   | đ         | В0   | <u>ナ</u>          | D0   | ッ        | F0   |

| Н    | 11   | n        | 31   | 쟓        | 51   | <del></del> | 71   | 환    | 91   | 어         | B1   |                   | D1   | ृप       | F1   |

| I    | 12   | 0        | 32   | 평        | 52   | <u> </u>    | 72   | 의    | 92   | 믜         | B2   | <u>_</u> <u>Z</u> | D2   | <u> </u> | F2   |

| J    | 13   | р        | 33   | 힘        | 53   | 계           | 73   | 좌    | 93   | ᅫ         | В3   | 不                 | D3   | ᄩ        | F3   |

| K    | 14   | q        | 34   | Ö        | 54   | 玔           | 74   | 화    | 94   | ō         | B4   | <u></u>           | D4   |          | F4   |

| L    | 15   | r        | 35   | 펀        | 55   |             | 75   | !    | 95   | 山         | B5   | <u>/\</u>         | D5   |          | F5   |

| M    | 16   | s        | 36   | 역        | 56   | <u> </u>    | 76   | %    | 96   | <u> 다</u> | В6   | <u> ヒ</u>         | D6   | <u> </u> | F6   |

| N    | 17   | t        | 37   | <u>정</u> | 57   | <u> 1</u>   | 77   | &    | 97   | 중         | B7   | <u> </u>          | D7   | 모        | F7   |

|      | 18   | u        | 38   | 전        | 58   | 로           | 78   | (    | 98   | 뵬         | B8   | <u> </u>          | D8   | <u>택</u> | F8   |

| Р    | 19   | V        | 39   | 장        | 59   | <u></u>     | 79   | )    | 99   | <u> </u>  | В9   | <u>ホ</u>          | D9   | 호        | F9   |

| Q    | 1A   | W        | 3A   | 집        | 5A   | <u> </u>    | 7A   | ж    | 9A   | <u> </u>  | ВА   | <u> </u>          | DA   | N/A      | FA   |

| R    | 1B   | ж        | 3B   | 절        | 5B   | 조           | 7B   | 5    | 9B   | <u>잔</u>  | BB   |                   | DB   | N/A      | FB   |

| S    | 1C   | У        | 3C   | 작        | 5C   | <u> </u>    | 7C   | _    | 9C   | <u> 7</u> | ВС   |                   | DC   | N/A      | FC   |

| T    | 1D   | Z        | 3D   | 캡        | 5D   | <u> </u>    | 7D   |      | 9D   | 1         | BD   | <u> </u>          | DD   | N/A      | FD   |

| U    | 1E   | <u>간</u> | 3E   | 亩        | 5E   | <u> </u>    | 7E   | /    | 9E   | <u> </u>  | BE   | <u>Ŧ</u>          | DE   | N/A      | FE   |

| V    | 1F   | <u>남</u> | 3F   |          | 5F   | 표           | 7F   | •    | 9F   | I         | BF   | <u> 77 </u>       | DF   | N/A      | FF   |

#### D/A CONVERTERS

The KS0125 contains three high speed current DACs. Each DAC can drive a 75 load. The three DACs operate at the 27 MHz clock rate. The voltage supply for the DAC must be decoupled from the power supply for the digital circuitry on the chip. The voltage between the analog supply (VDDA) and digital supply (VDD) must be maintained within one diode voltage drop (0.7 V). The DACs require two external 0.1  $\mu$ F capacitors and one 787  $\Omega$  resistor connected as shown in Figure 15. Also shown in Figure 15 is an optional reconstruction filter for the DAC output to reduce sinx/x distortion

Figure 15. Typical DAC Configuration with Optional Reconstruction Filter

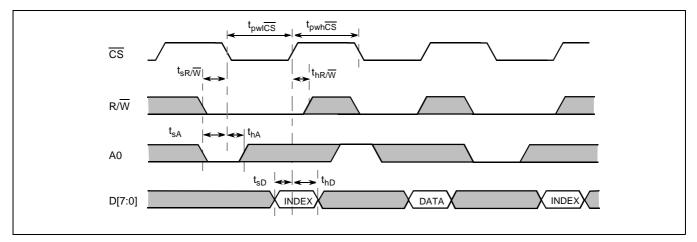

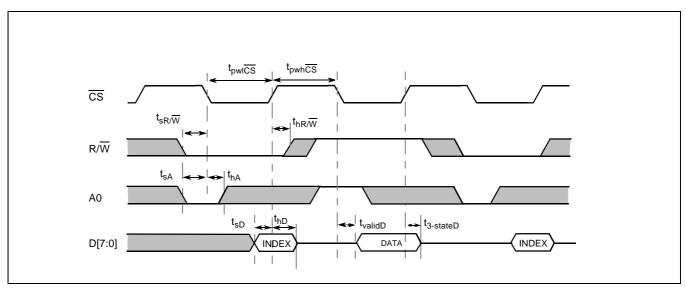

#### **Host Interface**

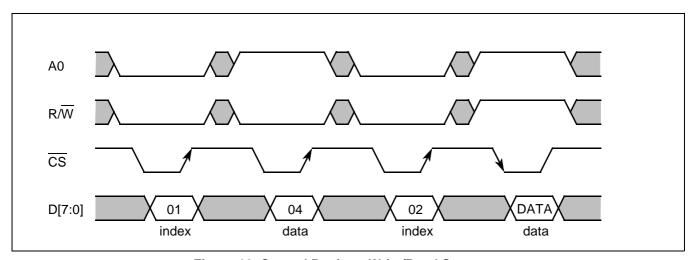

The KS0125 uses a parallel host interface for programming the control registers and OSD RAM. The bus consists of one address line, eight data lines, one read/write (R/W) line, and one chip select (CS) line. To access the control registers, an index is first written to the index register (A0 = 0). Then the data is read from or written to the data register (A0 = 1). Figure 16 shows how data is written to control register **REGB** (index 1) and how to read control register **VFLG** (index 2).

Figure 16. Control Register Write/Read Sequence

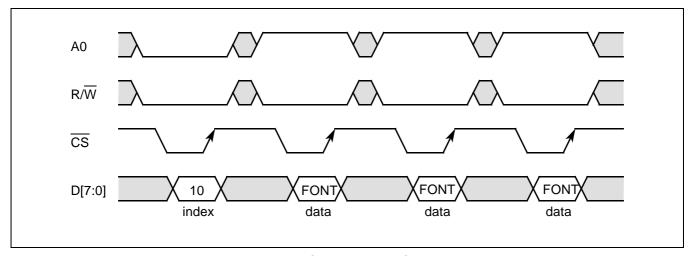

Writing to the OSD RAM is done by first writing the row number to the index register (the number must be offset by hex 10 to indicate that data written to the data register is intended for OSD RAM). A burst of 1 to 25 bytes is then written to the data register. The data will be transferred sequentially into the OSD RAM for the particular row starting from the first column location. Figure 17 provides an example of how to change the first three characters in the first row. Note that the OSD RAM can only be written.

Figure 17. OSD RAM Write Sequence

For both control registers and OSD RAM, the number written to the index register remains unchanged until a new number is written to it. For OSD RAM write, the internal auto-increment pointer gets reset to 0 either after the 25th location is written, or the index register is written.

## **DETAILED REGISTER DESCRIPTION**

The KS0125 contains eight user programmable control registers and one OSD RAM selection register. Table 2 is a register summary list.

**Table 5. Register Summary**

| Index     | Mnemonic | Power-On<br>Default | Description                                                                                                                                       |

|-----------|----------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 00h       | REGA     | 79h                 | Control register A.                                                                                                                               |

| 01h       | REGB     | 04h                 | Control register B.                                                                                                                               |

| 02h       | VFLG     | 02h/82h             | Vertical blank status and INT reset control. The msb is a read only vertical blank flag.                                                          |

| 03h       | HUE      | 00h                 | Hue control register.                                                                                                                             |

| 04h       | REGC     | 00h                 | Control register C.                                                                                                                               |

| 05h       | REGD     | 25h                 | Control register D.                                                                                                                               |

| 06h       | RESERVED | 07h                 | Reserved.                                                                                                                                         |

| 07h       | REGE     | 00h                 | Control register E.                                                                                                                               |

| 08h – 0fh | RESERVED | -                   | Reserved. Should not be written to.                                                                                                               |

| 10h – ffh | OSDRAM   | _                   | Internally, only bit 4 of the 8-bit index register is decoded. If bit 4 is a 1, data written to the data register (A0 = 1) is sent to the OSDRAM. |

The following is a description of the bits in each register. The default value is followed by an asterisk (\*). Register bits with no specific functions are indicated by a dash (–).

|                                                                                  | Control Register A |      |      |      |       |       |       |      |      |  |

|----------------------------------------------------------------------------------|--------------------|------|------|------|-------|-------|-------|------|------|--|

| Index   Mnemonic   bit 7   bit 6   bit 5   bit 4   bit 3   bit 2   bit 1   bit 0 |                    |      |      |      |       |       |       |      |      |  |

| 00h                                                                              | REGA               | CBW1 | CBW0 | VFIR | CRISP | GAMEN | GAMMA | COR1 | COR0 |  |

COR[1:0] Luma coring selection.

00 No coring.

01 1 LSB coring.\*

10 2 LSB coring.

11 3 LSB coring.

GAMMA Gamma correction selection.

0 Small peaking.\*

1 Large peaking.

GAMEN Luma gamma correction enable.

0 Gamma correction disabled.

1 Gamma correction enabled.\*

CRISP Luma crisper function enable.

O Cripser function is disabled.

1 Crisper function is enabled (recommended for MPEG video).\*

VFIR Vertical filter enable.

0 Vertical filter is disabled.

1 Vertical filter is enabled (recommended for MPEG video).\*

CBW[1:0] Chroma low pass filter bandwidth selection.

00 or 11 Low bandwidth.

01 Medium bandwidth (preferred for most video formats).\*

10 High bandwidth.

Note The default value for this REGA register is 79h.

During normal operation, users are recommended to program this register to 60h.

|       | Control Register B                                                               |     |        |        |        |        |      |      |      |  |

|-------|----------------------------------------------------------------------------------|-----|--------|--------|--------|--------|------|------|------|--|

| Index | Index   Mnemonic   bit 7   bit 6   bit 5   bit 4   bit 3   bit 2   bit 1   bit 0 |     |        |        |        |        |      |      |      |  |

| 01h   | REGB                                                                             | OSD | CHCLR1 | CHCLR0 | BGCLR1 | BGCLR0 | PDEN | FMT1 | FMT0 |  |

FMT[1:0] Encoder output video format selection.

00 NTSC.\*

x1 PAL-B,G,H.

10 Reserved.

PDEN NTSC pedestal insertion.

0 No pedestal (Japan NTSC).

1 Pedestal is inserted.\*

BGCLR[1:0] OSD background color selection.

0x Transparent.\*

10 Blue.

11 Black.

CHCLR[1:0] OSD character color selection.

00 White.\*

01 Cyan.

10 Green.

11 Magenta.

OSD OSD enable.

0 OSD is disabled.\*

1 OSD is enabled.

|       | Vertical Blank Status and INT Reset                   |      |   |   |   |   |   |   |        |  |

|-------|-------------------------------------------------------|------|---|---|---|---|---|---|--------|--|

| Index | IndexMnemonicbit 7bit 6bit 5bit 4bit 3bit 2bit 1bit 0 |      |   |   |   |   |   |   |        |  |

| 02h   | VFLG                                                  | VBLK | - | - | - | - | - | 1 | INTRST |  |

INTRST INT reset control.

0 Leave INT unchanged.\*

1 Force  $\overline{\text{INT}}$  to the high state.

VBLK Vertical blank flag. This is a read only status bit. The state of this bit tracks the state of the

VSYN pin except that this is active high. This bit can be polled by software; when it is high, the

OSD RAM can be updated.

| Hue Control Register |          |       |       |       |       |       |       |       |       |  |  |

|----------------------|----------|-------|-------|-------|-------|-------|-------|-------|-------|--|--|

| Index                | Mnemonic | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |  |  |

| 03h                  | HUE      | HUE7  | HUE6  | HUE5  | HUE4  | HUE3  | HUE2  | HUE1  | HUE0  |  |  |

HUE[7:0] Hue adjust. This number is unsigned. The nominal value is 0. The hue can be adjusted at a resolution of 1.40625 degrees.

| Control Register C |          |       |       |       |       |       |       |       |       |  |

|--------------------|----------|-------|-------|-------|-------|-------|-------|-------|-------|--|

| Index              | Mnemonic | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |  |

| 04h                | REGC     | VFM   | _     | _     | CKOSL | INFMT | MODE  | _     | _     |  |

MODE Master/slave timing mode selection.

0 Slave mode.\*

1 Master mode.

INFMT Digital video input format selection.

0 Input is CCIR 601.\*

1 Input is CCIR 656.

CKOSL CKO clock output frequency selection.

0 CKO frequency is 13.5 MHz.\*

1 CKO frequency is 27 MHz. This selection is not available if CKI27 is the clock input.

VFM Vertical filter mode selection.

Only even field is interpolated.\*

1 Both fields are interpolated.

| Control Register D |          |       |       |        |       |       |       |       |       |  |

|--------------------|----------|-------|-------|--------|-------|-------|-------|-------|-------|--|

| Index              | Mnemonic | bit 7 | bit 6 | bit 5  | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |  |

| 05h                | REGD     | _     | YCEN  | CVBSEN | _     | _     | HAV2  | HAV1  | HAV0  |  |

HAV[2:0]

Master mode active video start control. The KSO125 expects the first active pixel to be 122 13.5 MHz clocks after the leading edge of the HSYN (for PAL, the number is 132). The following offset, in number of 27 MHz clocks, provides additional phase shifts to compensate for any external data latency. **SHFHAV** is bit 4 of **REGE**.

000 +11+SHFHAV. 001 +9+SHFHAV. 010 +7+SHFHAV. +5+SHFHAV. 011 +3+SHFHAV. 100 +1+SHFHAV.\* 101 110 -1+SHFHAV. 111 -3+SHFHAV.

**CVBSEN**

CVBS DAC control.

CVBS DAC is disabled.

1 CVBS DAC is enabled.\*

YCEN LUMA and CHROMA DACs control.

0 LUMA and CHROMA DACs are disabled.\*

1 LUMA and CHROMA DACs are enabled.

| Control Register E |          |       |       |       |        |       |       |       |       |  |  |

|--------------------|----------|-------|-------|-------|--------|-------|-------|-------|-------|--|--|

| Index              | Mnemonic | bit 7 | bit 6 | bit 5 | bit 4  | bit 3 | bit 2 | bit 1 | bit 0 |  |  |

| 07h                | REGE     | _     | _     | _     | SHFHAV | EAV   | FLD   | YCDLY | CKILL |  |  |

CKILL Color kill.

0 Enable color.\*

1 Force output to be black and white. Color burst is still inserted.

YCDLY Luma path data delay control.

0 No delay.\*

1 One 27 MHz clock delay.

FLD Field identification in slave mode.

0 Use VSYN and HSYN for field identification.\*

1 Use ODD input.

EAV Slave mode synchronization selection.

0 Use HSYN, VSYN or ODD inputs for synchronization.\*

1 Use EAV for synchronization.

SHFHAV One additional 27 MHz clock phase shift for the start of active pixel in master mode

0 No shift.\*

1 One 27 MHz clock shift.

## **ABSOLUTE MAXIMUM RATINGS**

| Characteristics                                                  | Symbol           | Value                          | Units |

|------------------------------------------------------------------|------------------|--------------------------------|-------|

| Supply voltage (measured to VSS)                                 | $V_{DD}$         | -0.5 to + 7.0                  | V     |

| Analog and digital supply voltage difference                     | $\Delta V_{AD}$  | -0.7 to +0.7                   | V     |

| Digital input applied voltage <sup>(2)</sup> (measured to VSS)   | Vi               | -0.5                           | V     |

| Digital input forced current <sup>(3,4)</sup>                    | A <sub>i</sub>   | -100 to +100                   | mA    |

| Digital output applied voltage <sup>(2)</sup> (measured to VSS)  | V <sub>o</sub>   | -0.5 to (V <sub>DD</sub> +0.5) | V     |

| Digital output forced current <sup>(3,4)</sup>                   | A <sub>o</sub>   | -100 to +100                   | mA    |

| Digital short circuit duration (single output high state to VSS) | TDsc             | 1                              | sec   |

| Analog short circuit duration (single output to VSS)             | TA <sub>SC</sub> | infinite                       |       |

| Ambient operating temperature (case)                             | T <sub>A</sub>   | -60 to + 130                   | °C    |

| Storage temperature                                              | T <sub>S</sub>   | -65 to + 150                   | °C    |

| Junction temperature                                             | TJ               | -65 to +150                    | °C    |

| Vapor phase soldering (1 min.)                                   | Tvsol            | 220                            | °C    |

| Lead Soldering Temperature (10 sec., 1/4© from pin)              | Tsol             | 300                            | °C    |

#### NOTES:

- 1. .Absolute maximum ratings are limiting values applied individually, while all other parameters are within specified operating conditions.

- 2. Applied voltage must be current limited to the specified range, and measured with respect to VSS.

- 3. Forcing voltage must be limited to the specified range.

- 4. Current is specified as a conventional current, flowing into the device.

## **RECOMMENDED OPERATING CONDITIONS**

| Characteristics                          | Symbol           | Min  | Тур   | Max  | Units |

|------------------------------------------|------------------|------|-------|------|-------|

| Supply voltage (measured to VSS)         | V <sub>DD</sub>  | 4.75 | 5.0   | 5.25 | V     |

| Reference voltage                        | V <sub>ref</sub> | _    | 1.235 | _    | V     |

| Reference current                        | I <sub>ref</sub> | _    | 1.569 | _    | mA    |

| Analog output load                       | R <sub>L</sub>   | _    | 75    | _    | W     |

| Ambient operating temperature, still air | T <sub>A</sub>   | 0    | _     | 70   | °C    |

# **ELECTRICAL CHRACTERISTICS**

| Characteristics                                                | Symbol             | Min             | Тур   | Max             | Units |

|----------------------------------------------------------------|--------------------|-----------------|-------|-----------------|-------|

| SUPPLY                                                         |                    |                 |       |                 |       |

| Total power supply current (digital plus analog, CKIN=27MHz.)  | I <sub>DD</sub>    | -               | _     | 200             | mA    |

| DIGITAL-TO-ANALOG CONVERTER                                    |                    |                 |       |                 |       |

| DAC resolution                                                 | RES                | 10              | _     | _               | bits  |

| Voltage reference (VREF) output                                | $V_{REF}$          | 1.110           | 1.235 | 1.360           | V     |

| DAC gain factor                                                | K <sub>DAC</sub>   | 10.31           | 10.85 | 11.39           | _     |

| K <sub>DAC</sub> imbalance between DACs                        | K <sub>IMBAC</sub> | -5%             | _     | +5%             | _     |

| DAC reference current (V <sub>REF</sub> =nominal)              | I <sub>REF</sub>   | _               | 1.569 |                 | mA    |

| Reference resistor (V <sub>REF</sub> =nominal)                 | R <sub>REF</sub>   | -               | 787   | _               | Ω     |

| Blanking level output voltage (NTSC and PAL modes)             | V <sub>BLANK</sub> | -               | 0.300 | _               | V     |

| Video output compliance voltage                                | V <sub>OC</sub>    | -0.3            | _     | 1.6             | V     |

| Total output load resistance                                   | R <sub>L</sub>     | _               | 75    |                 | Ω     |

| Analog output delay                                            | T <sub>dly</sub>   | -               | 32    | -               | ns    |

| DIGITAL I/O CHARACTERISTICS                                    |                    |                 |       |                 |       |

| Digital input voltage, logic HIGH, TTL compatible inputs.      | V <sub>IH</sub>    | 2.5             | _     | V <sub>DD</sub> | V     |

| Digital input voltage, logic LOW, TTL compatible inputs        | V <sub>IL</sub>    | V <sub>SS</sub> | _     | 0.6             | V     |

| Digital input current, logic HIGH (V <sub>IN</sub> =4.0 V)     | I <sub>IH</sub>    |                 | -     | 10              | μΑ    |

| Digital input current, logic LOW (V <sub>IN</sub> =0.4 V)      | I <sub>IL</sub>    |                 | _     | -10             | μΑ    |

| Digital output voltage, logic HIGH (I <sub>OH</sub> = - 400μA) | V <sub>OH</sub>    | 2.4             | _     | V <sub>DD</sub> | V     |

| Digital output voltage, logic LOW ( $I_{OL}$ =3.2 mA)          | V <sub>OL</sub>    | V <sub>SS</sub> | _     | 0.4             | V     |

| DIGITAL VIDEO PORT TIMING                                      |                    |                 |       |                 |       |

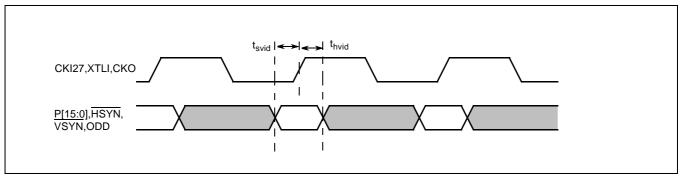

| Digital video input setup time to rising edge of pixel clock   | t <sub>svid</sub>  | 5               | _     | _               | ns    |

| Digital video input hold time from rising edge of pixel clock  | t <sub>hvid</sub>  | 5               | _     | _               | ns    |

| CKI27 frequency variation*                                     | $\Delta_{CKI27}$   | -               | _     | 50              | ppm   |

| XTLI frequency variation*                                      | $\Delta_{XTLI}$    | _               | _     | 50              | ppm   |

| Clock duty cycle (CKI27, XTLI)*                                | δ                  | 40%             | 50%   | 60%             | _     |

# **ELECTRICAL CHRACTERISTICS (Continued)**

| Characteristics                                                  | Symbol                | Min | Тур | Max | Units            |

|------------------------------------------------------------------|-----------------------|-----|-----|-----|------------------|

| Pipeline delay from P[15:0] input to DAC input*                  | t <sub>PD</sub>       | -   | 41  | -   | 27MHz<br>periods |

| Clock input-to-output (CKI27 or XTLI to CKO) delay (65 pF load)* | t <sub>dlyCLK</sub>   | -   | _   | 12  | ns               |

| Clock doubler short/long term jitter                             | $\delta_{CKdbl}$      | _   | _   | ±1  | ns               |

| HOST INTERFACE TIMING                                            |                       |     |     |     |                  |

| CS low                                                           | t <sub>pwl</sub> cs   | 148 | _   | _   | ns               |

| CS high                                                          | t <sub>pwh</sub> CS   | 296 | -   | _   | ns               |

| R/W setup time to falling edge of CS                             | t <sub>sR/W</sub>     | 8   | -   | _   | ns               |

| R/W hold time from rising edge of CS                             | t <sub>hR/W</sub>     | 222 | -   | _   | ns               |

| A0 setup time to falling edge of CS                              | t <sub>sA</sub>       | 8   | -   | _   | ns               |

| A0 hold time from falling edge of CS                             | t <sub>hA</sub>       | 8   | -   | _   | ns               |

| Write mode data setup time to rising edge of CS                  | t <sub>sD</sub>       | 8   | _   | _   | ns               |

| Write mode data hold time from rising edge of CS                 | t <sub>hD</sub>       | 8   | _   | _   | ns               |

| Read mode delay from falling edge of CS To data valid            | t <sub>validD</sub>   | _   | _   | 75  | ns               |

| Read mode delay from rising edge of CS to data 3-state           | t <sub>3-stateD</sub> | _   | _   | 10  | ns               |

<sup>\*:</sup> These parameters are guaranteed by by design.

Figure 18. Video Port Data Setup and Hold Time

Figure 19. CKI27 to CKO Delay

Figure 20. XTLI to CKO Delay

Figure 21. Write Protocol for the Host Interface

Figure 22. Read Protocol for the Host Interface

## **VIDEO PERFORMANCE**

The KS0125 encoder meets the requirements listed in the table below when configured using the application circuit of Figure 15. The test methods and test signals meets the requirements of NTC Report No. 7or EIA/TIA-250. A Tektronix TSG1001 Programmable TV Generator and a Tektronix VM700A Video Measurement Set are used for measurement verification.

#### **Video Performance Characteristics**

| Test Name                                                   | Symbol  | Test Waveform                                           | Min | Тур   | Max | Unit               |

|-------------------------------------------------------------|---------|---------------------------------------------------------|-----|-------|-----|--------------------|

| Amplitude response versus frequency                         | AMPRESP | Multiburst to 4.2 MHz                                   | -   | 0.25  | _   | dB <sub>p-p</sub>  |

| Differential gain                                           | DG      | Modulated staircase or ramp (NTC-7 composite)           | _   | 1.5   | _   | % <sub>p-p</sub>   |

| Differential phase                                          | DP      | Modulated staircase or ramp (NTC-7 composite)           | -   | 1.0   | _   | deg <sub>p-p</sub> |

| Chroma nonlinear gain distortion                            | CNLG    | Three-level chroma signal (NTC-7 combination)           | _   | 1.0   | _   | IRE                |

| Chroma nonlinear phase distortion                           | CNLP    | Three-level chroma signal (NTC-7 combination)           | -   | 1.0   | _   | deg                |

| Chroma-to-luma intermodulation                              | CLIMD   | Three-level chroma signal (NTC-7 Combination)           | _   | 1     | _   | IRE                |

| Chroma/luma gain equality                                   | CLGI    | 12.5T modulated pulse<br>(NTC-7 composite)<br>YCDLY=LOW | -   | 102.5 | _   | %                  |

| Chroma/luma delay inequality (analog filter delay excluded) | CLDI    | 12.5T modulated pulse<br>(NTC-7 Composite)<br>YCDLY=LOW | -   | 5     | _   | ns                 |

| Luma nonlinear distortion                                   | LNLD    | 5-step unmodulated staircase                            | _   | 2.5   | _   | %                  |

| Noise level                                                 | NOISE1  | 100% unmodulated ramp                                   | _   | -61   | _   | dB <sub>rms</sub>  |

| Noise level                                                 | NOISE2  | 100% unmodulated ramp                                   | -   | -72   | _   | dB <sub>rms</sub>  |

| Chroma AM noise                                             | CAMN    | Red field, 500kHz bandwidth                             | _   | -56   | _   | dB <sub>rms</sub>  |

| Chroma PM noise                                             | CPMN    | Red field, 500kHz bandwidth                             | _   | -58   | -   | dB <sub>rms</sub>  |

| Field time waveform distortion                              | FTWD    | Field square wave                                       | _   | 1.5   | _   | IRE <sub>p-p</sub> |

| Line time waveform distortion                               | LTWD    | 18 μs 100 IRE bar (NTC-7 composite)                     | _   | 0.5   | _   | IRE <sub>p-p</sub> |

| Long time waveform distortion:                              | LOTWD   | 10% / 90% APL bounce                                    |     |       |     |                    |

| initial peak overshoot                                      |         |                                                         |     | 15    |     | IRE                |

| peak overshoot after 5 seconds                              |         |                                                         |     | 1.5   |     | IRE                |