SEMICONDUCTOR IM

# FAN8402D (KA3081D) 3-Phase BLDC Motor Driver

### Features

- Commutation FG, PG is executed by 1-hall

- Soft switching at output terminal reduces switching impulse.

- 3-phase full wave BLDC motor driver.

- Voltage reference (Uses band gap circuit)

- Built-in thermal shut-down (TSD) circuit

# Description

FAN8402D is a bipolar integrated circuit used to drive 3phase brushless DC motor in full wave mode using 1-hall sensor. FAN8402D uses 1-hall for commutation and PG generation. It is a special circuit for soft switching using 1-hall reduces the EMI and eliminates snubber. The FG is generated by BEMF.

# **Typical Applications**

- Video Cassette recorder (VCR) cylinder (drum) motor

- Other 3-phase BLDC motor

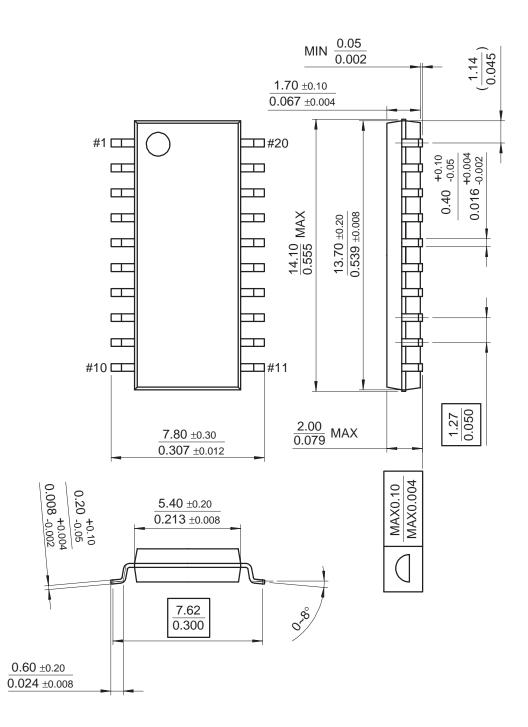

### **Ordering Information**

| Device     | Package    | Operating Temp. |

|------------|------------|-----------------|

| FAN8402D   | 20-SOP-300 | –25°C ~ +75°C   |

| FAN8402DTF | 20-SOP-300 | –25°C ~ +75°C   |

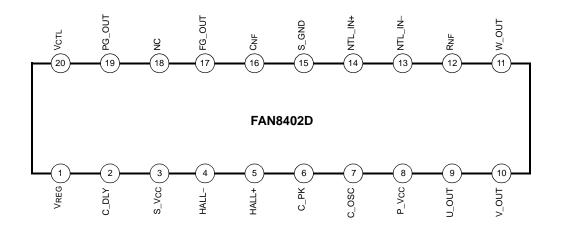

# **Pin Assignments**

### **Pin Definitions**

| Pin Number | Pin Name | Pin Function Description                         |

|------------|----------|--------------------------------------------------|

| 1          | Vreg     | Regurator output                                 |

| 2          | C_DLY    | PG. delay                                        |

| 3          | S_VCC    | Signal VCC                                       |

| 4          | HALL-    | Hall- input                                      |

| 5          | HALL+    | Hall+ input                                      |

| 6          | C_PK     | Peak detector of hall signal                     |

| 7          | C_OSC    | Start-up oscillator                              |

| 8          | P_VCC    | Power VCC                                        |

| 9          | U_OUT    | U-phase output                                   |

| 10         | V_OUT    | V-phase output                                   |

| 11         | W_OUT    | W-phase output                                   |

| 12         | RNF      | Output current sensing                           |

| 13         | NTL_IN-  | Input from the neutral point of the motor coils. |

| 14         | NTL_IN+  | Input from the neutral point of the motor coils. |

| 15         | S_GND    | Signal ground                                    |

| 16         | CNF      | Phase compensation                               |

| 17         | FG_OUT   | FG. output                                       |

| 18         | NC       | -                                                |

| 19         | PG_OUT   | PG. output                                       |

| 20         | VCTL     | Output current control                           |

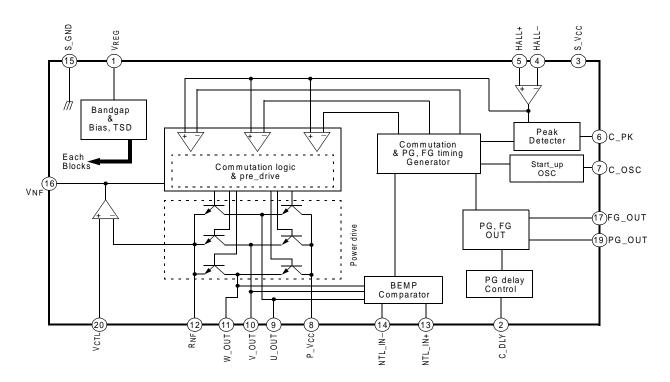

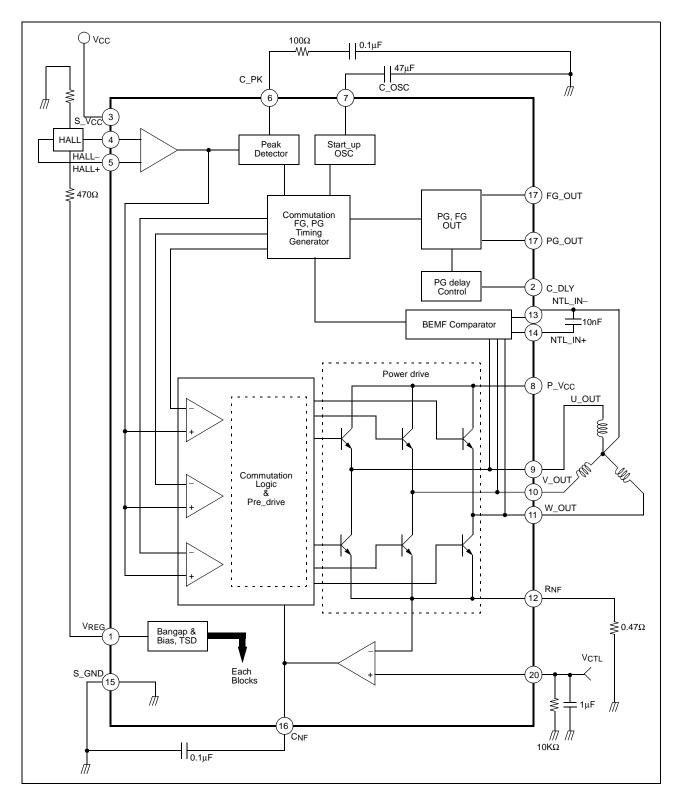

# **Internal Block Diagram**

# Equivalent Circuits

| Description                   | Pin No.         | Internal circuit                                                                                                      |

|-------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------|

| Hall input                    | 5,4             |                                                                                                                       |

| Output &<br>Current detection | 9,10,11<br>8,12 | (1) w_OUT<br>(1) w_OUT<br>(1) w_OUT<br>(1) w_OUT<br>(1) w_OUT<br>(1) w_OUT<br>(1) (1) (1) (1) (1) (1) (1) (1) (1) (1) |

| FG Output                     | 17              | VREG VCC                                                                                                              |

| PG Output                     | 19              | VREG VCC                                                                                                              |

# Equivalent Circuits (Continued)

| Description                  | Pin No. | Internal circuit |  |

|------------------------------|---------|------------------|--|

| Voltage control<br>reference | 20      |                  |  |

|                              |         |                  |  |

# Absolute Maximum Ratings (Ta=25°C)

| Parameter                | Symbol  | Value                | Unit      | Remark                   |

|--------------------------|---------|----------------------|-----------|--------------------------|

| Supply voltage (Signal)  | VCCmax  | 20                   | V         | -                        |

| Maxium Output current    | lOmax   | 1.0 <sup>note1</sup> | A / Phase |                          |

| Regulator output current | IREGmax | 10                   | mA        |                          |

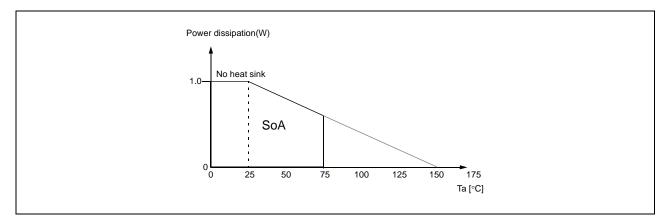

| Power dissipation        | Pd      | 1.0 <sup>note2</sup> | W         | No heat sink             |

| Junction temperature     | TJ      | 150                  | °C        | -                        |

| Operating temperature    | TOPR    | -20 ~ +75            | °C        | Ambient temperature (Ta) |

| Storage temperature      | TSTG    | -40 ~ +155           | °C        |                          |

#### NOTES:

1. Duty 1 / 100, pulse width  $500\mu s$

2. 1) When mounted on glass epoxy PCB ( $76.2 \times 114 \times 1.57$ mm)

2) Power dissipation reduces 9.6mW / °C for using above Ta=25°C.

3) Do not exceed Pd and SOA(Safe Operating Area).

### **Power Dissipation Curve**

# **Recommened Operating Conditions (Ta=25°C)**

| Parameter                        | Symbol | Min. | Тур. | Max | Unit |

|----------------------------------|--------|------|------|-----|------|

| Operating supply voltage(Signal) | S_VCC  | 4.5  | 5.0  | 5.5 | V    |

| Operating supply voltage(Power)  | P_Vcc  | 8    | 12   | 18  | V    |

# **Electrical Characteristics**

(Measured in test circuit, P\_V<sub>CC</sub>=12V, Ta=25°C)

| Parameter                           | Symbol         | Conditions                                                              | Min. | Тур. | max. | Unit  |

|-------------------------------------|----------------|-------------------------------------------------------------------------|------|------|------|-------|

| TOTAL                               | 1              |                                                                         |      |      | •    |       |

| Supply voltage                      | Vcc            | -                                                                       | 8.0  | -    | 18   | V     |

| Supply current (1)                  | ICC1           | P_V <sub>CC</sub> =12V, V <sub>REG</sub> =open,<br>V <sub>CTL</sub> =0V | -    | 11.2 | 17   | mA    |

| Supply current (2)                  | ICC2           | P_V <sub>CC</sub> =12V, V <sub>REG</sub> =open,<br>V <sub>CTL</sub> =0V | -    | 11.5 | 17   | mA    |

| REGURATOR                           |                |                                                                         |      |      |      | •     |

| VREG output voltage (2)             | VREG2          | P_VCC=12V, IREG=0mA                                                     | 4.7  | 5.0  | 5.3  | V     |

| VREG output voltage (5)             | VREG5          | P_VCC=12V, IREG=10mA                                                    | 4.7  | 5.0  | 5.3  | V     |

| START-UP OSCILLATOR                 |                |                                                                         |      |      |      | •     |

| C_OSC operation frequency           | OSC_FEQ        | C_OSC=47nF                                                              | 6    | 8    | 10   | Hz    |

| C_OSC charging current              | OSC_ICH        | C_OSC=47nF                                                              | -0.5 | -2   | -3.5 | μA    |

| C_OSC discharging current           | OSC_IDC        | C_OSC=47nF                                                              | 1    | 3    | 5    | μA    |

| C_OSC low threshold voltage         | OSC_THL        | C_OSC=47nF                                                              | 0.2  | 0.5  | 0.8  | V     |

| C_OSC high threshold voltage        | OSC_THH        | C_OSC=47nF                                                              | 2.7  | 3.0  | 3.3  | V     |

| VOLTAGE CONTROL                     |                |                                                                         |      |      | •    | •     |

| VCTL start voltage                  | VCTL_ST        | VCTL=0~2V When IO=25mA                                                  | 1.01 | 1.26 | 1.51 | V     |

| VCTL input voltage range            | VCTL_IN        | VREG                                                                    | 0    | -    | VREF | V     |

| VCTL input bias current             | VCTL_BI        | VCTL=2.0V                                                               | -    | 1.0  | 1.5  | μΑ    |

| Gain                                | GM             | R <sub>NF</sub> =0.47Ω, V <sub>CTL</sub> =0~2V                          | 0.38 | 0.45 | 0.52 | А     |

| HALL INPUT                          |                |                                                                         |      |      | •    | •     |

| Input hall signal Min. voltage note | VH_MIN         |                                                                         | 300  | -    | -    | mVp-p |

| PG hall 1'st Min. voltage note      | VH_P1          |                                                                         | 60   | -    | -    | mVo-p |

| PG hall 2'nd Min. voltage note      | VH_P2          |                                                                         | 55   | -    | -    | mVo-p |

| PG hall 3'rd Min. voltage note      | VH_P3          | 1st 3rd                                                                 | 75   | -    | -    | mVo-p |

| PG hall 1'st-2'nd level note        | $\Delta V_{H}$ | 2nd                                                                     | 5    | -    | -    | mVo-p |

| FG (FREQUENCY GENERATOR             | ), PG (PHAS    | E GENERATOR)                                                            |      |      | 1    |       |

| FG, PG high level                   | FG_PG_H        | -                                                                       | 4.5  | -    | -    | V     |

| FG, PG low level                    | FG_PG_L        | -                                                                       | -    | -    | 0.5  | V     |

### Notes:

The note in the chart means items calculated and approved in design not the items proven by actual test results.

### **Electrical Characteristics (Continued)**

(Measured in test circuit, P\_V<sub>CC</sub>=12V, Ta=25°C)

| Parameter                         | Symbol   | Conditions                        | Min. | Тур. | max. | Unit |  |

|-----------------------------------|----------|-----------------------------------|------|------|------|------|--|

| TSD                               |          |                                   |      |      |      |      |  |

| Temp. threshold note              | TSD_T    | -                                 | 130  | 150  | -    | °C   |  |

| Temp. hysteresis <sup>note</sup>  | TSD_H    | -                                 | 20   | 30   | -    | °C   |  |

| OUTPUT                            |          |                                   |      |      |      |      |  |

| Output saturation voltage (Upper) | VSU1     | VCTL=4V, IO=600mA,                | -    | 1.0  | 1.5  | V    |  |

| Output saturation voltage (Under) | VSD1     | $RNF=0.47\Omega, RL=10\Omega$     | -    | 0.4  | 0.7  | V    |  |

| NTL_IN- input voltage range       | VNTL_IN- | -                                 | 0    | -    | Vcc  | V    |  |

| C <sub>NF</sub> voltage           | VCNF     | V <sub>CTL</sub> =2V              | 1    | -    | -    | V    |  |

| C_PK frequency                    | CPK_FRQ  | C_PK=100Ω + 0.1μF                 | 0.8  | 1    | 1.2  | kHz  |  |

| C_CK voltage level                | CPK_V    | C_PK=100Ω + 0.1μF<br>HALL- =0.25V | 0.4  | -    | -    | Vр-р |  |

| C_DLY                             |          |                                   |      |      |      |      |  |

| C_DLY charging current            | IC_DLY   | C_DLY=4nF                         | -20  | -30  | -40  | μA   |  |

#### Notes:

The note in the chart means items calculated and approved in design not the items proven by actual test results.

# **Application Information**

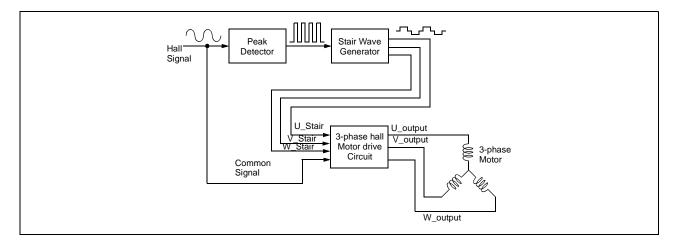

### 1. SYSTEM BLOCK DIAGRAM

The figure 1 shows concept of soft switching for 3-phase output with a hall sensor.

Figure 1.

- Peak detector Generates clock pulses at the peak points of the hall signal.

- Stair wave generator

- Generates 3 stair wave signals 120 degree apart from the clock pulses.

- 3-phase motor drive circuit Controls output currents to operate 3-phase motor using the vol

- tage difference between the 3 stair wave signals and FG hall signal.

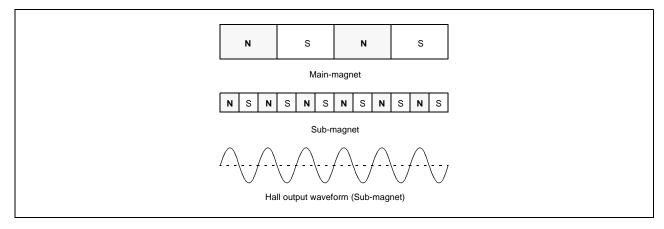

### 2. STRUCTURE OF BLDC MOTOR

Consists of main and sub magnets. For every main magnet there are 3 submagnets as shown in Fig 2. Sub-magnet takes hall signal and goes through 6 gradual filtering steps purifying in order to operate 3-phase motor with one

Sub-magnet takes hall signal and goes through 6 gradual filtering steps purifying in order to operate 3-phase motor with o hall sensor.

Figure 2.

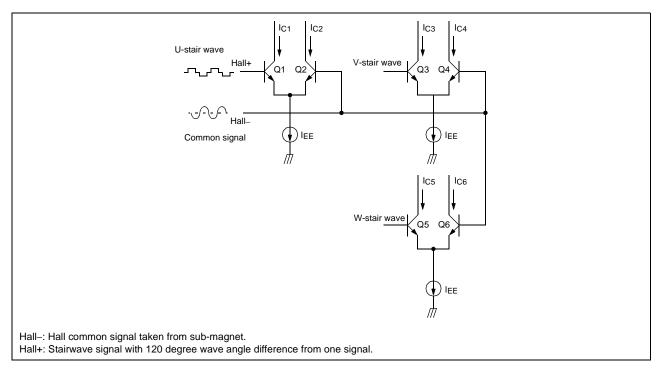

### 3. PRINCIPLE OF OPERATION

Input circuit of 3-phase motor drive with soft-switching function is shown as the figure 3.

Figure 3.

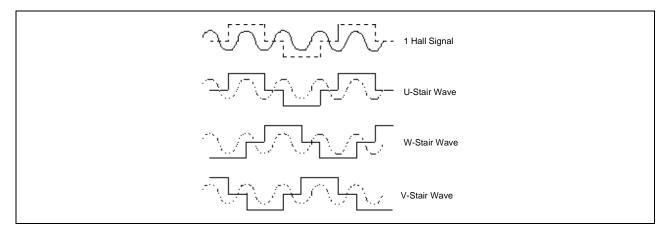

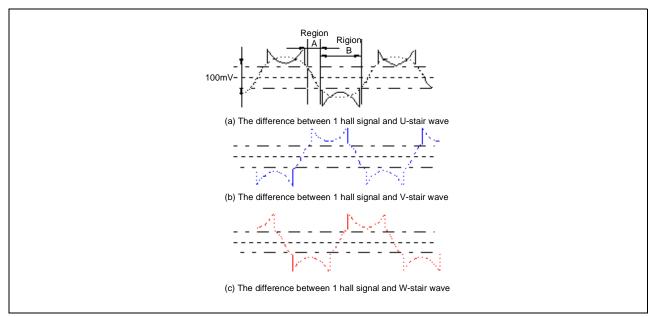

Next the figure 4 shows common signal (Hall signal) and each individual stairwave at its own position.

Figure 4.

Figure 5 shows hall signal and stairwave signal position.

The section where the difference between hall signal and stairwave is within 100mV.

Figure 5.

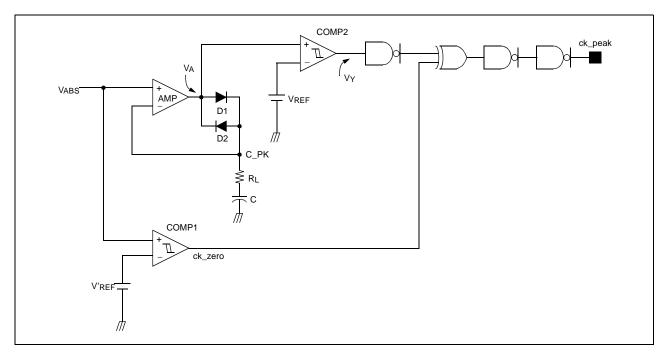

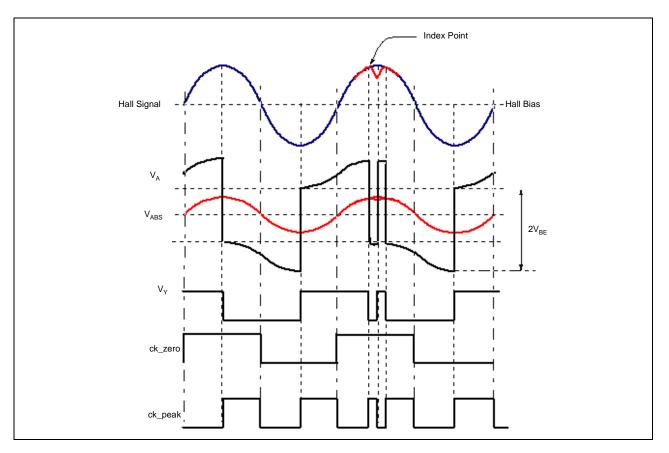

#### 4. PEAK DETECTOR

Hall signals and stairwave signals made from peak detectors's output rotate the motor. The peak detector circuit is shown in Fig 6.

#### Figure 6.

VABS in the figure 6 is a signal from twice amplified hall signal and hall bias at 2.5 volt as standard voltage as you see in the figure 7.

Figure 7.

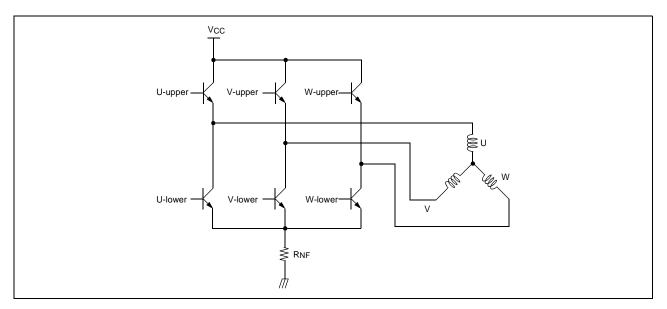

### 5. DRIVE OUTPUT

Figure 8.

The figure 8 shows the 3-phases of the BLDC motor.

The upper power TRs in output group operate in linear area and the lower group work in saturation area.

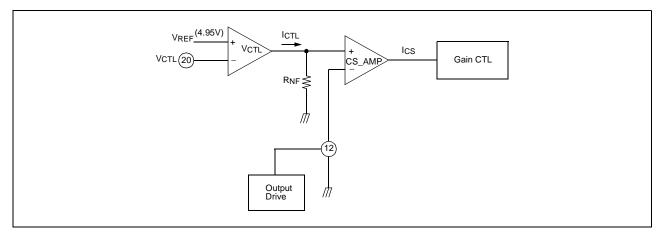

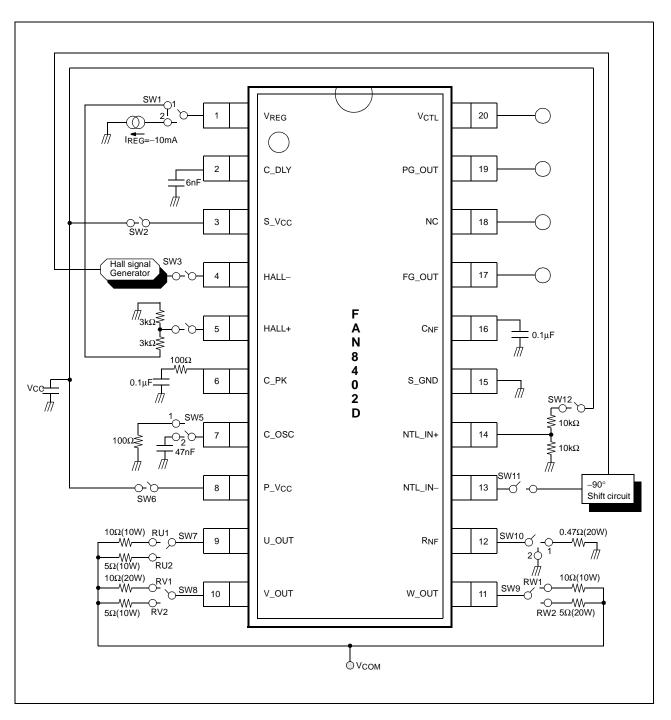

### 6. VOLTAGE CONTROL & CURRENT SENSING

The circuit in the figure 9 outputs ICTL current when VCTL (Control voltage from servo) is larger than the value of VREF. The V-I characteristic of this circuit is shown in the figure 10.

The CS-AMP terminal amplifies by getting inputs from output terminal getting ICTL and RNF voltages. RNF resistance feedbacks the current in output terminal.

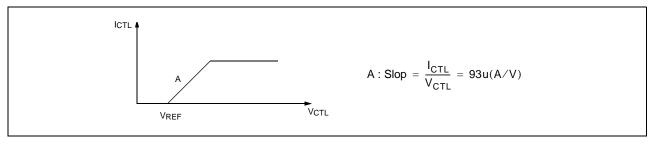

# **Timing Chart**

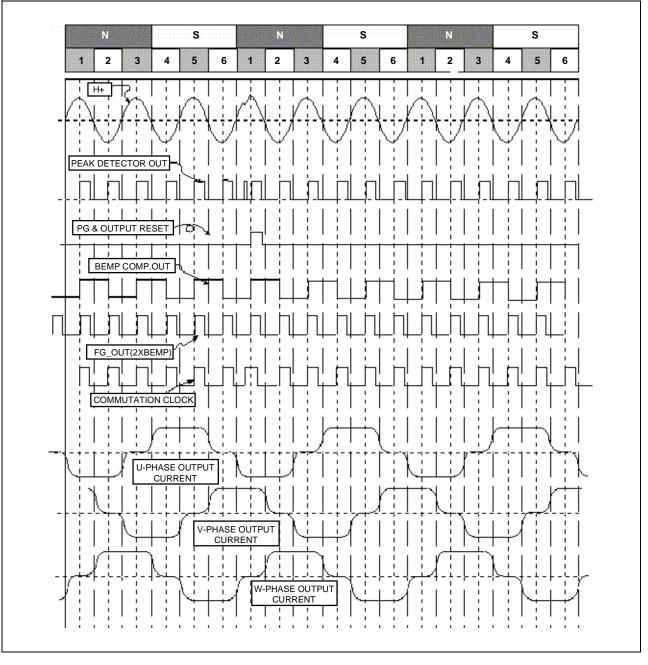

### **Test Circuits**

# **Typical Application Circuits**

#### TRADEMARKS

The following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is not intended to be an exhaustive list of all such trademarks.

ACEx™ Bottomless™ CoolFET™ CROSSVOLT™ DOME™ E<sup>2</sup>CMOS<sup>™</sup> EnSigna™ FACT™ FACT Quiet Series™ **FAST<sup>®</sup>**

FASTr™ GlobalOptoisolator™ GTO™ HiSeC™ **ISOPLANAR™** MICROWIRE™ **OPTOLOGIC**<sup>™</sup> OPTOPLANAR™ POP™ PowerTrench<sup>®</sup>

QFET™ QS™ QT Optoelectronics<sup>™</sup> Quiet Series™ SuperSOT™-3 SuperSOT™-6 SuperSOT<sup>™</sup>-8 SyncFET™ TinyLogic™ UHC™

VCX™

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, or (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.

2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### PRODUCT STATUS DEFINITIONS

**Definition of Terms**

| Datasheet Identification | Product Status            | Definition                                                                                                                                                                                                                        |

|--------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advance Information      | Formative or<br>In Design | This datasheet contains the design specifications for<br>product development. Specifications may change in<br>any manner without notice.                                                                                          |

| Preliminary              | First Production          | This datasheet contains preliminary data, and<br>supplementary data will be published at a later date.<br>Fairchild Semiconductor reserves the right to make<br>changes at any time without notice in order to improve<br>design. |

| No Identification Needed | Full Production           | This datasheet contains final specifications. Fairchild<br>Semiconductor reserves the right to make changes at<br>any time without notice in order to improve design.                                                             |

| Obsolete                 | Not In Production         | This datasheet contains specifications on a product<br>that has been discontinued by Fairchild semiconductor.<br>The datasheet is printed for reference information only.                                                         |

|                          | •                         | Rev. F1                                                                                                                                                                                                                           |