# HY6716100/101 64K x 16 Bit SYNCHRONOUS CMOS SRAM

PRELIMINARY

269

#### DESCRIPTION

This device integrates high-speed 64Kx16 SRAM core, address registers, data input registers, a 2-bit burst address counter and pipelined output. All synchronous inputs pass through registers controlled by a positive-edge triggered clock(K).

The device is ideally suited for 486/Pentium system by including all necessary timing and control logic on a chip. Any external address latches, counters, or other timing and control logic are not necessary.

#### **FEATURES**

- Single 5V±5% power supply

- 6ns/9ns/12ns access times from clock Support up to 75MHz System Operation

- Optimized for use with Intel 486/Pentium secondary cache applications (Interleaved burst sequence and Linear burst sequence)

- Registered data-out for pipelined read

- Byte writable using seperate upper/lower byte write input controls

- Write Pass-through functionality

- On-chip burst address counter

- · On-chip clocked input and output registers

- 3-state buffered output with asynchronous output enable control

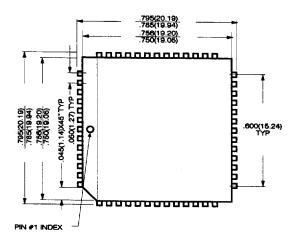

- Standard 52-lead PLCC package with JEDEC pinout

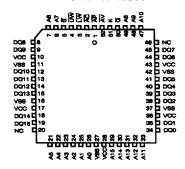

## PIN CONNECTION

### PART NUMBER EXAMPLES

| Part No.  | Burst Sequence |

|-----------|----------------|

| HY6716100 | Interleaved    |

| HY6716101 | Linear         |

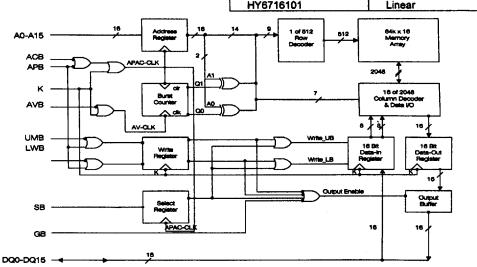

# **FUNCTION BLOCK DIAGRAM**

This document is a general product description and is subject to change without notice. Hyundai Electronics does not assume any responsibility for use of circuits described. No patent licences are implied. 1DH05-11-MAY95

4675088 0006280 lot **=**

# PIN DESCRIPTIONS

| SYMBOL      | PIN NUMBER                                                         | TYPE             | DESCRIPTION                                                                                                                                                                                                                                                                                                                                            |

|-------------|--------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| К           | 51                                                                 | Input            | Clock.  This signal is used to synchronize the device with the system timing. It registers the Addresses, Data inputs, Byte Write Enables and Chip Enable. It may clear or increment the burst counter depending on the state of APB, ACB and AVB.                                                                                                     |

| A0-An       | 6, 7, 21, 22, 23, 24,<br>25, 26, 29, 30, 31,<br>32, 33, 47, 48, 49 | Input            | Synchronous Address.  The addresses are registered at rising edge of the clock.                                                                                                                                                                                                                                                                        |

| SB          | 5                                                                  | Input            | Chip Select. A synchronous control input used to enable(LOW state) and disable(HIGH state) the device. This input is sampled and registered only when a new base address cycle is initiated.                                                                                                                                                           |

| UWB/<br>LWB | 3, 4                                                               | Input            | Upper and Lower Byte Write Enable.  Synchronous control input registered by rising edge of the clock. A  LOW state allows data to be written into the device, and a HIGH  state initiates a read cycle. UWB controls upper byte(DQ8-15) and  LWB controls lower byte(DQ0-7).                                                                           |

| АРВ         | 1                                                                  | Input            | Address Status from Processor.  A synchronous control input registered by rising edge of the clock.  A LOW state interrupts the burst sequence and loads in a new address. The device will read out the data at new address. This input over-rides ACB and UWB/LWB.                                                                                    |

| ACB         | 2                                                                  | Input            | Address Status from Cache Controller.  A synchronous control input registered by rising edge of the clock.  When this input is at LOW state and APB is HIGH state, burst sequence is interrupted and new addresses are loaded into the device. The device will perform a read or write cycle with new addresses.                                       |

| AVB         | 52                                                                 | Input            | Burst Address Advance. A synchronous control input registered by rising edge of the clock. When this input is at LOW state, the burst counter increments at rising clock edge. A HIGH state will insert wait states into the burst sequence. The burst addresses will wrap around to the initial state after burst counter completed a burst sequence. |

| GB          | 50                                                                 | Input            | Output Enable. An asynchronous control input. A LOW state will enable the DQs and a HIGH state will tri-state the DQs.                                                                                                                                                                                                                                 |

| DQ0-n       | 8, 9, 12, 13, 14, 15,<br>18, 19, 34, 35, 38,<br>39, 40, 41, 44, 45 | Input/<br>Output | Data Input/Outputs.  A bi-directional common I/O data pins. GB controls the pins when the device is outputting the data(read cycle). At write cycle, input data are registered at rising edge of the clock.                                                                                                                                            |

| Vcc         | 28                                                                 | Supply           | Positive Power Supply:+5.0V±5%                                                                                                                                                                                                                                                                                                                         |

| Vss         | 27                                                                 | Supply           | Negative Power Supply and Ground Return.                                                                                                                                                                                                                                                                                                               |

| Vccq        | 10, 17, 36, 43                                                     | Supply           | Isolated Output Buffer Supply:+5.0V±5%                                                                                                                                                                                                                                                                                                                 |

| Vssq        | 11, 16, 37, 42                                                     | Supply           | Isolated Output Buffer Ground:GND                                                                                                                                                                                                                                                                                                                      |

| NC          | 20, 46                                                             | Supply           | No Connection                                                                                                                                                                                                                                                                                                                                          |

|     | 4675088 | 0006597 | 046 |               |

|-----|---------|---------|-----|---------------|

| 270 |         |         |     | 4DUGE 44 MAYO |

## TRUTH TABLE

| OPERATION                                                                | ADD. | SB | LWB | UWB | APB | ACB | AVB | K   | GB | DQ   |

|--------------------------------------------------------------------------|------|----|-----|-----|-----|-----|-----|-----|----|------|

| Deselected, Outputs High Z                                               | х    | Н  | X   | Х   | х   | L   | Х   | L-H | X  | Hi-Z |

| Output Disabled, Outputs High Z                                          | Х    | Х  | х   | х   | Х   | Х   | Х   | Х   | Н_ | Hi-Z |

| Register New Base Address, Read from Base Address During Next Cycle      | NBA  | L  | x   | ×   | L   | x   | х   | L-H | L  | VQ   |

| Register New Base Address, Read from<br>Base Address During Next Cycle   | NBA  | L  | н   | н   | Н   | L   | х   | L-H | L  | VQ   |

| Increment Burst Address, Read from Incremented Address During Next Cycle | х    | х  | н   | н   | н   | н   | L   | L-H | L  | VQ   |

| Read, Non-Incremented Burst Address : Wait-State                         | x    | x  | н   | н   | н   | н   | н   | L-H | L  | VQ   |

| Register New Base Address, Write Both Bytes at Base Address              | NBA  | L  | L   | L   | н   | L   | ×   | L-H | ×  | VD   |

| Register New Base Address, Write Only the Lower Byte at Base Address     | NBA  | L  | L   | н   | н   | L   | x   | L-H | ×  | VD   |

| Register New Base Address, Write Only the Upper Byte at Base Address     | NBA  | L  | н   | L   | н   | L   | ×   | L-H | ×  | VD   |

| Increment Burst Address, Write Both<br>Bytes at Incremented Address      | x    | x  | L   | L   | н   | н   | L   | L-H | x  | VD   |

| Increment Burst Address, Write Only Lower Byte at Incremented Address    | x    | х  | L   | н   | н   | н   | L   | L-H | ×  | VD   |

| Increment Burst Address, Write Only Upper Byte at Incremented Address    | ×    | ×  | н   | L   | Н   | н   | L   | L-H | x  | VD   |

| Write Both Bytes, Non-Incremented Burst Address : Wait-State             | х    | x  | L   | L   | Н   | Н   | н   | L-H | x  | VD   |

| Lower Byte Write, Non-Incremented Burst Address: Wait-State              | x    | ×  | L   | н   | н   | н   | н   | L-H | x  | VD   |

| Upper Byte Write, Non-Incremented Burst Address: Wait-State              | x    | x  | н   | L   | н   | н   | н   | L-H | x  | VD   |

#### NOTE:

All inputs except GB must meet set-up and hold times on the rising edge(LOW to HIGH) of K. The burst counter is cleared or incremented by the rising edge of K combined with the control inputs APB, ACB and AVB.

Hi-Z = High Impedance

VQ = Valid Data Output

VD = Valid Data Input

NBA = New Base Address

X = Don't Care : Input

Changing : Output

L = Low

H = High

|               | 4675088 | 000P595 | <b>58</b> T |  |    |

|---------------|---------|---------|-------------|--|----|

| DH05-11-MAY95 |         |         |             |  | 27 |

# INTERLEAVED BURST SEQUENCE TABLE

Note that in every case the sequence starts with the initial address, then complements the RAM LSB, then complements both, and finally complements the RAM 2nd LSB, It is only when application-specific address weights are assigned that the sequence appears to differ.

| APPLICATION TYPE        | SEQUENCE 0  | SEQUENCE 1  | SEQUENCE 2  | SEQUENCE 3  |

|-------------------------|-------------|-------------|-------------|-------------|

| '486 Application :      |             |             |             |             |

| Initial                 | 00          | 04          | 08          | oc          |

| First in Burst          | 04          | 00          | oc          | 08          |

| Second in Burst         | 08          | OC          | 00          | 04          |

| Third in Burst          | OC          | 08          | 04          | 00          |

| Pentium Application :   |             |             |             |             |

| Initial                 | 00          | 08          | 10          | 18          |

| First in Burst          | 08          | 00          | 18          | 10          |

| Second in Burst         | 10          | 18          | 00          | 08          |

| Third in Burst          | 18          | 10          | 08          | 00          |

| Arbitrary Application : |             |             |             |             |

| Initial                 | RAM A1 A0   | RAM A1 A0   | RAM A1 A0   | RAM A1 A0   |

| First in Burst          | RAM A1 A0B  | RAM A1 A0B  | RAM A1 A0B  | RAM A1 A0B  |

| Second in Burst         | RAM A1B A0  | RAM A1B A0  | RAM A1B A0  | RAM A1B A0  |

| Third in Burst          | RAM A1B A0B | RAM A1B A0B | RAM A1B A0B | RAM A1B A0B |

### LINEAR BURST SEQUENCE TABLE

|                 | SEQUENCE 0  | SEQUENCE 1  | SEQUENCE 2  | SEQUENCE 3  |

|-----------------|-------------|-------------|-------------|-------------|

| Initial         | RAM A1B A0B | RAM A1B A0  | RAM A1 A0B  | RAM A1 A0   |

| First in Burst  | RAM A1B A0  | RAM A1 A0B  | RAM A1 A0   | RAM A1B A0B |

| Second in Burst | RAM A1 A0B  | RAM A1 A0   | RAM A1B A0B | RAM A1B A0  |

| Third in Burst  | RAM A1 A0   | RAM A1B A0B | RAM A1B A0  | RAM A1 A0B  |

4675088 0006283 919 🚟 \_\_\_\_

## **ABSOLUTE MAXIMUM RATINGS**

Stress greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are absolute stress ratings only. Functional operation of the device is not implied at these or any other conditions in the excess of those given in the operation sections of this data sheet. Exposure to Absolute Maximum Ratings for extended periods can adversely affect device reliability.

| Parameter                   | SYMBOL | MIN  | MAX     | UNIT     |

|-----------------------------|--------|------|---------|----------|

| Storage Temperature         | TSTG   | -55  | 125     | လူ       |

| Junction Temperature        | Tc     |      | 125     | •€       |

| Case Temperature Under Bias | •••    | -10  | 85      | ဇင       |

| Vcc Potential to Vss        |        | -0.5 | 6       | <b>v</b> |

| input Voltage(dc)           |        | -0.5 | Vcc+0.5 | V        |

## RECOMMENDED OPERATING CONDITIONS

Recommended Operating Conditions are defined as the range of operating conditions over which the device performance meets or exceeds the specified DC characteristics.

| PARAMETER                      | SYMBOL | MIN  | MAX     | UNIT |

|--------------------------------|--------|------|---------|------|

| Operating Supply               | Vcc    | 4.75 | 5.25    | V    |

| Supply Return, Reference Level | Vss    | 0.0  | 0.0     | >    |

| Input Low Voltage Level        | VIL    | -0.5 | 0.8     | V    |

| Input High Voltage Level       | VIH    | 2.2  | Vcc+0.5 | V    |

| Case Temperature               | Tc     | 0    | 70      | ပ္   |

4675088 0006284 855 🗯 \_\_\_\_

# **ELECTRICAL CHARACTERISTIC**

| PARAMETER                          | SYMBOL     | TEST CONDITIONS                                                                                                                                      |      | MIN         | TYP | MAX            | UNIT       |

|------------------------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------|-----|----------------|------------|

| Input Voltage : High<br>Low        | VIH<br>VIL |                                                                                                                                                      |      | 2.2<br>-0.5 |     | Vcc+0.5<br>0.8 | <b>V V</b> |

| Output Voltage : High<br>Low       | VOH<br>VOL | IOH=-4.0mA<br>IOL=8.0mA                                                                                                                              |      |             |     | <br>0.4        | V<br>V     |

| Input Leakage Current              | IL1        | 0V≤VIN≤VCC                                                                                                                                           |      | -2          |     | 2              | μА         |

| Output Leakage Current             | ILo        | GB≥Vcc-0.2, 0V≤Vo∪t≤                                                                                                                                 | Vcc. | -2          |     | 2              | μА         |

| Power Supply Current :<br>Operting | Icc        | Device selected,<br>all inputs≤VIL or ≥VIH,                                                                                                          |      |             |     | 250            | mA         |

| Operang                            |            | Vcc=MAX,<br>cycle≥tKC min.                                                                                                                           | 15ns | •••         |     | 225            | mA         |

|                                    |            | outputs open.                                                                                                                                        | 20ns | •••         |     | 180            | mA         |

| CMOS Standby                       | Isb1       | Device deselected:  S ≥ Vcc-0.2,  AC ≤ Vss+0.2,  all inputs≤Vss+0.2 or  ≥Vcc- 0.2,  all inputs static,  Vcc=MAX, fcLκ=0.                             |      | <b></b>     | ::  | 3              | mA         |

|                                    | isb2       | Device deselected;<br>S ≥ Vcc-0.2,<br>AC ≤ Vss+0.2,<br>all inputs ≤ Vss+0.2 or<br>≥Vcc-0.2,<br>all inputs static,<br>Vcc=MAX,<br>cycle time≥tKC min. |      |             | ••• | 80             | mA         |

|                                    | lsb3       | Device deselected; S≥VIH, AC≤VIL, all inputs ≤ VIL or ≥ VIH, all inputs static, VCC=MAX, fcLk=0                                                      |      |             |     | 20             | mA         |

| Short Ciruit Output<br>Current     | los        | -                                                                                                                                                    |      | •••         |     | 50             | mA         |

| 4675088 | 0006285 | 791 |                  |

|---------|---------|-----|------------------|

|         |         |     |                  |

|         |         |     | 451165 44 554465 |

## TIMING CHARACTERISTICS

| 0.41001                                                 | '486/'P5 Local Bus Rate                                                                                                         | 50N  | AHz | 67N | lHz | 75N |      |    |

|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|------|-----|-----|-----|-----|------|----|

| SYMBOL                                                  | Cache RAM                                                                                                                       | 12ns |     | 9n  | ıs  | 6r  | Unit |    |

|                                                         | Parameter                                                                                                                       | Min  | Max | Min | Max | Min | Max  |    |

| tcyc                                                    | Cycle Time                                                                                                                      | 20   |     | 15  |     | 13  | •••  | ns |

| tKQV                                                    | Access Time from Clock                                                                                                          |      | 12  |     | 9   |     | 6    | ns |

| tis<br>tas<br>tss<br>taps<br>tacs<br>tavs<br>tws<br>tos | Input Setup Time Address Select Address Status - µP Address Status - Controller Address Advance Write Enables(LWB, UWB) Data in | 3    |     | 2.0 |     | 2.0 |      | ns |

| tiH<br>tAH<br>tSH<br>tAPH<br>tACH<br>tAVH<br>tWH<br>tDH | Input Hold Time Address Select Address Status - μP Address Status - Controller Address Advance Write Enables (LWB, UWB) Data In | 3    |     | 2.0 |     | 2.0 |      | ns |

| tкн                                                     | Clock High Pulse Width                                                                                                          | 7    |     | 5.5 |     | 4.5 |      | ns |

| tKL                                                     | Clock Low Pulse Width                                                                                                           | 7    |     | 5.5 |     | 4.5 |      | ns |

| tGLQX                                                   | Output Enable to Output<br>Active                                                                                               | 3    |     | 2   |     | 1   |      | ns |

| tGLQV                                                   | Output Enable Time                                                                                                              |      | 7   |     | 6   |     | 6    | ns |

| tGHQZ                                                   | Output Disable Time                                                                                                             |      | 7.  |     | 6   |     | 6    | ns |

| tkox                                                    | Output Change from Clock &<br>Output Enable from Clock                                                                          | 4    |     | 3   |     | 2   |      | ns |

| tĸqz                                                    | Output Disable from Clock                                                                                                       |      | 10  |     | 8   |     | 7    | ns |

## NOTE:

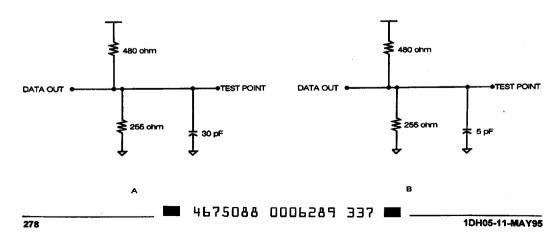

- Switching measurements are from 1.5V levels on the inputs to 1.5V levels on the outputs, except for enable and disable times.

- Enable and disable time measurements are from 1.5V levels on the inputs to change of 0.1V in the output levels.

- 3. See figure AC TEST LOAD A. for output load.

- 4. Input levels for switching measurements are 0V to 3.0V.

- 5. Input rise and fall times for switching measurements are ≤2.0ns(20% to 80%).

- 6. This unit is measured using output loading as specified in figure AC TEST LOAD B.

|               |   |         | <b>1</b> |     |     |

|---------------|---|---------|----------|-----|-----|

|               |   | 4675088 | 0006586  | P58 |     |

| DH05-11-MAY95 | _ |         |          |     | 075 |

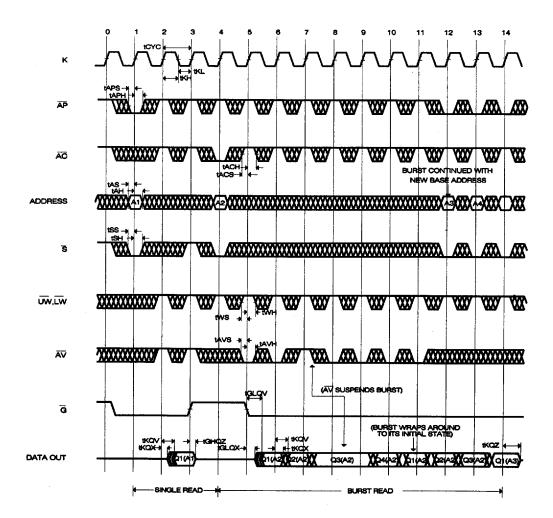

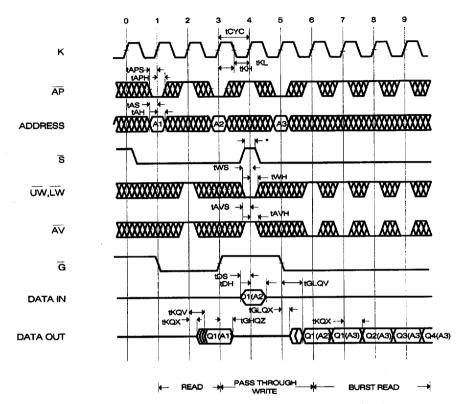

## **TIMNING DIAGRAM**

#### READ CYCLE

₩ 4675088 0006287 564 **₩**

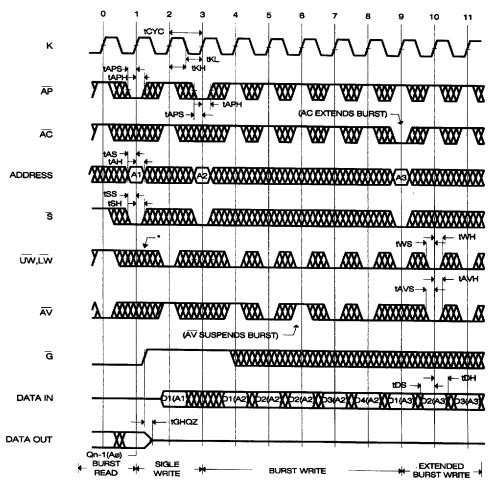

#### WRITE CYCLE

\* When  $\overrightarrow{AP}$  is initiates the burst sequence, the  $\overrightarrow{W}$  control input is ignored for the first cycle, The  $\overrightarrow{W}$  and DATA IN should be asserted and registered in the subsequent cycle.

■ 4675088 0006288 4TD ■ 1DH05-11-MAY95

### READ AND WRITE

\*The state of \$\bar{S}\$ at 4 is ignored due to address A2 being registered one cycle earlier.

# **AC TEST LOAD**

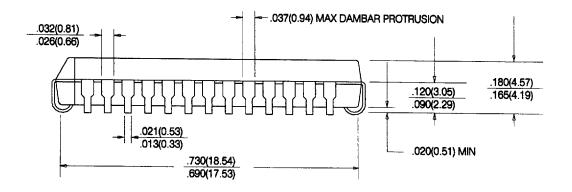

# PACKAGE INFORMATION

4675088 0006290 059 **■**1DH05-11-MAY95 279

# **ORDERING INFORMATION**

| PART NO.   | SPEED(ns) | FEATURES                | PACKAGE    |  |

|------------|-----------|-------------------------|------------|--|

| HY6716100C | 6/9/12    | Pipelined (Interleaved) | 52pin PLCC |  |

| HY6716101C | 6/9/12    | Pipelined (Linear)      | 52pin PLCC |  |

■ 4675088 0006291 T95 **■**

1DH05-11-MAY95