# 16,384-BIT ROM WITH I/O PORTS \*16.384-BIT EPROM WITH I/O PORTS

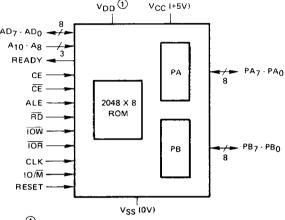

DESCRIPTION The  $\mu$ PD8355 and the  $\mu$ PD8755A are  $\mu$ PD8085A Family components. The  $\mu$ PD8355 contains 2048 x 8 bits of mask ROM and the µPD8755A contains 2048 x 8 bits of mask EPROM for program development. Both components also contain two general purpose 8-bit I/O ports. They are housed in 40 pin packages, are designed to directly interface to the  $\mu$ PD8085A, and are pin-for-pin compatible with each other.

- FEATURES 2048 X 8 Bits Mask ROM (μPD8355 and μPD8355-2)

- 2048 X 8 Bits Mask EPROM (μPD8755A)

- 2 Programmable I/O Ports

- Single Power Supplies: +5V

- Directly Interfaces to the μPD8085A

- · Pin for Pin Compatible

- μPD8755A: UV Erasable and Electrically Programmable

- μPD8335 and μPD8355-2 Available in Plastic Package

- μPD8755A Available in Ceramic Package

### PIN CONFIGURATIONS

www.DataSheet4U.com

| CE 🗖 1               |             | 40 🗖 Vcc             | ਹਵ ₫                 | $\overline{}$ | 40 VCC               |

|----------------------|-------------|----------------------|----------------------|---------------|----------------------|

| CE 🔂 2               |             | 39 🗖 PB7             | CE 🗖                 | 2             | 39 PB <sub>7</sub>   |

| CLK 🗖 3              |             | 38 🗖 PB6             | CLK 🗖                | 3             | 38 🗖 PB <sub>6</sub> |

| RESET 🗖 4            |             | 37 D PB5             | RESET 🗖              | 4             | 37 🗖 PB5             |

| NC 🗖 5               |             | 36 🗖 PB4             | V <sub>DD</sub> 🗖    | 5             | 36 🗖 PB4             |

| READY 🗖 6            |             | 35 🗖 PB3             |                      | 6             | 35 🗖 PB3             |

| 10/M 🗖 7             |             | 34 🗖 PB2             | 10/⋒ 🗖               | 7             | 34 🗖 PB <sub>2</sub> |

| ior 🗖 8              |             | 33 🗖 PB <sub>1</sub> | IOR 🗖                | 8             | 33 🗖 PB <sub>1</sub> |

| RD 🗖 9               |             | 32 🗖 PB <sub>0</sub> | RD 🗖                 | 9             | 32 🏳 PB <sub>O</sub> |

| iow 🗖 10             | μ <b>PD</b> | 31 🗖 PA7             | iow 🗖 1              | 0 <b>μPD</b>  | 31 🗖 PA7             |

| ALE 🗖 11             | 8355/       | 30 🗖 PA6             | ALE 🗖 1              | 1 8755A       | 30 🗖 PA6             |

| AD <sub>0</sub> 🗖 12 | 8355-2      | 29 🗖 PA5             | AD <sub>0</sub> □ 1  | 2             | 29 🏳 PA5             |

| AD1 ☐ 13             |             | 28 🗖 PA4             | AD <sub>1</sub> □ 13 | 3             | 28 🗖 PA4             |

| AD2 🗖 14             |             | 27 🗖 PA3             | AD <sub>2</sub> □ 1- | 4             | 27 🏳 PA3             |

| AD3 🗖 15             |             | 26 🗖 PA2             | AD3 🗖 1              | 5             | 26 🏳 PA2             |

| AD4 🗖 16             |             | 25 🗖 PA1             | AD4 🗖 11             | 6             | 25 🏳 PA 1            |

| AD5 🗖 17             |             | 24 🏳 PA <sub>0</sub> | AD <sub>5</sub> □ 1  | 7             | 24 🏳 PA0             |

| AD6 🗖 18             |             | 23 🗖 A <sub>10</sub> | AD6 🗖 1              | 8             | 23 🗖 A10             |

| AD7 🗖 19             |             | 22 🗖 Ag              | AD <sub>7</sub> 🗖 1  | 9             | 22 🗖 Ag              |

| ∨ <sub>SS</sub> □ 20 |             | 21 A8                | ∨ <sub>SS</sub> □ 2' | 0             | 21 A8                |

NC: Not Connected

Rev/2

The µPD8355 and µPD8755A contain 16,384 bits of mask ROM and EPROM respectively, organized as 2048 X 8. The 2048 word memory location may be selected anywhere within the 64K memory space by using the upper 5 bits of address from the µPD8085A as a chip select.

The two general purpose I/O ports may be programmed input or output at any time. Upon power up, they will be reset to the input mode.

**FUNCTIONAL DESCRIPTION**

BLOCK DIAGRAM

Note: 1 Van applies to #PD8755A only.

ABSOLUTE MAXIMUM Operating Temperature ( $\mu$ PD8355) . . . . . . . . . . . . . . . . . 0°C to +70°C **RATINGS\*** Voltage on Any Pin (μPD8355) . . . . . . . . . . . . . . . . -0.5 to +7V ① (μPD8755A) . . . . . . . . . . . . . . . . . . -0.5 to +7V (1) Note: (1) With Respect to Ground

$T_a = 25^{\circ}C$

\*COMMENT: Stress above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

$T_0 = 0^{\circ} C$  to  $+70^{\circ} C$ :  $V_{CC} = 5V \pm 5\%$

|                                |        | LIMITS  |                      |      | TEST<br>CONDITIONS                      |  |

|--------------------------------|--------|---------|----------------------|------|-----------------------------------------|--|

| PARAMETER                      | SYMBOL | MIN MAX |                      | UNIT |                                         |  |

| Input Low Voltage              | VIL    | -0.5    | 0.8                  | ٧    | V <sub>CC</sub> = 5.0V ①                |  |

| Input High Voltage             | ViH    | 2.0     | V <sub>CC</sub> +0.5 | V    | V <sub>CC</sub> = 5.0V <sup>-</sup> 1   |  |

| Output Low Voltage             | VOL    |         | 0.45                 | ٧    | IOL = 2 mA                              |  |

| Output High Voltage            | Voн    | 2.4     |                      | ٧    | I <sub>OH</sub> = -400 μA               |  |

| Input Leakage                  | 11L    |         | 10                   | μΑ   | V <sub>IN</sub> = V <sub>CC</sub> to 0V |  |

| Output Leakage Current         | ¹LO    |         | ±10                  | μА   | 0.45V <vout <vcc<="" td=""></vout>      |  |

| V <sub>CC</sub> Supply Current | ¹cc    |         | 180/125              | mA   | μPD8355/8355-2                          |  |

Note: ① These conditions apply to  $\mu PD8355/\mu PD8355-2$  only.

DC CHARACTERISTICS

### PIN IDENTIFICATION

| PIN   |                                  |                            |                                                                           |  |  |

|-------|----------------------------------|----------------------------|---------------------------------------------------------------------------|--|--|

| NO.   | SYMBOL                           | NAME                       | FUNCTION                                                                  |  |  |

| 1,2   | ĈĒ, CE                           | Chip Enables               | Enable Chip activity for memory or I/O                                    |  |  |

| 3     | CLK                              | Clock Input                | Used to Synchronize Ready                                                 |  |  |

| 4     | Reset                            | Reset Input                | Resets PA and PB to all inputs                                            |  |  |

| 5 ①   | NC                               | Not Connected              |                                                                           |  |  |

| 5②    | V <sub>DD</sub>                  | Programming<br>Voltage     | Used as a programming voltage, tied to +5V normally                       |  |  |

| 6     | Ready                            | Ready Output               | A tri-state output which is active during data direction register loading |  |  |

| 7     | IO/M                             | I/O or Memory<br>Indicator | An input signal which is used to indicate I/O or memory activity          |  |  |

| 8     | IOR                              | I/O Read                   | I/O Read Strobe In                                                        |  |  |

| 9     | · RD                             | Memory Read                | Memory Read Strobe In                                                     |  |  |

| 10    | iÓW                              | I/O Write                  | I/O Write Strobe In                                                       |  |  |

| 11    | ALE                              | Address Low<br>Enable      | Indicates information on<br>Address/Data lines is valid                   |  |  |

| 12-19 | AD <sub>0</sub> -AD <sub>7</sub> | Low Address/Data<br>Bus    | Multiplexed Low Address and Data Bus                                      |  |  |

| 20    | V <sub>SS</sub>                  | Ground                     | Ground Reference                                                          |  |  |

| 21-23 | A8-A10                           | High Address               | High Address inputs for ROM reading                                       |  |  |

| 24-31 | PA <sub>0</sub> -PA <sub>7</sub> | Port A                     | General Purpose I/O Port                                                  |  |  |

| 32-39 | PB <sub>0</sub> -PB <sub>7</sub> | Port B                     | General Purpose I/O Port                                                  |  |  |

| 40    | Vcc                              | 5V Input                   | Power Supply                                                              |  |  |

Notes: ① μPD8355 ② μPD8755A

www.DataSheet4U.com

# I/O PORTS

I/O port activity is controlled by performing I/O reads and writes to selected I/O port numbers. Any activity to and from the  $\mu$ PD8355 requires the chip enables to be active. This can be accomplished with no external decoding for multiple devices by utilizing the upper address lines for chip selects. ① Port activity is controlled by the following I/O addresses:

| AD <sub>1</sub> | AD <sub>0</sub> | PORT SELECTED | FUNCTION                |

|-----------------|-----------------|---------------|-------------------------|

| 0               | 0               | Α Α           | Read or Write PA        |

| 0               | 1               | В             | Read or Write PB        |

| 1               | 0               | Α             | Write PA Data Direction |

| 1               | 1               | В             | Write PB Data Direction |

Since the data direction registers for PA and PB are each 8-bits, any pin on PA or PB may be programmed as input of output (0 = in, 1 = out).

Note: ① During ALE time the data/address lines are duplicated on A15-A8.

# μPD8355/8755A

Ta = 0°C to 70°C; V<sub>CC</sub> = 5V ± 5%

|    | www.DataSheet4U.com |

|----|---------------------|

| AC | CHARACTERISTICS     |

|                   |                                        | 8355 |      | 8355-2 |      |      | Test                       |

|-------------------|----------------------------------------|------|------|--------|------|------|----------------------------|

| Symbol            | Parameter                              | Min. | Max. | Min.   | Max. | Unit | Canditions                 |

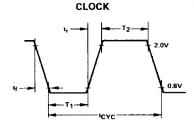

| <sup>†</sup> CYC  | Clock Cycle Time                       | 320  |      | 200    |      | nş   |                            |

| T <sub>1</sub>    | CLK Pulse Width                        | 80   |      | 40     |      | ns   | D 150 - 5                  |

| Т2                | CLK Pulse Width                        | 120  |      | 70     |      | ns   | C <sub>LOAD</sub> = 150 pF |

| tg,t <sub>f</sub> | CLK Rise and Fall Time                 |      | 30   |        | 30   | ns   | 1                          |

| †AL               | Address to Latch Set Up Time           | 50   |      | 30     |      | ns   |                            |

| ¹LA               | Address Hold Time after Latch          | 80   |      | 30     |      | ns   | ]                          |

| ¹LC               | Latch to READ/WRITE Control            | 100  |      | 40     |      | ns   | ]                          |

| †RD               | Valid Data Out Dealy from READ Control |      | 170  |        | 140  | ns   |                            |

| ¹AD               | Address Stable to Data Out Valid       |      | 400  |        | 330  | ns   |                            |

| <sup>t</sup> LL   | Latch Enable Width                     | 100  |      | 70     |      | ns   | 1                          |

| <sup>t</sup> RDF  | Data Bus Float after READ              | 0    | 100  | 0      | 85   | ns   | 1                          |

| †CL               | READ/WRITE Control to Latch Enable     | 20   |      | 10     |      | ns   | 150 p⊬ Load                |

| tCC               | READ/WRITE Control Width               | 250  |      | 200    |      | ns   | ]                          |

| †DW               | Data in to Write Set Up Time           | 150  |      | 150    |      | ns   | ]                          |

| ¹WD               | Data in Hold Time After WRITE          | 10   |      | 10     | 1    | ns   | ]                          |

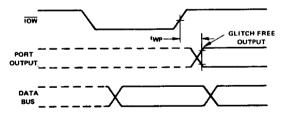

| twp               | WRITE to Port Output                   |      | 400  |        | 400  | ns   | ]                          |

| tPR               | Port Input Set Up Time                 | 50   |      | 50     |      | ns   | ]                          |

| <sup>t</sup> RP   | Port Input Hold Time                   | 50   |      | 50     |      | ns   | ]                          |

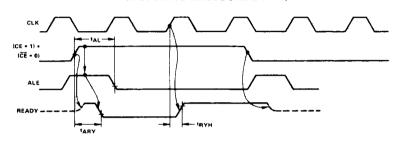

| <sup>t</sup> BYH  | READY HOLD Time                        | 0    | 160  | 0      | 160  | ns   | ]                          |

| †ARY              | ADDRESS (CE) to READY                  |      | 160  |        | 160  | ns   | ]                          |

| ¹RV               | Recovery Time Between Controls         | 300  |      | 200    |      | ns   | ]                          |

| †RDE              | READ Control to Data Bus Enable        | 10   |      | 10     |      | ns   | 1                          |

Notes: 30 ns for µPD8755A

C<sub>LOAD</sub> = 150 pF

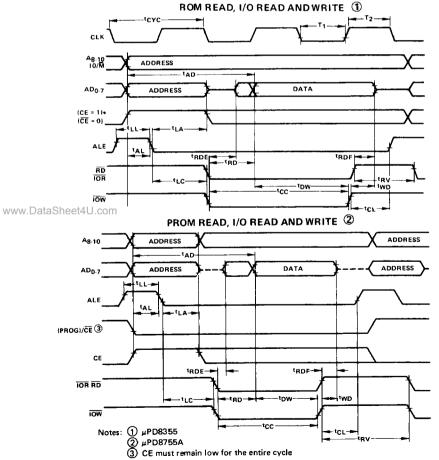

**TIMING WAVEFORMS**

www.DataSheet4U.com

TIMING WAVEFORMS (CONT.)

### WAIT STATE TIMING (READY = 0)

# INPUT MODE: I/O PORT RD OR IOR PORT INPUT DATA BUS

www.DataSheet4U.com

## OUTPUT MODE:

EPROM PROGRAMMING μPD8755A

Erasure of the  $\mu$ PD8755A occurs when exposed to ultraviolet light sources of wavelengths less than 4000 Å. It is recommended, if the device is exposed to room fluorescent lighting or direct sunlight, that opaque labels be placed over the window to prevent exposure. To erase, expose the device to ultraviolet light at 2537 Å at a minimum of 15 W-sec/cm² (intensity X expose time). After erasure, all bits are in the logic 1 state. Logic 0's must be selectively programmed into the desired locations. It is recommended that NEC's PROM programmer be used for this application.

6

# **Package Outlines**

For information, see Package Outline Section 7.

Plastic, μPD8355HC/8755AC Ceramic, μPD8355D Ceramic, μPD8355HD Ceramic, μPD8755AD

Cerdip,  $\mu$ PD8755AD, has quartz window

www.DataSheet4U.com