## SIEMENS

# PEB 2030 Frame Aligner Circuit (FRAC)

- Detection of Frame Alignment Signals for PCM 30 Highways in Accordance with CCITT Recommendations G 737, 738, 739

- Delay Compensation and Clock Alignment between Transmission Line and Exchange

- Compensation of Phase Jitter up to 60 μs

- Detection and Initiation of Route Alarms (AIS, Service Word)

- Loss of Frame Alignment Indicator

- Slip Detection

- Error Simulation for Test Purposes

- Digital Interface, TTL-Compatible

- NMOS

| Pin Configuration                                                                                                                                                              |                                                                             | Pin Definitions                                         |                                                                                                                                                                                                                                                                                |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| (Top View)                                                                                                                                                                     | Pin                                                                         | Symbol                                                  | Function                                                                                                                                                                                                                                                                       |  |  |  |

| V <sub>00</sub> FP IN B8 B7 B6 B5 B4 B3 B2 B1 P<br>24 23 22 21 20 19 18 17 16 15 14 13<br>1 2 3 4 5 6 7 B 9 10 11 12<br>0B1 0B2 SP R/W PE RCL SCL B1 SCT CE SO V <sub>SS</sub> | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>23<br>22<br>14<br> | DB 1 DB 2 SP R/W PCL SCL BI SCE SO FP IN 1 B 8 P SS VDD | Data Interfaces (DBi) Synchronous Pulse Direction of Data Transfer Alarm Port Enable Route Clock Station Clock Buffer Inactive Station Counter Trigger Pulse Chip Enable Serial Output Fault Pulse PCM Input Parallel Outputs (Bi) Parity Bit Ground (0V) Supply Voltage (+5V) |  |  |  |

The PEB 2030 frame aligner circuit is used for interfacing PCM 30 routes with PCM switching networks.

#### Its main applications are as follows:

- In multiplex units for PCM transmission routes

- In concentrators and subscriber multiplexers at one end of PCM routes

- As interface between PCM routes and public and private PCM switches (DIU)

- For delay compensation between switching stages

The Siemens frame aligner circuit PEB 2030 is a monolithic NMOS circuit. Its main application is detection of frame alignment signals of PCM 30 routes according to CCITT Recommendations G 737, 738, 739 and clock adjustment with delay compensation between PCM routes and PCM switches.

An incorporated buffer enables the PEB 2030 to compensate phase jitter up to 60  $\mu$ s. Route alarms can be challenged by a bidirectional data interface.

© Siemens Components, Inc.

4-3

April 1987

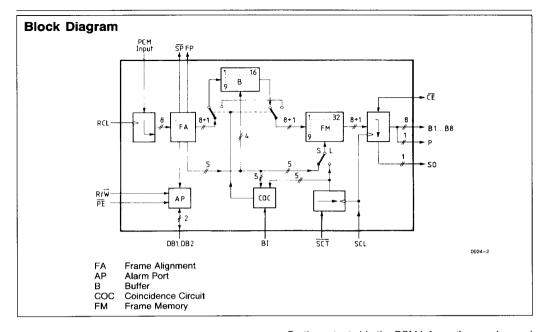

#### **Functional Description**

The PEB 2030 IC is fabricated using N-channel depletion technology.

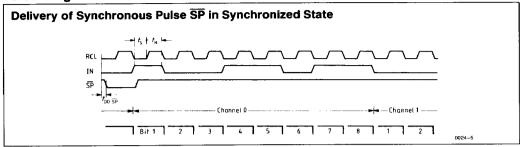

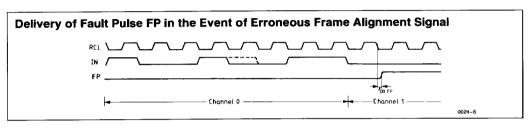

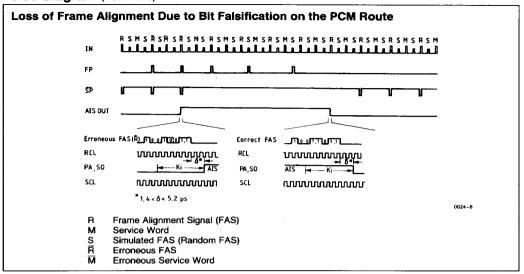

The circuit, connected to a PCM 30 line, and the associated input clock (route clock RCL), are synchronized with the PCM frame in accordance with CCITT Recommendation G 732. In the stable condition the circuit supplies 488 ns synchronous pulses  $(\overline{SP})$  at a bit rate of 4 Kbits/s which identify the beginning of the PCM frames containing the bunched frame alignment signal (FAS). During the synchronizing phase and in the event of frame alignment signal (FAS), the synchronizing pulses are suppressed and a 2  $\mu s$  fault pulse FP is delivered every 250  $\mu s$ . When a synchronized state exists, such a fault pulse appears only if a FAS is not recognized.

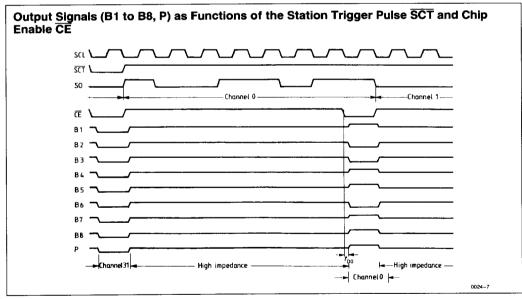

On the output side the PCM information can be read out in serial or parallel form. For this purpose, a reading clock (SCL) and a 488 ns reading synchronizing pulse (SCT) must be applied at 250  $\mu s$  intervals to fix the beginning of the frame. The circuit supplies a parity check bit (even parity) to each PCM word via a tristate output which is activated by a chip enable ( $\overline{CE}$ ) in the same way as the tristate outputs for the parallel information.

An alarm flipflop (FA alarm) in the circuit is set in the event of frame alignment loss, route timing loss or loss of the  $\overline{CE}$  or SCT signals. The alarm bit is recorded in another flipflop in the service word (bit 3), whereas a third flipflop stage is set when logic "1" signals are received by the PCM route for the duration of two frames (Alarm Indication Signal AIS). A further flipflop is set when a slip of the frame occurs. The alarms are polled via a bidirectional data interface. The alarm circuits can be triggered and reset for test purposes via the data interface.

**Description of Individual Pins**

| Symbol          | Features                                     | Description                                                                                                                                                          |  |

|-----------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1. Supply       |                                              |                                                                                                                                                                      |  |

| V <sub>DD</sub> | +5V ±5%                                      | Typical Power Consumption 300 mW.                                                                                                                                    |  |

| V <sub>SS</sub> | oV                                           |                                                                                                                                                                      |  |

| 2. PCM Inter    | faces                                        |                                                                                                                                                                      |  |

| IN              |                                              | PCM Input. Information Bit from One Negative RCL Edge to the Next.                                                                                                   |  |

| RCL             | 2.048 MHz ±50 ppm                            | Route Clock.                                                                                                                                                         |  |

| B1B8            | 256 Kbit/s                                   | Parallel PCM Output Information. B1 = Most Significant Information Bit.                                                                                              |  |

| Р               | 256 Kbit/s                                   | Parity Bit (Even Parity).                                                                                                                                            |  |

| SO              | 2.048 Mbit                                   | Serial PCM Output. Bit Sequence with Decreasing Significance.                                                                                                        |  |

| SCL             | 2.048 MHz                                    | Station Clock. Information Bits from One<br>Negative SCL Edge to the Next.                                                                                           |  |

| 3. Control S    | ignals                                       |                                                                                                                                                                      |  |

| SCT             | 4 Kbit/s<br>Width 488 ns                     | From One Negative SCL Edge to the Next. Frame Begins at Positive SCT edge.                                                                                           |  |

| SP              | 4 Kbit/s<br>Width 488 ns                     | From One Negative RCL Edge to the Next. Frame Begins with FAS at Positive SP Edge.                                                                                   |  |

| ВІ              |                                              | Continuous Signal.  BI = 1 or Not Connected: Buffer Inactive.                                                                                                        |  |

| FP              | Width:<br>4 × 488 ns = 1.95 μs               | Fault Pulse Delivered for Every Undetected FAS or<br>Every 250 μs is the Event of Frame Alignment Loss                                                               |  |

| CE              | 256 Kbit, with 488 ns<br>or Continuous Level | Chip Enable Controls Outputs B1 to B8, P Low-<br>Impedance. The CE Must be Active During the SCT, so that the SCT Supervision by Station<br>Counter is Not Impaired. |  |

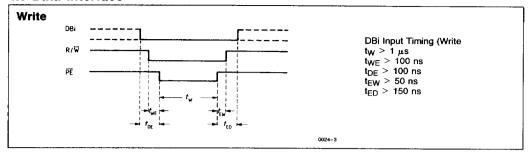

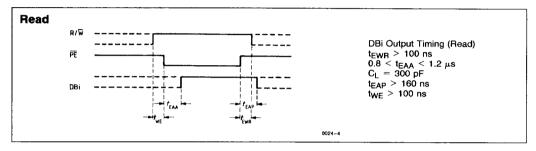

### 4.0 Data Interface

$\begin{array}{ll} \text{Data Transfer Direction} \\ R/\overline{W} = 1 \text{ Read Alarm Port} \\ R/\overline{W} = 0 \text{ Write Alarm Port} \\ \text{Alarm Port Enable} \\ \text{Bidirectional Data Interface for Command Acceptance or Alarm Signaling:} \end{array}$

| DB2 | DB1 |                                                 |

|-----|-----|-------------------------------------------------|

| 0   | 0   | Command: Poll FA, Alarm, AIS Alarm              |

| 0   | 1   | Command: Poll B3 of the Service Word Slip Alarm |

| 1   | 0   | Command: Reset Alarm Flipflop                   |

| 1   | 1   | Command: Alarm Simulation                       |

#### Note:

Alarms are Signalled as Log. "1"

### Pulse Diagram

## **Absolute Maximum Ratings\***

| Input Voltage (V <sub>I</sub> ) $-0.3V$ to $+7.0V$                       |

|--------------------------------------------------------------------------|

| Supply Voltage (VDD) $\dots -0.3V$ to $+7.0V$                            |

| Operating Temperature (T <sub>A</sub> ) $0^{\circ}$ C to $+70^{\circ}$ C |

| Storage Temperature (Tstg) $\dots -55^{\circ}$ C to $+125^{\circ}$ C     |

| Total Power Consumption (Ptot) 400 mW                                    |

\*Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Electrical Characteristics** $(T_A = 25^{\circ}C)$

| Parameter                              | Symbol             |      | Units |       |        |

|----------------------------------------|--------------------|------|-------|-------|--------|

| r di dinotoj                           | Symbol             | Min  | Тур   | Max   | Ullits |

| Supply Voltage                         | $V_{DD}$           | 4.75 | 5     | 5.25  | V      |

| Supply Current                         | Is                 |      | 50    | 70    | mA     |

| Input Current                          | լ I <sub>I</sub> ը | 50   |       | 200   | μΑ     |

| H Input Voltage                        | V <sub>IH</sub>    | 2.4  |       |       | ٧      |

| L input Voltage                        | V <sub>IL</sub>    |      |       | 0.7   | ٧      |

| L Output Voltage                       | V <sub>OL</sub>    |      |       | 0.4   | ٧      |

| H Output Voltage                       | V <sub>OH</sub>    | 2.7  |       |       | ٧      |

| H Output Current (FP, SO, SP)          | Іон                |      |       | -0.02 | mA     |

| H Output Current (Bi, P)               | loh                |      | -     | -0.05 | mA     |

| L Output Current (FP, SO, SP, 1 Bi, P) | l <sub>OL</sub>    |      |       | 0.46  | mA     |

| H Output Current (DBi)                 | loh                |      |       | -0.04 | mA     |

| L Output Current (DBi)                 | I <sub>OL</sub>    |      |       | 0.9   | mA     |

**Timing Specification**

| Parameter                                                                   | Symbol          |     | Units |     |       |

|-----------------------------------------------------------------------------|-----------------|-----|-------|-----|-------|

|                                                                             |                 | Min | Тур   | Max | Units |

| Input H-L Transfer Time                                                     | t <sub>HL</sub> |     |       | 20  | ns    |

| Input L-H Transfer Time                                                     | t <sub>LH</sub> |     |       | 20  | ns    |

| Clock Frequency<br>(Pulse-Pause Ratio 1:1) t <sub>WH</sub> :t <sub>WL</sub> | <sup>f</sup> CL | 0.2 | 2.048 | 2.1 | MHz   |

| Setup Time                                                                  | ts              | 150 |       | •   | ns    |

| Hold Time                                                                   | t <sub>H</sub>  | 40  |       |     | ns    |

Switching Times ( $V_{DD} = +5V$ ,  $T_A = +25$ °C)

| Parameter       |                |                 |              |     | Limits |     |       |

|-----------------|----------------|-----------------|--------------|-----|--------|-----|-------|

| From<br>(Input) | To<br>(Output) | Symbol          | Conditions   | Min | Тур    | Max | Units |

| CE              | B1B8, P        | t <sub>DO</sub> | 50 pF, 10 kΩ |     |        | 200 | ns    |

| SCL             | DB 2, DB 1     | t <sub>DO</sub> | 50 pF, 5 kΩ  |     |        | 350 | ns    |

| RCL             | FP, SP         | t <sub>DQ</sub> | 15 pF, 10 kΩ |     |        | 200 | ns    |

| SCL             | SO             | t <sub>DO</sub> | 15 pF, 10 kΩ |     |        | 200 | ns    |

**Ordering Information**

| Туре     | Package |  |  |

|----------|---------|--|--|

| PEB 2030 | DIC 24  |  |  |