7-75-15

Preliminary

## Am2091

### ISDN Echocancellation Circuit (IEC-Q)

Advanced Micro Devices

### DISTINCTIVE CHARACTERISTICS

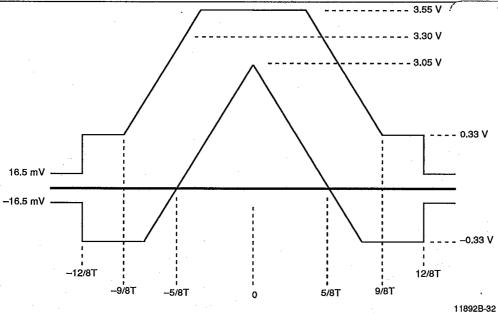

- Full duplex data transmission and reception at the U reference point according to the Layer 1 Specification of the American National Standard institute ANSI® T1.601-1988

- -144 kb/s user bit rate over a two-wire subscriber loop

- -2B1Q block code (2 binary, 1 quaternary)

- -4 kb/s maintenance channel for execution of data loop back commands and monitoring transmission errors

- -Activation and deactivation procedure

- -Satisfies transmission requirements for loops 1-15 of ANSI's 15 telephone plant test loops

- IOM-2™ Interface

- -Optimized for working in conjunction with SBCX™, EPIC™ and IDEC™ telecom IC's

- -Handling of the commands and indications contained in the IOM-2 C/I channel for deactivation, activation, supervision of power supply unit and equipment for testing

- -Data available via Monitor channel: CRC transmission errors Measurement value of the loop current Echo Canceller coefficients and internal status values

- -Switching test loops

- -Generation of synchronized 7.68-MHz clock for SBCX in NT mode

- Adaption of internal interfaces to the current signal direction by programmable operational modes:

- -LT: Line termination in public or private exchange

- –TE: Terminal mode

- -NT: Network termination connected to SBCX

- -NT-PABX: Trunk module (TDM)

- Built in wake-up unit for activation from powerdown state

- Adaptive echocancellation

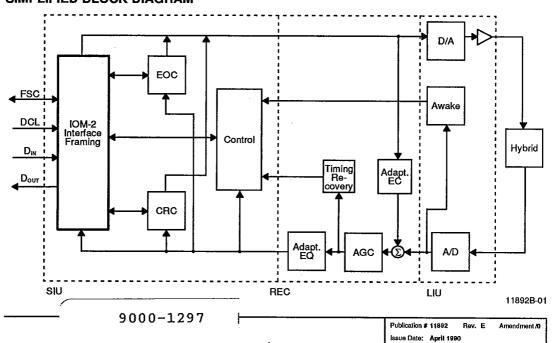

### SIMPLIFIED BLOCK DIAGRAM

### **DISTINCTIVE CHARACTERISTICS (continued)**

- Adaptive equalization

- Automatic polarity adaption

- Clock recovery (frame and bit synchronization) in all applications

- **Automatic gain control**

- Low-power consumption:

standby: 35 mW

active:

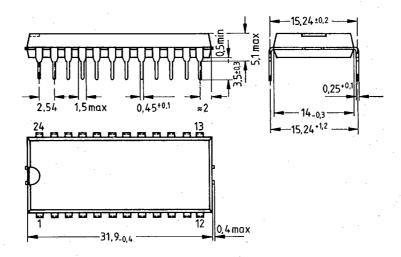

290 mW (Am2091) 150 mW (Am20911) 24-pin DIP package (Am20912) 44-pin PLCC package (Am2091)

40-pin DIP package (Am20911)

Note: The Am2091 is the one-chip version of the Am20911 and Am20912

### **GENERAL DESCRIPTION**

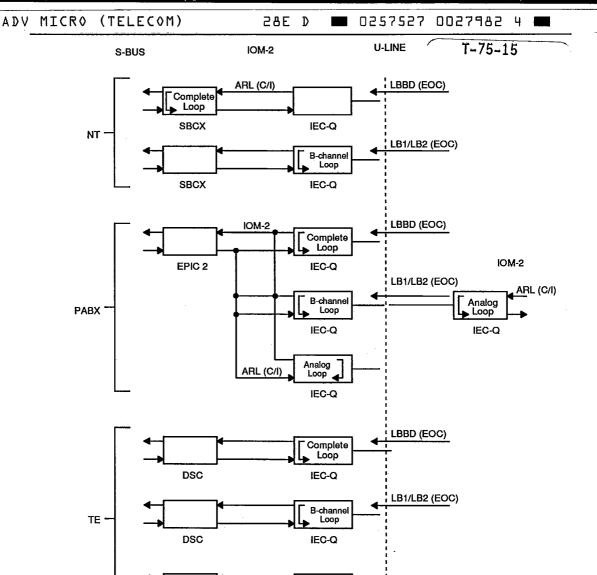

Different hardware configurations as well as different operating modes of the IEC-Q™ are selectable to cope with the different system requirements.

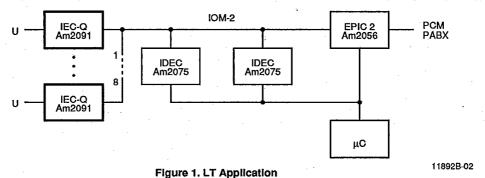

Together with the EPIC, performing the control of the C/I channel, B-channel slot assignment and the Monitor channel handling and together with the IDEC, a HDLC controller for four independent D channels, an LT configuration with up to 8 IEC-Q devices can be built.

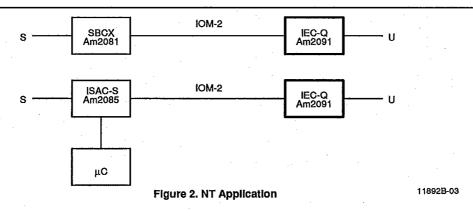

By using the SBCX (four-wire S/T bus interface) a complete NT1 Network Termination can be built with only two devices. If intelligent maintenance functions are required, the SBCX is replaced by the ISAC-S™ which provides microcontroller access to the IOM-2 control channels (MON, C/I).

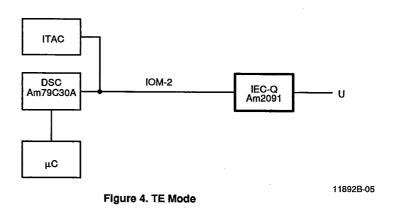

With Voice/Data modules such as DSC Digital Subscriber Controller™ and ITAC™ Terminal Adapter Circuit a complete TE configuration can be built in a cost effective manner.

Am2091

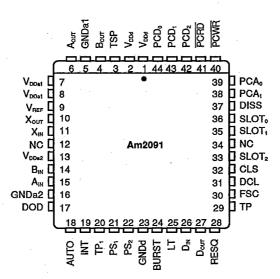

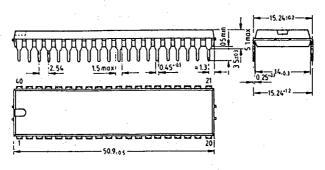

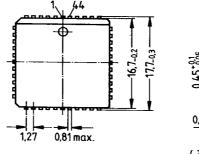

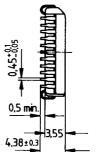

# CONNECTION DIAGRAMS Top View

### 44-Pin PLCC

Note: Pin 1 is marked for orientation.

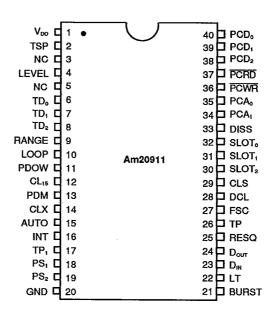

### **CONNECTION DIAGRAMS (continued)**

#### 40-Pin DIP

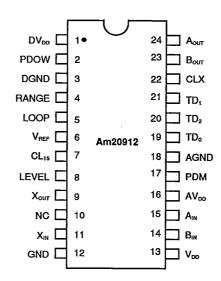

### 24-Pin DIP

Note: Pin 1 is marked for orientation.

Am2091

5

LOGIC SYMBOL

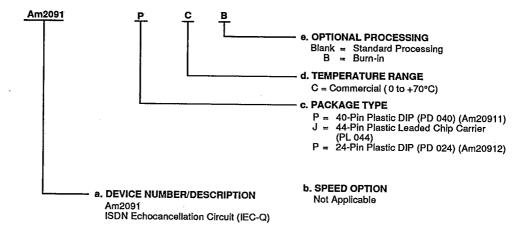

### ORDERING INFORMATION **Standard Products**

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of: a. Device Number

- b. Speed Option (if applicable)

- c. Package Type d. Temperature Range

- e. Optional Processing

| Valid Combinations |         |  |  |  |  |  |

|--------------------|---------|--|--|--|--|--|

| AM2091             | JC, JCB |  |  |  |  |  |

| AM20911            | PC, PCB |  |  |  |  |  |

| AM20912            | PC, PCB |  |  |  |  |  |

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

### Am2091 PIN DESCRIPTION

$A_{IN}$

(input)

Received line signal to hybrid.

(Output)

Transmitted line signal to hybrid.

**AUTO**

(Input)

Auto/transparent mode selection of EOC (automode = High).

BIN

(Input)

Received line signal to hybrid.

BOUT

(Output)

Transmitted line signal to hybrid.

BURST

(Input)

NT, NT-TE mode = Low. LT, NT-PABX mode = High.

CLS

(Output)

TE/NT: 7,68-MHz clock out synchronous to line signal. NT-PABX: 512-kHz clock out synchronous to line signal.

DCL

(Input/Output)

IOM-2 device clock.

$\mathbf{D}_{\mathsf{IN}}$

(Input)

IOM-2 data input synchronous to DCL.

DISS

(Output)

Disable supply (active High).

\*DOD

(Input)

Dour open drain (High); internal pull-up resistor at Dour (Low).

Dout

(Output)

IOM-2 data output synchronous to DCL.

**FSC**

(Input/Output)

IOM-2 frame clock.

**GNDa1**

0-V analog ground.

GNDa2

0-V analog ground.

GNDd

0-V digital ground.

INT

(Input)

Controller interface Interrupt must be clamped to Low during normal operation.

LT

(Input)

LT mode. (High input = LT mode; Low input = NT mode.)

NC

Not connected.

\*PCA

(Output)

Power Controller interface address bus.

\*PCA<sub>1</sub>

(Output)

Power Controller interface address bus.

\*PCDo

(input/Output)

Power Controller interface data bus (MSB, do not connect if not used; internal pull-up).

\*PCD<sub>1</sub>

(input/Output)

Power Controller interface data bus (do not connect if not used; internal pull-up).

\*PCD<sub>2</sub>

(Input/Output)

Power Controller interface data bus (LSB, do not connect if not used; internal pull-up).

\*PCRD

(Output)

Power Controller interface read request (active Low).

\*PCWR

(Output)

Power Controller interface write request (active Low).

Ω

### PS<sub>1</sub>

### (Input)

NT: Power Status (primary).

LT: PFOFF, Power Feed Off. Must be clamped to Low if not used.

### PS<sub>2</sub>

### (Input)

NT: Power Status (secondary).

LT: Monitor Power Feed (active High). Serial data of Power Feed Current.

### **RESQ**

### (Input)

Power On Reset (active Low) must be Low at least 300 µs. The clock on the DCL pin has to be applied during RESET in the LT mode and in the NT-PABX mode. Clamp to High if not used.

### SLOT

### (Input)

$256\,\mathrm{kb/s}$  modes select. Allocation of time slot for BURST mode.

#### SLOT<sub>1</sub>

#### (Input)

$256\,\mathrm{kb/s}$  modes select. Allocation of time slot for BURST mode.

### SLOT<sub>2</sub>

### (Input)

$256\,\mbox{kb/s}$  modes select. Allocation of time slot for BURST mode.

### ΤP

#### (Input)

Test Pin (do not connect; internal pull-down).

#### TP<sub>1</sub>

#### (Input)

Test Pin (digital loop, do not connect; internal pull-down).

### **TSP**

#### (Input)

Test Single Pulses must be clamped to Low if not used.

#### $V_{DDa1}$

5-V  $\pm$ 5% analog supply voltage.

### $V_{\text{DDa2}}$

5-V ±5% analog supply voltage.

### $V_{DDd}$

5-V ±5% digital supply voltage.

#### VREF

### (Output)

$V_{\text{REF}}$  pin to buffer internally generated voltage with capacitor 10 nF versus GNDa.

### $X_{IN}$

### (Input)

In all NT modes, crystal connection. In all LT modes, 15.36-MHz clock input synchronized to IOM™ clocks.

#### Xout

### (Output)

In all NT modes, crystal connection. In all LT modes, to be left open.

\*Note: These pins are switched as test pins (I/O) during test condition.

For DOD = 1: Doυτ open drain output (external pull-up) For DOD = 0: Doυτ

|          | Binary<br>Equivalent<br>Dout | Dout<br>In SLOT<br>Position | Dout<br>in /SLOT<br>Position |  |

|----------|------------------------------|-----------------------------|------------------------------|--|

| RESQ = 0 | 0                            | Low                         | Internal pull-up             |  |

|          | 1                            | Internal pull-up            | Internal pull-up             |  |

| RESQ = 1 | 0                            | Low                         | High Z                       |  |

|          | 1                            | High                        | High Z                       |  |

| <br>RESQ    | TSP | Mode               |

|-------------|-----|--------------------|

| 0           | 0   | RESET              |

| 0           | 1   | Data Through       |

| 1           | 0   | Normal             |

| 1           | 1   | Test Single Pulses |

| 0<br>1<br>1 | •   | Normal             |

### **Am20911 PIN DESCRIPTIONS**

The Am20911 is the digital part of the IEC-Q containing the SIU (System Interface Unit) and REC (Receiver blocks) in a 40-pin DIP package. Specified functions and timing requirements are identical to those for the one-chip (Am2091) solution.

### **AUTO**

#### (input)

Auto/transparent mode selection of EOC (automode = High).

### **BURST**

### (Input)

NT, NT-TE mode = Low. LT, NT-PABX mode = High.

### CLS

### (Output)

TE/NT: 7.68-MHz clock out synchronous to line signal.

NT-PABX: 512-kHz clock out synchronous to line signal.

### **CLX**

### (Output)

Transmit clock to Am20912.

### **CL**<sub>15</sub>

#### (Input)

15.36-MHz input clock connected to  $\text{CL}_{15}$  pin of Am20912 in proposed application.

### DCL

### (Input/Output)

IOM-2 device clock.

### DIN

### (Input)

IOM-2 data input synchronous to DCL.

### DISS

### (Output)

Disable supply (active High).

### Dout

### (Output)

IOM-2 data output synchronous to DCL.

### **FSC**

### (Input/Output)

IOM-2 frame clock.

#### GNDd

0-V digital ground.

#### INT

### (Input)

Controller interface interrupt pin must be clamped during normal operation.

#### LEVEL

#### (Input)

Level signal connected to LEVEL output of Am20912 during normal operation.

### LOOP

#### (Output)

Analog loop if active High (to Am20912).

#### LT

### (Input)

LT mode. (High input = LT mode; Low input = NT mode.)

#### NC

Not connected.

### \*PCA

### (Output)

Power Controller interface address bus.

#### \*PCA

#### (Output)

Power Controller interface address bus.

### \*PCD

#### (Input/Output)

Power Controller interface data bus (do not connect if not used; internal pull-up).

### \*PCD<sub>1</sub>

### (Input/Output)

Power Controller interface data bus (do not connect if not used; internal pull-up).

### \*PCD<sub>2</sub>

### (input/Output)

Power Controller interface data bus (do not connect if not used; internal pull-up).

### \*PCRD

#### (Output)

Power Controller interface read request (Low).

### \*PCWR

### (Output)

Power Controller interface write request (Low).

10

PDM

(Input)

Output of A/D converter (15.36-MHz periods) connected to PDM pin of Am20912.

PDOW

(Output)

Power down signal active High (to Am20912).

PS<sub>1</sub>

(Input)

NT: Power Status (primary).

LT: PFOFF, Power Feed Off. Must be clamped to Low if not used.

PS<sub>2</sub>

(Input)

NT: Power Status (secondary).

LT: Monitor Power Feed (active High). Serial data of Power Feed Current.

RANGE

(Output)

Range signal to Am20912.

**RESQ**

(Input)

Power On Reset (active Low). Must be Low at least 300 µs. The clock on the DCL pin has to be applied during RESET in the LT mode and in the NT-PABX mode. Clamp to High if not used.

SLOT<sub>0</sub>

(Input)

256 kb/s modes select. Allocation of time slot for BURST mode.

SLOT₁

(Input)

$256\,\mathrm{kb/s}$  modes select. Allocation of time slot for BURST mode.

SLOT<sub>2</sub>

(Input)

$256\,kb/s$  modes select. Allocation of time slot for BURST mode,

TD0

(Output)

Quad ternary data out.

TD₁

(Output)

Quad ternary data out.

$TD_2$

(Output)

Quad ternary data out. Stable with falling edge of CLX.

TP

(input)

Test Pin (do not connect; internal pull-down).

TP<sub>1</sub>

(input)

Test Pin (digital loop, do not connect; internal pull-down).

TSP

(Input)

Test Single Pulses must be clamped to Low if not used.

$V_{\text{DDd}}$

5-V ±5% digital supply voltage.

\*Note: These pins are switched as test pins (I/O) during test condition.

| <br>TDo | TD <sub>1</sub> | TD <sub>2</sub> | Signal Level |

|---------|-----------------|-----------------|--------------|

| 0       | 1               | 0               | 3            |

| 0       | 1               | 1               | 1            |

| 0       | 0               | 1               | -1           |

| 0       | 0               | 0               | -3           |

| 1       | x               | x               | 0            |

|         |                 |                 |              |

x = 1 or 0

| RESQ | TSP | Mode               |

|------|-----|--------------------|

| 0    | 0   | RESET              |

| 0    | 1   | Data Through       |

| 1    | 0   | Normal             |

| 1    | 1   | Test Single Pulses |

### **Am20912 PIN DESCRIPTION**

### **AGND**

(Input)

Ground pin.

### AIN

(Input)

Received line signal from hybrid.

### Aout

(Output)

Transmitted line signal to hybrid.

### $AV_{DD}$

(Input)

Voo pin.

### $B_{iN}$

(Input)

Received line signal from hybrid.

#### Вол

(Output)

Transmitted line signal to hybrid.

### CLX

(Input)

80-kHz clock input. Transmitter is synchronized to this clock.

#### CL<sub>15</sub>

### (Output)

15-MHz input clock. Capacitive load should be minimized.

### DGND

(Input)

Ground pin.

### $DV_{DD}$

(input)

Voo pin.

### GND

(input)

Ground pin.

### **LEVEL**

### (Output)

Detects the 0 crossing of the differential input signal and is used to activate the IEC-D.

### LOOP

(Input)

Activates the analog test loop.

#### NC

Not connected.

### **PDM**

### (Output)

15-MHz, 1-bit output signal of the ADC in phase with CL<sub>15</sub>. Changes with rising edge of CL<sub>15</sub> +2-4 ns. Capacitive load should be minimized.

#### **PDOW**

### (Input)

Activates power-down mode, only oscillator and level detect are operating during power-down.

### RANGE

### (input)

Activates 6-dB attenuation for the ADC input signal.

### TD<sub>o</sub>

### (Input)

Digital input signal to the DAC.

### TD<sub>1</sub>

(Input)

Digital input signal to the DAC.

### TD<sub>2</sub>

### (Input)

Digital input signal to the DAC.  $TD_{2-0}$  must be stable with falling edge +150 ns -150 ns of CLX.

### V<sub>DD</sub>

(input)

Voo pin.

#### VREF

#### (Output)

$\mbox{\sc Vref}$  pin to buffer internally generated voltage with capacitor 10 nF versus AGND.

### XIN

### (Input)

In all NT modes, crystal connection. In all LT modes, 15.36-MHz clock input synchronized to IOM clocks.

### Xout

#### (Output)

In all NT modes, crystal connection. In all LT modes, to be left open.

| TD₀ | TD <sub>1</sub> | TD <sub>2</sub> | Signal Level |

|-----|-----------------|-----------------|--------------|

| 0   | 1               | 0               | 3 -          |

| 0   | 1               | 1               | 1            |

| 0   | 0               | 1               | 1            |

| 0   | 0               | 0               | -3           |

| 100 | ×               | , <b>X</b>      | 0            |

x = 1 or 0

12

## **OPERATIONAL DESCRIPTION Operation Modes and Functions**

**Table 1. Modes of Operation**

|      |       |    | Inpi                 | ut Pin     |     | Out <sub>j</sub><br>Synchro | Super-<br>Frame-<br>Marker |          |      |

|------|-------|----|----------------------|------------|-----|-----------------------------|----------------------------|----------|------|

| Mode | Burst | LT | LT Slot0 Slot1 Slot2 |            | DCL | DCL                         |                            |          | CLS  |

| NT   | 0     | 0  | 0                    | 0          | 0   |                             | 512 kHz                    | 7.68 MHz | No*  |

| NT   | 0     | 0  | 1                    | 0          | 0   | _                           | 512 kHz                    | 7.68 MHz | Yes* |

| TE   | 0     | 0  | 0                    | 1          | 0   |                             | 1.536 MHz                  | 7.68 MHz | No*  |

| TE   | 0     | 0  | 1                    | 1          | 0   |                             | 1.536 MHz                  | 7.68 MHz | Yes* |

| PABX | 1     | 0  | Slot                 | : Assignme | nt  | 512 kHz-<br>4.096 MHz       | _                          | 512 kHz  |      |

| LT   | 1     | 1  | Slot                 | Assignmen  | nt  | 512 kHz-<br>4.096 MHz       | _                          |          |      |

### Interfaces

**Table 2. Slot Assignment** (DCL = 4.096 MHz)

| Time<br>Slot<br>No. | Slot0 | Slot1 | Slot2 | Bit No. |

|---------------------|-------|-------|-------|---------|

| 0                   | 0     | 0     | 0     | 031     |

| 1 1                 | 0     | 0     | 1     | 32-63   |

| 2                   | 0     | 1     | 0     | 64–95   |

| 3                   | 0     | 1     | 1     | 96–127  |

| 4                   | 1     | 0     | 0     | 128-159 |

| 5                   | 1     | 0     | 1     | 160-191 |

| 6                   | 1     | 1     | 0     | 192-223 |

| 7                   | 1     | 1     | 1     | 224–255 |

**Table 3. Embedded Operation** Channel Mode (EOC)

| Mode        | Input Pin<br>Auto |

|-------------|-------------------|

| Transparent | 0                 |

| Automatic   | 1                 |

<sup>\*</sup>Notes: 1, DCL period High phase of FSC at superframe position.

2. DCL period High phase of FSC at normal frame position (see Timing Diagram).

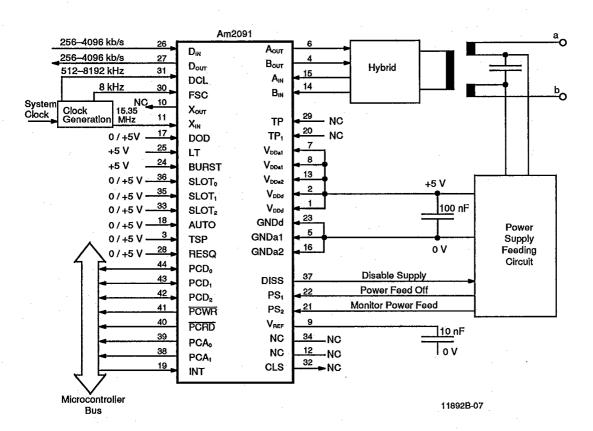

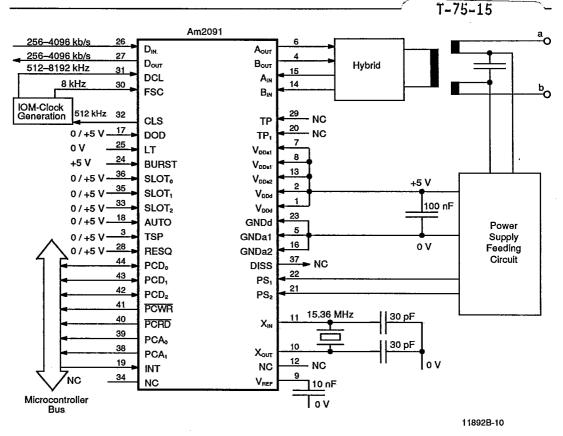

Figure 5. NT Mode

Figure 6. NT-PABX Mode

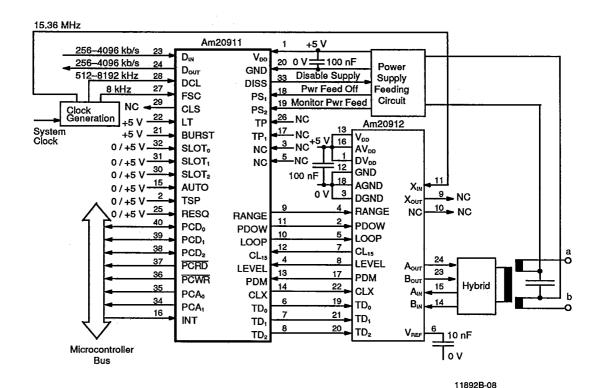

Figure 7. NT Mode

Figure 8. NT-PABX Mode

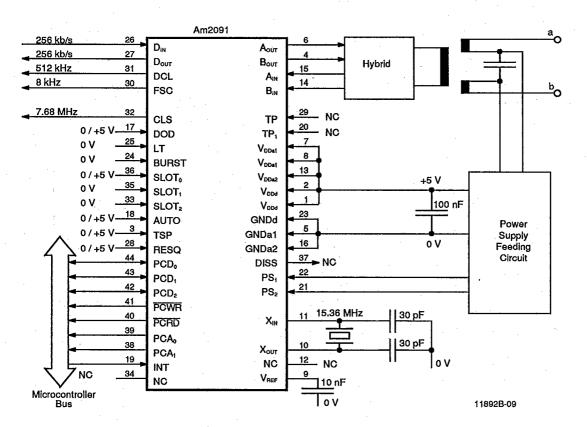

Figure 9. TE Mode

### **FUNCTIONAL DESCRIPTION**

The IEC-Q can be subdivided into three main blocks:

- -LIU, Line Interface Unit

- -SIU, System Interface Unit

- -REC, Receiver

The Line Interface Unit (LIU) contains the crystal oscillator and all of the analog functions, such as the A/D converter in the receive path and the pulse-shaping D/A converter and line driver in the transmit path.

The System Interface Unit (SIU) performs the connection between the U and the IOM interface. The data channels (2B+D) are transferred after scrambling or descrambling and speed adaption to the appropriate frame. A complete activation and deactivation procedure is implemented, which is directly controlled by activation and deactivation indications from U or IOM interface. State transition of the procedure depends on the reached status of the receiver (adaption and synchronization) and timing functions to watch fault conditions.

For maintenance functions two modes can be selected. In the automode all ANSI specified EOC procedure handling and executing is performed. In the transparent mode all bits are transferred transparent to the IOM interface without any internal processing.

The Receiver block (REC) performs the filter algorithmic functions using digital signal processing techniques. Modules for echo cancellation, pre- and post-equalization, phase adaption and frame detection are implemented in a modular multi-processor concept.

The B-version of the IEC-Q is available in a One-Chip (Am2091) and a Two-Chip (Am20911 Digital, Am20912 Analog) solution.

In the first part of this data sheet the overall function of the U transceiver (One- or Two-Chip) is described.

In the second part selected information is given for the digital and analog part.

### **IEC-Q INTERFACES U** Interface

**Table 4. U Frame Structure**

|                     | * .                 | Framing      | 2B+D   |                   |                   | verhead           | Bits (M1-N | 16)               |                   |

|---------------------|---------------------|--------------|--------|-------------------|-------------------|-------------------|------------|-------------------|-------------------|

|                     | Quat Positions      | 1–9          | 10-117 | 118s              | 118m              | 119s              | 119m       | 120s              | 120m              |

|                     | Bit Positions       | 1–18         | 19–234 | 235               | 236               | 237               | 238        | 239               | 240               |

| Super<br>Frame<br># | Basic<br>Frame<br># | Sync<br>Word | 2B+D   | Mil               | M2                | МЗ                | M4         | M5                | M6                |

| 1                   | 1                   | ISW          | 2B+D   | eoc <sub>at</sub> | 60C ₹             | 90C <sub>43</sub> | act        | 1                 | 1                 |

|                     | 2                   | sw           | 2B+D   | 600 qu            | eocit             | 60C <sup>15</sup> | deact.     | . 1               | febe              |

|                     | 3                   | sw           | 2B+D   | eoc <sub>ia</sub> | 60CH              | e00 <sub>5</sub>  | 1 ps2      | crc <sub>1</sub>  | crc <sub>2</sub>  |

|                     | 4                   | sw           | 2B+D   | 60C l6            | eoc,,             | 60C <sup>18</sup> | 1 ntm      | crc <sub>3</sub>  | crc <sub>4</sub>  |

|                     | 5                   | sw           | 2B+D   | eoc <sub>al</sub> | 90C <u>a2</u>     | 60C s3            | CSO        | crc <sub>5</sub>  | crc <sub>6</sub>  |

|                     | 6                   | sw           | 2B+D   | 60C qu            | 60C <sup>II</sup> | 60C <sup>15</sup> | 1          | crc <sub>7</sub>  | crc <sub>8</sub>  |

|                     | 7                   | sw           | 2B+D   | 90C <sub>B</sub>  | еоси .            | eoc <sub>15</sub> | 1          | crc <sub>9</sub>  | crc <sub>10</sub> |

|                     | 8                   | sw           | 2B+D   | 60C <sup>16</sup> | eoc,,             | 60C 16            | 1          | crc <sub>11</sub> | CrC <sub>12</sub> |

| 2,3                 |                     |              | ø      |                   |                   |                   | 1 1        |                   |                   |

NT-to-LT LT-to-NT direction

Reserve = reserve bit for future standard; set = 1

EOC =

Embedded operations channel Address bit Data/message indicator Information (data/message) dm

isw Inverted Sync Word Sync Word

SW

2B1Q Superframe Technique & Overhead Bit Assignments (8 x 1.5 ms "Basic Frames" = 12 ms Superframe)

act

= activation bit

ps1, ps2 = power status bits ntm = Nt1 in Test Mode bit

= cyclic redundancy check covers 2B+D & M4 = far end block error bit crc

febe

= cold start only CSO

deact = deactivation

### **U Interface Maintenance Channel**

### Embedded Operation Channel (EOC)

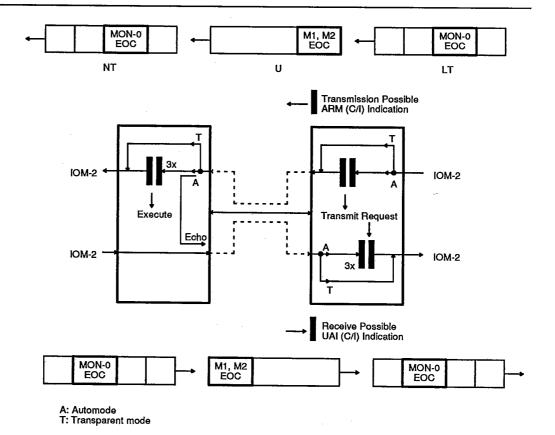

The EOC protocol operates in a repetitive command or response mode with a triple last look and master function on the network side.

All messages are latching. That is, they will be continually executed until an RTN (return to normal) message appears.

Figure 10. EOC Procedure

11892B-12

**Table 5. Frame and Functions**

T-75-15

|            |               |     | EOC              |     |                                    |     |     |    |    |           |                           |    |         |     |                   |

|------------|---------------|-----|------------------|-----|------------------------------------|-----|-----|----|----|-----------|---------------------------|----|---------|-----|-------------------|

|            | ddre<br>Field |     |                  | 1   | Information (o)rigin (d)estination |     |     |    |    |           | (o)rigin<br>(d)estination |    | Message |     |                   |

| <b>a</b> 1 | <b>a2</b>     | а3  | Indicator<br>d/m | 11  | 12                                 | 2 1 | 3 i | 14 | 15 | <b>i6</b> | 17                        | 18 | LT      | NT  |                   |

| 0          | 0             | 0   |                  |     |                                    |     |     |    |    |           |                           |    |         |     | NT Address        |

| 1          | 1             | 1 - |                  |     | -1                                 |     |     |    |    |           |                           |    |         |     | Broadcast Address |

|            |               |     | 1                | 1   |                                    |     |     |    |    |           |                           |    |         |     | Message           |

|            |               |     | o                |     |                                    |     |     |    |    |           |                           |    | ļ       |     | Data              |

|            |               |     | 1                |     | , .                                | ı   | 0   | 1  | 0  | 0         | 0                         | 0  |         | d   | LBBD              |

|            |               |     | 1                | 0   | ,                                  | l   | 0   | 1  | 0  | 0         | 0                         | 1  | 0       | d   | LB1               |

|            |               |     | . 1              | 0   | ) :                                | ı   | 0   | 1  | 0  | 0         | 1                         | 0  | 0       | d   | LB2               |

|            |               |     | 1                | 1.0 | ) . ·                              | l   | 0   | 1  | 0  | 0         | 1                         | 1  | 0       | ď   | RCC               |

|            |               |     | 1                | 0   | ).                                 | i   | 0   | 1. | 0  | 1         | 0                         | 0  | 0       | d   | NCC               |

|            |               |     | 1                | 1   |                                    | ı   | 1   | 1  | 1  | 1         | 1                         | 1  | 0       | d   | RTN               |

|            |               |     | 1 1              | 0   | ) (                                | )   | 0   | 0  | Ö  | 0         | 0                         | 0  | d/o     | o/d | Н                 |

|            |               |     | 1 . 1            | 1   | (                                  | )   | 1   | 0  | 1  | 0         | 1                         | 0  | d       | o . | UTC               |

RTN = Return to Normal

UTC = Unable to Comply Ack

NCC = Notify of Corrupted CRC

RCC = Request Corrupt CRC

Releases all outstanding EOC controlled operations; reset of EOC processor to initial state.

Validates the receipt of an EOC message, but the EOC message is

not in the menu of NT.

RCC = Request Corrupt CRC

H = Hold State

LBBD = Loopback B1, B2 and D

LB1/LB2 = Loopback Channel (B1 or B2)

Request within NT/SBCX. Request within NT/IEC-Q.

Only EOC frames with data/message indicator set to 1 (message) are able to evaluate; otherwise, a UTC message will be replied.

### **NT Automode**

For NT Automode configuration, every EOC message will be recognized and executed after receiving three identical consecutive EOC frames with correct NT address 000 or broadcast address 111. All received EOC frames are echoed back in the next transmitted EOC frame (0.75 ms frame delay) except:

#### Wrong address

22

In this case, the HOLD state message with NT address will be transmitted until a correctly addressed message is received.

#### Message not executable

A UTC message is transferred back after the third non-executable identical received message.

For test purposes, all EOC frames are transmitted via the IOM-2 Monitor channel, after the third correct reception.

### **NT Transparent Mode**

For NT Transparent Mode, the received EOC frame will not be analyzed or executed but rather transmitted downstream to the IOM-2 Monitor channel. In the upstream direction, the last incoming EOC code from the IOM-2 Monitor channel is used for transmission.

### LT Automode

In the LT Automode, EOC frames to be sent are taken from the IOM-2 Monitor channel and are continually transmitted until a new EOC frame is to be sent. After POWER DOWN, RESET or during start procedure, an RTN (return to normal) message is transmitted. Every new transmit request will enable the return message. The return message upstream via IOM-2 is a single transmission of an accepted EOC frame. Every EOC frame will be accepted only after first detecting 3 identical consecutive EOC frames and if the new EOC frame is different from the previously accepted one.

### LT Transparent Mode

For LT Transparent Mode the transmit procedure corresponds to the LT automode. In the receive direction, the IEC-Q is transparent to every EOC frame.

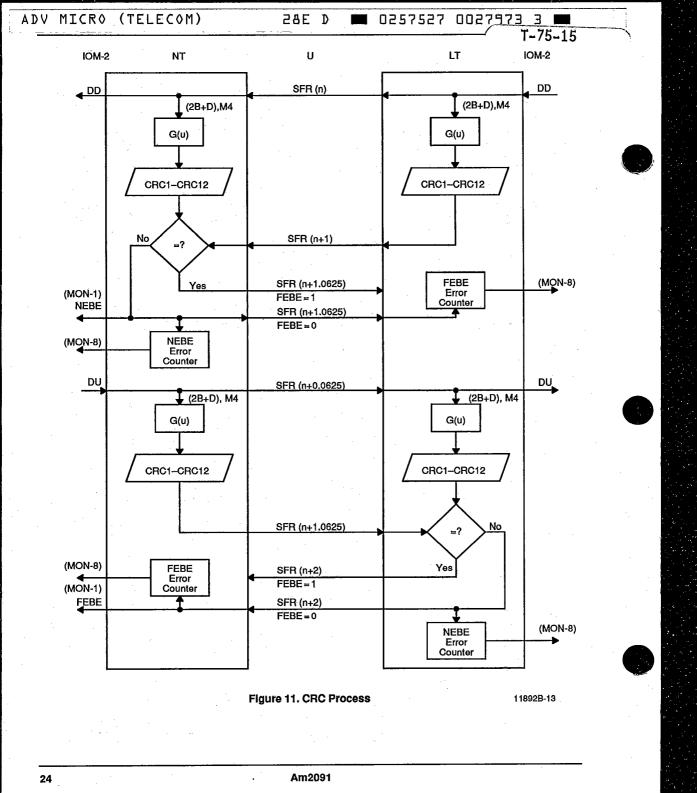

#### **CRC Process**

An error monitoring function is implemented covering the 2B+D and M4 data transmission of a U-superframe by a Cyclic Redundancy Check (CRC).

The computed polynomial is:

$$G(u) = u^{12} + u^{11} + u^3 + u^2 + u + 1$$

(+ modulo 2 addition)

The generated check digits (CRC bits CRC1, CRC2,..., CRC12) from the data are transmitted in the following U-superframe after the data transmission (CRC1 most significant bit). The receiver will compute the CRC of the received 2B+D and M4 data and a comparison will be done with the received CRC bits generated by the transmitter.

A CRC error will indicate a block error: FEBE (Far End Block Error) or NEBE (Near End Block Error) are set to 0 (Error) depending on the upstream or downstream direction.

The FEBE bit will be placed in the next available U-superframe transmitted to the originator.

The IEC-Q contains two error counters clocked by the far end or near end error indication.

The maximum counter value is 255; a reset is performed either during activation of the U interface or after read out. Both counter values can be read out via the Monitor channel (MON-8) of the IOM-2 interface. In the NT mode, block error indications are issued additionally by a MON-1 message every time an error has occurred.

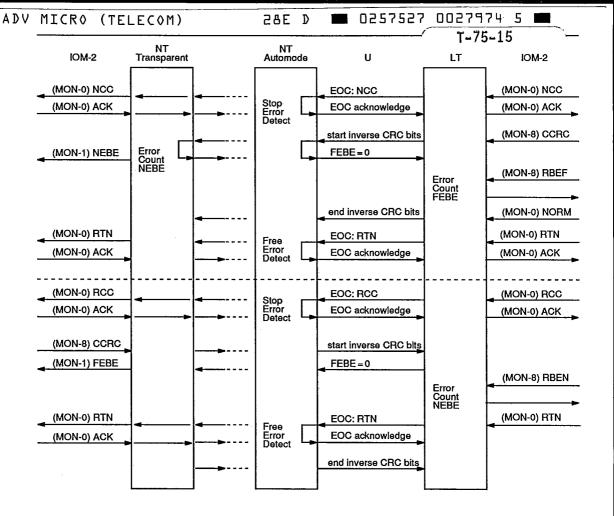

### Corrupted CRC (CCRC)

Data fault conditions can be generated for testing of the CRC procedure by manipulating the CRC reset.

A Request of Corrupted CRC (RCC) will invert the transmitted CRC bits.

The Notify of Corrupted CRC (NCC) causes the received CRC bits to be corrupted. In both test modes the error counters in the addressed chip are stopped and error indications via IOM-2 interface are retained.

In the transparent mode the EOC messages will pass through the chip without execution. There is no suppression of error counter and error messages towards the IOM interface.

Figure 12. Corrupted CRC test

Am2091

11892B-14

rom\_\_\_\_

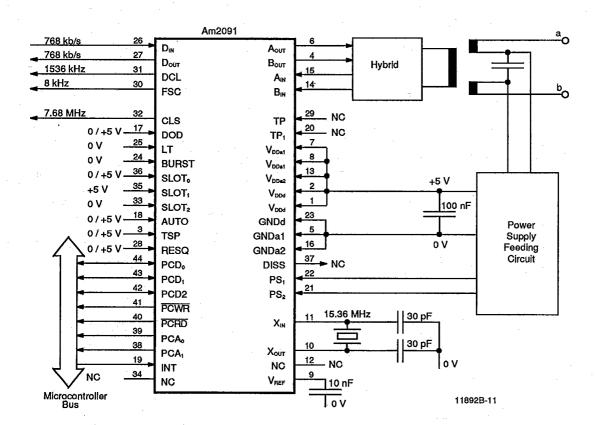

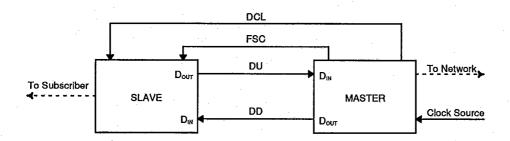

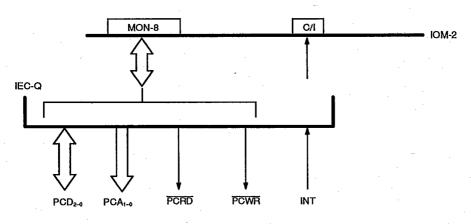

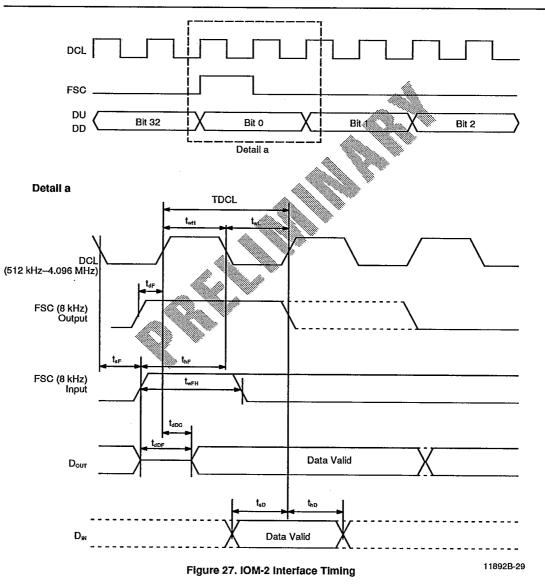

#### IOM-2 Interface

The IOM-2 interface is viewed as a standard interface that interconnects different modules together in a terminal. The interface is synchronized by frame and data clock signals supplied by a master clock source. The definition of master or slave mode depends on whether the timing for the interface is received or supplied by the device.

The IOM-2 interface consists of four physical connections. Two lines are for the transmission of data, one for each direction. The other two lines are for the frame and data clocks (see Figure 13).

DU Data Upstream—Transmission of data from the subscriber side to the exchange side.

- DD Data Downstream—Transmission of data from the exchange side to the subscriber side. T-75

- DCL Data Clock—Twice the data transmission frequency on DU and DD.

- FSC Frame Synchronization Clock—Resets the bit counter at the start of each frame.

The downstream and upstream directions are always with respect to the exchange. From the device point of view, these connections can also be named  $D_{\text{IN}}$  and  $D_{\text{OUT}}$ , referring to the reception or transmission of data, respectively.

Figure 13. IOM-2 Interface Signals

11892B-15

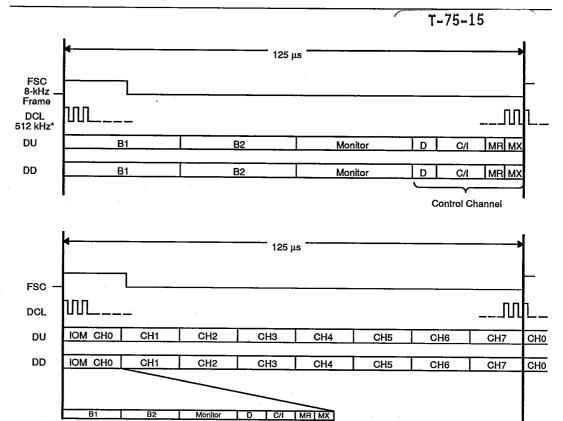

Figure 14. IOM-2 Interface Multiplexed Frame Structure (2.048 kb/s)

B1, B2: Circuit switched voice/data

D: D channel for signaling and packet switched data

C/l: Command/indication bits for control

MR, MX: Monitor handshake bits

11892B-16

\*DCL is programmable for values from 512 kHz to 4.096 MHz.

### **IOM-2 Interface Maintenance Functions**

### Control/Indication Channel

The Control/Indication channel (C/I channel) is used to control the operational status of the IEC-Q and to issue corresponding indications.

In general, commands (on  $D_{IN}$ ) have to be applied continuously as long as the required action is needed.

A command is validated by the IEC-Q if it has been detected in two subsequent IOM frames (double last look criterion). Indications (on Dour) are issued by the IEC-Q as long as no other indication has to be forwarded. They are not strictly state oriented.

Table 6. C/I Channel Codes

| Table 0. 0/1 Charlines Codes |      |          |      |               |  |  |  |  |  |  |  |

|------------------------------|------|----------|------|---------------|--|--|--|--|--|--|--|

| Code                         | NTI  | Mode     | LT   | Mode          |  |  |  |  |  |  |  |

| Code                         | ĺn   | Out      | In   | Out           |  |  |  |  |  |  |  |

| 0000                         | TIM  | DR       | DR   | <del></del> . |  |  |  |  |  |  |  |

| 0001                         | RES  | _        | RES  | DEAC          |  |  |  |  |  |  |  |

| 0010                         | _    | FJ       | _    | FJ            |  |  |  |  |  |  |  |

| 0011                         |      | _        | LTD  | HI            |  |  |  |  |  |  |  |

| 0100                         | El1  | - El1    | RES1 | RSY           |  |  |  |  |  |  |  |

| 0101                         | SSP  |          | SSP  | El2           |  |  |  |  |  |  |  |

| 0110                         | DT   | INT      | DT   | INT           |  |  |  |  |  |  |  |

| 0111                         | _    | PU       | _    | UAI           |  |  |  |  |  |  |  |

| 1000                         | AR   | AR       | AR   | AR            |  |  |  |  |  |  |  |

| 1001                         | _    |          |      | ARM           |  |  |  |  |  |  |  |

| 1010                         | ARL  | ARL      | ARL  | _             |  |  |  |  |  |  |  |

| 1011                         | _    | <u> </u> |      | El3           |  |  |  |  |  |  |  |

| 1100                         | Al - | . Al     | _ `  | AI ·          |  |  |  |  |  |  |  |

| 1101                         |      |          |      | LSL           |  |  |  |  |  |  |  |

| 1110                         | _    | AIL      | _    | _             |  |  |  |  |  |  |  |

| 1111                         | DI   | DC       | DC   | DI            |  |  |  |  |  |  |  |

| AI<br>AR<br>ARL<br>ARM<br>DC<br>DR<br>DEAC<br>DI<br>DT<br>EII<br>EI2<br>EI3<br>HINT<br>LTD<br>LSL | Activation Indication Activation Request Activation Request Local Loop Activation Request Maintenance bits Deactivation Confirmation Deactivation Request Deactivation Accepted Deactivation Indication Data Through (test mode) Error Indication 1 (error on U) Error Indication 2 (error on S/T) Error Indication 3 (timeout 15 s: error on U) High Impedance (set by PFOFF) Interrupt (set by power controller) LT Disable (control of pin DISS) Loss of Signal Level on U |

|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HĻ                                                                                                | High Impedance (set by PFOFF)                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| INT                                                                                               | Interrupt (set by power controller)                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| LSL                                                                                               | Loss of Signal Level on U                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| UAI                                                                                               | U Activation Indication                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| RES                                                                                               | Circuit Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RES1                                                                                              | Receiver Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RSY                                                                                               | Loss of Synchronization                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| PU                                                                                                | Power Up                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| SSP                                                                                               | Test Mode (Send Single Pulses)                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TIM                                                                                               | Timing Required                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| FJ                                                                                                | Frame Jump                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

#### **IOM-2 MONITOR Channel**

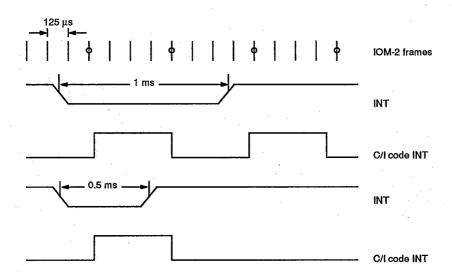

The MONITOR (MON) channel is used for the transfer of messages and data related to maintenance functions. The MX and MR bits in the fourth octet of the IOM frame are used for flow control (active Low).

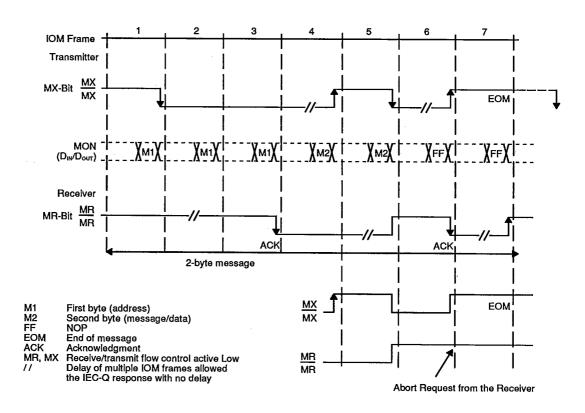

### Transfer Procedure

The MON channel procedure allows a full duplex transmission. The MX bit is used to start or indicate the transmission of data on the MON channel. The receipt of data is acknowledged making use of the MR bit in the reverse direction.

The procedure allows the transmission of two-byte messages or data. The first byte contains the address and possibly data while the second byte contains a message or data.

The MON channel is idle when the MX bit is inactive in two or more consecutive frames. In this case, the MR bit in the reverse direction is inactive too. In the MON channel binary 1s are transmitted. The transmission of the first byte M1 is started by the transmitter with the transition of the MX bit from inactive to active in the same frame. This is allowed only if the MR bit in the reverse direction has been in the inactive state for at least two consecutive frames.

The receiver confirms the start of the transfer procedure by setting the MR bit active if the transmitted bytes are identical in the first two received frames. It acknowledges the receipt of byte M1 by keeping the MR bit in the active state for at least one more frame.

In the frame following the transition of the MR bit from inactive to active, the transmitter starts the transfer of the second byte M2 with the transition of the MX bit from active to inactive. The MX bit stays in the inactive state for only one frame if the receipt of byte M1 has been acknowledged by the receiver.

In the next frame the receiver sets the MR bit inactive and acknowledges the receipt of byte M2 by a transition of the MR bit from inactive to active one frame later.

The transmitter sets the MX bit inactive and keeps it in the inactive state for at least one more frame. The presence of the MX bit in the inactive state for two or more consecutive frames indicates the end of the message (EOM).

In the frame following the transition of the MX bit from active to inactive, the receiver sets the MR bit inactive. As it detects the EOM, it keeps the MR bit in the inactive state until a new message is received.

If the received bytes are not identical and no EOM is detected, the receiver sends no acknowledgment to the transmitter; that is, it sets the bit inactive and keeps it in this state until it has detected the response of the transmitter (MX bit inactive in at least two frames) and until a new transfer procedure is started. In general, after starting the receive procedure, the MR bit stays in the inactive state for at least two consecutive frames, the transmitter is requested to abort transmission (MX bit inactive) and to re-transmit the entire message.

If an EOM is detected the receiver sets the MR-bit inactive, that is, no acknowledgment is issued and the MR bit is kept in this state until a new transfer procedure is started. The bit has to be set inactive at the latest one frame after the MX bit has been inactive two times. Furthermore, the receiver checks after the receipt of EOM to see whether 2 bytes have been transferred. If this is not the case the whole message is disregarded by the receiver.

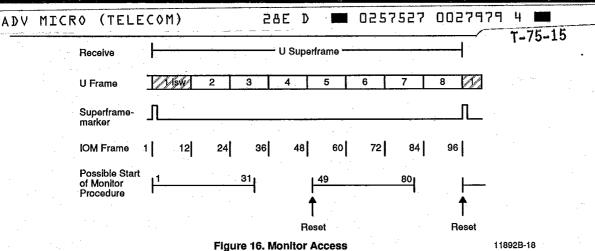

To allow the start of a new cycle of MON messages every 6 ms, and to prevent a hang-up situation under failure conditions, the transmit procedure is reset to its idle state every 6 ms. If this happens when a transfer procedure is being performed, the transmitter of the IEC-Q sets the MX bit inactive two times to assure that the receiver enters the idle state too. If a transmit procedure is reset the message is lost. To prevent this situ-

ation the transmitter does not start a transfer procedure during a period of time corresponding to 16 IOM frames before the superframe indication (IOM frames 81–96) or 6 ms after (IOM frames 33–48). In this case the receiver is requested to delay the receive procedure for not more than four IOM frames compared to the timing diagram in Figure 15.

The receive procedure is also reset to its idle state every 6 ms. If this happens when a receive procedure is being performed the message may be lost because the generation of an abort request can not be guaranteed. To prevent this situation the receiver does not start a receive procedure during a period of time corresponding to 16 IOM frames before the superframe indication or 6 ms after. In this case the transmitter is requested to delay the transmit procedure for not more than five IOM frames compared to the timing diagram in Figure 15.

Figure 15. Transfer Procedure

11892B-17

### Message Structure

Table 7, MON-0

#### **Automode**

| 0 0 0 0 | a.a a        | 1   | 8 8 8 8 8 8 8 |

|---------|--------------|-----|---------------|

| 0       | EOC<br>addr. | d/m | EOC Code      |

| EOC<br>Code          | N                                     | Т. | LT                        |                 |  |  |

|----------------------|---------------------------------------|----|---------------------------|-----------------|--|--|

| Hex                  | D                                     | U  | ם                         | U               |  |  |

| 50<br>51<br>52<br>54 | LBBD 1)<br>LB1 1)<br>LB2 1)<br>NCC 1) |    | LBBD<br>LB1<br>LB2<br>NCC |                 |  |  |

| 53<br>FF             | RCC 1)<br>RTN 1)                      |    | RCC<br>RTN                |                 |  |  |

| 00<br>AA<br>zz       | H 1)                                  |    | Н                         | H<br>UTC<br>ACK |  |  |

#### Notation:

zz code identical to corresponding command

U upstream (TE -> LT)

D downstream (LT -> TE)

downstream (LT -> TE)

d/m data/message indicator: 1; message

0: data

Notes: 1. These indications are issued for test purposes only. They are disregarded by the SBCX but acknowledged according to the procedure specified in the MON-1 Indications section.

The EOC address of the NT is 000. The NT also reacts to the broadcast address 111. The MON-0 structure is used for EOC related messages. The EOC address, the data/message (d/m) indicator and the EOC code are as specified for the U interface.

Commands (messages on D<sub>IN</sub>) are used in the LT mode only. They may be passed at any moment in time and need to be transferred only once according to the procedure specified in the MON-1 Indications section. Code repetition is performed within the chip by the EOC processor. These commands are latched. That is, they are valid as long as they are not disabled explicitly by a "revalid as long as they are not disabled explicitly by a "realioned. That is, one command is allowed. That is, one command has to be acknowledged before a new one may be passed (valid for MON and for EOC channel).

Indications (messages on Dour) are used in the LT and NT mode. The validation (receipt of three identical consecutive messages) of received EOC messages is performed within the chip by the EOC processor. The EOC messages are issued across the MON channel every time a change has been detected in the EOC channel, but only when validated by the EOC processor (latched). In the NT mode these indications are issued for test purposes only.

### **Transparent Mode**

The MON-0 structure is used to transfer the 24 bits defined for the EOC channel in the automode (M1, M2, M3). They are passed in the same order as on the U interface making use of two 2-byte messages per superframe. The 2-byte message marked by the superframe indication transfers the first 12 bits of a superframe. The second 2-byte message is transferred 6 ms later.

These bits are monitored continuously; that is, every 6 ms 12 bits are passed across the MON channel in both the transmit and the receive direction. The IEC-Q doesn't perform any processing of the bits and treats them in a completely transparent manner.

#### Table 8, MON-1

### Automode and transparent mode

| 0 0 0 1 | x | 8888     | m m m m |

|---------|---|----------|---------|

| 1       |   | S/Q Code | M Bits  |

| S/Q<br>Code | 1    | NT   | LT |   |  |  |

|-------------|------|------|----|---|--|--|

|             | D    | U    | D  | U |  |  |

| 0000        |      |      |    |   |  |  |

| 0001        |      | ST   |    |   |  |  |

| 0010        | STP  |      | į  |   |  |  |

| 0100        | FEBE |      | ļ  |   |  |  |

| 1000        | NEBE |      |    |   |  |  |

| 1100        | FNBE |      |    |   |  |  |

| 1111        |      | NORM |    |   |  |  |

| M bits |      |  |

|--------|------|--|

| 1xx0   | NTM  |  |

| 1111   | NORM |  |

#### Notation:

upstream (TE -> LT)

D downstream (LT -> TE)

don't care

### Messages:

**FEBE** Far End Block Error

FNBE Far and Near End Block Error

NERE Near End Block Error NORM Return to Normal NTM NT Test Mode

Self Test Request NT

STP Self Test Pass

#### MON-1 indications

The MON-1 structure applies to the NT mode only and is used for indications corresponding to specific bits in the maintenance channel of the U interface and for S/Q channel related messages.

Indications related to the Q channel issued by the SBCX are transferred over the MON channel every time a change has been detected in the Q channel (latching). Block error indications (FEBE, NEBE and FNBE) are issued by the IEC-Q every time an error has occurred (non-latching); the response to a self test request (STP) is non-latching too.

All indications received by the IEC-Q during one superframe (12 ms) are passed over the MON channel in one block making use of one 2-byte message. Indications issued by the SBCX may be received with a different timing (for instance every 5 ms).

### Automode and transparent mode

| 0010 | d | d  | d   | d |   | d | d | d | d | d    | d | ď | d |

|------|---|----|-----|---|---|---|---|---|---|------|---|---|---|

| 2    |   | МЕ | its |   | 1 |   |   |   | М | 3its |   |   |   |

The MON-2 structure is used in both NT and the LT modes to transfer all the overhead bits except EOC and CRC. This corresponds to 12 bits passed in the same order as defined on the U interface and starting (first bit after the address bit) with the act bit:

| U Super-          | NT -     | > LT    | LT -> NT |         |  |  |

|-------------------|----------|---------|----------|---------|--|--|

| Frame<br>Position | position | control | position | control |  |  |

| M41               | act      | IEC-Q   | act      | IEC-Q   |  |  |

| M51               | 1        | MON-2   | 1        | MON-2   |  |  |

| M61               | 1        | MON-2   | 1        | MON-2   |  |  |

| M42               | ps1      | pin     | deact    | IEC-Q   |  |  |

| M52               | 1        | MON-2   | 1        | MON-2   |  |  |

| M62               | FEBE     | IEC-Q   | FEBE     | IEC-Q   |  |  |

| M43               | ps2      | pin     | 1        | MON-2   |  |  |

| M44               | ntm      | MON-1   | 1        | MON-2   |  |  |

| M45               | cso      | IEC-Q*  | 1        | MON-2   |  |  |

| M46               | 1        | MON-2   | 1        | MON-2   |  |  |

| M47               | 1        | MON-2   | 1        | MON-2   |  |  |

| M48               | 1        | MON-2   | 1        | MON-2   |  |  |

Note: \*set to 0

Mxy: Mx in frame y

In the transmit direction (on D<sub>IN</sub>) only the undefined bits marked with binary 1 may be controlled by making use of a MON-2 message. They are set to binary 1 after leaving a Power Down state. The transfer mode is latched; that is, the U bit transmits a given bit polarity as long as it is not changed by a new MON-2 message. No further processing is performed by the IEC-Q. The bits act, deact, FEBE and cso are always controlled by the IEC-Q itself. The ntm bit is controlled by the S chip making use of a MON-1 message. The bits ps1 and ps2 are defined by pins.

In the receive direction (on Dout) a MON-2 message defining all 12 bits is issued every time a change on at least 1 bit has been detected but not more often than once per superframe (12 ms interval). This is valid for all bits except the FEBE bit. In the LT mode, single block errors are not indicated autonomously, but may be read by making use of a local command (RBEN, RBEF). In the NT mode, single block errors are indicated by making use of a MON-1 message.

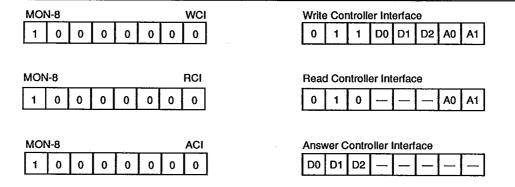

### Table 10. MON-8

### Automode and transparent mode

| 1000 | r 0 0 0  | 00000000                       |

|------|----------|--------------------------------|

| 8    | Reg. Ad. | Local Command/<br>Message/Data |

|   |           |                  | NT               | LT               |                  |

|---|-----------|------------------|------------------|------------------|------------------|

| r | Code C    | D                | Ü                | D                | υ                |

| 0 | 1111 0000 |                  | CCRC1            | CCRC             |                  |

| 0 | 1111 0100 |                  | LB1 <sup>1</sup> |                  |                  |

| O | 1111 0010 |                  | LB2 <sup>1</sup> |                  |                  |

| 0 | 1111 0001 |                  | LBBD1,3          |                  |                  |

| 0 | 1111 1111 |                  | NORM1            | NORM             |                  |

| 0 | 1111 1011 | •                | RBEN             | RBEN             |                  |

| 0 | 1111 1010 |                  | RBEF             | RBEF             | l .              |

| 0 | 1111 1000 |                  |                  | RPFC             |                  |

| 0 | 011d ddaa |                  | WCI <sup>2</sup> | WCI2             |                  |

| 0 | 010* **aa |                  | RCI <sup>2</sup> | RCI <sup>2</sup> | ١,               |

| 0 | ddd* **** | ACI <sup>2</sup> |                  |                  | ACI <sup>2</sup> |

| 0 | 00000000  |                  | RID              | RID              |                  |

Notation:

U upstream (TE → LT)

D downstream (LT -> TE)

1 binary 1

0 binary 0

a...a address controller interface to pin PCA

d...d data controller interface to pin PCD

Notes: 1. These codes are only used in the transparent mode.

2. See controller interface description.

3. TE mode only.

Commands:

CCRC Corrupt crc

LB1 Loopback Channel B1 request (within NT/IEC-Q) LB2 Loopback Channel B2 request (within NT/IEC-Q)

LBBD Loopback B1, B2, and D channel request

(within NT/IEC-Q)

NORM Return To Normal

RBEF Read Block Error Counter Far End RBEN Read Block Error Counter Near End

WCI Write Controller Interface

RCI Read Controller Interface

ACI Answer Controller Interface

RID Read Identification

RPFC Read Power Feed Current Value

The MON-8 structure is used for local functions. Commands (on D<sub>IN</sub>) concerning loopback and CRC may be passed at any time and need to be transferred only once. They are latched; that is, they are valid as long as they are not disabled explicitly by a NORM message, except the commands requesting the transfer of internal data which are non-latching.

In the case of the identification code, all data are set to 0:

IF = 00 design = 000000

59E D

(U Interface) (Reserved)

### **Test Loops**

For the test of the line cards, several test loops are provided which can be controlled from the exchange. In the complete loop all channels (2B+D) shall be transmitted back towards the transmitting station without modification. The data from the other end of the line is ignored. There are separate loops for single channels called individual B-channel loopbacks. The individual B-channel loopbacks. The individual B-channel loopback can provide per channel maintenance capabilities without totally disrupting service to the customer. All loops are transparent loops; that means all bits toward the loop are passed onward as well as looped back. Nevertheless, the NT receives this signal and remains synchronized.

### Switching an Analog Loop in the IEC-Q

The analog loop is closed in the IEC-Q as near to the U interface as possible. Using internal switches, the signal from the line driver is fed back directly to the input. It is a short-circuit between the pins Aout and Ain as well as between Bout and Bin. The input signal from the hybrid is ignored in this mode.

The analog loop mode is controlled via the IOM-2 C/I channel.

In an analog loop the transmit path is set to the LT mode and the receive path is set to the NT mode independently of the polarity of the LT pin.

# Switching the Complete Loop and the Individual B-Channel Loopback

The individual B-channel loopbacks are always closed in the IEC-Q. The complete loop can be closed in the IEC-Q NT-PABX and NT-TE modes. With internal switches the corresponding user data at Dour (2B+D or B1 or B2) are directly fed back into D<sub>IN</sub>. The control input (Monitor- and C/I-channel as well as MX- and MR-bit) is still read from the IOM-2 interface. Although these loops are closed by command from the exchange, the IEC-Q can still be deactivated by RES and SSP C/I- channel commands from the Layer 2 device.

In the NT the activation of an analog loop leads to the deactivation of all services initiated by the exchange. While the analog loop is activated the NT is not available for services, that is, a complete or an individual B-channel loopback can't be closed and a required CCRC shall not be carried out.

Figure 17. Test Loops Closed by the IEC-Q or Under its Remote Control

Analog

Loop

IEC-Q

Note: For transparent mode operation the EOC loop request is performed over the IOM-2 interface NT upstream by a MON-8 message.

DSC

ARL (C/I)

Am2091

11892B-19

28E D

0257527 0027983 6

T-75-15

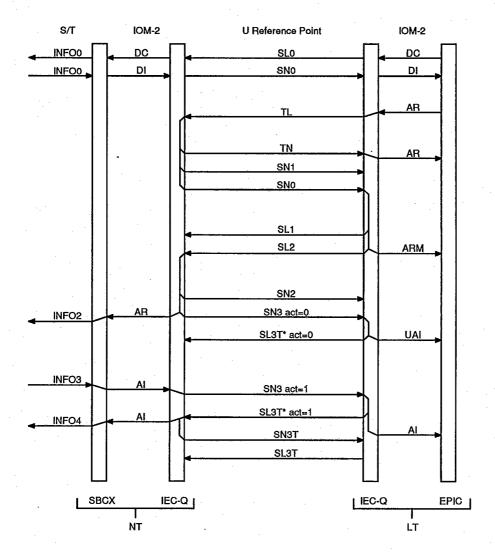

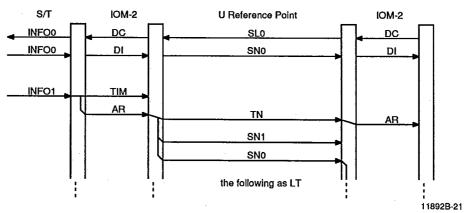

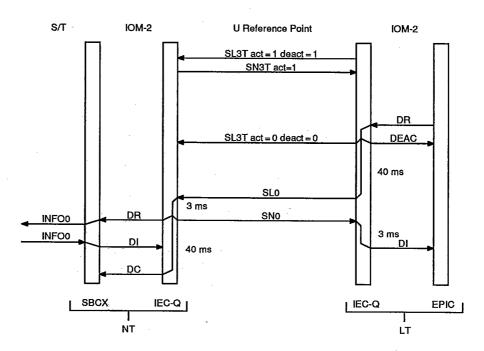

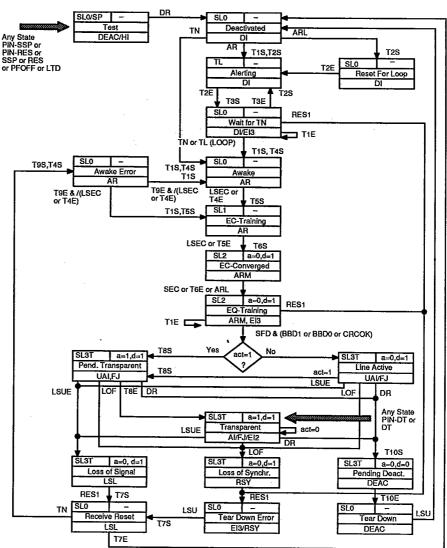

# ACTIVATION AND DEACTIVATION PROCEDURES

Activation can be initiated by either the LT or the NT side.

Deactivation is always initiated from the LT side.

Note: SL3 is generated by exchange at this time.

11892B-20

Figure 18. Activation From LT

34

Figure 19. Activation from NT

Figure 20. Deactivation Procedure

11892B-22

T-75-15

Table 11

| Signal | Synch Word (SW) | Superframe (ISW) | 2B+D      | M         |

|--------|-----------------|------------------|-----------|-----------|

| TN     | ±3              | ±3               | ±3        | ±3        |

| SN0    | no signal       | no signal        | no signal | no signal |

| SN1    | present         | absent           | 1         | 1         |

| SN2    | present         | absent           | 1         | 1         |

| SN3    | present         | present          | 1         | normal    |

| SN3T   | present         | present          | normal    | normal    |

| TL     | ±3              | ±3               | ±3        | ±3        |

| SLO    | no signal       | no signal        | no signal | no signal |

| SL1    | present         | absent           | 1 ]       | 1         |

| SL2    | present         | present          | . 0       | normal    |

| SL3*)  | present         | present          | 0         | normal    |

| SL3T   | present         | present          | normal    | normal    |

<sup>\*)</sup> SL3 is generated by exchange.

TL/TN alternate ±3 for 10 kHz tone. SNx signal from NT to LT. SLx signal from LT to NT.

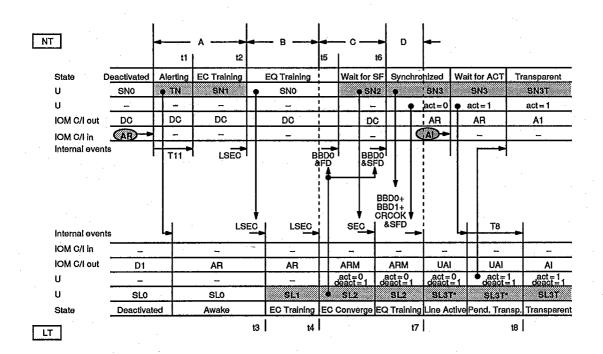

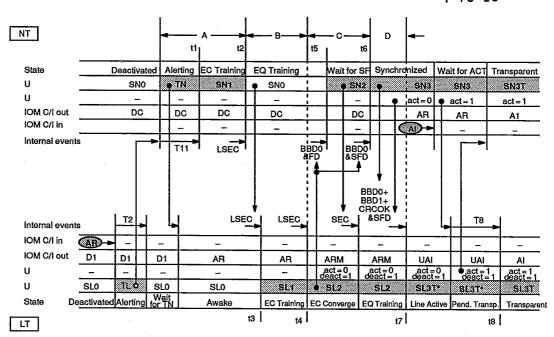

Figure 21. Activation from NT

11892B-23

36

<sup>\*</sup> SL3 is generated by exchange at this time.

Figure 22. Activation from LT

11892B-24

$t2-t3 \le 480 \text{ ms}$   $A+c \le 5 \text{ s cold start}$   $A+C \le 150 \text{ ms warm start}$   $B+D \le 10 \text{ s cold start}$  $B+D \le 150 \text{ ms warm start}$

<sup>\*</sup> SL3 is generated by exchange at this time.

Pin:

Function:

RESQ

TSP

11892B-25

0

0

PIN-RES

1

1

PIN-SSP

0

1

PIN-DT

Figure 23. State Transition Diagram NT, NT-PABX Modes

Am2091

38

# **Explanation for NT State Diagram**

The following commands or events are used for the transition:

# C/I Channel (on DIN)

#### Al-Activation Indication

The SBCX issues this indication to announce that the receiver is synchronized. The IEC-Q informs the network side by setting the act bit to 1.

### AR-Activation Request

INFO1 has been received by the SBCX (NT mode only, not relevant in NT-PABX mode) and the IEC-Q is requested to start the activation process by sending the wake-up signal TN.

# ARL—Activation Request Local Loopback

The IEC-Q is requested to operate an analog loopback (close to the U interface) and to begin the start-up sequence by sending SN1 (without starting timer T1). This command may be issued only after the IEC-Q has been reset by making use of the C/I channel code RES or the pin reset RESQ. This assures that the EC and EQ coefficient-updating algorithms converge correctly. The ARL command has to be issued continuously as long as the loopback is required.

### DI-Deactivation Indication

This indication is used during a deactivation procedure to inform the IEC-Q that timing signals are not needed any more and that the IEC-Q may enter the deactivated (power-down) state. The DI indication has to be issued by the SBCX continuously until the IEC-Q has answered with the DC code.

#### DIN=0-Binary 0 polarity on DIN

In the NT mode this asynchronous signal requests the IEC-Q when staying in the deactivated state to enter the power-up state and to provide timing signals on the IOM interface. Hereafter, binary 0s in the C/I channel (code TIM 0000 or any other code different from DI 1111) maintain the IOM interface activated.

# DT-Data Through

This unconditional command is used for test purposes only and forces the IEC-Q into a state equivalent to the

transparent state. The far-end transceiver is assumed to be in the same condition.

# T-75-15

#### El1—Error Indication 1

The SBCX indicates an error condition on its receive side (loss of frame alignment or loss of incoming signal). The IEC-Q informs the network side by setting the act bit to 0 thus indicating that transparency has been lost.

#### RES-Reset

Unconditional command which resets the whole chip; especially the EC and EQ coefficients are set to 0. For cold start the reset code should be applied for a period of time of at least 8 IOM frames (1 ms).

### SSP-Send Single Pulses

Unconditional command which requests the transmission of single pulses on the U interface.

#### TIM—Timing

In the NT mode the IEC-Q is requested to continue providing timing signals and not to leave the power upstate. In the NT-PABX mode the IEC-Q is requested to enter the power-up state or not to leave it.

#### **Pins**

#### Pin-Res-Pin-Reset

Corresponds to pin RESQ. The functionality of this pin is the same as for the C/I code RES.

#### Pin-SSP—Pin-Send Single Pulses

Corresponds to pin TSP. The functionality of this pin is the same as for the C/I code SSP.

#### Pin-DT-Pin-Data Through

This function is activated when both pins RESQ and TSP are active (RESQ=0 and TSP=1). The functionality is the same as for the C/I code DT.

### Events related to the U Interface

#### act=0/1—act Bit Received from Network Side

act=1 requests the IEC-Q to achieve transparency of the transmission in both directions. As transparency in receive direction (U interface to IOM) is already performed when the receiver is synchronized, the receipt of act=1 establishes transparency in transmit direction (IOM to U interface) too. In the case of loopbacks however, transparency in both directions of transmission is performed when the receiver is synchronized.

$\operatorname{act} = 0$  indicates that the network side has lost transparency.

# deact=0/1—dea Bit Received from the Network Side

deact=0 informs the IEC-Q that a deactivation procedure has been started by the network side.

97 🚃

deact=1 reflects the case when deact=0 was detected by mistake for example, due to transmission errors, and allows the IEC-Q to recover from this situation.

# LOF-Loss of Framing on the U Interface

# LSEC—Loss of Signal Level behind the Echo Canceller

Internal signal which indicates that the Echo Canceller has converged.

# LSU-Loss of Signal level on the U Interface

This signal indicates that a loss of signal level of a duration of 3 ms has been detected on the U interface. This short response time is relevant in all cases where the NT waits for a response (no signal level) from the network side, that is, after a deactivation has been announced (receipt of deact=0), after the NT has lost framing, and after timer T1 has elapsed.

# LSUE—Loss of Signal level on the U Interface (Error condition)

This signal indicates that a loss of signal level of a duration of 588 ms has been detected on the U interface. This long response time (see also LSU) is valid in all cases where the NT is not prepared to lose signal level; that is, the LT has stopped transmission because of loss of framing, an unsuccessful activation, or interruption of the transmission line.

### SFD—Superframe Detected

#### FD-Frame Detected

TL—Tone (wake-up signal) received from the LT The IEC-Q is requested to start the activation process.

# BBD0/1—Binary 0s or 1s Detected in the B and D Channels

This internal signal indicates that for a period of time of 6–12 ms, a continuous stream of binary 0s or 1s (analog loopback) has been detected. It is used as a criterion for receiver synchronization (SL2 from the network side or SN3 in the case of an analog loopback detected correctly).

#### **Timers**

The start of timers is indicated by TxS, the expiration by TxE. The following timers are used:

|     | (ms)  |                        | (state)               |

|-----|-------|------------------------|-----------------------|

| T1  | 15000 | activation control     |                       |

| T11 | 9     | TN transmit            | alerting              |

| T12 | 5500  | supervisor EC converge | EC training           |

| T13 | 15000 | frame synchronization  | pending receive reset |

| T7  | 40    | hold time              | receive reset         |

| T14 | 0,5   | hold time              | pending timing        |

The following indications or signals are transmitted:

# C/I Channel (on Dout)

T-75-15

#### AI—Activation Indication

The IEC-Q has established transparency of transmission in the direction IOM to U interface. In the NT mode, the SBCX is requested to send INFO4 and to achieve transparency of transmission in the direction IOM to S/T interface. In the NT-PABX mode, the AI code signals that the IEC-Q is "ready for sending."

# AIL—Activation Indication Loopback

The IEC-Q has detected act=1 while loopback 2 is still established. In the NT mode, the SBCX is requested to send INFO4 (if a transparent loopback 2 is to be implemented) and to keep loopback 2 established. In the NT-PABX mode, the AIL code indicates that act=1 has been detected and that loopback 2 is still established within the IEC-Q.

# AR—Activation Request

The U receiver has synchronized on the incoming signal. In the NT mode, the SBCX is requested to start the activation procedure on the S/T interface by sending INFO2. In the NT-PABX mode, the AR code on Dout has to be answered by the AI code on Din.

# ARL—Activation Request Loopback

The IEC-Q has detected a loopback 2 command in the EOC channel and has established transparency of transmission in the direction IOM to U interface. In the NT mode, the SBCX is requested to send INFO2 (if a transparent loopback 2 is to be implemented) and to operate loopback 2. In the NT-PABX mode, the ARL code indicates that loopback 2 is in operation within the IEC-Q.

# DC-Deactivation Confirmation

Idle code on the IOM interface. Normally the IEC-Q stays in the power-down mode, but an activation procedure may have been started from the network side as well.

# DR—Deactivation Request

The IEC-Q has detected a deactivation request command from the network side or stays in a test mode. In the NT mode, the SBCX is requested to start the deactivation procedure on the S/T interface by sending INFOO. In the NT-PABX mode, the DR code on Dout has to be answered by the DI code on DIM.

# El1—Error Indication 1

The IEC-Q has entered a failure condition (loss of framing on the U interface or expiration of timer T1).

40

#### FJ-Frame Jump

This indication is relevant only in the NT-PABX mode and signals that either a data buffer overflow/underflow has been detected or a phase jump of one of the IOM timing signals DCL or FSC has occurred. The FJ code is issued for a period of 1.5 ms.

# Signals Transmitted on the U Interface

The signals SNx, TN and SP transmitted on the U interface are defined in this section. The following states are used:

#### Alerting

The wake-up signal TN is transmitted for a period of T11 either in response to a received wake-up signal TL or to start an activation procedure on the network side.

# Alerting IOM Awaked

This state is entered when a wake-up tone was received in the receive reset state and the deactivation procedure on the user side was not yet finished. The transmission of wake-up tone TN is started.

#### Analog Loopback

Upon detection of binary 1s for a period of 6–12 ms and of the superframe indication the analog loopback state is entered and transparency is achieved in both directions of transmission. This state can be left making use of any unconditional command. However, only the C/I channel code RES or pin RESQ should be used. This assures that the EC and EQ coefficients are set to zero and that for a subsequent normal activation procedure the receiver updating algorithms converge correctly.

#### Deactivated (full reset)

This state corresponds to the power-down or low-power consumption mode; that is, no timing signals are delivered on the IOM interface and no signal is sent on the U interface. The IEC-Q waits for a wake-up signal TL from the network side or a wake-up signal (DIN=0) from the user side to start an activation procedure. In the NT-PABX mode (where timing signals are delivered from the PABX side) the C/I channel codes AR and TIM are valid too.

#### EC Training

The signal SN1 is transmitted on the U interface to allow the NT receiver to update the EC coefficients. The automatic gain control (AGC), the timing recovery and the EQ updating algorithm are disabled. The EC training state is left when the EC has converged (LSEC) or when timer T12 has elapsed.

# EC Training IOM Awaked

This state is entered if the transmission of signal SN1 has to be started and the deactivation procedure on the user side is not yet finished.

#### EQ Trainina

The receiver waits for signal SL1 or SL2 to be able to update the AGC, to recover the timing phase, to detect the synch word (SWD) and to update the EQ coefficients. The EQ training state is left upon detection of binary 0s in the B and D channels for a period of 6–12 ms corresponding to the detection of SL2.

#### Error S/T

Loss of framing or loss of incoming signal has been detected on the S/T interface (EI1). The network side is informed by setting the act bit to 0 (loss of transparency on the user side). The following codes are issued on the C/I channel:

- -normal activation or single channel loopback: AR

- -loopback 2: ARL

#### IOM Awaked

Timing signals are delivered on the IOM interface. The IEC-Q enters the deactivated state again upon detection of the C/I channel code DI (idle code).

#### Pending Deactivation

The IEC-Q waits for the receive signal level to be turned off (LSU) to enter the receiver reset state and start the deactivation procedure.

### Pending Receive Reset

This state is entered upon detection of loss of framing on the U interface or expiration of timer T1. This failure condition is signaled to the network side by turning off the transmit level (SN0). The IEC-Q then waits for a response (no signal level LSU) from the network side to enter the receive reset state.

### Pending Timing

In the NT mode this state assures that the C/I channel code DC is issued four times before the timing signals on the IOM interface are turned off.

# Receive Reset

This state is entered upon detection of a deactivation request from the network side, after a failure condition on the U interface (loss of signal level LSUE) or through the pending reset state upon expiration of timer T1 or loss of framing.

No signal is transmitted on the U interface, especially no wake-up signal TN, and the SBCX is requested to start the deactivation procedure on the user side (DR). Timer T7 assures that no activation procedure is started from the user side for a minimum period of time of T7.

The state is left only after completion of the deactivation procedure on the user side (receipt of the C/I channel code DI), unless a wake-up tone is received from the network side.

Synchronized

When the IEC-Q has reached this state, it informs the network side by sending the superframe indication (inverted synchword) and the user side by issuing the C/I channel codes AR or ARL. The loopback commands decoded by the EOC processor control the output of indications and transmit signals: