**CMOS**

#### **Features**

- High Accuracy Programmable Gain Amplifiers

- ± 0.02 dB Accuracy (Typical)

- 31.5 dB Range In 0.5 dB Steps

- Software Programmable Group Delay Equalizer For Leased and Dial-Up Lines

- High Dynamic Range over 90 dB

- . On-Chip Anti-Aliasing Filters

- On-Chip E<sup>2</sup>PROM Configuration Code Memory

- Microcomputer Interface with Serial Data Port

- Three Convenient Clock Options

- 11.0592 MHz

- 3.6864 MHz

- 2.4576 MHz (or 2.56 MHz)

- Operates from ± 5 V Supplies

- Low Power Standby Mode 100 μA (Typical)

- TTL and CMOS Compatible Digital Interface

- · Economical 16-Lead Package

- Full Military, Commercial and Industrial Temperature Ranges

#### **Description**

The AT76C10E integrates two Programmable Gain Amplifiers and a Programmable Telephone Line Group Delay Equalizer on a monolithic substrate. It is fabricated in a state-of-theart, low power CMOS process. The Gain and Group Delay steps are controlled by a seven-bit configuration code which can be programmed in real time and can also be stored permanently in on-chip E²PROMS. The AT76C10E is implemented in an advanced switched-capacitor technology and is designed to provide precise Gain and Group Delay compensation for low bit-error-rate data transmission over dial-up and leased lines. Anti-alias and clock filters are included on-chip as the AT76C10E employs sampled-data techniques, and external filters are not required for most applications.

Pin Definitions

No. Pin Name Fun

# Pin Configuration

|         |   | $\overline{}$ | 1 |      |

|---------|---|---------------|---|------|

| VSS 🗆   | 1 | 16            | Þ | DIN  |

| XTALO [ | 2 | 15            | Þ | WE   |

| XTALI 🗆 | 3 | 14            | Þ | CS   |

| CK OUT  | 4 | 13            | Þ | DGND |

| VDD 🗆   | 5 | 12            | Þ | EIN  |

| AOUT 🗆  | 6 | 11            | Þ | AGND |

| CK SEL  | 7 | 10            | Þ | EOUT |

| AIN C   | 8 | 9             | Þ | VDD  |

| 1  | VSS    | Negative Power Supply.<br>Nominal -5 Volts.                                                             |

|----|--------|---------------------------------------------------------------------------------------------------------|

| 2  | XTALO  | Crystal Oscillator Output.                                                                              |

| 3  | XTALI  | Crystal Oscillator Input.                                                                               |

| 4  | CKOUT  | Sampling Clock Output.<br>(Open Drain)                                                                  |

| 5  | RE     | Recall Enable Input.<br>Loads Configuration into Control<br>Registers from On-Chip E <sup>2</sup> PROM. |

| 6  | AOUT   | PG-B Analog Signal Output.                                                                              |

| 7  | CK SEL | Clock Select. Selects one of the 3 recommended Clock frequencies.                                       |

| 8  | AIN    | PG-B Analog Signal Input.                                                                               |

| 9  | VDD    | Positive Power Supply.<br>Nominal +5 Volts.                                                             |

| 10 | EOUT   | Delay Equalizer Analog<br>Signal Output.                                                                |

| 11 | AGND   | Analog Ground.                                                                                          |

| 12 | EIN    | Delay Equalizer Analog Signal Input.                                                                    |

| 13 | DGND   | Digital Ground.                                                                                         |

| 14 | cs     | Chip Select Control Input.                                                                              |

| 15 | WE     | Write Enable Control Input.                                                                             |

Function

E<sup>2</sup>PROM

Programmable

Amplifier

Delay

Equalizer

<u>AMEL</u>

Serial Data Input.

11-11

**| 1**074177 0005794 327 |

DIN

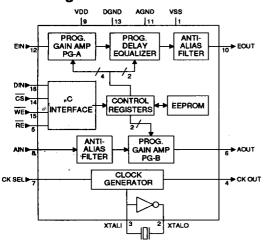

#### **Block Diagram**

#### **Device Operation**

The AT76C10E is designed for use in the signal paths of a modem or voice/data phone to minimize the bit-error-rate over dial-up and leased lines. Gain and Group Delay response of the AT76C10E are controlled by a serial seven-bit configuration code. D1 and D0 of the configuration code are the address bits which select one of the three control registers. Bits D2 to D5 set the gain and delay equalizer steps. D6 is an option bit which determines whether the configuration code will update one of the control registers only, or also be stored in on-chip non-volatile memory (E<sup>2</sup>PROM) of the AT76C10E. All the functions associated with the configuration code are summarized in Tables 1 to 4.

#### **Configuration Code Format**

| D6               | D5 | D4     | D3     | D2 | D1  | D0   |

|------------------|----|--------|--------|----|-----|------|

| Option<br>Select |    | Contro | l Code |    | Add | ress |

This chip can be used as part of an adaptive equalizer for medium to high speed modems (1200 bps to greater than 19.2K bps). The configuration code is loaded into the chip at a serial data input port and updated in real time. It can also be stored permanently in on-chip E<sup>2</sup>PROMS and updated periodically. The high performance Atmel E<sup>2</sup>PROM process together with redundancy circuits allows over 10E6 write cycles. The amplitude response of the equalizer is nominally at 0 dB with negligible ripple. The AT76C10E can also be used as a fixed compromise delay equalizer.

PROGRAMMABLE GAIN AMPLIFIER: The AT76C10E provides two high dynamic range amplifiers for maximizing

signal-to-noise ratio. Amplifier PG-A offers 16 programmable gain steps from 0 dB to 7.5 dB in 0.5 dB steps. Amplifier PG-B provides -8 to 16 dB of gain in 8 dB steps. The two amplifiers can be cascaded to provide 31.5 dB range of programmable gain in 0.5 dB steps. The Programmable Amplifiers can be used as an Automatic Gain Control Circuit or as a fixed gain adjustment.

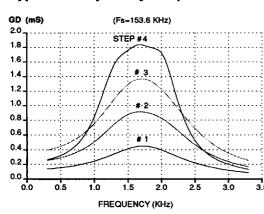

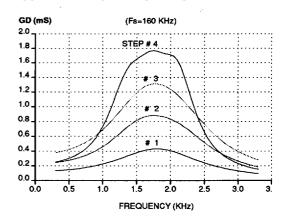

PROGRAMMABLE GROUP DELAY EQUALIZER: The Group Delay Equalizer is designed to provide programmable compromise group delay compensation to achieve low bit-error-rate data transmission. Four group delay responses are provided to accommodate the majority of conditioned as well as unconditioned lines. The first three responses are recommended for line types C2 and C1, while the fourth response can be used for 3002-type lines. Two or more ATT6C10Es can be cascaded to obtain additional group delay compensation.

CONTROL REGISTERS: Four control registers are used to store the configuration codes for the gain steps of PG-A and PG-B, the delay steps of the Delay Equalizer, and the control bit for the power-down mode. All the control bits, except the power down-bit, can also be programmed into on-chip non-volatile memories of the AT76C10E.

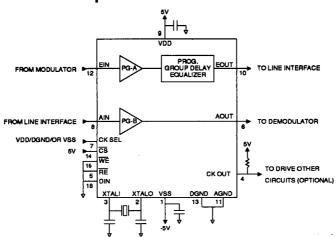

MICROCOMPUTER INTERFACE: Control inputs  $\overline{CS}$ ,  $\overline{WE}$ ,  $\overline{RE}$  and serial data input DIN allow the AT76C10E to be easily interfaced with most popular microcontrollers. All digital I/Os are TTL as well as CMOS compatible. For stand alone operation,  $\overline{CS}$  should be tied to VDD while  $\overline{WE}$ ,  $\overline{RE}$  and DIN should be tied to ground.

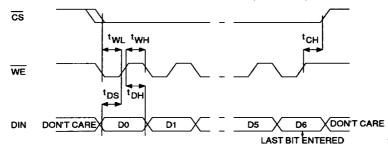

WRITE OPERATION: To program a configuration code into a particular control register, the voltage at  $\overline{CS}$  has to be brought low while the data bits appearing at DIN are strobed in at the rising edge of  $\overline{WE}$ . At the rising edge of  $\overline{CS}$ , the last 7 input data bits are latched into the control registers. Therefore, if the first bit of an update byte is a "start bit," it will be ignored. If a "0" was inserted at D6 of the input code, the configuration code will also be immediately written into on-chip  $E^2PROM$  of the AT76C10E. As all timing signals and programming voltages are generated internally, writing the  $E^2PROM$  is transparent to the user. However, while the  $E^2PROM$  is being programmed, which takes 1.5 mS, any further attempt to initiate programming will be ignored until the first operation is completed.

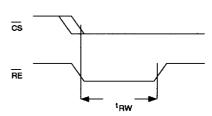

RECALL OPERATION: A RECALL operation can be initiated any time during operation by bringing both  $\overline{CS}$  and  $\overline{RE}$  low simultaneously. The configuration codes which have been preprogrammed in the  $E^2$ PROM of the AT76C10E are loaded into the control registers.

POWER-DOWN MODE: To minimize power consumption for battery powered applications and in certain linecard applications, the AT76C10E provides a low power standby mode of operation. In the power-down mode, the analog outputs go into a high impedance state. The power-down mode is initiated by writing a "0" into the power-down register. Once in the power-down mode, the AT76C10E can be reactivated by writing a "1" into the power-down register or performing a RECALL operation. It should be noted that upon powering up the AT76C10E for the first time, it automatically goes into the normal active mode of operation.

AT76C10E

11-12

1074177 0005795 263

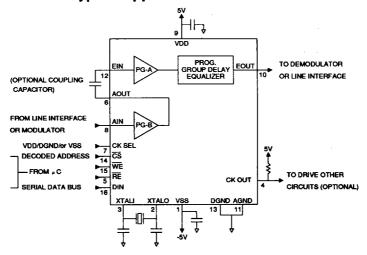

CRYSTAL OSCILLATOR: Internal timing of the chip is generated either by connecting a crystal across pins XTALI and XTALO of the on-chip oscillator, or by applying an external clock at pin XTALI. In the latter case, pin XTALO should be left unconnected. To accommodate different applications, three clock options: 2.4576 MHz, 3.6864 MHz and 11.0592 MHz,

can be selected via control pin CK SEL. For applications in a lineard environment, a 2.56 MHz clock can be used instead of the 2.4576 MHz clock. The 153.6 kHz (160 kHz with 2.56 MHz clock) sampling clock is available as an open drain output at CK OUT for synchronization or driving other circuits, e.g. the transmit or receive filters, or A/D and D/A converters.

Recommended **CK SEL XTAL Frequency CK OUT** VDD 11.0592 MHz 153.6 kHz **DGND** 3.6864 MHz 153.6 kHz VSS 2.4576 MHz 153.6 kHz VSS 2.56 MHz 160.0 kHz

**Table 2. Equalizer Selection**

| Add | Address |    | Control Code |    | Equalizer<br>Step | Recommened<br>Line |           |

|-----|---------|----|--------------|----|-------------------|--------------------|-----------|

| D1  | D0      | D5 | D4           | D3 | D2                | No.                | Condition |

| 0   | 0       | Х  | Х            | 0  | 0                 | 1                  | C2        |

| 0   | 0       | Х  | X            | 0  | 1                 | 2                  | C1        |

| 0   | 0       | X  | X            | 1  | 0                 | 3                  | C1        |

| 0   | 0       | X  | Х            | 1  | 1                 | 4                  | 3002      |

**Group Delay Characteristics (Microseconds)**

Fs = 153.6 kHz

| Frequency<br>(Hz) | Step<br>#1 | Step<br>#2 | Step<br>#3 | Step<br>#4 |

|-------------------|------------|------------|------------|------------|

| 300               | 158        | 278        | 416        | 284        |

| 600               | 188        | 336        | 502        | 386        |

| 900               | 237        | 463        | 681        | 680        |

| 1200              | 325        | 671        | 985        | 1360       |

| 1500              | 431        | 890        | 1330       | 1791       |

| 1700              | 462        | 938        | 1382       | 1838       |

| 1900              | 435        | 897        | 1305       | 1810       |

| 2100              | 372        | 777        | 1144       | 1510       |

| 2400              | 266        | 542        | 808        | 683        |

| 2700              | 181        | 361        | 534        | 342        |

| 3000              | 136        | 250        | 368        | 213        |

| 3300              | 102        | 182        | 267        | 148        |

|                   |            |            |            |            |

Table 3. Programmable Gain Amplifier, PG-A

| Add | ress | Co | ontro | l Co | de | PG-A     | PG-A Gain |

|-----|------|----|-------|------|----|----------|-----------|

| D1  | DO   | D5 | D4    | DЗ   | D2 | Step No. | (dB)      |

| 0   | 1    | 0  | 0     | 0    | 0  | 1        | 0.0       |

| 0   | 1    | 0  | 0     | 0    | 1  | 2        | 0.5       |

| 0   | 1    | 0  | 0     | 1    | 0  | 3        | 1.0       |

| 0   | 1    | 0  | 0     | 1    | 1  | 4        | 1.5       |

| 0   | 1    | 0  | 1     | 0    | 0  | 5        | 2.0       |

| 0   | 1    | 0  | 1     | 0    | 1  | 6        | 2.5       |

| 0   | 1    | 0  | 1     | 1    | 0  | 7        | 3.0       |

| 0   | 1    | 0  | 1     | 1    | 1  | 8        | 3.5       |

| 0   | 1    | 1  | 0     | 0    | 0  | 9        | 4.0       |

| 0   | 1    | 1  | 0     | 0    | 1  | 10       | 4.5       |

| 0   | 1    | 1  | 0     | 1    | 0  | 11       | 5.0       |

| 0   | _1   | 1  | 0     | 1    | 1  | 12       | 5.5       |

| 0   | 1    | 1  | 1     | 0    | 0  | 13       | 6.0       |

| 0   | 1    | 1  | 1     | 0    | 1  | 14       | 6.5       |

| 0   | 1    | 1  | 1     | 1    | 0  | 15       | 7.0       |

| 0   | 1    | 1  | 1     | 1    | 1  | 16       | 7.5       |

**Table 1. Option Selection**

| Add | ddress Option Bit |    |                                                          |

|-----|-------------------|----|----------------------------------------------------------|

| D1  | D0                | D6 | Function                                                 |

| 0   | 0                 | 0  | Writes Control Code into E <sup>2</sup> PROM and updates |

| 1   | 0                 | 0  | Control Registers                                        |

| 0   | 0                 | 1  | Updates Control                                          |

| 0   | 1                 | 1  | Registers Only                                           |

| 1   | 0                 | 1  |                                                          |

| 1   | 1                 | 0  | Power Down Mode                                          |

| 1   | 1                 | 1  | Active Mode                                              |

Table 4. Programmable Gain Amplifier, PG-B

| ress | C  | ontro         | I Co                   | de                                                                                                                      | PG-B                                                                                                                                                   | PG-B Gain                                                                                                                                                                                   |  |

|------|----|---------------|------------------------|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| D0   | D5 | D4            | D3                     | D2                                                                                                                      | Step No.                                                                                                                                               | (dB)                                                                                                                                                                                        |  |

| 0    | Х  | Х             | 0                      | 0                                                                                                                       | 1                                                                                                                                                      | 0.0                                                                                                                                                                                         |  |

| 0    | Х  | Х             | 0                      | 1                                                                                                                       | 2                                                                                                                                                      | 8.0                                                                                                                                                                                         |  |

| 0    | Х  | Х             | 1                      | 0                                                                                                                       | 3                                                                                                                                                      | 16.0                                                                                                                                                                                        |  |

| 0    | Х  | Х             | 1                      | 1                                                                                                                       | 4                                                                                                                                                      | -8.0                                                                                                                                                                                        |  |

|      |    | D0 D5 0 X 0 X | D0 D5 D4  0 X X  0 X X | D0         D5         D4         D3           0         X         X         0           0         X         X         0 | D0         D5         D4         D3         D2           0         X         X         0         0           0         X         X         0         1 | D0         D5         D4         D3         D2         Step No.           0         X         X         0         0         1           0         X         X         0         1         2 |  |

X = Don't Care

11-13

1074177 DDO5796 1TT

### **Sample Connection for Typical Application**

### **Stand Alone Operation Example**

### **Absolute Maximum Ratings\***

| Temperature Under Bias55° C to 125° C                            | ; |

|------------------------------------------------------------------|---|

| Storage Temperature65° C to 150° C                               | ; |

| Voltage on Pins AGND and DGND with Respect to VSS0.6 V to 6.25 V | , |

| All Voltages with Respect to VSS0.6 V to VDD + 0.6 V             | , |

\*NOTICE: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### 11-14

## AT76C10E

**■ 1074177 0005797 036 ■**

### D.C. and A.C. Operating Range

|            | Operating Temperature (Case) | VDD / VSS Power Supplies |

|------------|------------------------------|--------------------------|

| Commercial | 0° C - 70° C                 | 5 V / -5V ± 10%          |

| Industrial | -40° C - 85° C               | 5 V / -5 V ± 10%         |

| Military   | -55° C - 125° C              | 5 V / -5 V ±5%           |

#### **Electrical Characteristics**

| Symbol | Parameter                               | Conditions                 | Min   | Тур   | Max  | Units |

|--------|-----------------------------------------|----------------------------|-------|-------|------|-------|

| Odal   | VDD Quiescent Current (active mode)     |                            |       | 3     | 6    | mA    |

| Isso   | VSS Quiescent Current (active mode)     |                            |       | 3     | 6    | mA    |

| IDDP   | VDD Quiescent Current (power-down mode) |                            |       | 100   | 500  | μА    |

| ISSP   | VSS Quiescent Current (power-down mode) |                            |       | 100   | 500  | μА    |

| RIA    | Input Resistance at AIN                 |                            | 100   |       |      | kohm  |

| RIE    | Input Resistance at EOUT                | Fs=153.6 KHz               | 1     |       |      | Mohm  |

| Cı     | Input Capacitance                       |                            |       |       | 20   | pF    |

| ROA    | Ouput Resistance at AOUT                |                            |       |       | 1    | kohm  |

| ROE    | Ouput Resistance at EOUT                |                            |       |       | 200  | ohm   |

| Fo     | Center Frequency                        |                            |       | 1700  |      | Hz    |

| DT     | Group Delay Tolerance                   |                            | -1.5  |       | +1.5 | %     |

| GT     | Gain Tolerance                          |                            | -0.05 |       | 0.05 | dB    |

| Go     | Insertion Loss                          |                            | -0.15 |       | 0.15 | dB    |

| Vo     | Output Voltage                          | RL = 20 kohm               | VSS   |       | VDD  | V     |

| VN     | Output Noise                            | BW = Fs/2                  |       |       | 200  | μVrms |

| THD    | Total Harmonic Distortion               | RL = 20 kohm<br>Vo = 8 Vpp |       | 0.1   | 0.5  | %     |

| Fs     | Sampling Frequency                      |                            |       | 153.6 |      | kHz   |

| VFT    | Clock Feedthrough                       |                            |       |       | 5    | mVpp  |

11-15

■ 1074177 0005798 T72 ■

### **Configuration Code Write Waveform**

### **Digital Timing Parameters**

| Symbol | Parameter         | Min | Max | Units |

|--------|-------------------|-----|-----|-------|

| twL    | Write Enable Low  | 50  |     | ns    |

| twн    | Write Enable High | 50  |     | ns    |

| tch    | CS Hold Time      | 100 |     | ns    |

| tos    | Data Setup Time   | 40  |     | ns    |

| tрн    | Data Hold Time    | 40  |     | ns    |

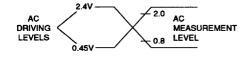

#### **Input Test Waveform**

tR, tF < 20 ns (10% to 90%)

11-16

### **Configuration Code Recall Waveform**

## **Typical Group Delay Response**

### **Typical Group Delay Response**

AT76C10E

**■** 1074177 0005799 909 **■**

### **Ordering Information**

| Delay<br>(ms) | Gain<br>(dB) | Power<br>Supply | Bandwidth<br>(KHz) | Ordering Code              | Package     | Operation Range               |

|---------------|--------------|-----------------|--------------------|----------------------------|-------------|-------------------------------|

| 1.8           | 31.5         | ±10%            | 4                  | AT76C10E-PC<br>AT76C10E-SC | 16P3<br>16S | Commercial<br>(0°C to 70°C)   |

|               |              |                 |                    | AT76C10E-PI<br>AT76C10E-SI | 16P3<br>16S | Industrial<br>(-40°C to 85°C) |

| 1.8           | 31.5         | ±5%             | 4                  | AT76C10E-DM                | 16D3        | Military<br>(-55°C to 125°C)  |

| Package Type |                                                                         |  |  |  |  |

|--------------|-------------------------------------------------------------------------|--|--|--|--|

| 16D3         | 16 Lead, 0.300" Wide Non-Windowed, Ceramic Dual Inline Package (Cerdip) |  |  |  |  |

| 16P3         | 16 Lead, 0.300" Wide, Plastic Dual Inline Package (PDIP)                |  |  |  |  |

| 168          | 16 Lead, 0.300" Wide, Plastic Gull Wing Small Outline (SOIC)            |  |  |  |  |

11-17

**1**074177 0005800 450 **1**