# GS1561 HD-LINX™ II Multi-Rate Deserializer

PRELIMINARY DATA SHEET

#### **KEY FEATURES**

- SMPTE 292M and SMPTE 259M-C compliant descrambling and NRZI → NRZ decoding (with bypass)

- DVB-ASI sync word detection and 8b/10b decoding

- · auto-configuration for HD-SDI, SD-SDI and DVB-ASI

- dual serial digital input buffers with 2 x 1 mux

- · integrated serial digital signal termination

- · integrated reclocker

- automatic or manual rate selection / indication (HD/SD)

- · descrambler bypass option

- · adjustable loop bandwidth

- user selectable additional processing features including:

- CRC, TRS, ANC data checksum, line number and EDH CRC error detection and correction

- programmable ANC data detection

- illegal code remapping

- · internal flywheel for noise immune H, V, F extraction

- FIFO load Pulse

- 20-bit / 10-bit CMOS parallel output data bus

- 148.5MHz / 74.25MHz / 27MHz / 13.5MHz parallel digital output

- · automatic standards detection and indication

- 1.8V core power supply and 3.3V charge pump power supply

- · 3.3V digital I/O supply

- JTAG test interface

- small footprint compatible with GS1560A, GS1532, GS9060 and GS9062

## **APPLICATIONS**

- SMPTE 292M Serial Digital Interfaces

- SMPTE 259M-C Serial Digital Interfaces

- DVB-ASI Serial Digital Interfaces

#### DESCRIPTION

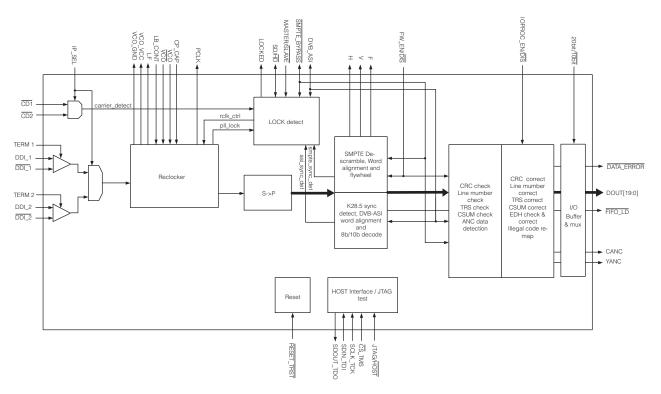

The GS1561 is a reclocking deserializer. When used in conjunction with the GS1524 Automatic Cable Equalizer and the GO1525 Voltage Controlled Oscillator, a receive solution can be realized for HD-SDI, SD-SDI and DVB-ASI applications.

In addition to reclocking and deserializing the input data stream, the GS1561 performs NRZI-to-NRZ decoding, descrambling as per SMPTE 292M/259M-C, and word alignment when operating in SMPTE mode. When operating in DVB-ASI mode, the device will word align the data to K28.5 sync characters and 8b/10b decode the received stream.

Two serial digital input buffers are provided with a 2x1 multiplexer to allow the device to select from one of two serial digital input signals.

The integrated reclocker features a very wide Input Jitter Tolerance of  $\pm 0.3$  UI (total 0.6 UI), a rapid asynchronous lock time, and full compliance with DVB-ASI data streams.

The GS1561 also includes a range of data processing functions such as error detection and correction, automatic standards detection, and EDH support. The device can also detect and extract SMPTE 325M payload identifier packets and independently identify the received video standard. This information is read from internal registers via the host interface port.

Line-based CRC errors, line number errors, TRS errors, EDH CRC errors and ancillary data checksum errors can all be detected. A single 'DATA\_ERROR' pin is provided which is a logical 'OR'ing of all detectable errors. Individual error status is stored in internal 'ERROR\_STATUS' registers.

Finally, the device can correct detected errors and insert new TRS ID words, line-based CRC words, ancillary data checksum words, EDH CRC words, and line numbers. Illegal code re-mapping is also available. All processing function may be individually enabled or disabled via host interface control.

**GS1561 FUNCTIONAL BLOCK DIAGRAM**

# **TABLE OF CONTENTS**

| 1. | PIN OUT  |                                                          | 5  |

|----|----------|----------------------------------------------------------|----|

|    | 1.1      | PIN ASSIGNMENT                                           | 5  |

|    | 1.2      | PIN DESCRIPTIONS                                         | 6  |

| 2. | ELECTRIC | CAL CHARACTERISTICS                                      | 15 |

|    |          | ABSOLUTE MAXIUMUM RATINGS                                |    |

|    |          | DC ELECTRICAL CHARACTERISTICS.                           |    |

|    |          | AC ELECTRICAL CHARACTERISTICS                            |    |

|    |          | INPUT/OUTPUT CIRCUITS                                    |    |

|    |          | HOST INTERFACE MAP.                                      |    |

| J  |          | D DESCRIPTION                                            |    |

| J. |          | FUNCTIONAL OVERVIEW                                      |    |

|    |          |                                                          |    |

|    | 3.2      | SERIAL DIGITAL INPUT                                     |    |

|    |          | 3.2.1 INPUT SIGNAL SELECTION                             |    |

|    |          | 3.2.3 SINGLE INPUT CONFIGURATION                         |    |

|    | 3.3      | SERIAL DIGITAL RECLOCKER                                 |    |

|    |          | 3.3.1 EXTERNAL VCO                                       |    |

|    |          | 3.3.2 LOOP BANDWIDTH                                     |    |

|    | 3.4      | SERIAL-TO-PARALLEL CONVERSION                            | 24 |

|    | 3.5      | MODES OF OPERATION                                       | 24 |

|    |          | 3.5.1 LOCK DETECT                                        | 24 |

|    |          | 3.5.2 MASTER MODE                                        |    |

|    |          | 3.5.3 SLAVE MODE                                         |    |

|    | 3.6      | SMPTE FUNCTIONALITY                                      |    |

|    |          | 3.6.1 SMPTE DESCRAMBLING AND WORD ALIGNMENT              |    |

|    |          | 3.6.2 INTERNAL FLYWHEEL                                  |    |

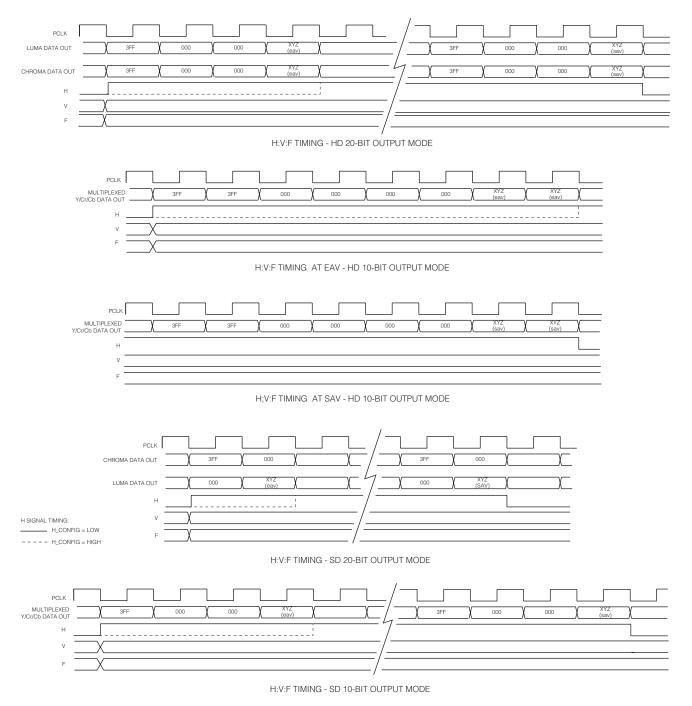

|    |          | 3.6.4 HVF TIMING SIGNAL GENERATION                       |    |

|    | 3.7      | DVB-ASI FUNCTIONALITY                                    |    |

|    | 0.7      | 3.7.1 DVB-ASI 8B/10B DECODING AND WORD ALIGNMENT         |    |

|    |          | 3.7.2 STATUS SIGNAL OUTPUTS                              |    |

|    | 3.8      | DATA THROUGH MODE                                        | 31 |

|    | 3.9      | ADDITIONAL PROCESSING FUNCTIONS                          | 32 |

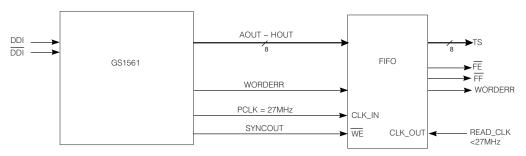

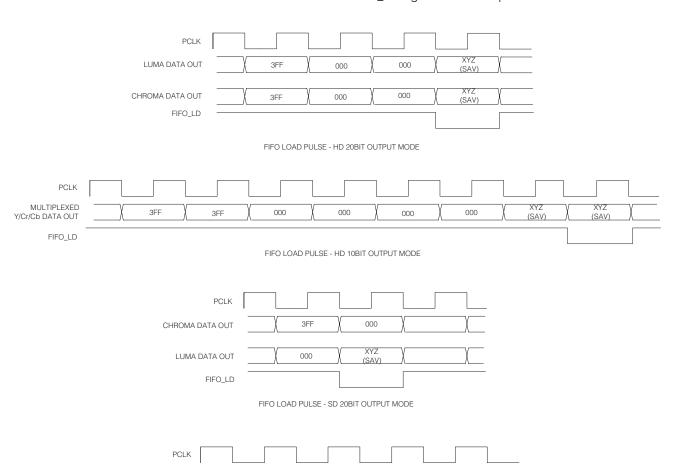

|    |          | 3.9.1 FIFO LOAD PULSE                                    |    |

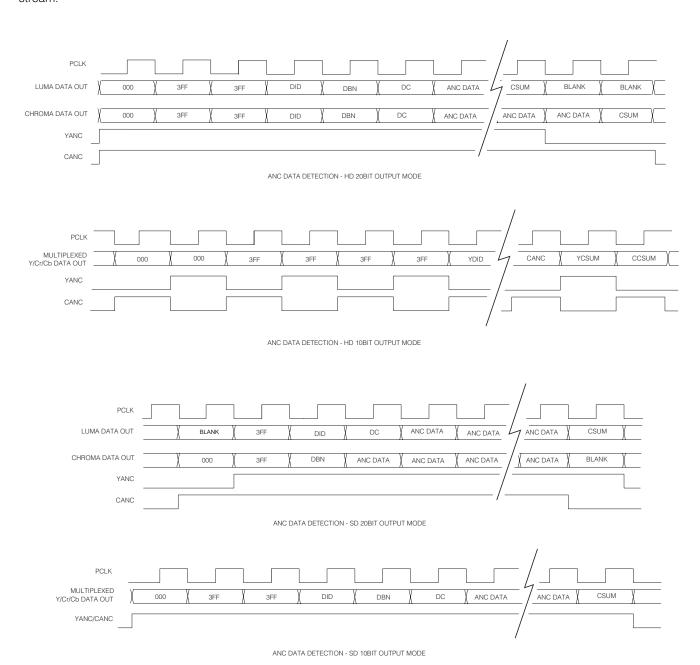

|    |          | 3.9.2 ANCILLARY DATA DETECTION AND INDICATION            |    |

|    |          | 3.9.3 SMPTE 352M PAYLOAD IDENTIFIER                      |    |

|    |          | 3.9.4 AUTOMATIC VIDEO STANDARD AND DATA FORMAT DETECTION |    |

|    |          | 3.9.5 ERROR DETECTION AND INDICATION                     |    |

|    |          | 3.9.7 EDH FLAG DETECTION                                 |    |

|    | 3.10     | O PARALLEL DATA OUTPUTS                                  |    |

|    |          | 3.10.1 PARALLEL DATA BUS BUFFERS                         |    |

|    |          | 3.10.2 PARALLEL OUTPUT IN SMPTE MODE                     | 46 |

|    |          | 3.10.3 PARALLEL OUTPUT IN DVB-ASI MODE                   |    |

|    |          | 3.10.4 PARALLEL OUTPUT IN DATA-THROUGH MODE              |    |

|    |          | 3 10.5 PARALLEL OUTPUT CLOCK (PCLK)                      | 47 |

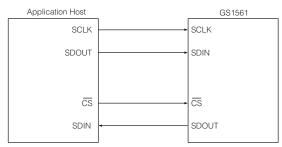

|    | 3.11 GSPI HOST INTERFACE                  | 48 |

|----|-------------------------------------------|----|

|    | 3.11.1 COMMAND WORD DESCRIPTION           | 48 |

|    | 3.11.2 DATA READ AND WRITE TIMING         |    |

|    | 3.11.3 CONFIGURATION AND STATUS REGISTERS |    |

|    | 3.12 JTAG                                 | 5C |

|    | 3.13 DEVICE POWER UP                      | 50 |

|    | 3.14 DEVICE RESET                         | 50 |

| 4. | APPLICATION REFERENCE DESIGN              | 51 |

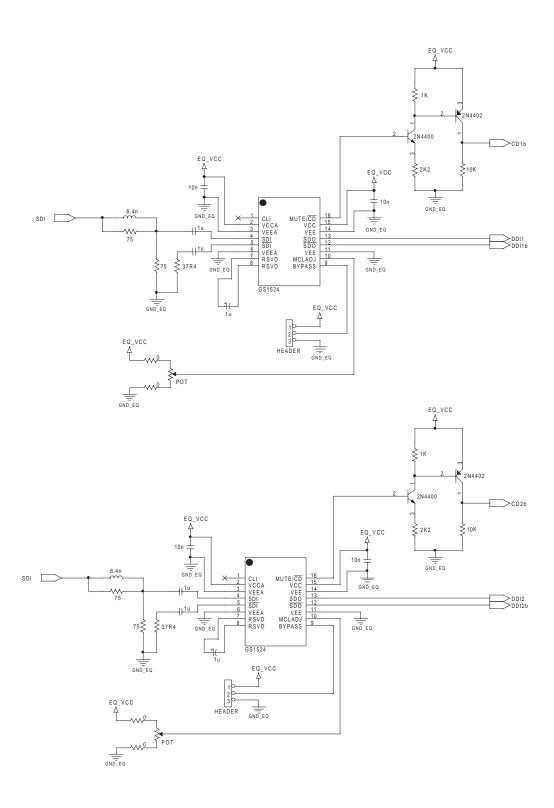

|    | 4.1 TYPICAL APPLICATION CIRCUIT (PART A)  | 51 |

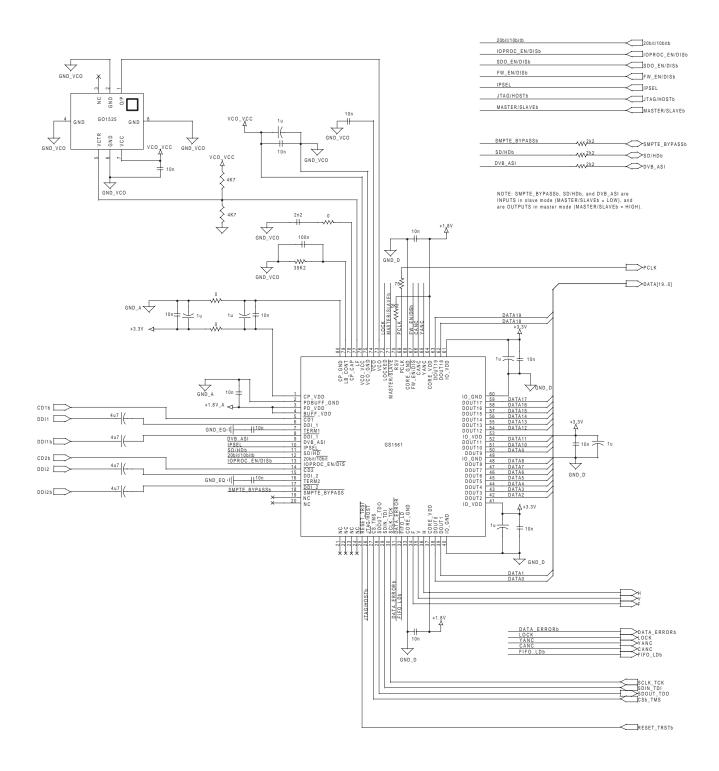

|    | 4.2 TYPICAL APPLICATION CIRCUIT (PART B)  |    |

| 5. | REFERENCES & RELEVANT STANDARDS           | 53 |

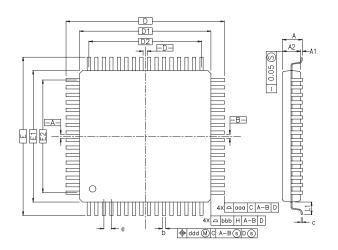

| 6. | PACKAGE & ORDERING INFORMATION            | 53 |

|    | 6.1 PACKAGE DIMENSIONS                    | 53 |

|    | 6.2 ORDERING INFORMATION                  | 54 |

| 7  | REVISION HISTORY                          | 54 |

# 1. PIN OUT

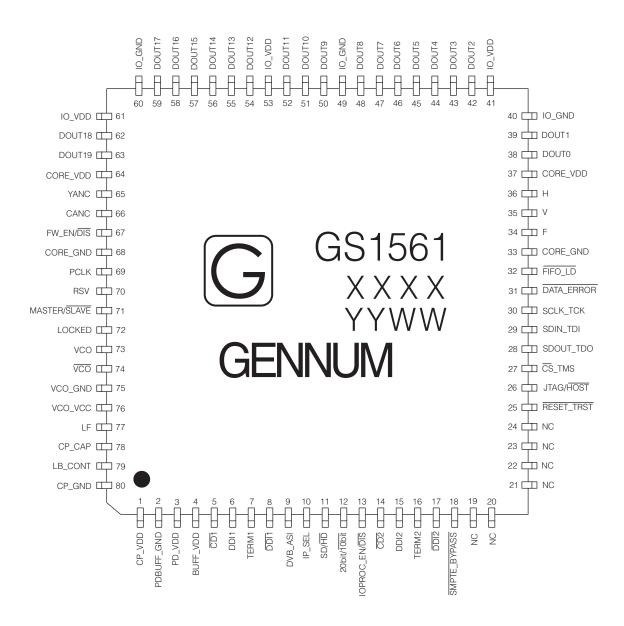

#### 1.1 PIN ASSIGNMENT

# 1.2 PIN DESCRIPTIONS

| PIN<br>NUMBER | NAME       | TIMING             | TYPE              | DESCRIPTION                                                                                                                                                       |  |

|---------------|------------|--------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1             | CP_VDD     | -                  | Power             | Power supply connection for the charge pump. Connect to +3.3V DC analog.                                                                                          |  |

| 2             | PDBUFF_GND | -                  | Power             | Ground connection for the phase detector and serial digital input buffers. Connect to analog GND.                                                                 |  |

| 3             | PD_VDD     | -                  | Power             | Power supply connection for the phase detector. Connect to +1.8V DC analog.                                                                                       |  |

| 4             | BUFF_VDD   | -                  | Power             | Power supply connection for the serial digital input buffers. Connect to +1.8V DC analog.                                                                         |  |

| 5             | CD1        | Non<br>Synchronous | Input             | STATUS SIGNAL INPUT<br>Signal levels are LVCMOS/LVTTL compatible.                                                                                                 |  |

|               |            |                    |                   | Used to indicate the presence of a serial digital input signal. Normally generated by a Gennum automatic cable equalizer.                                         |  |

|               |            |                    |                   | When LOW, the serial digital input signal received at the DDI1 and DDI1 pins is considered valid.                                                                 |  |

|               |            |                    |                   | When HIGH, the associated serial digital input signal is considered to be invalid. In this case, the LOCKED signal is set LOW and all parallel outputs are muted. |  |

| 6,8           | DDI1, DDI1 | Analog             | Input             | Differential input pair for serial digital input 1.                                                                                                               |  |

| 7             | TERM1      | Analog             | Input             | Termination for serial digital input 1. AC couple to PDBUFF_GND.                                                                                                  |  |

| 9             | DVB_ASI    | Non<br>Synchronous | Input /<br>Output | CONTROL SIGNAL INPUT / STATUS SIGNAL OUTPUT Signal levels are LVCMOS/LVTTL compatible.                                                                            |  |

|               |            |                    |                   | This pin will be an input set by the application layer in slave mode, and will be an output set by the device in master mode.                                     |  |

|               |            |                    |                   | Master Mode (MASTER/SLAVE = HIGH) The DVB_ASI signal will be HIGH only when the device has locked to a DVB-ASI compliant data stream. It will be LOW otherwise.   |  |

|               |            |                    |                   | Slave Mode (MASTER/SLAVE = LOW) When set HIGH in conjunction with SD/HD = HIGH and SMPTE_BYPASS = LOW, the device will be configured to operate in DVB-ASI mode.  |  |

|               |            |                    |                   | When set LOW, the device will not support the decoding or word alignment of received DVB-ASI data.                                                                |  |

| 10            | IP_SEL     | Non<br>Synchronous | Input             | CONTROL SIGNAL INPUT<br>Signal levels are LVCMOS/LVTTL compatible.                                                                                                |  |

|               |            |                    |                   | Used to select DDI1 / DDI1 or DDI2 / DDI2 as the serial digital input signal, and CD1 or CD2 as the carrier detect input signal.                                  |  |

|               |            |                    |                   | When set HIGH, DDI1 / DDI1 is selected as the serial digital input and CD1 is selected as the carrier detect input signal.                                        |  |

|               |            |                    |                   | When set LOW, DDI2 / DDI2 serial digital input and CD2 carrier detect input signal is selected.                                                                   |  |

| PIN<br>NUMBER | NAME          | TIMING             | TYPE              | DESCRIPTION                                                                                                                                                                                      |

|---------------|---------------|--------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11            | SD/HD         | Non<br>Synchronous | Input /<br>Output | CONTROL SIGNAL INPUT / STATUS SIGNAL OUTPUT Signal levels are LVCMOS/LVTTL compatible.                                                                                                           |

|               |               |                    |                   | This pin will be an input set by the application layer in slave mode, and will be an output set by the device in master mode.                                                                    |

|               |               |                    |                   | Master Mode (MASTER/SLAVE = HIGH) The SD/HD signal will be LOW whenever the received serial digital signal is 1.485Gb/s or 1.485/1.001Gb/s.                                                      |

|               |               |                    |                   | The SD/HD signal will be HIGH whenever the received serial digital signal is 270Mb/s.                                                                                                            |

|               |               |                    |                   | Slave Mode (MASTER/SLAVE = LOW) When set LOW, the device will be configured for the reception of 1.485Gb/s or 1.485/1.001Gb/s signals only and will not lock to any other serial digital signal. |

|               |               |                    |                   | When set HIGH, the device will be configured for the reception of 270Mb/s signals only and will not lock to any other serial digital signal.                                                     |

| 12            | 20bit/10bit   | Non<br>Synchronous | Input             | CONTROL SIGNAL INPUT<br>Signal levels are LVCMOS/LVTTL compatible.                                                                                                                               |

|               |               |                    |                   | Used to select the output data bus width in SMPTE or Data-Through modes. This signal is ignored in DVB-ASI mode.                                                                                 |

|               |               |                    |                   | When set HIGH, the parallel output will be 20-bit demultiplexed data.                                                                                                                            |

|               |               |                    |                   | When set LOW, the parallel outputs will be 10-bit multiplexed data.                                                                                                                              |

| 13            | IOPROC_EN/DIS | Non<br>Synchronous | Input             | CONTROL SIGNAL INPUT<br>Signal levels are LVCMOS/LVTTL compatible.                                                                                                                               |

|               |               |                    |                   | Used to enable or disable I/O processing features.                                                                                                                                               |

|               |               |                    |                   | When set HIGH, the following I/O processing features of the device are enabled:                                                                                                                  |

|               |               |                    |                   | EDH CRC Error Correction (SD-only)                                                                                                                                                               |

|               |               |                    |                   | ANC Data Checksum Correction                                                                                                                                                                     |

|               |               |                    |                   | Line-based CRC Error Correction (HD-only)  Line Number Error Correction (HD-only)                                                                                                                |

|               |               |                    |                   | Line Number Error Correction (HD-only)     TRS Error Correction                                                                                                                                  |

|               |               |                    |                   | Illegal Code Remapping                                                                                                                                                                           |

|               |               |                    |                   | To enable a subset of these features, keep IOPROC_EN/DIS HIGH and disable the individual feature(s) in the IOPROC_DISABLE register accesible via the host interface.                             |

|               |               |                    |                   | When set LOW, the I/O processing features of the device are disabled, regardless of whether the features are enabled in the IOPROC_DISABLE register.                                             |

| 14            | CD2           | Non<br>Synchronous | Input             | STATUS SIGNAL INPUT<br>Signal levels are LVCMOS/LVTTL compatible.                                                                                                                                |

|               |               |                    |                   | Used to indicate the presence of a serial digital input signal. Normally generated by a Gennum automatic cable equalizer.                                                                        |

|               |               |                    |                   | When LOW, the serial digital input signal received at the DDI2 and DDI2 pins is considered valid.                                                                                                |

|               |               |                    |                   | When HIGH, the associated serial digital input signal is considered to be invalid. In this case, the LOCKED signal is set LOW and all parallel outputs are muted.                                |

7 of 54 **GENNUM CORPORATION**22048 - 1

| PIN<br>NUMBER | NAME                  | TIMING                          | TYPE              | DESCRIPTION                                                                                                                                                                                                      |

|---------------|-----------------------|---------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15,17         | DDI_2, DDI_2          | Analog                          | Input             | Differential input pair for serial digital input 2.                                                                                                                                                              |

| 16            | TERM2                 | Analog                          | Input             | Termination for serial digital input 2. AC couple to PDBUFF_GND.                                                                                                                                                 |

| 18            | SMPTE_BYPASS          | Non<br>Synchronous              | Input /<br>Output | CONTROL SIGNAL INPUT / STATUS SIGNAL OUTPUT Signal levels are LVCMOS/LVTTL compatible.                                                                                                                           |

|               |                       |                                 |                   | This pin will be an input set by the application layer in slave mode, and will be an output set by the device in master mode.                                                                                    |

|               |                       |                                 |                   | Master Mode (MASTER/SLAVE = HIGH) The SMPTE_BYPASS signal will be HIGH only when the device has locked to a SMPTE compliant data stream. It will be LOW otherwise.                                               |

|               |                       |                                 |                   | Slave Mode (MASTER/SLAVE = LOW) When set HIGH in conjunction with DVB_ASI = LOW, the device will be configured to operate in SMPTE mode. All I/O processing features may be enabled in this mode.                |

|               |                       |                                 |                   | When set LOW, the device will not support the descrambling, decoding or word alignment of received SMPTE data. No I/O processing features will be available.                                                     |

| 19–24         | NC                    | -                               | =                 | No connect                                                                                                                                                                                                       |

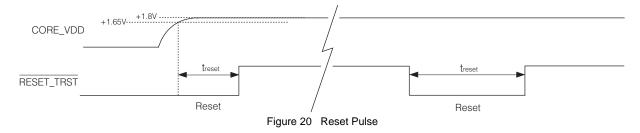

| 25            | RESET_TRST            | Non<br>Synchronous              | Input             | CONTROL SIGNAL INPUT Signal levels are LVCMOS/LVTTL compatible.                                                                                                                                                  |

|               |                       |                                 |                   | Used to reset the internal operating conditions to default settings and to reset the JTAG test sequence.                                                                                                         |

|               |                       |                                 |                   | Host Mode (JTAG/HOST = LOW) When asserted LOW, all functional blocks will be set to default conditions and all input and output signals become high impedance, including the serial digital outputs SDO and SDO. |

|               |                       |                                 |                   | Must be set HIGH for normal device operation.                                                                                                                                                                    |

|               |                       |                                 |                   | JTAG Test Mode (JTAG/HOST = HIGH) When asserted LOW, all functional blocks will be set to default and the JTAG test sequence will be held in reset.                                                              |

|               |                       |                                 |                   | When set HIGH, normal operation of the JTAG test sequence resumes.                                                                                                                                               |

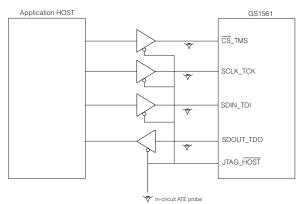

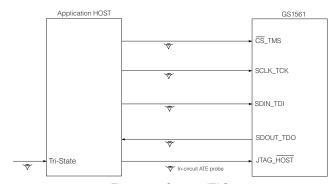

| 26            | JTAG/ <del>HOST</del> | Non<br>Synchronous              | Input             | CONTROL SIGNAL INPUT<br>Signal levels are LVCMOS/LVTTL compatible.                                                                                                                                               |

|               |                       |                                 |                   | Used to select JTAG Test Mode or Host Interface Mode.                                                                                                                                                            |

|               |                       |                                 |                   | When set HIGH, CS_TMS, SDOUT_TDO, SDI_TDI and SCLK_TCK are configured for JTAG boundary scan testing.                                                                                                            |

|               |                       |                                 |                   | When set LOW, CS_TMS, SDOUT_TDO, SDI_TDI and SCLK_TCK are configured as GSPI pins for normal host interface operation.                                                                                           |

| 27            | CS_TMS                | Synchronous<br>with<br>SCLK_TCK | Input             | CONTROL SIGNAL INPUT Signal levels are LVCMOS/LVTTL compatible.                                                                                                                                                  |

|               |                       | JOLN_TON                        |                   | Chip Select / Test Mode Select                                                                                                                                                                                   |

|               |                       |                                 |                   | Host Mode (JTAG/HOST = LOW)  CS_TMS operates as the host interface chip select, CS, and is active LOW.                                                                                                           |

|               |                       |                                 |                   | JTAG Test Mode (JTAG/HOST = HIGH)  CS_TMS operates as the JTAG test mode select, TMS, and is active HIGH.                                                                                                        |

| PIN<br>NUMBER | NAME       | TIMING                | TYPE   | DESCRIPTION                                                                                                                                                                                                           |

|---------------|------------|-----------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 28            | SDOUT_TDO  | Synchronous with      | Output | CONTROL SIGNAL OUTPUT<br>Signal levels are LVCMOS/LVTTL compatible.                                                                                                                                                   |

|               |            | SCLK_TCK              |        | Serial Data Output / Test Data Output<br>Host Mode (JTAG/HOST = LOW)                                                                                                                                                  |

|               |            |                       |        | SDOUT_TDO operates as the host interface serial output, SDOUT, used to read status and configuration information from the internal registers of the device.                                                           |

|               |            |                       |        | JTAG Test Mode (JTAG/HOST = HIGH) SDOUT_TDO operates as the JTAG test data output, TDO.                                                                                                                               |

| 29            | SDIN_TDI   | Synchronous with      | Input  | CONTROL SIGNAL INPUT<br>Signal levels are LVCMOS/LVTTL compatible.                                                                                                                                                    |

|               |            | SCLK_TCK              |        | Serial Data In / Test Data Input                                                                                                                                                                                      |

|               |            |                       |        | Host Mode (JTAG/HOST = LOW) SDIN_TDI operates as the host interface serial input, SDIN, used to write address and configuration information to the internal registers of the device.                                  |

|               |            |                       |        | JTAG Test Mode (JTAG/ <del>HOST</del> = HIGH)<br>SDIN_TDI operates as the JTAG test data input, TDI.                                                                                                                  |

| 30            | SCLK_TCK   | Non<br>Synchronous    | Input  | CONTROL SIGNAL INPUT<br>Signal levels are LVCMOS/LVTTL compatible.                                                                                                                                                    |

|               |            |                       |        | Serial Data Clock / Test Clock.                                                                                                                                                                                       |

|               |            |                       |        | Host Mode (JTAG/HOST = LOW) SCLK_TCK operates as the host interface burst clock, SCLK. Command and data read/write words are clocked into the device synchronously with this clock.                                   |

|               |            |                       |        | JTAG Test Mode (JTAG/ <del>HOST</del> = HIGH)<br>SCLK_TCK operates as the JTAG test clock, TCK.                                                                                                                       |

| 31            | DATA_ERROR | Synchronous with PCLK | Output | STATUS SIGNAL OUTPUT<br>Signal levels are LVCMOS/LVTTL compatible.                                                                                                                                                    |

|               |            |                       |        | The DATA_ERROR signal will be LOW when an error within the received data stream has been detected by the device. This pin is a logical 'OR'ing of all detectable errors listed in the internal ERROR_STATUS register. |

|               |            |                       |        | Once an error is detected, DATA_ERROR will remain LOW until the start of the next video frame / field, or until the ERROR_STATUS register is read via the host interface.                                             |

|               |            |                       |        | The DATA_ERROR signal will be HIGH when the received data stream has been detected without error.                                                                                                                     |

|               |            |                       |        | NOTE: It is possible to program which error conditions are monitored by the device by setting appropriate bits of the ERROR_MASK register HIGH. All error conditions are detected by default.                         |

| 32            | FIFO_LD    | Synchronous with PCLK | Output | CONTROL SIGNAL OUTPUT Signal levels are LVCMOS/LVTTL compatible.                                                                                                                                                      |

|               |            |                       |        | Used as a control signal for external FIFO(s).                                                                                                                                                                        |

|               |            |                       |        | Normally HIGH but will go LOW for one PCLK period at SAV.                                                                                                                                                             |

| 33, 68        | CORE_GND   | -                     | Power  | Ground connection for the digital core logic. Connect to digital GND.                                                                                                                                                 |

| PIN<br>NUMBER | NAME     | TIMING                | TYPE   | DESCRIPTION                                                                                                                                                                                           |  |

|---------------|----------|-----------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 34            | F        | Synchronous with PCLK | Output | STATUS SIGNAL OUTPUT Signal levels are LVCMOS/LVTTL compatible.                                                                                                                                       |  |

|               |          |                       |        | Used to indicate the ODD / EVEN field of the video signal.                                                                                                                                            |  |

|               |          |                       |        | The F signal will be HIGH for the entire period of field 2 as indicated by the F bit in the received TRS signals.                                                                                     |  |

|               |          |                       |        | The F signal will be LOW for all lines in field 1 and for all lines in progressive scan systems.                                                                                                      |  |

| 35            | V        | Synchronous with PCLK | Output | STATUS SIGNAL OUTPUT Signal levels are LVCMOS/LVTTL compatible.                                                                                                                                       |  |

|               |          |                       |        | Used to indicate the portion of the video field / frame that is used for vertical blanking.                                                                                                           |  |

|               |          |                       |        | The V signal will be HIGH for the entire vertical blanking period as indicated by the V bit in the received TRS signals.                                                                              |  |

|               |          |                       |        | The V signal will be LOW for all lines outside of the vertical blanking interval.                                                                                                                     |  |

| 36            | Н        | Synchronous with PCLK | Output | STATUS SIGNAL OUTPUT<br>Signal levels are LVCMOS/LVTTL compatible.                                                                                                                                    |  |

|               |          |                       |        | Used to indicate the portion of the video line containing active video data. H signal timing is configurable via the H_CONFIG bit of the IOPROC_DISABLE register accessible via the host interface.   |  |

|               |          |                       |        | Active Line Blanking (H_CONFIG = $0_h$ )<br>The H signal will be HIGH for the entire horizontal blanking period, including the EAV and SAV TRS words, and LOW otherwise. This is the default setting. |  |

|               |          |                       |        | TRS Based Blanking (H_CONFIG = $1_h$ ) The H signal will be HIGH for the entire horizontal blanking period as indicated by the H bit in the received TRS ID words, and LOW otherwise.                 |  |

| 37, 64        | CORE_VDD | -                     | Power  | Power supply connection for the digital core logic. Connect to +1.8V DC digital.                                                                                                                      |  |

| PIN<br>NUMBER        | NAME      | TIMING                | TYPE   |                                                                               | DESCRIPTION                                                         |

|----------------------|-----------|-----------------------|--------|-------------------------------------------------------------------------------|---------------------------------------------------------------------|

| 38, 39,<br>42–48, 50 | DOUT[0:9] | Synchronous with PCLK | Output | PARALLEL DATA BUS Signal levels are LVCMOS/LVTTL compatible.                  |                                                                     |

|                      |           |                       |        | DOUT9 is the MSB and DOU                                                      | T0 is the LSB.                                                      |

|                      |           |                       |        | HD 20-bit mode<br>SD/HD = LOW<br>20bit/10bit = HIGH                           | Chroma data output in SMPTE mode SMPTE_BYPASS =HIGH DVB_ASI = LOW   |

|                      |           |                       |        |                                                                               | Data output in Data-Through mode  SMPTE_BYPASS = LOW  DVB_ASI = LOW |

|                      |           |                       |        | HD 10-bit mode<br>SD/HD = LOW<br>20bit/10 bit = LOW                           | Forced LOW in all modes.                                            |

|                      |           |                       |        | SD 20-bit mode<br>SD/HD = HIGH<br>20bit/10bit = HIGH                          | Chroma data output in SMPTE mode SMPTE_BYPASS = HIGH DVB_ASI = LOW  |

|                      |           |                       |        |                                                                               | Data output in Data-Through mode  SMPTE_BYPASS = LOW  DVB_ASI = LOW |

|                      |           |                       |        |                                                                               | Forced LOW in DVB-ASI mode  SMPTE_BYPASS = LOW  DVB_ASI = HIGH      |

|                      |           |                       |        | SD 10-bit mode<br>SD/HD = HIGH<br>20bit/10bit = LOW                           | Forced LOW in all modes.                                            |

| 40, 49, 60           | IO_GND    | -                     | Power  | Ground connection for digital                                                 | I I/O buffers. Connect to digital GND.                              |

| 41, 53, 61           | IO_VDD    | -                     | Power  | Power supply connection for digital I/O buffers. Connect to +3.3V DC digital. |                                                                     |

| PIN<br>NUMBER               | NAME        | TIMING                | TYPE   |                                                                                | DESCRIPTION                                                                               |

|-----------------------------|-------------|-----------------------|--------|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| 51, 52,<br>54–59, 62,<br>63 | DOUT[19:10] | Synchronous with PCLK | Output | PARALLEL DATA BUS<br>Signal levels are LVCMOS/LV                               | ·                                                                                         |

|                             |             |                       |        | DOUT19 is the MSB and DO  HD 20-bit mode SD/HD = LOW 20bit/10bit = HIGH        | Luma data output in SMPTE mode SMPTE_BYPASS = HIGH DVB_ASI = LOW                          |

|                             |             |                       |        |                                                                                | Data output in Data-Through mode  SMPTE_BYPASS = LOW  DVB_ASI = LOW                       |

|                             |             |                       |        | HD 10-bit mode<br>SD/HD = LOW<br>20bit/10bit = LOW                             | Multiplexed Luma and Chroma data output in SMPTE mode SMPTE_BYPASS = HIGH DVB_ASI = LOW   |

|                             |             |                       |        |                                                                                | Data output in Data-Through mode  SMPTE_BYPASS = LOW  DVB_ASI = LOW                       |

|                             |             |                       |        | SD 20-bit mode<br>SD/HD = HIGH<br>20bit/10bit = HIGH                           | Luma data output in SMPTE mode SMPTE_BYPASS = HIGH DVB_ASI = LOW                          |

|                             |             |                       |        |                                                                                | Data output in Data-Through mode  SMPTE_BYPASS = LOW  DVB_ASI = LOW                       |

|                             |             |                       |        |                                                                                | DVB-ASI data in DVB-ASI mode  SMPTE_BYPASS = LOW  DVB_ASI = HIGH                          |

|                             |             |                       |        | SD 10-bit mode<br>SD/HD = HIGH<br>20bit/10bit = LOW                            | Multiplexed Luma and Chroma data output in SMPTE mode SMPTE_BYPASS = HIGH DVB_ASI = LOW   |

|                             |             |                       |        |                                                                                | Data input in data through mode  SMPTE_BYPASS = LOW  DVB_ASI = LOW                        |

|                             |             |                       |        |                                                                                | DVB-ASI data in DVB-ASI mode<br>SMPTE_BYPASS = LOW<br>DVB_ASI = HIGH                      |

| 65                          | YANC        | Synchronous with PCLK | Output | STATUS SIGNAL OUTPUT<br>Signal levels are LVCMOS/LV                            | /TTL compatible.                                                                          |

|                             |             |                       |        | Used to indicate the presenc                                                   | e of ancillary data in the video stream.                                                  |

|                             |             |                       |        | HD Mode (SD/HD = LOW) The YANC signal will be HIGI HANC data in the luma video | H when the device has detected VANC or ostream and LOW otherwise.                         |

|                             |             |                       |        |                                                                                | a (20bit/10bit = HIGH), the YANC signal will NC data is detected in the luma video stream |

|                             |             |                       |        |                                                                                | 20bit/10bit = LOW), the YANC signal will be data is detected anywhere in the data stream  |

GENNUM CORPORATION 22048 - 1

| PIN<br>NUMBER | NAME         | TIMING                | TYPE   |                                                                                                                                                                                                                                                                                       | DESCRIPTION                                                                                                                                                                                                     |

|---------------|--------------|-----------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 66            | CANC         | Synchronous with PCLK | Output | STATUS SIGNAL OUTPUT<br>Signal levels are LVCMOS/LV                                                                                                                                                                                                                                   | TTL compatible.                                                                                                                                                                                                 |

|               |              |                       |        | Used to indicate the presenc                                                                                                                                                                                                                                                          | e of ancillary data in the video stream.                                                                                                                                                                        |

|               |              |                       |        | HD Mode (SD/HD = LOW) The CANC signal will be HIGH when the device has detected VANC or HANC data in the chroma video stream and LOW otherwise.                                                                                                                                       |                                                                                                                                                                                                                 |

|               |              |                       |        |                                                                                                                                                                                                                                                                                       | a (20bit/10bit = HIGH), the CANC signal will NC data is detected in the chroma video                                                                                                                            |

|               |              |                       |        |                                                                                                                                                                                                                                                                                       | 20bit/10bit = LOW), the CANC signal will be data is detected anywhere in the data stream                                                                                                                        |

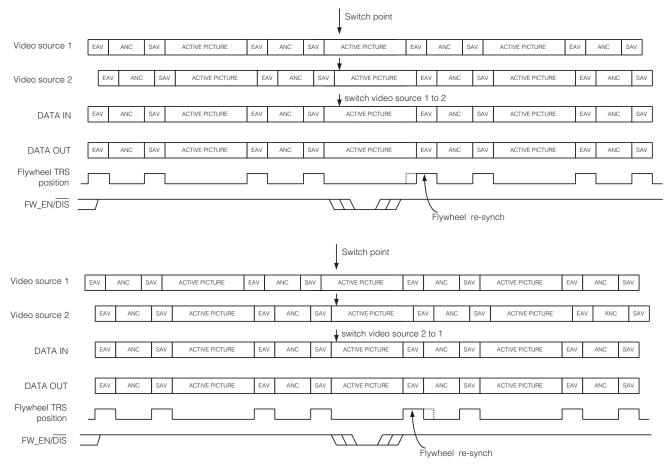

| 67            | FW_EN/DIS    | Non<br>Synchronous    | Input  | CONTROL SIGNAL INPUT<br>Signal levels are LVCMOS/LV                                                                                                                                                                                                                                   | TTL compatible.                                                                                                                                                                                                 |

|               |              |                       |        | Used to enable or disable the                                                                                                                                                                                                                                                         | e noise immune flywheel of the device.                                                                                                                                                                          |

|               |              |                       |        | When set HIGH, the internal flywheel is enabled. This flywheel is used in the extraction and generation of TRS timing signals, in automatic video standards detection, and in manual switch line lock handling.                                                                       |                                                                                                                                                                                                                 |

|               |              |                       |        | When set LOW, the internal flywheel is disabled and TRS correction and insertion is unavailable.                                                                                                                                                                                      |                                                                                                                                                                                                                 |

| 69            | PCLK         | -                     | Output | PARALLEL DATA BUS CLOCK Signal levels are LVCMOS/LVTTL compatible.                                                                                                                                                                                                                    |                                                                                                                                                                                                                 |

|               |              |                       |        | HD 20-bit mode                                                                                                                                                                                                                                                                        | PCLK = 74.25MHz or 74.25/1.001MHz                                                                                                                                                                               |

|               |              |                       |        | HD 10-bit mode                                                                                                                                                                                                                                                                        | PCLK = 148.5MHz or 148.5/1.001MHz                                                                                                                                                                               |

|               |              |                       |        | SD 20-bit mode                                                                                                                                                                                                                                                                        | PCLK = 13.5MHz                                                                                                                                                                                                  |

|               |              |                       |        | SD 10-bit mode                                                                                                                                                                                                                                                                        | PCLK = 27MHz                                                                                                                                                                                                    |

| 70            | RSV          | -                     | -      | Connect to CORE_VDD throu                                                                                                                                                                                                                                                             | ugh 2.2KΩ.                                                                                                                                                                                                      |

| 71            | MASTER/SLAVE | Non<br>Synchronous    | Input  | CONTROL SIGNAL INPUT<br>Signal levels are LVCMOS/LV                                                                                                                                                                                                                                   | TTL compatible.                                                                                                                                                                                                 |

|               |              |                       |        | Used to determine the input and SMPTE_BYPASS pins.                                                                                                                                                                                                                                    | / output selection for the DVB_ASI, SD/HD,                                                                                                                                                                      |

|               |              |                       |        | When set HIGH, the GS1561 is set to operate in master mode where DVB_ASI, SD/HD, and SMPTE_BYPASS become status signal output pins set by the device. In this mode, the GS1561 will automatically detect, reclock, deserialize and process SD SMPTE, HD SMPTE, or DVB-ASI input data. |                                                                                                                                                                                                                 |

|               |              |                       |        | DVB_ASI, SD/HD, and SMPT<br>In this mode, the application<br>the correct reception of eithe                                                                                                                                                                                           | is set to operate in slave mode where E_BYPASS become control signal input pins. layer must set these external device pins for r SMPTE or DVB-ASI data. Slave mode also deserializing of data not conforming to |

| PIN<br>NUMBER | NAME     | TIMING                | TYPE            | DESCRIPTION                                                                                                                                                                                                                         |  |

|---------------|----------|-----------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 72            | LOCKED   | Synchronous with PCLK | Output          | STATUS SIGNAL OUTPUT<br>Signal levels are LVCMOS / LVTTL compatible.                                                                                                                                                                |  |

|               |          |                       |                 | The LOCKED signal will be HIGH whenever the device has correctly received and locked to SMPTE compliant data in SMPTE mode or DVB-ASI compliant data in DVB-ASI mode, or when the reclocker has achieved lock in Data-Through mode. |  |

|               |          |                       |                 | It will be LOW otherwise.                                                                                                                                                                                                           |  |

| 73, 74        | VCO, VCO | Analog                | Input           | Differential inputs for the external VCO reference signal. For single ended devices such as the GO1525, VCO should be AC coupled to VCO_GND.                                                                                        |  |

|               |          |                       |                 | VCO is nominally 1.485GHz.                                                                                                                                                                                                          |  |

| 75            | VCO_GND  | -                     | Output<br>Power | Ground reference for the external voltage controlled oscillator. Connect to pins 2, 4, 6, and 8 of the GO1525. This pin is an output.                                                                                               |  |

|               |          |                       |                 | Should be isolated from all other grounds.                                                                                                                                                                                          |  |

| 76            | VCO_VCC  | -                     | Output<br>Power | Power supply for the external voltage controlled oscillator. Connect to pin 5 of the GO1525. This pin is an output.                                                                                                                 |  |

|               |          |                       |                 | Should be isolated from all other power supplies.                                                                                                                                                                                   |  |

| 77            | LF       | Analog                | Output          | Control voltage to external voltage controlled oscillator. Nominally +1.25V DC.                                                                                                                                                     |  |

| 78            | CP_CAP   | Analog                | Input           | PLL lock time constant capacitor connection. Normally connected to VCO_GND through 2.2nF.                                                                                                                                           |  |

| 79            | LB_CONT  | Analog                | Input           | Control voltage to set the loop bandwidth of the integrated reclocker. Normally connected to VCO_GND through 40k $\Omega$ .                                                                                                         |  |

| 80            | CP_GND   | -                     | Power           | Ground connection for the charge pump. Connect to analog GND.                                                                                                                                                                       |  |

# 2. ELECTRICAL CHARACTERISTICS

# 2.1 ABSOLUTE MAXIUMUM RATINGS

| PARAMETER                            | VALUE/UNITS                      |

|--------------------------------------|----------------------------------|

| Supply Voltage Core                  | -0.3V to +2.1V                   |

| Supply Voltage I/O                   | -0.3V to +4.6V                   |

| Input Voltage Range (any input)      | -2.0V to + 5.25V                 |

| Ambient Operating Temperature        | $-20$ °C ≤ $T_A$ ≤ $85$ °C       |

| Storage Temperature                  | -40°C ≤ T <sub>STG</sub> ≤ 125°C |

| Lead Temperature (soldering, 10 sec) | 230°C                            |

# NOTES:

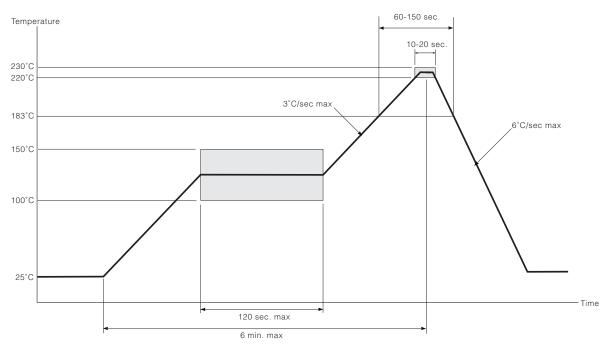

1. See reflow solder profile

Figure 1 Reflow Solder Profile

# 2.2 DC ELECTRICAL CHARACTERISTICS

$T_A = 0$ °C to 70°C, unless otherwise specified.

| PARAMETER                             | SYMBOL                                | CONDITIONS  | MIN             | TYP  | MAX  | UNITS | TEST<br>LEVEL | NOTES |

|---------------------------------------|---------------------------------------|-------------|-----------------|------|------|-------|---------------|-------|

|                                       |                                       | SYSTEM      |                 |      |      |       |               |       |

| Operation Temperature Range           | T <sub>A</sub>                        |             | 0               | -    | 70   | °C    | -             | 1     |

| Function Temperature Range            |                                       |             | -25             | -    | 85   | °C    | -             | 2     |

| Digital Core Supply Voltage           | CORE_VDD                              |             | 1.65            | 1.8  | 1.95 | V     | 1             | 1     |

| Digital I/O Supply Voltage            | IO_VDD                                |             | 3.0             | 3.3  | 3.6  | V     |               |       |

| Charge Pump Supply Voltage            | CP_VDD                                |             | 3.0             | 3.3  | 3.6  | V     |               |       |

| Phase Detector Supply<br>Voltage      | PD_VDD                                |             | 1.65            | 1.8  | 1.95 | V     |               |       |

| Input Buffer Supply Voltage           | BUFF_VDD                              |             | 1.65            | 1.8  | 1.95 | V     |               |       |

| External VCO Supply Voltage<br>Output | VCO_VCC                               |             | 2.25            | 2.50 | 2.75 | V     | 1             | -     |

| +1.8V Supply Current                  | I <sub>1V8</sub>                      |             | -               | -    | 200  | mA    | 7             | -     |

| +3.3V Supply Current                  | I <sub>3V3</sub>                      |             | -               | -    | 55   | mA    | 7             | -     |

| Total Device Power                    | P <sub>D</sub>                        |             | -               | -    | 545  | mW    | 7             | -     |

| ESD Protection on all Pins            | -                                     |             | 1               | -    | -    | kV    | -             | 3     |

|                                       |                                       | DIGITAL I/O |                 |      |      | ı     |               |       |

| Input Logic LOW                       | V <sub>IL</sub>                       |             | -               | -    | 0.8  | V     | 1             | -     |

| Input Logic HIGH                      | V <sub>IH</sub>                       |             | 2.1             | -    | -    | V     | 1             | -     |

| Output Logic LOW                      | V <sub>OL</sub>                       |             | -               | 0.2  | 0.4  | V     | 1             | -     |

| Output Logic HIGH                     | V <sub>OH</sub>                       |             | IO_VDD<br>- 0.4 | -    | -    | V     | 1             | -     |

|                                       |                                       | INPUT       | 1               |      |      |       |               |       |

| Input Common Mode Voltage             | V <sub>CMIN</sub>                     |             | -               | 1.45 | -    | V     | 6             | 4     |

| TEQT I EVELQ                          | · · · · · · · · · · · · · · · · · · · |             | NOTES           | 1    |      |       |               |       |

## TEST LEVELS

- 1. Production test at room temperature and nominal supply voltage with guardbands for supply and temperature ranges.

- 2. Production test at room temperature and nominal supply voltage with guardbands for supply and temperature ranges using correlated test.

- ${\it 3. \ Production \ test \ at \ room \ temperature \ and \ nominal \ supply \ voltage.}$

- 4. QA sample test.

- 5. Calculated result based on Level 1, 2, or 3.

- 6. Not tested. Guaranteed by design simulations.

- 7. Not tested. Based on characterization of nominal parts.

- 8. Not tested. Based on existing design/characterization data of similar product.

- 9. Indirect test.

## NOTES

- 1. All DC and AC electrical parameters within specification.

- 2. Guaranteed functional.

- 3. MIL STD 883 ESD protection will be applied to all pins on the device.

- 4. Input common mode is set by internal biasing resistors.

# 2.3 AC ELECTRICAL CHARACTERISTICS

$T_A = 0$ °C to 70°C, unless otherwise shown

| PARAMETER                                | SYMBOL             | CONDITIONS                                        | MIN     | TYP                           | MAX   | UNITS                | TEST<br>LEVEL | NOTES    |

|------------------------------------------|--------------------|---------------------------------------------------|---------|-------------------------------|-------|----------------------|---------------|----------|

|                                          | <u> </u>           | SYS                                               | TEM     |                               | I     | 1                    | 1             | <u> </u> |

| Serial Digital Input Jitter<br>Tolerance | IJT                | Nominal loop bandwidth                            | 0.6     | -                             | -     | UI                   | 1             | 1        |

| Master Mode Asynchronous                 |                    | No data to HD                                     | -       | -                             | 468   | us                   | 6,7           | 2        |

| Lock Time                                |                    | HD to SD                                          | -       | -                             | 260   |                      |               |          |

|                                          |                    | HD to DVB-ASI                                     | -       | -                             | 135   |                      |               |          |

|                                          |                    | No data to SD                                     | -       | -                             | 340   |                      |               |          |

|                                          |                    | SD to HD                                          | -       | -                             | 256   |                      |               |          |

|                                          |                    | SD to DVB-ASI                                     | -       | -                             | 173   |                      |               |          |

|                                          |                    | No data to DVB-ASI                                | -       | -                             | 65    |                      |               |          |

|                                          |                    | DVB-ASI to SD                                     | -       | -                             | 227   |                      |               |          |

|                                          |                    | DVB-ASI to HD                                     | -       | -                             | 215   |                      |               |          |

| Slave Mode Asynchronous                  |                    | No data to HD                                     | -       | -                             | 240   | us                   | 6,7           | 2        |

| Lock Time                                |                    | No data to SD                                     | -       | -                             | 197   |                      |               |          |

|                                          |                    | No data to DVB-ASI                                | -       | -                             | 68    |                      |               |          |

| Device Latency                           |                    | 10-bit SD                                         | -       | 21                            | -     | PCLK                 | 6             | -        |

|                                          |                    | 20-bit HD                                         | -       | 21                            | -     | PCLK                 | 6             | -        |

|                                          |                    | DVB-ASI                                           | -       | 11                            | -     | PCLK                 | 6             | -        |

| Reset Pulse Width                        | t <sub>reset</sub> |                                                   | 1       | -                             | -     | ms                   | 7             | 3        |

|                                          | •                  | SERIAL DIGITAL DI                                 | FFEREN  | TIAL INPUT                    | 1     | •                    |               | l        |

| Serial Input Data Rate                   | DR <sub>DDI</sub>  |                                                   | -       | 1.485,<br>1.485/1.001,<br>270 | -     | Gb/s<br>Gb/s<br>Mb/s | 1             | -        |

| Serial Digital Input Signal<br>Swing     | $\Delta V_{DDI}$   | Differential with internal 100Ω input termination | 200     | 600                           | 1000  | mV <sub>p-p</sub>    | 1             | -        |

|                                          |                    | PARALLE                                           | L OUTPU | Т                             |       |                      |               |          |

| Parallel Clock Frequency                 | f <sub>PCLK</sub>  |                                                   | 13.5    | -                             | 148.5 | MHz                  | 1             |          |

| Parallel Clock Duty Cycle                | DC <sub>PCLK</sub> |                                                   | 40      | 50                            | 60    | %                    | 1             |          |

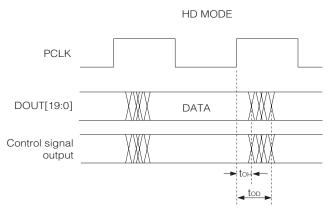

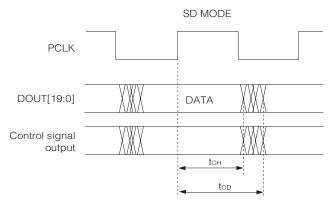

| Output Data Hold Time                    | t <sub>OH</sub>    | 20-bit HD                                         | 1.0     | -                             | -     | ns                   | 1             | 3        |

|                                          |                    | 10-bit SD                                         | 19.5    | -                             | -     | ns                   | 1             |          |

| Output Data Delay Time                   | t <sub>OD</sub>    | 20-bit HD                                         | -       | -                             | 4.5   | ns                   | 1             | 3        |

|                                          |                    | 10-bit SD                                         | -       | -                             | 22.8  | ns                   | 1             |          |

| Output Data Rise/Fall Time               | tr/tf              |                                                   | -       | -                             | 1.5   | ns                   | 3             | 3        |

# 2.3 AC ELECTRICAL CHARACTERISTICS (CONTINUED)

$T_A = 0$ °C to 70°C, unless otherwise shown

| PARAMETER                      | SYMBOL             | CONDITIONS | MIN  | TYP | MAX  | UNITS | TEST<br>LEVEL | NOTES |

|--------------------------------|--------------------|------------|------|-----|------|-------|---------------|-------|

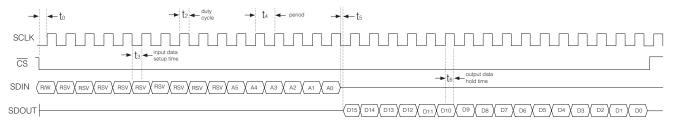

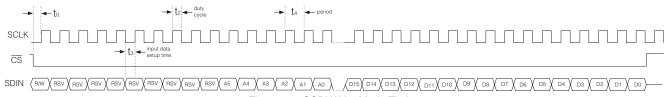

|                                |                    | G          | SPI  |     | •    |       | •             |       |

| GSPI Input Clock Frequency     | f <sub>SCLK</sub>  |            | -    | -   | 6.6  | MHz   | 1             | -     |

| GSPI Input Clock Duty<br>Cycle | DC <sub>SCLK</sub> |            | 40   | 50  | 60   | %     | 3             | -     |

| GSPI Input Data Setup Time     |                    |            | 0    | -   | -    | ns    | 3             | -     |

| GSPI Input Data Hold Time      |                    |            | -    | -   | 1.43 | ns    | 3             | -     |

| GSPI Output Data Hold<br>Time  |                    |            | 2.10 | -   | -    | ns    | 3             | -     |

| GSPI Output Data Delay<br>Time |                    |            | -    | -   | 7.27 | ns    | 3             | -     |

### TEST LEVELS

- 1. Production test at room temperature and nominal supply voltage with guardbands for supply and temperature ranges.

- Production test at room temperature and nominal supply voltage with guardbands for supply and temperature ranges using correlated test.

- 3. Production test at room temperature and nominal supply voltage.

- 4. QA sample test.

- 5. Calculated result based on Level 1, 2, or 3.

- 6. Not tested. Guaranteed by design simulations.

- 7. Not tested. Based on characterization of nominal parts.

- 8. Not tested. Based on existing design/characterization data of similar product.

- 9. Indirect test.

### **NOTES**

- 1. 6MHz sinewave modulation.

- 2. HD = 1080i, SD = 525i

- 3. See Section 3.13, Figure 20.

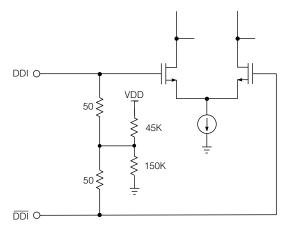

# 2.4 INPUT/OUTPUT CIRCUITS

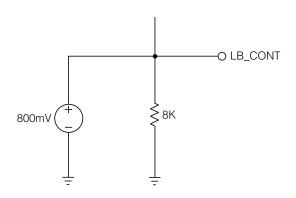

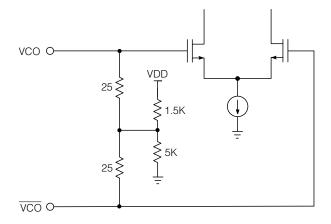

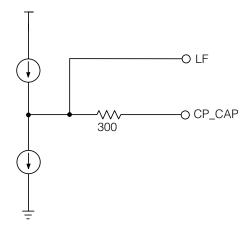

All resistors in ohms, all capacitors in farads, unless otherwise shown.

Figure 2 Serial Digital Input

Figure 4 PLL Loop Bandwidth Control

Figure 3 VCO Input

Figure 5 VCO Control Output & PLL Lock Time Capacitor

2.5 HOST INTERFACE MAP

| REGISTER NAME      | ADDRESS | 15       | 14       | 13       | 12       | 11       | 10                      | 6                      | 80                      | 7                     | 9                | 2                 | 4                     | က                     | 2                 | -                | 0                |

|--------------------|---------|----------|----------|----------|----------|----------|-------------------------|------------------------|-------------------------|-----------------------|------------------|-------------------|-----------------------|-----------------------|-------------------|------------------|------------------|

| ERROR_MASK         | 026h    | Not Used | VD_STD_<br>ERR_<br>MASK | F_CRC_<br>ERR_<br>MASK | AP_CRC_<br>ERR_<br>MASK | LOCK_<br>ERR_<br>MASK | CCS_ERR_<br>MASK | YCS_ERR_<br>MASK  | CCRC_<br>ERR_<br>MASK | YCRC_<br>ERR_<br>MASK | LNUM_ER<br>R_MASK | SAV_ERR_<br>MASK | EAV_ERR_<br>MASK |

| FF_LINE_END_F1     | 025h    | Not Used                | 69                     | 8q                      | /q                    | 99               | 99                | b4                    | P3                    | p2                | p1               | 09               |

| FF_LINE_START_F1   | 024h    | Not Used                | 6q                     | 8q                      | P2                    | 9q               | 99                | p4                    | p3                    | p2                | p1               | 09               |

| FF_LINE_END_F0     | 023h    | Not Used                | 6q                     | 8q                      | 2q                    | 99               | 99                | p4                    | Eq.                   | p2                | p1               | 09               |