# MX·COM, INC. MiXed Signal ICs

# CTCSS/DCS/SelCall Processor

## PRELIMINARY INFORMATION

## Features

- Fast CTCSS Detection

- Full Duplex CTCSS and SelCall

- Full 23/24 Bit DCS Codec

- SelCall Codec

- Non Predictive Tone Detection

- Low Power 3.3V/5.0V Operation

- Variable Gain Audio Filter

- Programmable:

- Tone Decoder Tone Encoder Modulator Drivers Comparator for RSSI

- Pin compatible with reduced function MX818

DATA BULLETIN

**MX828**

• Full control via 4-Wire Serial Interface

The MX828 is a low power SelCall, CTCSS, and DCS signal processor designed for use in the latest generation of LMR (Land Mobile Radio) equipment where sub-audible signaling is required for functions such as Trunking Control, Selective Calling, and Group Calling applications. The MX828 is full duplex and offers many advanced features to assist in the design of new Sub-Audible and in-band based systems. These include: a programmable tone decoder which may be set to respond to between 1 and 15 CTCSS or SelCall tones with minimum software intervention, a Fast/Predictive CTCSS detector that can respond to a single programmed tone in less than 60ms or provide an output if CTCSS tone is present at the detector input, two high resolution tone encoders that accurately generate CTCSS or SelCall tones, and a full 23/24 bit DCS encoder and decoder. The MX828 also provides a general purpose timer, a comparator with a programmable threshold, and a summing amplifier with two adjustable gain blocks to facilitate design integration and reduce part count.

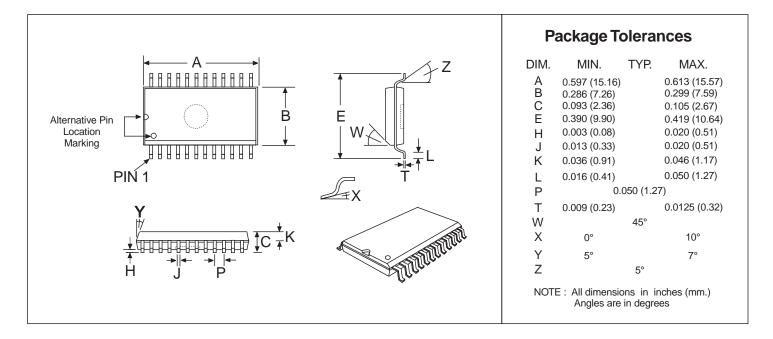

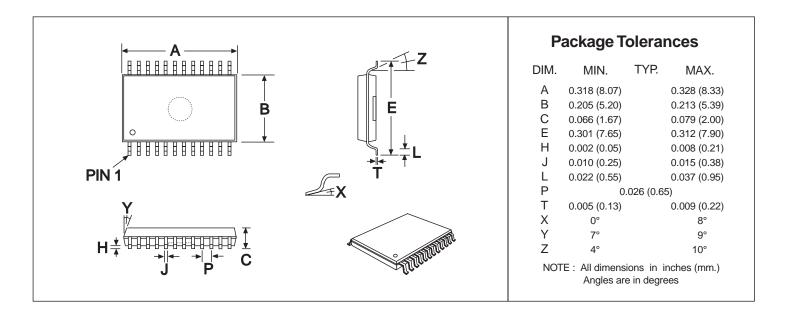

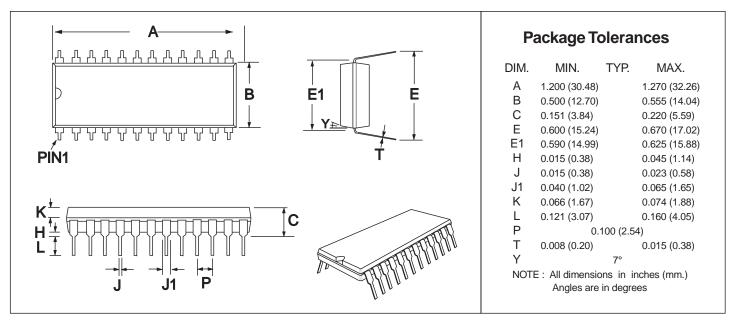

The MX828 may be used with a 3.0 to 5.5 volt supply and is available in the following packages: 24-pin SSOP (MX828DS), 24-pin SOIC (MX828DW), and 24-pin PDIP (MX828P).

# Applications

- Radio Systems Requiring Sub-Audible Signaling Trunking Control Selective Calling Group Calling

- Increased Efficiency Scanning Systems Trunking Systems

Section

All trademarks and service marks are held by their respective companies.

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USA

# CONTENTS

#

MX•COM, Inc. reserves the right to change specifications at any time and without notice.

Page

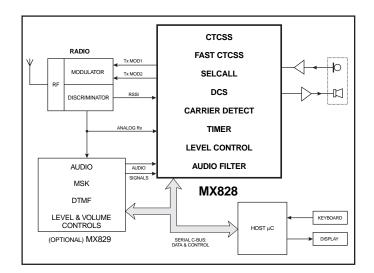

## 1. Block Diagram

Figure 1: Block Diagram

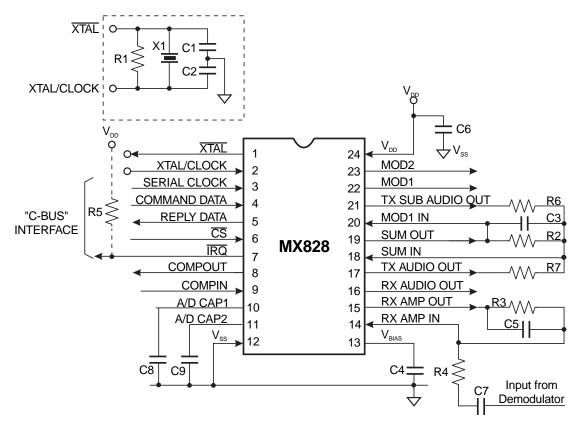

# 2. Signal List

| Pin No. | Name              | Туре   | Description                                                                                                                                                                                                                                                                                                                                                     |

|---------|-------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | XTAL              | output | The inverted output of the on-chip oscillator.                                                                                                                                                                                                                                                                                                                  |

| 2       | XTAL/CLOCK        | input  | The input to the on-chip oscillator, for external Xtal circuit or clock.                                                                                                                                                                                                                                                                                        |

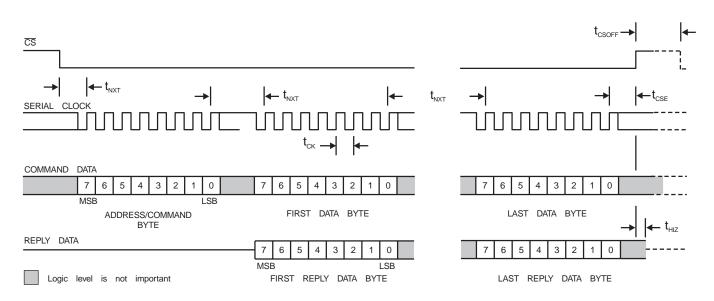

| 3       | SERIAL CLOCK      | input  | The "C-BUS" serial clock input. This clock, produced by the $\mu$ C, is used for timing transfer of commands and data to and from the device. (Figure 4).                                                                                                                                                                                                       |

| 4       | COMMAND DATA      | input  | The "C-BUS" serial data input from the $\mu$ C. Data is loaded into this device in 8-bit bytes, MSB (B7) first, and LSB (B0) last, synchronized to the SERIAL CLOCK. (Figure 4).                                                                                                                                                                                |

| 5       | REPLY DATA        | output | The "C-BUS" serial data output to the $\mu$ C. The transmission of REPLY DATA bytes is synchronized to the SERIAL CLOCK under the control of the $\overline{CS}$ input. This 3-state output is held at high impedance when not sending data to the $\mu$ C. (Figure 4).                                                                                         |

| 6       | CS                | input  | The "C-BUS" data loading control function: this input is provided by the $\mu$ C. Data transfer sequences are initiated, completed or aborted by the $\overline{CS}$ signal (Figure 4).                                                                                                                                                                         |

| 7       | IRQ               | output | This output indicates an interrupt condition to the $\mu$ C by going to a logic "0".<br>This is a "wire-ORable" output, enabling the connection of up to 8<br>peripherals to 1 interrupt port on the $\mu$ C. This pin has a low impedance<br>pulldown to logic "0" when active and a high-impedance when inactive. An<br>external pullup resistor is required. |

|         |                   |        | The conditions that cause interrupts are indicated in the IRQ FLAG register<br>and are effective if not masked out by a corresponding bit in the IRQ MASK<br>register.                                                                                                                                                                                          |

| 8       | COMPOUT           | output | The output of the comparator.                                                                                                                                                                                                                                                                                                                                   |

| 9       | COMPIN            | input  | The input to the comparator.                                                                                                                                                                                                                                                                                                                                    |

| 10      | A/D CAP 1         | output | An internal reference voltage for the CTCSS A/D. By<br>passed to $V_{SS}$ with an external capacitor.                                                                                                                                                                                                                                                           |

| 11      | A/D CAP 2         | output | An internal reference voltage for the DCS A/D. By<br>passed to $V_{\mbox{\scriptsize SS}}$ with an external capacitor.                                                                                                                                                                                                                                          |

| 12      | V <sub>SS</sub>   | Power  | Negative supply (ground).                                                                                                                                                                                                                                                                                                                                       |

| 13      | V <sub>BIAS</sub> | output | A bias line for the internal circuitry, held at $V_{DD}/2$ . This pin must be bypassed by a capacitor mounted close to the device pins.                                                                                                                                                                                                                         |

| 14      | RX AMP IN         | input  | The inverting input to the Rx input amplifier.                                                                                                                                                                                                                                                                                                                  |

| 15      | RX AMP OUT        | output | Output of the Rx input amplifier                                                                                                                                                                                                                                                                                                                                |

| 16      | RX AUDIO OUT      | output | Output of the Rx audio filter section.                                                                                                                                                                                                                                                                                                                          |

| 17      | TX AUDIO OUT      | output | Output of the SelCall tone generator.                                                                                                                                                                                                                                                                                                                           |

| 18      | SUM IN            | input  | Input to the audio summing amplifier.                                                                                                                                                                                                                                                                                                                           |

| 19      | SUM OUT           | output | Output of the audio summing amplifier.                                                                                                                                                                                                                                                                                                                          |

| 20      | MOD1 IN           | input  | Input to MOD1 audio gain control.                                                                                                                                                                                                                                                                                                                               |

| 21      | TX SUB AUDIO OUT  | output | Output of the CTCSS or DCS Tx tone generator.                                                                                                                                                                                                                                                                                                                   |

| 22      | MOD1              | output | Output of MOD1 audio gain control.                                                                                                                                                                                                                                                                                                                              |

| 23      | MOD2              | output | Output of MOD2 audio gain control.                                                                                                                                                                                                                                                                                                                              |

| 24      | V <sub>DD</sub>   | Power  | Positive supply. Levels and voltages are dependent upon this supply. This pin should be bypassed to $V_{SS}$ by a capacitor.                                                                                                                                                                                                                                    |

Table 1: Signal List

## 3. External Components

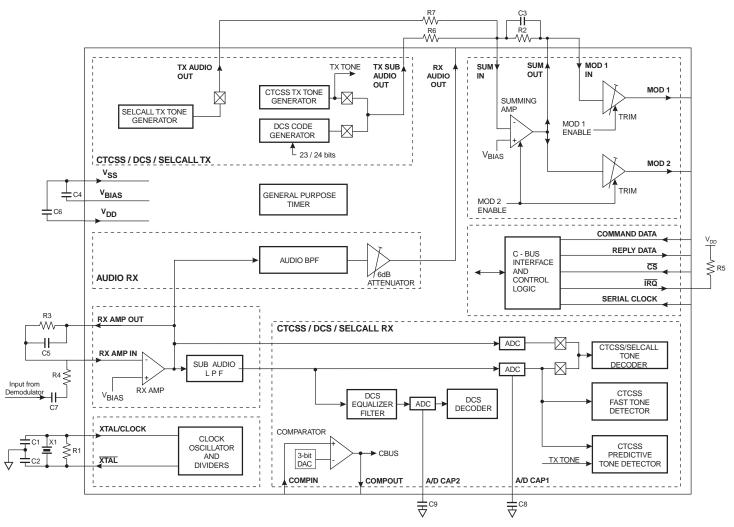

Figure 2: Recommended External Components

| R1 |        | 1MΩ           | ±5%  | C3 |        | 100pF          | ±20%    |

|----|--------|---------------|------|----|--------|----------------|---------|

| R2 |        | 100k $\Omega$ | ±10% | C4 |        | 0.1µF          | ±20%    |

| R3 |        | 100k $\Omega$ | ±10% | C5 |        | 100pF          | ±20%    |

| R4 | Note 2 |               | ±10% | C6 |        | 0.1µF          | ±20%    |

| R5 |        | $22k\Omega$   | ±10% | C7 | Note 2 |                | ±20%    |

| R6 | Note 1 |               | ±10% | C8 |        | 0.1µF          | ±20%    |

| R7 | Note 1 |               | ±10% | C9 |        | 1.0µF to 3.3µF | ±20%    |

| C1 |        | 22pF          | ±20% |    |        |                |         |

| C2 |        | 22pF          | ±20% | X1 | Note 3 | 4.032MHz       | ±100ppm |

**Table 2: External Components**

© 1997 MX•COM Inc. www.mxcom.com Tele: 800 638-5577 336 744-5050 Fax: 336 744-5054 Doc. # 20480161.002 4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USA All trademarks and service marks are held by their respective companies.

#### **External Components Notes:**

1. R2, R6, R7 and C3 form the gain components for the Summing Amplifier. R6 and R7 should be chosen as required from the system specification, using the following formula:

Tx Sub Audio Gain =

$$-\frac{R2}{R6}$$

Tx Audio Gain =  $-\frac{R2}{R7}$

2. R3, R4, C5 and C7 form the gain components for the Rx Input Amplifier. R4 should be chosen as required by the signal level, using the following formula:

Gain =

$$-\frac{R3}{R4}$$

C7 x R4 should be chosen so as not to compromise the low frequency performance of this product.

For best results, a crystal oscillator design should drive the clock inverter input with signal levels of at least 40% of V<sub>DD</sub>, peak to peak. Tuning fork crystals generally cannot meet this requirement. To obtain crystal oscillator design assistance, consult your crystal manufacturer.

## 4. General Description

The MX828 is a signaling encoder/decoder for use in land mobile radio equipment, see Figure 1. The transmitter section of the MX828 has independently controllable tone generators for sub-audio (CTCSS) and inband (SelCall) signaling. Also featured is a DCS code generator, which may be used in place of the CTCSS tone generator.

The receiver section of the MX828 has a fast/predictive CTCSS tone detector which operates in parallel with a DCS decoder and a CTCSS/SelCall tone decoder. The latter is switchable to perform either CTCSS or SelCall tone decoding of a user-programmable set of up to 15 tones. In the CTCSS mode it performs a more accurate (but slower) analysis of the tones detected by the fast/predictive CTCSS tone detector, which is a single detector that is switchable to provide either a fast response to any CTCSS tone (FAST DETECT mode) or a fast response to a single user-programmed CTCSS tone (PREDICTIVE mode).

Both the DCS transmit and receive bit rates are fixed at 134.4bps.

Other functions on the MX828 are a comparator with programmable threshold level, a general purpose timer and a summing amplifier with two adjustable gain blocks, which may be used for two point modulation, for example. All MX828 functions are controlled by an external  $\mu$ C over the "C-BUS" interface, a serial interface designed to reduce interference levels in radio equipment.

## 4.1 Software Description

### 4.1.1 Command Summary

The following table contains a brief description of all valid Commands. Details follow below.

|                                   |                          |                        |                 | DATA E                                                                       | BYTE(S)              |  |

|-----------------------------------|--------------------------|------------------------|-----------------|------------------------------------------------------------------------------|----------------------|--|

| REGISTER NAME                     | SECTION                  | HEX ADDRESS<br>COMMAND | READ /<br>WRITE | BYTE 1                                                                       | BYTE 2               |  |

| General Reset                     | 4.4.1                    | \$01                   | W               | none                                                                         | none                 |  |

| Sub-Audio Control                 | 4.4.2                    | \$80                   | W               | Refer to Bit<br>Description                                                  | none                 |  |

| SelCall<br>Sub-Audio Status       | 4.5<br>4.6.1             | \$81                   | R               | Refer to Bit<br>Description                                                  | none                 |  |

| Sub-Audio Set-Up                  | 4.4.3                    | \$82                   | W               | Refer to Bit<br>Description                                                  | none                 |  |

| CTCSS<br>TX/ Fast RX<br>Frequency | 4.4.10                   | \$83                   | W               | Specify Tx or Fast Rx<br>Frequency per command \$<br>& \$83 Bit descriptions |                      |  |

| RX Tone Program                   | 4.4.11                   | \$84                   | W               | 1 of 15 possible Registers<br>Select & Decode Frequencies                    |                      |  |

| DCS Code                          | 4.4.4                    | \$85                   | W               | Byte 3 of 3                                                                  | none                 |  |

| DCS Code                          | 4.4.5                    | \$86                   | W               | Byte 2 of 3                                                                  | none                 |  |

| DCS Code                          | 4.4.6                    | \$87                   | W               | Byte 1 of 3                                                                  | none                 |  |

| General Control                   | 4.4.7                    | \$88                   | W               | Refer to Bit<br>Description                                                  | none                 |  |

| Audio Control                     | 4.4.12                   | \$8A                   | W               | Mod 1<br>Attenuation                                                         | Mod 2<br>Attenuation |  |

| General Purpose<br>Timer          | 4.4.8                    | \$8B                   | W               | Refer to Bit<br>Description                                                  | none                 |  |

| SelCall TX                        | 4.4.13<br>4.4.2<br>4.4.3 | \$8D                   | W               | Specify TX SelCall<br>Frequencies                                            |                      |  |

| IRQ Mask                          | 4.4.9                    | \$8E                   | W               | Refer to Bit<br>Description                                                  | none                 |  |

| IRQ Flag                          | 4.5<br>4.6.2             | \$8F                   | R               | Refer to Bit<br>Description                                                  | none                 |  |

Table 3: Command Summary

#### 4.1.2 Address/Commands

Instructions and data are transferred, via "C-BUS", in accordance with the timing information given in Figure 4. Instruction and data transactions to and from the MX828 consist of an Address/Command (A/C) byte followed by either:

- (i) a further instruction or data (1 or 2 bytes) or

- (ii) a status or Rx data reply (1 byte)

## 4.2 8-bit Write Only Registers

| HEX<br>ADDRESS/<br>COMMAND | REGISTER<br>NAME      | BIT 7<br>(D7)            | BIT 6<br>(D6)             | BIT 5<br>(D5)            | BIT 4<br>(D4)   | BIT 3<br>(D3)   | BIT 2<br>(D2)           | BIT 1<br>(D1) | BIT 0<br>(D0)       |

|----------------------------|-----------------------|--------------------------|---------------------------|--------------------------|-----------------|-----------------|-------------------------|---------------|---------------------|

| \$01                       | GENERAL<br>RESET      | N/A                      | N/A                       | N/A                      | N/A             | N/A             | N/A                     | N/A           | N/A                 |

| \$80                       | SIGNALLING<br>CONTROL | SUBAUDIO<br>TX<br>ENABLE | TONE<br>DECODER<br>ENABLE | FAST<br>DETECT<br>ENABLE | 0               | 0               | SELCALL<br>TX<br>ENABLE | 0             | DCS<br>RX<br>ENABLE |

|                            |                       | TOT                      |                           | R BANDW                  | IDTH            | FAST CTCSS      |                         |               |                     |

| \$82                       | SIGNALLING            | MSB                      |                           |                          | LSB             | MODE<br>DETECT/ | TONE<br>DECODER         | SUBAUDIO      | DCS                 |

|                            | SET-UP                | BIT 3                    | BIT 2                     | BIT 1                    | BIT 0           | PREDICTIVE      | MODE                    | TX MODE       | 23/24               |

|                            |                       |                          | I                         |                          | DCS             | BYTE 3          |                         |               |                     |

| \$85                       | DCS                   | OPTIONAL<br>MSB          |                           |                          |                 |                 |                         |               |                     |

|                            | BYTE 3                | BIT 23                   | BIT 22                    | BIT 21                   | BIT 20          | BIT 19          | BIT 18                  | BIT 17        | BIT 16              |

|                            |                       |                          |                           |                          | DCS             | BYTE 2          |                         | [             |                     |

| \$86                       | DCS                   |                          |                           |                          |                 |                 |                         |               |                     |

|                            | BYTE 2                | BIT 15                   | BIT 14                    | BIT 13                   | BIT 12          | BIT 11          | BIT 10                  | BIT 9         | BIT 8               |

|                            |                       |                          |                           |                          | DCS             | BYTE 1          |                         |               | 1                   |

| \$87                       | DCS                   |                          |                           |                          |                 |                 |                         |               | LSB                 |

|                            | BYTE 1                | BIT 7                    | BIT 6                     | BIT 5                    | BIT 4           | BIT 3           | BIT 2                   | BIT 1         | BIT 0               |

|                            |                       |                          |                           | BPF                      | MSB             |                 | LSB                     |               |                     |

| \$88                       | GENERAL               | BPF                      | BPF                       | 6dB                      | DAC             | DAC             | DAC                     | GP TIMER      | GP TIMER            |

|                            | CONTROL               | ENABLE                   | UN-MUTE                   | PAD                      | BIT 2           | BIT 1           | BIT 0                   | ENABLE        | RE-CYCLE            |

|                            | GENERAL               |                          | 1                         |                          | GENERAL PL      | JRPOSE TIME     | R                       |               | 1                   |

| \$8B                       | PURPOSE               | MSB                      |                           |                          |                 |                 |                         |               | LSB                 |

|                            | TIMER                 | BIT 7                    | BIT 6                     | BIT 5                    | BIT 4           | BIT 3           | BIT 2                   | BIT 1         | BIT 0               |

|                            |                       |                          | GP TIMER                  | COMP                     | COMP            | TONE            | CTCSS                   |               | DCS                 |

| \$8E                       | IRQ                   | 0                        | IRQ                       | 0 to 1                   | 1 to 0          | IRQ             | FAST IRQ                | 0             | IRQ                 |

|                            | MASK                  |                          | MASK                      | IRQ MASK                 | IRQ MASK        | MASK            | MASK                    |               | MASK                |

| \$9C                       |                       |                          |                           | Reserved                 | d for later use | 9               |                         |               |                     |

Table 4: 8-bit Write Only Registers

## 4.3 16-bit Write Only Registers

| HEX<br>ADDRESS/<br>COMMAND | REGISTER<br>NAME | BIT 7<br>(D7) | BIT 6<br>(D6)   | BIT 5<br>(D5) | BIT 4<br>(D4)              | BIT 3<br>(D3) | BIT 2<br>(D2) | BIT 1<br>(D1) | BIT 0<br>(D0) |  |

|----------------------------|------------------|---------------|-----------------|---------------|----------------------------|---------------|---------------|---------------|---------------|--|

|                            | CTCSS TX/        |               |                 |               | CTCSS TX/FAST RX FREQUENCY |               |               |               |               |  |

| \$83                       | FAST RX          | CTCSS (TX)    | 0               | 0             | MSB                        |               |               |               |               |  |

|                            | FREQUENCY (1)    | NOTONE        |                 |               | BIT 12                     | BIT 11        | BIT 10        | BIT 9         | BIT 8         |  |

|                            | CTCSS TX/        |               |                 | CTCS          | S TX/FAST I                | RX FREQUE     | NCY           |               |               |  |

|                            | FAST RX          |               |                 |               |                            |               |               |               | LSB           |  |

|                            | FREQUENCY (2)    | BIT 7         | BIT 6           | BIT 5         | BIT 4                      | BIT 3         | BIT 2         | BIT 1         | BIT 0         |  |

|                            | RX TONE          |               | TONE AD         | DRESS         |                            |               | TONE FR       | EQUENCY       |               |  |

| \$84                       | PROGRAM          | MSB           |                 |               | LSB                        | MSB           |               |               |               |  |

|                            | (1)              | BIT 3         | BIT 2           | BIT 1         | BIT 0                      | BIT 11        | BIT 10        | BIT 9         | BIT 8         |  |

|                            | RX TONE          |               |                 |               | TONE FRE                   | QUENCY        |               |               |               |  |

|                            | PROGRAM          |               |                 |               |                            |               |               |               | LSB           |  |

|                            | (2)              | BIT 7         | BIT 6           | BIT 5         | BIT 4                      | BIT 3         | BIT 2         | BIT 1         | BIT 0         |  |

|                            | AUDIO            |               |                 |               |                            |               | MOD 1         |               |               |  |

| \$8A                       | CONTROL          | 0             | 0               | MOD 1         | MSB                        |               |               |               | LSB           |  |

|                            | (1)              |               |                 | ENABLE        | BIT 4                      | BIT 3         | BIT 2         | BIT 1         | BIT 0         |  |

|                            | AUDIO            |               |                 |               |                            |               | MOD 2         |               |               |  |

|                            | CONTROL          | 0             | 0               | MOD 2         | MSB                        |               |               |               | LSB           |  |

|                            | (2)              |               |                 | ENABLE        | BIT 4                      | BIT 3         | BIT 2         | BIT 1         | BIT 0         |  |

|                            |                  |               | SELCALL TX TONE |               |                            |               |               |               |               |  |

| \$8D                       | SELCALL TX       | SELCALL       | 0               | 0             | MSB                        |               |               |               |               |  |

|                            | (1)              | NOTONE        |                 |               | BIT 12                     | BIT 11        | BIT 10        | BIT 9         | BIT 8         |  |

|                            |                  |               |                 |               | SELCALL                    | TX TONE       |               |               |               |  |

|                            | SELCALL TX       |               |                 |               |                            |               |               |               | LSB           |  |

|                            | (2)              | BIT 7         | BIT 6           | BIT 5         | BIT 4                      | BIT 3         | BIT 2         | BIT 1         | BIT 0         |  |

Table 5: 16-bit Write Only Registers

© 1997 MX•COM Inc. www.mxcom.com Tele: 800 638-5577 336 744-5050 Fax: 336 744-5054 Doc. # 20480161.002 All trademarks and service marks are held by their respective companies.

## 4.4 Write Only Register Description

## 4.4.1 GENERAL RESET (Hex address \$01)

| REGISTER NAME                |     | HEX<br>ADDRESS | BIT 7<br>(D7) | BIT 6<br>(D6) | BIT 5<br>(D5) | BIT 4<br>(D4) | BIT 3<br>(D3) | BIT 2<br>(D2) | BIT 1<br>(D1) | BIT 0<br>D0) |

|------------------------------|-----|----------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|--------------|

| SIGNALING CONTROL            |     | \$80           | 0             | 0             | 0             | 0             | 0             | 0             | 0             | 0            |

| SELCALL & SUB-AUDIO STATUS   |     | \$81           | 0             | 0             | 0             | 0             | х             | х             | х             | Х            |

| SIGNALING SET-UP             |     | \$82           | 0             | 0             | 0             | 0             | 0             | 0             | 0             | 0            |

| CTCSS TX / FAST RX FREQUENCY | (1) | \$83           | 0             | 0             | 0             | 0             | 0             | 0             | 0             | 0            |

| CTCSS TX / FAST RX FREQUENCY | (2) |                | 0             | 0             | 0             | 0             | 0             | 0             | 0             | 0            |

| RX TONE PROGRAM              | (1) | \$84           | 0             | 0             | 0             | 0             | 0             | 0             | 0             | 0            |

| RX TONE PROGRAM              | (2) |                | 0             | 0             | 0             | 0             | 0             | 0             | 0             | 0            |

| DCS BYTE 3                   |     | \$85           | 0             | 0             | 0             | 0             | 0             | 0             | 0             | 0            |

| DCS BYTE 2                   |     | \$86           | 0             | 0             | 0             | 0             | 0             | 0             | 0             | 0            |

| DCS BYTE 1                   |     | \$87           | 0             | 0             | 0             | 0             | 0             | 0             | 0             | 0            |

| GENERAL CONTROL              |     | \$88           | 0             | 0             | 0             | 0             | 0             | 0             | 0             | 0            |

| AUDIO CONTROL                | (1) | \$8A           | 0             | 0             | 0             | 0             | 0             | 0             | 0             | 0            |

| AUDIO CONTROL                | (2) |                | 0             | 0             | 0             | 0             | 0             | 0             | 0             | 0            |

| GENERAL PURPOSE TIMER        |     | \$8B           | 0             | 0             | 0             | 0             | 0             | 0             | 0             | 0            |

| SELCALL TX                   | (1) | \$8D           | 0             | 0             | 0             | 0             | 0             | 0             | 0             | 0            |

| SELCALL TX                   | (2) |                | 0             | 0             | 0             | 0             | 0             | 0             | 0             | 0            |

| IRQ MASK                     |     | \$8E           | 0             | 0             | 0             | 0             | 0             | 0             | 0             | 0            |

| IRQ FLAG                     |     | \$8F           | 0             | 0             | 0             | 0             | 0             | 0             | 0             | 0            |

The reset command has no data attached to it. It sets the device registers into the specific (all powersaved) states as listed below:

X = undefined

#### Table 6: GENERAL RESET (Hex address \$01)

## 4.4.2 SIGNALING CONTROL Register (Hex address \$80)

This register is used to control the functions of the device as described below:

| SUBAUDIO TX<br>ENABLE<br>(Bit 7)       | Bit 7 should be set to "1" to enable the CTCSS/DCS subaudio transmitter. The subaudio Tx type will depend on the state of the SUBAUDIO TX MODE (Bit 1 SIGNALING SET-UP Register \$82).                                                                                           |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TONE DECODER<br>ENABLE                 | Bit 6 should be set to "1" to enable the CTCSS/SelCall tone decoder or the DCS decoder. Note: See Bit 0 for DCS decoder operation.                                                                                                                                               |

| (Bit 6)                                | Bits 7 and 6 should not both be set to "1" when Bit 0 is set to "1" because the DCS function is half-duplex only.                                                                                                                                                                |

| CTCSS FAST DETECT<br>ENABLE<br>(Bit 5) | When this bit is "1", the FAST CTCSS DETECT or FAST CTCSS PREDICTIVE mode is enabled, depending upon the setting of FAST CTCSS MODE (Bit 3 SIGNALING SET-UP Register, \$82). When this bit is "0", both FAST CTCSS DETECT and FAST CTCSS PREDICTIVE tone detectors are disabled. |

| SELCALL TX<br>ENABLE<br>(Bit 2)        | When this bit is "1" the SelCall transmitter is enabled. When this bit is "0" the SelCall transmitter is disabled and powersaved.                                                                                                                                                |

11

| DCS RX ENABLE      | When this bit is "1", the DCS decoder is enabled. When this bit is "0" the DCS decoder is disabled. |

|--------------------|-----------------------------------------------------------------------------------------------------|

| (Bit 0)            | The DCS decoder and the subaudio (CTCSS or DCS) transmitter should not be enabled at the same time. |

| (Bits 4, 3, and 1) | Reserved for future use. These bits should be set to "0".                                           |

Table 7: SIGNALING CONTROL Register (Hex address \$80)

#### 4.4.3 SIGNALING SET-UP Register (Hex address \$82)

This register is used to define the signaling parameters, as described below:

| TONE DECODER<br>BANDWIDTH<br>(Bits 7, 6, 5 and 4) | These four bits set the bandwidth of the CTCSS/SelCall tone decoder according to the table below:                                                                                                                                                                    |

|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FAST CTCSS MODE<br>(Bit 3)                        | When CTCSS FAST DETECT ENABLE (Bit 5 SIGNALING CONTROL Register, \$80) is "1", this bit selects the FAST CTCSS DETECT or the FAST CTCSS PREDICTIVE mode, according to the table below:<br>If the CTCSS FAST DETECT ENABLE bit is "0" then both modes are deselected. |

| TONE DECODER<br>MODE<br>(Bit 2)                   | When this bit is "1" the CTCSS/SelCall tone decoder is set to detect inband (SelCall) tones. When this bit is "0" the tone decoder is set to detect subaudio (CTCSS) tones.                                                                                          |

| SUBAUDIO TX MODE<br>(Bit 1)                       | When this bit is "1" the subaudio transmitter will be set to transmit DCS signals, if enabled. When this bit is "0" the subaudio transmitter will be set to transmit CTCSS signals, if enabled.                                                                      |

| DCS 23/24<br>(Bit 0)                              | When this bit is "1" the DCS transmitter and decoder are configured for a 23-bit code.<br>When this bit is "0" they are configured for a 24-bit code.                                                                                                                |

## Table 8: SIGNALING SET-UP Register (Hex address \$82)

|                       |       |       |       |       | BANDWIDTH   |                 |  |  |

|-----------------------|-------|-------|-------|-------|-------------|-----------------|--|--|

|                       | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Will Decode | Will Not Decode |  |  |

| Recommended for CTCSS | 1     | 0     | 0     | 0     | ±1.1%       | ±2.4%           |  |  |

| Recommended for CCIR  | 1     | 0     | 0     | 1     | ±1.3%       | ±2.7%           |  |  |

|                       | 1     | 0     | 1     | 0     | ±1.6%       | ±2.9%           |  |  |

|                       | 1     | 0     | 1     | 1     | ±1.8%       | ±3.2%           |  |  |

|                       | 1     | 1     | 0     | 0     | ±2.0%       | ±3.5%           |  |  |

|                       | 1     | 1     | 0     | 1     | ±2.2%       | ±3.7%           |  |  |

| Recommended for ZVEI  | 1     | 1     | 1     | 0     | ±2.5%       | ±4.0%           |  |  |

|                       | 1     | 1     | 1     | 1     | ±2.7%       | ±4.2%           |  |  |

### Table 9: TONE DECODER BANDWIDTH

| DETECT/PREDICTIVE<br>Bit 3 | Function        |

|----------------------------|-----------------|

| 0                          | DETECT mode     |

| 1                          | PREDICTIVE mode |

### Table 10: FAST CTCSS MODE

12

#### 4.4.4 DCS BYTE 3 Register (Hex address \$85)

### 4.4.5 DCS BYTE 2 Register (Hex address \$86)

#### 4.4.6 DCS BYTE 1 Register (Hex address \$87)

These three bytes set the code that is transmitted or received in the DCS mode. The LSB bit "0" of the DCS BYTE 1 is transmitted first and the last bit is the MSB bit 23 of DCS BYTE 3 in the 24-bit mode or bit 22 in the 23-bit mode. See Table 22 or refer to the latest version of ANSI/TIA/EIA - 603 specification and programming documentation for DCS standard 23-bit codes.

#### 4.4.7 GENERAL CONTROL Register (Hex address \$88)

This register is used to control the functions of the device as described below:

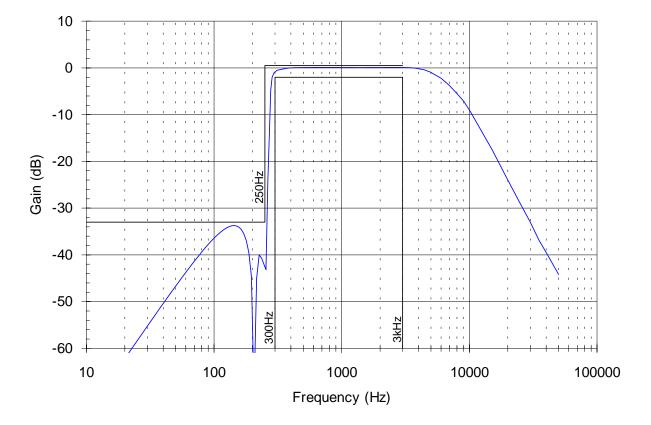

| BPF ENABLE<br>(Bit 7)     | When this bit is "1" the audio band-pass filter is enabled. When this bit is "0" the audio band-pass filter is disabled (powersaved).                                                                                                                                                                                                                                                                                             |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BPF UN-MUTE<br>(Bit 6)    | When this bit is "1" the audio band-pass filter output is switched to the RX AUDIO OUT pin. When this bit is "0" the output of the filter is disconnected from RX AUDIO OUT, which is then in a high impedance state.                                                                                                                                                                                                             |

|                           | This control, along with BPF ENABLE, allows the filter to power up and settle internally before switching the output on, to avoid clicks when coming out of powersave.                                                                                                                                                                                                                                                            |

| BPF 6dB PAD<br>(Bit 5)    | When this bit is "1" a 6dB attenuator is inserted into the output of the audio band-pass filter. When this bit is "0" the output of the audio band-pass filter is not attenuated.                                                                                                                                                                                                                                                 |

| DAC<br>(Bits 4, 3 and 2)  | These three bits set the level of the digital to analogue converter that feeds the negative input of the comparator. The DAC can be set to one of eight levels equally spaced between $V_{SS}$ and $V_{BIAS}$ , not including $V_{SS}$ , but including $V_{BIAS}$ , i.e. with a 5V supply, the lowest level would be 312.5mV set by "000" in bits 2, 3 and 4 and the highest level would be 2.5V set by "111" in bits 2, 3 and 4. |

| TIMER ENABLE<br>(Bit 1)   | When this bit goes to a "1" the general purpose timer is restarted and its internal register is re-loaded from the value specified in the GENERAL PURPOSE TIMER Register (Hex address \$8B). It will then count down from the count held in its internal register. When this bit is "0" the count down is disabled and the last pre-programmed value is retained in the timer's internal register.                                |

| TIMER RE-CYCLE<br>(Bit 0) | When this bit is "1" the general purpose timer will re-load its internal register from the value specified in the GENERAL PURPOSE TIMER Register (Hex Address \$8B) when the count in the internal register reaches zero (i.e. the timeout has expired). It then restarts the count down, so that the timer continuously cycles.                                                                                                  |

|                           | When this bit is "0" the general purpose timer will stop when the count in the internal register reaches zero (i.e. the timeout has expired). The timer can only be restarted by reloading a value into the GENERAL PURPOSE TIMER Register (Hex address \$8B).                                                                                                                                                                    |

|                           | If this bit is switched from "1" to "0" while the timer is enabled then the timer will complete the present count before stopping.                                                                                                                                                                                                                                                                                                |

Table 11: GENERAL CONTROL Register (Hex address \$88)

### 4.4.8 GENERAL PURPOSE TIMER (GPT) Register (Hex address \$8B)

This register is used to preset the value of a countdown timer. Once a binary value has been loaded into this register, it will be automatically transferred to an internal register within the timer. This internal register is then decremented at each count interval (1ms) until it reaches zero. On reaching zero, the GPT IRQ FLAG in the IRQ FLAG Register (Hex address \$8F) is set to "1". An interrupt is generated on the IRQ pin if the GPT IRQ MASK in the IRQ MASK Register (Hex address \$8E) is "1" otherwise the GPT IRQ FLAG remains set to "1" and no interrupt is generated.

When the internal register has reached a count of zero, the action of the timer depends on the setting of the TIMER RE-CYCLE bit in the GENERAL CONTROL Register (Hex address \$88). If the TIMER RE-CYCLE bit is "1" then the timer will re-load the countdown value from the GENERAL PURPOSE TIMER Register and restart the countdown from this value. If the TIME RE-CYCLE bit is "0" then the timer will stop and no further action or timer interrupts will take place until the GENERAL PURPOSE TIMER Register is re-loaded. Loading the GENERAL PURPOSE TIMER with "0" will cause the timer circuitry to be disabled (i.e. powersaved).

#### 4.4.9 IRQ MASK Register (Hex address \$8E)

| (Bits 7 and 1)                     | Reserved for future use. These should be set to "0".                                                                                                                                                                     |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPT IRQ MASK<br>(Bit 6)            | When this bit is set to "1" it enables an interrupt that occurs when GPT IRQ FLAG (Bit 6, IRQ FLAG Register, \$8F) changes from "0" to "1". When this bit is "0" the interrupt is masked.                                |

| COMP 0 to 1<br>IRQ MASK<br>(Bit 5) | When this bit is set to "1" it enables an interrupt that occurs when the comparator output goes from "0" to "1". When this bit is set to "0" the interrupt is masked.                                                    |

| COMP 0 to 1<br>IRQ MASK<br>(Bit 4) | When this bit is set to "1" it enables an interrupt that occurs when the comparator output goes from "1" to "0". When this bit is set to "0" the interrupt is masked.                                                    |

| TONE IRQ MASK<br>(Bit 3)           | When this bit is set to "1" it enables an interrupt that occurs when the TONE IRQ FLAG (Bit 3, IRQ FLAG Register, \$8F) changes from "0" to "1". When this bit is "0" the interrupt is masked.                           |

| CTCSS FAST IRQ MASK<br>(Bit 2)     | When this bit is set to "1" it enables an interrupt that occurs when the CTCSS FAST IRQ FLAG (Bit 2, IRQ FLAG Register, \$8F) changes from "0" to "1". When this bit is "0" the interrupt is masked.                     |

| DCS IRQ MASK<br>(Bit 0)            | When this bit is set to "1" it enables an interrupt that occurs when the DCS DECODE/NO DECODE FLAG (Bit 7, SELCALL & SUB-AUDIO STATUS Register \$81) changes state. When this bit is set to "0" the interrupt is masked. |

This register is used to control the interrupts (IRQs) as described below:

#### Table 12: IRQ MASK Register (Hex address \$8E)

#### 4.4.10 CTCSS TX/FAST RX FREQUENCY Register (Hex address \$83)

This is a 16-bit register. Byte (1) is sent first. When the CTCSS fast detector is enabled, the bits 0 to 12 define the receive frequency which the fast predictive detector is looking for according to the formula below:

$$A = \frac{f_{XTAL} (Hz)}{16 x f_{TONE} (Hz)}$$

where A is the binary number programmed into the 13 bits.

When the CTCSS transmitter is enabled, the bits 0 to 12 control the frequency of the transmitted CTCSS tones according to the formula above.

When the fast detector and the transmitter are both enabled, bits 0-12 define the receive frequency which the fast predictive detector is looking for and the frequency of the transmitted tone according to the formula above. (i.e. Tx Tone = predictive tone).

When Bit 7 in byte (1) is set to "1" the tone output is set at  $V_{BIAS}$  or NOTONE without regard to the number "A" programmed. When Bit 7 is "0" the programmed tone is set on the output. Programming the bits 0 to 12 to "0" puts the Tx into powersave and the output goes to  $V_{BIAS}$ . Powersave is also achieved by disabling the SUBAUDIO Tx and the CTCSS FAST DETECT.

## 4.4.11 RX TONE PROGRAM Register (Hex address \$84)

This is a 16-bit register. Byte (1) is sent first. The two bytes are used to program the center frequencies of up to 15 tones in either the audio or sub-audio band that will be decoded by the receiver.

Each tone is identified by its address in bits 7, 6, 5 and 4 of byte (1). The remaining 12 bits contain the data representing the tone frequency according to the formula below. If a tone is not required the 12 bits should be set to zero.

|          |          |          |          | Byte <sup>·</sup> | 1        |                      |                       |          |          |                                                                         | Byt                  | te 2                   |                      |                       |          |  |  |

|----------|----------|----------|----------|-------------------|----------|----------------------|-----------------------|----------|----------|-------------------------------------------------------------------------|----------------------|------------------------|----------------------|-----------------------|----------|--|--|

| Bit<br>7 | Bit<br>6 | Bit<br>5 | Bit<br>4 | Bit<br>3          | Bit<br>2 | Bit<br>1             | Bit<br>0              | Bit<br>7 | Bit<br>6 | Bit<br>5                                                                | Bit<br>4             | Bit<br>3               | Bit<br>2             | Bit<br>1              | Bit<br>0 |  |  |

| 0        | 0        | 0        | 0        | <                 |          |                      | N                     |          | <> R>    |                                                                         |                      |                        |                      |                       |          |  |  |

| 0        | 0        | 0        | 1        |                   |          |                      |                       |          |          |                                                                         |                      |                        |                      |                       |          |  |  |

| 0        | 0        | 1        | 0        | N is th           | ne binar | y repres             | sentatio              | n of the | •        | R is the nearest 6-bit binary                                           |                      |                        |                      |                       |          |  |  |

| 0        | 0        | 1        | 1        | followi           | ing deci | mal nui              | nber (n               | ):       |          | repres                                                                  | entatio              | n of (r),              | where:               |                       |          |  |  |

| 0        | 1        | 0        | 0        |                   |          |                      |                       |          |          |                                                                         |                      |                        |                      |                       |          |  |  |

| 0        | 1        | 0        | 1        |                   |          |                      |                       |          |          |                                                                         |                      |                        |                      |                       |          |  |  |

| 0        | 1        | 1        | 0        |                   |          |                      |                       |          |          |                                                                         |                      |                        |                      |                       |          |  |  |

| 0        | 1        | 1        | 1        | SUBA              | UDIO (   | CTCSS                | S)                    |          |          | SUBAUDIO (CTCSS)                                                        |                      |                        |                      |                       |          |  |  |

| 1        | 0        | 0        | 0        | n = IN1           | Г (94898 | 2 x f <sub>TON</sub> | E / f <sub>XTAL</sub> | )        |          | r = ((237245/f <sub>XTAL</sub> ) - (n/(4 x f <sub>TONE</sub> ))) x 8400 |                      |                        |                      |                       |          |  |  |

| 1        | 0        | 0        | 1        |                   |          |                      |                       |          |          |                                                                         |                      |                        |                      |                       |          |  |  |

| 1        | 0        | 1        | 0        |                   |          |                      |                       |          |          |                                                                         |                      |                        |                      |                       |          |  |  |

| 1        | 0        | 1        | 1        |                   |          |                      |                       |          |          |                                                                         |                      |                        |                      |                       |          |  |  |

| 1        | 1        | 0        | 0        | INBAN             | ND (SE   |                      |                       |          |          | INBAN                                                                   | ND (SE               | LCALL                  | )                    |                       |          |  |  |

| 1        | 1        | 0        | 1        | n = IN1           | Г (83036 | x f <sub>TONE</sub>  | / f <sub>XTAL</sub> ) |          |          | r = ((20                                                                | )759/f <sub>XT</sub> | <sub>AL</sub> ) - (n/( | 4 x f <sub>TON</sub> | <sub>E</sub> ))) x 96 | 000      |  |  |

| 1        | 1        | 1        | 0        |                   |          |                      |                       |          |          |                                                                         |                      |                        |                      |                       |          |  |  |

#### Table 13: RX TONE PROGRAM Register (Hex address \$84)

Example: To program 100Hz when using the recommended 4.032MHz Xtal in SUBAUDIO (CTCSS) mode.

Thus the 12-bit code is 010111001011

The Hex address represented by bits 7, 6, 5 and 4 in byte (1) is used as the code to indicate which tone has been decoded. This code appears in bits 3, 2, 1 and 0 of the SELCALL and SUB-AUDIO STATUS Register (Hex address \$81). The 15 programmed tones use Hex addresses \$0 - \$E.

#### MX828 PRELIMINARY INFORMATION

### 4.4.12 AUDIO CONTROL Register (Hex address \$8A)

This is a 16-bit register. Byte (1) is sent first. Bits 0 - 5 of the first byte in this register are used to set the attenuation of the Modulator 1 amplifier and bits 0 - 5 of the second byte in this register are used to set the attenuation of the Modulator 2 amplifier, according to Table 14.

|           | BYTE 1              |       |     |   |   |                                                            |    |      |      | BYTE 2 |      |       |       |                               |  |  |  |

|-----------|---------------------|-------|-----|---|---|------------------------------------------------------------|----|------|------|--------|------|-------|-------|-------------------------------|--|--|--|

| 5         | 4                   | 3     | 2   | 1 | 0 | Mod. 1 Attenuation                                         |    | 5    | 4    | 3      | 2    | 1     | 0     | Mod. 2 Attenuation            |  |  |  |

| 0         | Х                   | Х     | Х   | Х | Х | Disabled (V <sub>BIAS</sub> )                              |    | 0    | Х    | Х      | Х    | Х     | Х     | Disabled (V <sub>BIAS</sub> ) |  |  |  |

| 1         | 0                   | 0     | 0   | 0 | 0 | >40dB                                                      |    | 1    | 0    | 0      | 0    | 0     | 0     | >40dB                         |  |  |  |

| 1         | 0                   | 0     | 0   | 0 | 1 | 12.0dB                                                     |    | 1    | 0    | 0      | 0    | 0     | 1     | 6.0dB                         |  |  |  |

| 1         | 0                   | 0     | 0   | 1 | 0 | 11.6dB                                                     |    | 1    | 0    | 0      | 0    | 1     | 0     | 5.8dB                         |  |  |  |

| 1         | 0                   | 0     | 0   | 1 | 1 | 11.2dB 1 0 0 0 1 1 5.6dB                                   |    |      |      |        |      |       |       |                               |  |  |  |

| 1         | 0                   | 0     | 1   | 0 | 0 | 10.8dB                                                     |    | 1    | 0    | 0      | 1    | 0     | 0     | 5.4dB                         |  |  |  |

| 1         | 0                   | 0     | 1   | 0 | 1 | 10.4dB                                                     |    | 1    | 0    | 0      | 1    | 0     | 1     | 5.2dB                         |  |  |  |

| 1         | 0                   | 0     | 1   | 1 | 0 | 10.0dB                                                     |    | 1    | 0    | 0      | 1    | 1     | 0     | 5.0dB                         |  |  |  |

| 1         | 0                   | 0     | 1   | 1 | 1 | 9.6dB                                                      |    | 1    | 0    | 0      | 1    | 1     | 1     | 4.8dB                         |  |  |  |

| 1         | 0                   | 1     | 0   | 0 | 0 | 9.2dB                                                      |    | 1    | 0    | 1      | 0    | 0     | 0     | 4.6dB                         |  |  |  |

| 1         | 0                   | 1     | 0   | 0 | 1 | 8.8dB                                                      |    | 1    | 0    | 1      | 0    | 0     | 1     | 4.4dB                         |  |  |  |

| 1         | 0                   | 1     | 0   | 1 | 0 | 8.4dB                                                      |    | 1    | 0    | 1      | 0    | 1     | 0     | 4.2dB                         |  |  |  |

| 1         | 0                   | 1     | 0   | 1 | 1 | 8.0dB                                                      |    | 1    | 0    | 1      | 0    | 1     | 1     | 4.0dB                         |  |  |  |

| 1         | 0                   | 1     | 1   | 0 | 0 | 7.6dB                                                      |    | 1    | 0    | 1      | 1    | 0     | 0     | 3.8dB                         |  |  |  |

| 1         | 0                   | 1     | 1   | 0 | 1 | 7.2dB                                                      |    | 1    | 0    | 1      | 1    | 0     | 1     | 3.6dB                         |  |  |  |

| 1         | 0                   | 1     | 1   | 1 | 0 | 6.8dB                                                      |    | 1    | 0    | 1      | 1    | 1     | 0     | 3.4dB                         |  |  |  |

| 1         | 0                   | 1     | 1   | 1 | 1 | 6.4dB                                                      |    | 1    | 0    | 1      | 1    | 1     | 1     | 3.2dB                         |  |  |  |

| 1         | 1                   | 0     | 0   | 0 | 0 | 6.0dB                                                      |    | 1    | 1    | 0      | 0    | 0     | 0     | 3.0dB                         |  |  |  |

| 1         | 1                   | 0     | 0   | 0 | 1 | 5.6dB                                                      |    | 1    | 1    | 0      | 0    | 0     | 1     | 2.8dB                         |  |  |  |

| 1         | 1                   | 0     | 0   | 1 | 0 | 5.2dB                                                      | 1  | 1    | 0    | 0      | 1    | 0     | 2.6dB |                               |  |  |  |

| 1         | 1                   | 0     | 0   | 1 | 1 | 4.8dB                                                      |    | 1    | 1    | 0      | 0    | 1     | 1     | 2.4dB                         |  |  |  |

| 1         | 1                   | 0     | 1   | 0 | 0 | 4.4dB                                                      |    | 1    | 1    | 0      | 1    | 0     | 0     | 2.2dB                         |  |  |  |

| 1         | 1                   | 0     | 1   | 0 | 1 | 4.0dB                                                      |    | 1    | 1    | 0      | 1    | 0     | 1     | 2.0dB                         |  |  |  |

| 1         | 1                   | 0     | 1   | 1 | 0 | 3.6dB                                                      |    | 1    | 1    | 0      | 1    | 1     | 0     | 1.8dB                         |  |  |  |

| 1         | 1                   | 0     | 1   | 1 | 1 | 3.2dB                                                      |    | 1    | 1    | 0      | 1    | 1     | 1     | 1.6dB                         |  |  |  |

| 1         | 1                   | 1     | 0   | 0 | 0 | 2.8dB                                                      |    | 1    | 1    | 1      | 0    | 0     | 0     | 1.4dB                         |  |  |  |

| 1         | 1                   | 1     | 0   | 0 | 1 | 2.4dB                                                      |    | 1    | 1    | 1      | 0    | 0     | 1     | 1.2dB                         |  |  |  |

| 1         | 1                   | 1     | 0   | 1 | 0 | 2.0dB                                                      |    | 1    | 1    | 1      | 0    | 1     | 0     | 1.0dB                         |  |  |  |

| 1         | 1                   | 1     | 0   | 1 | 1 | 1.6dB                                                      |    | 1    | 1    | 1      | 0    | 1     | 1     | 0.8dB                         |  |  |  |

| 1         | 1                   | 1     | 1   | 0 | 0 | 1.2dB                                                      |    | 1    | 1    | 1      | 1    | 0     | 0     | 0.6dB                         |  |  |  |

| 1         | 1                   | 1     | 1   | 0 | 1 | 0.8dB                                                      |    | 1    | 1    | 1      | 1    | 0     | 1     | 0.4dB                         |  |  |  |

| 1         | 1                   | 1     | 1   | 1 | 0 | 0.4dB                                                      |    | 1    | 1    | 1      | 1    | 1     | 0     | 0.2dB                         |  |  |  |

| 1         | 1                   | 1     | 1   | 1 | 1 | 0dB                                                        |    | 1    | 1    | 1      | 1    | 1     | 1     | 0dB                           |  |  |  |

| Χ =       | = do                | n't c | are |   | , |                                                            |    |      |      |        |      |       |       |                               |  |  |  |

|           | DD1<br>it 5,        |       |     |   |   | When this bit is "1" the Mo<br>When this bit is "0" the Mo |    |      |      |        |      |       |       | (i.e. powersaved).            |  |  |  |

| MC<br>(Bi | DD2<br>it 5,<br>te) | EN/   | ABL | E |   |                                                            | OD | 2 at | tenu | ator   | and  | the   | SUI   | MMING AMP are enabled.        |  |  |  |

|           | its 7<br>d se       |       |     |   |   | Reserved for future use.                                   | Th | ese  | sho  | uld b  | e se | et to | "0".  |                               |  |  |  |

#### Table 14: AUDIO CONTROL Register (Hex address \$8A)

## 4.4.13 SELCALL TX Register (Hex address \$8D)

This is a 16-bit register. Byte (1) is sent first.

When the SELCALL transmitter is enabled, bits 0 to 12 control the frequency of the transmitted SELCALL tones according to the formula below:

$$A = \frac{f_{XTAL} (Hz)}{4 x f_{TONE} (Hz)}$$

where A is the binary number programmed into the 13 bits.

When Bit 7 (in the first 8 bits) is set to "1" the tone output is set at  $V_{BIAS}$  or NOTONE without regard to the number "A" programmed. When Bit 7 is "0" the programmed tone is set on the output. Programming bits 0 through 12 to "0" places the Tx into powersave and the output goes to  $V_{BIAS}$ . Powersave is also achieved by disabling the SELCALL Tx.

## 4.5 8-bit Read Only Registers

| HEX<br>ADDRESS/<br>COMMAND | REGISTER<br>NAME | BIT 7<br>(D7) | BIT 6<br>(D6) | BIT 5<br>(D5) | BIT 4<br>(D4) | BIT 3<br>(D3) | BIT 2<br>(D2) | BIT 1<br>(D1) | BIT 0<br>(D0) |

|----------------------------|------------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|

|                            | SELCALL &        | DCS           | CTCSS         |               |               |               | RX TC         | DNE           |               |

| \$81                       | SUB-AUDIO        | DECODE/       | FAST          | 0             | TONE          | MSB           |               |               | LSB           |

|                            | STATUS           | NO DECODE     | TONE          |               | DECODE        | BIT 3         | BIT 2         | BIT 1         | BIT 0         |

|                            |                  |               | GP TIMER      | COMP          | COMP          | TONE          | CTCSS FAST    |               | DCS           |

| \$8F                       | IRQ FLAG         | 0             | IRQ           | 0 to 1        | 1 to 0        | IRQ           | IRQ           | 0             | IRQ           |

|                            |                  |               | FLAG          | IRQ FLAG      | IRQ FLAG      | FLAG          | FLAG          |               | FLAG          |

Table 15: 8-bit Read Only Registers

## 4.6 Read Only Register Description

#### 4.6.1 SELCALL and SUB-AUDIO STATUS Register (Hex address \$81)

This register is used to indicate the status of the device as described below:

| DCS DECODE/<br>NO DECODE<br>(Bit 7) | When the DCS decoder is enabled this bit is continuously updated with the result. A "1" indicates a successful decode (with 3 or less errors). A "0" indicates a failure to decode.                                                                     |

|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CTCSS FAST TONE<br>(Bit 6)          | When Bit 5 in the SIGNALING CONTROL Register and Bit 3 in the SIGNALING SET-UP Register are set to enable FAST CTCSS DETECT mode, this bit will be set to "1" if a periodic tone is detected. If no periodic tone is detected this bit will be "0".     |

|                                     | When bits 5 and 3 are set to enable FAST CTCSS PREDICTIVE mode, this bit will be set to "1" if a periodic tone that matches the frequency programmed in the CTCSS TX/FAST RX FREQUENCY Register is detected. If no match is found this bit will be "0". |

|                                     | When Bit 5 in the SIGNALING CONTROL Register is set to "0" this bit will be "0".                                                                                                                                                                        |

| (Bit 5)                             | Reserved for future use. This will be set to "0" but should be ignored by the user's software.                                                                                                                                                          |

| TONE DECODE<br>(Bit 4)          | This bit indicates the status of the tone decoder. A "1" indicates a tone has been detected (TONE DECODE) and a "0" indicates the loss of the tone (NOTONE).<br>TONE DECODE means that a tone has been decoded and its characteristics are defined by the bandwidth (See SIGNALING SET-UP Register bits 7, 6, 5 and 4) and the RX TONE number (See SELCALL and SUB-AUDIO STATUS Register bits 3, 2, 1 and 0).<br>When Bit 6 in the SIGNALING CONTROL Register is set to "0" the TONE DECODE bit 4 will be set to "0".<br>Identification of a valid tone which is not in the pre-programmed list of up to 15 tones will cause the decoder to move to the TONE DECODE state with the RX TONE address of "1111" in bits 3, 2, 1 and 0; indicating a valid, but unrecognized, tone. Loss of tone, will cause the NOTONE timer to be started. If loss of tone continues for the duration of pre-programmed tones will start again. |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RX TONE<br>(Bits 3, 2, 1 and 0) | These four bits hold a Hex number from \$0 to \$F. Numbers \$0 to \$E represent the address of the tone decoded according to the tones programmed in the RX TONE PROGRAM Register, \$84. The Hex number \$F indicates the presence of any tone that is not described by DECODER BANDWIDTH (Bits 7, 6, 5 and 4, SIGNALING SET-UP Register, \$82) and FREQUENCY (Bits 11 - 0, RX TONE PROGRAM Register, \$84).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

#### Table 16: SELCALL and SUB-AUDIO STATUS Register (Hex address \$81)

### 4.6.2 IRQ FLAG Register (Hex address \$8F)

This register is used to indicate when the device requires attention as below:

| (Bits 7 and 1)                     | Reserved for future use. These will be set to "0" but should be ignored by user's software.                                                                                                                                                                                                  |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPT IRQ FLAG<br>(Bit 6)            | When the general purpose timer has reached zero in its internal register, this bit will be set to "1" to indicate the timeout has expired. This bit is cleared to "0" by a read of the IRQ FLAG Register (Hex address \$8F).                                                                 |

| COMP 0 to 1<br>IRQ FLAG<br>(Bit 5) | When the comparator output goes from "0" to "1" (i.e. when the input voltage is above the DAC output voltage) this bit will be set to "1" and an interrupt generated (if bit 5 of the IRQ MASK Register \$8E is set to "1"). This bit is set to "0" when the IRQ FLAG Register \$8F is read. |

| COMP 1 to 0<br>IRQ FLAG<br>(Bit 4) | When the comparator output goes from "1" to "0" this bit will be set to "1" and an interrupt generated (if bit 4 of the IRQ MASK Register \$8E is set to "1"). This bit is set to "0" when the IRQ FLAG Register \$8F is read.                                                               |

| TONE IRQ FLAG<br>(Bit 3)           | When RX TONE DECODE (Bit 4, SELCALL and SUB-AUDIO STATUS Register, \$81) changes state this bit will be set to "1". This bit is cleared to "0" by a read of the IRQ FLAG Register (Hex address \$8F).                                                                                        |

| CTCSS FAST IRQ<br>FLAG<br>(Bit 2)  | When CTCSS FAST TONE (Bit 6, SELCALL and SUB-AUDIO STATUS Register, \$81) changes state this bit will be set to "1". This bit is cleared to "0" by a read of the IRQ FLAG Register (Hex address \$8F).                                                                                       |

| DCS IRQ FLAG<br>(Bit 0)            | When DCS DECODE/NO DECODE (Bit 7 SELCALL and SUB-AUDIO STATUS Register, \$81) changes state this bit will be set to "1". This bit is cleared to "0" by a read of the IRQ FLAG Register (Hex address \$8F).                                                                                   |

Table 17: IRQ FLAG Register (Hex address \$8F)

CTCSS/DCS/SelCall Processor

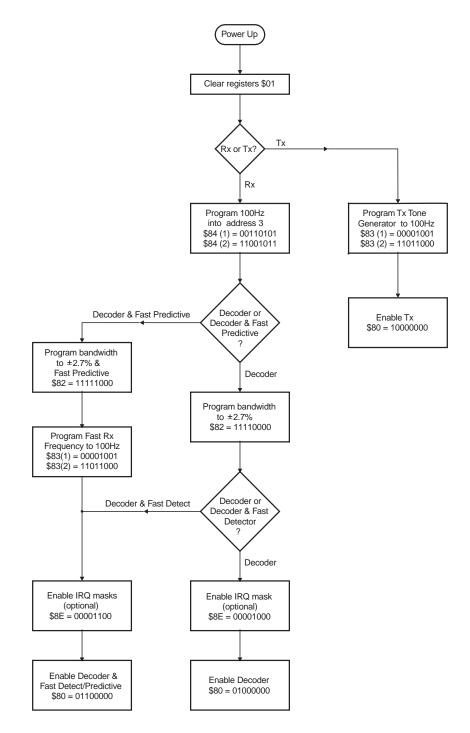

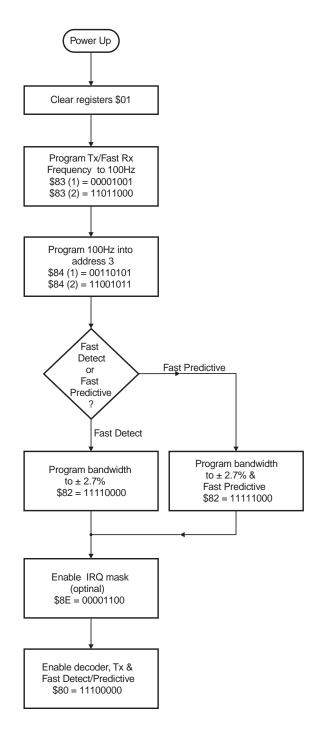

The flow chart shows the following modes of operation for the example below: )

- 1. Decode