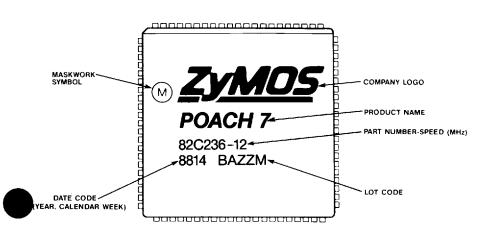

DATA SHEET

APPIAN TECHNOLOGY INC

## POACH/ATF™ POACH 7/POACH 8

丁-52-33-05

#### **FEATURES**

- fully IBM PC AT-compatible

- two chip set replaces the major logic functions of the IBM PC AT motherboard including the functions of all the microprocessor peripherals:

| — 8259A       | Programmable Interrupt |

|---------------|------------------------|

|               | Controller (Master)    |

| 8259A         | Programmable Interrupt |

|               | Controller (Slave)     |

| <b>— 8254</b> | Programmable Interval  |

|               | Timer                  |

|               | OL 1 O                 |

- 8284A Clock Generator (Timer) - 8284A Clock Generator (Coprocessor) Clock Generator & Ready -82284Interface

- 82288 **Bus Controller — 8237** DMA Controller (Byte) **— 8237** DMA Controller (Word) **—** 6818 Real Time Clock Memory Mapper

- includes:

- 74LS612

- 10-bit Refresh Generation Logic

- Refresh/DMA Arbitration

- Address/Data Bus Control

- 16- to 8-bit Conversion Logic

#### DESCRIPTION

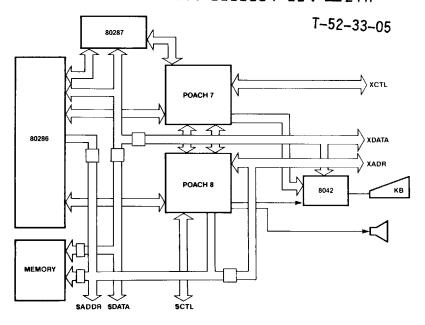

The ZyMOS POACH/ATF (PC On A CHip) chip set is a high performance two-chip implementation of LSI/MSI/SSI logic controlling the IBM Personal Computer AT. POACH/ATF operates at 16 MHz using cost-effective DRAMs. The devices provide a low-power, highly integrated PC AT design solution that may also be applied to any 80286-based system.

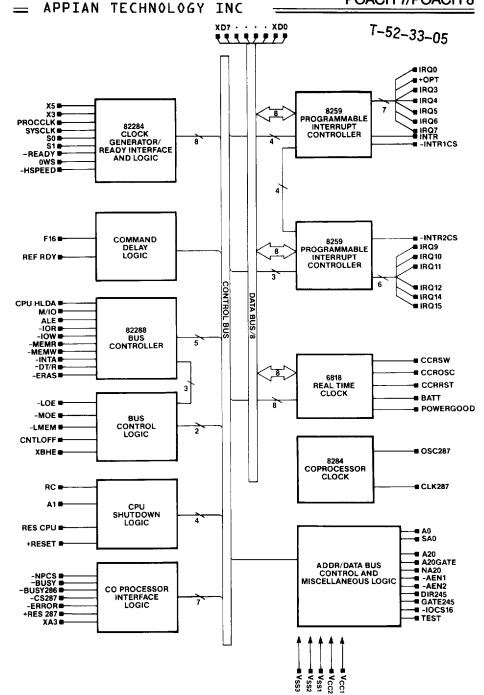

POACH 7 performs the functions of the 82284 Clock Generator and READY Interface, 82288 Bus Controller for 80286 processors, 6818 Real Time Clock/RAM, and the Master/Slave implementation of the dual 8259A Programmable Interrupt Controllers as well as Command Delay. Shut Down, Address/Data Bus Control and READY Generation logic and the

- 16-MHz operation

- high integration 80286 design solution

- numerical processor control with independent 8284A for asynchronous coprocessor clock

- single +5V power supply

- low-power CHMOS-3

- microprocessor peripheral functions available as standard cells in the ZyMOS cell library for unique design integration

- generation of an early RAS signal

- support of multispeed systems through dynamic clock switching

- provides high system speed with provision for lower-speed expansion bus

- additional I/O command delay

- special PCB test mode

- DRAM on local data bus

- Schmitt inputs on POWERGOOD. REFRESH, IOCHRDY

8284A Coprocessor Clock Generator. POACH 8 includes the 8254 Programmable Interval Timer, 8284A Clock Generator, LS612 Memory Mapper and the dual 8237 DMA Controller functions as well as Refresh Generation and Refresh/ **DMA Arbitration Logic.**

POACH/ATF peripherals are fully compatible with those used in standard PC AT designs; the chip set is fully IBM PC AT-compatible. High-speed operation is possible by selecting the optimum RAM/ buffer combination. Occupying only two 84-pin plastic leaded chip carriers on the AT motherboard, POACH/ATF implementation results in a dramatic reduction in board size.

17E D = 9997499 0001049 751 = ZYM

T-52-33-05

## **FUNCTIONAL DESCRIPTION**

POACH/ATF (POACH 7 and 8) has been developed to maximize the full performance capabilities of the basic PC AT system architecture. The high performance POACH 7 and 8 ICs are similar to POACH 1 and 2, and include features which support the development of systems operating above 12 MHz. The system enhancements available from POACH/ATF include:

- 1. Memory Path Timing Enhancements

- 2. Dynamic Processor Speed Switching

- 3. Additional Command Delays

- 4. Independent 80287 Clocking

- 5. POWERGOOD Signal Conditioning

- 6. Board Test Mode

## **Memory Path Timing Enhancements**

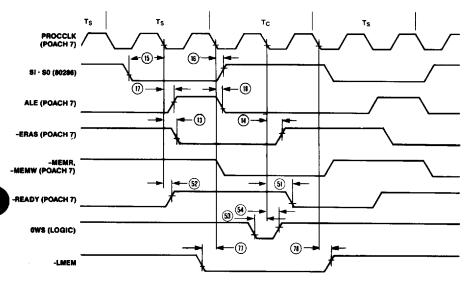

To allow the use of slower, lower-cost memories in a high performance PC AT system, POACH 7 supports local data bus memory connections and provides an -ERAS control signal. The -ERAS (Early RAS) signal supports higher speed memory designs than +RAS of the standard PC AT.

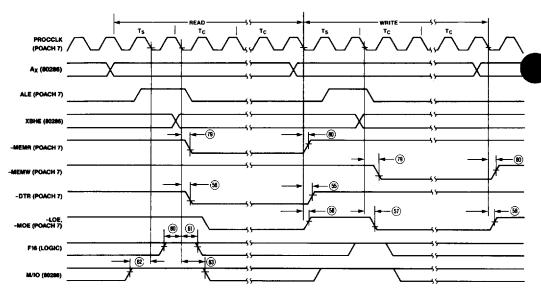

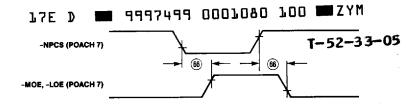

The new -LMEM (local memory) input signal provided on POACH 7 supports direct connection of system board memory to the 80286 processor's local data bus. This feature also allows slower memories to be used by eliminating transceiver delays in the critical memory timing path. The -LMEM signal controls the outputs -DTR, -MOE, -LOE, and disables -ERAS to reduce system power consumption. When -LMEM is high, the signals -DTR, -MOE, and -LOE operate identically to their POACH 1 equivalents DT/R, MSDEN and LSDEN. When -LMEM is driven low, data transfer is directed to the local data bus via the -DTR, -MOE and -LOE controls during DMA and bus master operations.

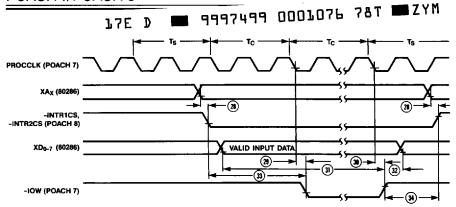

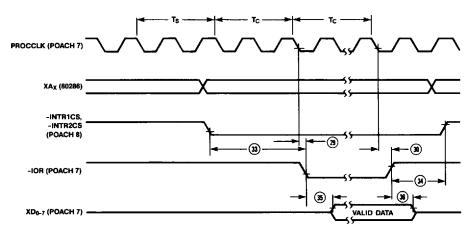

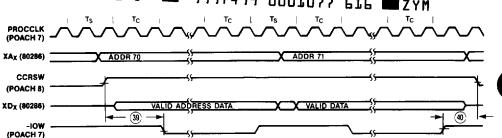

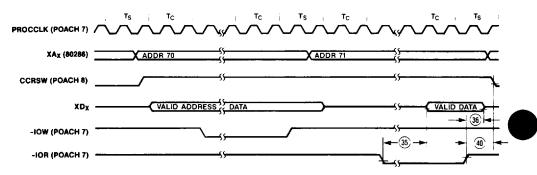

## **Additional Command Delays**

Another important feature available from

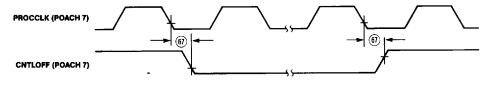

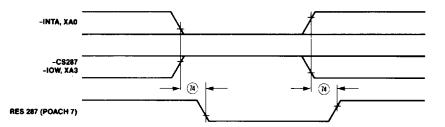

POACH/ATF is the extra command delay added to the -IOR and -IOW signals. In a high performance system with a short clock cycle, there may not be enough command recovery time, or precharge, time, to meet the peripheral IC or expansion card requirements even though the actual command time is sufficient. The standard PC AT design provides a command pulse width of 41/2 PROCCLK cycles and a recovery time of 11/2 cycles. POACH/ATF extends the command delay by an extra half cycle to increase the recovery time by 33%, while reducing the command pulse only 11%. The improved balance between command pulse and recovery time is important in a high speed system.

## **Dynamic Processor Speed Switching**

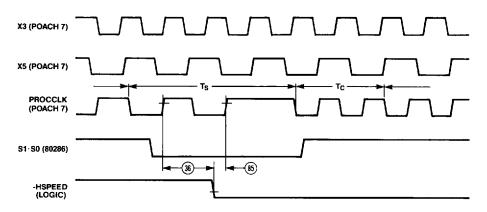

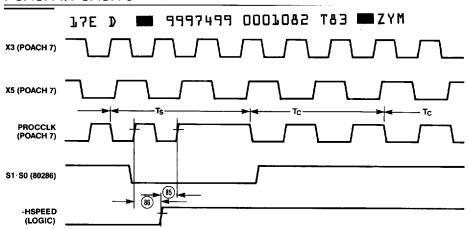

POACH/ATF provides the ability to switch the system speed dynamically during normal operation via the -HSPEED input. The -HSPEED (high speed) input selects either the X3 or X5 input frequency. In a typical system, the X3 input clock is twice the frequency of the system speed: i.e., 32 MHz for a 16-MHz system. The X5 input clock is typically used to set the expansion bus operating speed and is also twice the required speed; i.e., 16 MHz for a 8-MHz expansion bus. When -HSPEED is high, the X5 input is selected. The frequency of PROCCLK will be equal to the frequency of either X3 or X5. depending on which one is selected. Note that for reliable operation both the X3 and X5 inputs must have a clock input source even if it is the same signal, and even if speed switching is not used.

Dynamic speed switching provides an important capability to high performance systems because some expansion cards cannot operate at speeds beyond the 8-MHz IBM PC AT standard. By detecting an I/O or expansion bus operation, the entire system speed can be slowed to the standard IBM PC AT speed, thereby allowing time for the peripheral or expansion card to respond. As a result, a

## POACH 7/POACH 8

## APPIAN TECHNOLOGY INC

T-52-33-05

universal solution for interfacing with the wide variety of expansion cards is easily implemented with POACH/ATF. Using this feature, keyboard control of system speed can also be easily implemented where low-speed operation for real-time applications, such as games, is needed.

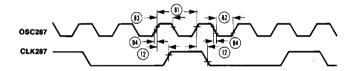

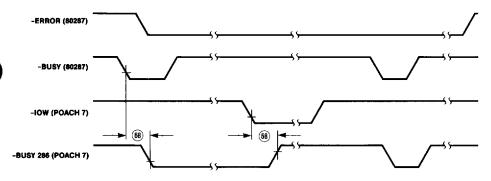

### Independent 80287 Clocking

An 80287 coprocessor with a clock rate above 10 MHz is not commercially available, and as a result, the standard coprocessor clock connections of the PC AT will not function for systems faster than 10 MHz. POACH/ATF provides an 8284 clock generator for dedicated asynchronous operation of the coprocessor. This feature of POACH/ATF allows a coprocessor of any specific performance requirement to be included in the system. Maximizing performance of the coprocessor becomes independent of the system operating speed.

The output of an oscillator is connected to the OSC287 input of POACH/ATF. The frequency of this oscillator should be three times the 80287 coprocessor speed; a 30-MHz oscillator for a 10-MHz coprocessor. The 8284 of POACH/ATF produces a clock signal of the recommended 33% duty cycle on the CLK287 output. Note that the clock mode input (CKM) of the 80287 coprocessor must be connected to a high logic level for this POACH/ATF feature to work properly.

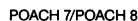

## **POWERGOOD Signal Conditioning**

POACH/ATF uses an active-high POWER-GOOD input signal. As a result, design

flexibility for implementing a very lowpower, low-voltage, 32-KHz oscillator circuit is improved since an external batterypowered inverter is not needed.

The input buffer of the POACH/ATF POWERGOOD signal is implemented as a Schmitt trigger. This feature provides additional operating margin, which is especially important for applications that do not have high-quality PC AT-type power supplies.

## **System Board Testing**

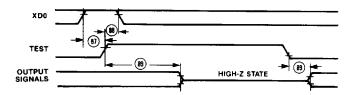

To facilitate "bed-of-nails" board testing, a test mode has been added to POACH 7 that enables the switching of all outputs to a high-impedance state. As long as the maximum device limits are not exceeded, this allows a test system to overdrive the POACH 7 outputs without the concern of device degradation resulting from high currents and conflicting signal levels.

Data on the XD0 pin is sampled on the rising edge of the TEST input. If XD0 is sampled as a high logic level, this test mode is enabled. The test mode remains enabled until the TEST input returns to a low logic level. Note that a RESET following TEST mode exit may be needed before normal POACH 7 operation can begin since random test vectors on POACH 7 inputs may latch an erroneous internal condition.

The TEST input of POACH 7 must be connected to an external  $10K\Omega$  pulldown resistor if this feature is to be used. If this test mode is not to be used, the TEST input must be tied to ground.

T-52-33-05

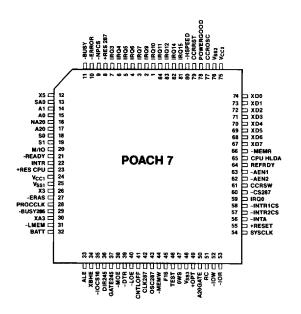

## Pin Diagram POACH 7

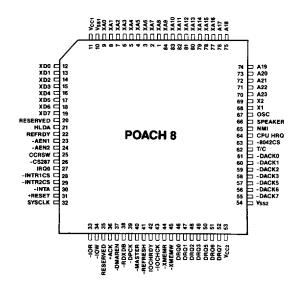

Pin Diagram POACH 8

POACH 7/POACH 8

POACH 7—Block Diagram

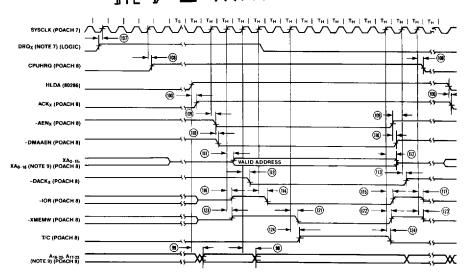

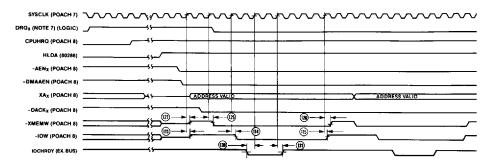

T-52-33-05 9997499 0001053 17E D 185 | ZYM -IOR ---IOW ---XMEMW ---INTA --.a DRQ0 ■ DRQ1 B DRQ2 READ/WRITE 8237 DRQ3 LOGIC AND -INTRICS DMA CONTROLLER DACKO -CS287 ---RDXD8 ---8042CS --CCRSW --SELECT DECODE DACK2 LATCHES -MASTER ■--DMAAEN ■--TC ■--8 MISCELLANEOUS +ACK =--SPEAKER =--+RESET =-LOGIC ■ DRQ5 8 ■ DRQ6 TEST . ■ DRQ7 8237 DMA CONTROLLER # DACK5 11 **■ DACK6** B DACK7 8254 COUNTER/ IRQ0 ■ TIMER LATCHES CONTROL BUS ADDRESS DATA BUS / 8 SYSCLK . DRAM OSC -CLOCK GENERATION REFRESH COUNTER /LATCH X1 ₽ & LOGIC X2 ₩ - CPU HRQ - REFRESH - P2 - REFRDY A17 BA18 BA19 BA REFRESH 74612 & DMA ARBITRATION MEMORY A20 =-MAPPER A21 B A22 B A23 B ■ -XMEMR ■ IOCHRDY ■ HLDA & TIMING • NMI PARITY CHECK -IOCHCK LOGIC - DPCK

POACH 8—Block Diagram

17E D 9997499 0001054 019 ZYM

Block Diagram of POACH 7 and POACH 8 for PC AT

## POACH 7/POACH 8

## APPIAN TECHNOLOGY INC

## **POACH 7 Pin Description**

| Pin<br>No. | Symbol         | Туре | Description                                                                                                                                                                                                                                 |  |  |  |  |

|------------|----------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 15         | A0             | ı    | ADDRESS 0 input from the CPU. It is used to generate SA0.                                                                                                                                                                                   |  |  |  |  |

| 14         | A1             | ı    | ADDRESS 1 input from the CPU. It is used in conjunction with M/IO, S0 and S1 to detect a CPU shutdown condition.                                                                                                                            |  |  |  |  |

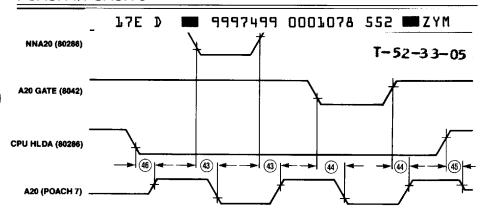

| 17         | A20            | 0    | ADDRESS 20 is the A20 (NA20) line from the CPU after conditioning by the A20GATE signal.                                                                                                                                                    |  |  |  |  |

| 50         | A20GATE        | 1    | A20GATE from the keyboard controller is used to force A20 low. When A20GATE is low, A20 on the CPU address bus is forced low. When A20GATE is high, A20 follows the CPU address 20. Tie directly to the P21 pin of the keyboard controller. |  |  |  |  |

| 62<br>63   | -AEN2<br>-AEN1 | I    | ADDRESS ENABLE 1 & 2 from DMAs 1 & 2, respectively. Each signal is the result of the DMAAEN pin NAND'd with -MASTER. Tie directly from the -AEN and -AEN2 pins of POACH 8.                                                                  |  |  |  |  |

| 33         | ALE            | 0    | ADDRESS LATCH ENABLE is an active high signal that controls the address latches used to hold addresses during bus cycles. ALE is held inactive for halt bus cycles.                                                                         |  |  |  |  |

| 32         | BATT           | ı    | BATTERY power to the clock calendar and RAM.                                                                                                                                                                                                |  |  |  |  |

| 29         | -BUSY286       | 0    | -BUSY286 is an active low output indicating the oper<br>ating condition of the 80287 coprocessor to the pro<br>cessor. It is normally tied to the processor BUSY pin.                                                                       |  |  |  |  |

| 11         | -BUSY          | ı    | -BUSY is an active low input from the 80287 to indicate that it is currently executing a command. It is used to generate the -BUSY286 output signal.                                                                                        |  |  |  |  |

| 77         | CCROSC         | ı    | CLOCK CALENDAR RAM OSCILLATOR.                                                                                                                                                                                                              |  |  |  |  |

| 79         | CCRRST         | 1    | CLOCK CALENDAR RAM RESET signal for the Real Time Clock. This is an active low input.                                                                                                                                                       |  |  |  |  |

| 61         | CCRSW          | I    | CLOCK CALENDAR RAM Select signal for the real-<br>time clock. A high enables READ/WRITE operation to<br>the real-time clock. Tie directly to the CCRSW pin of<br>POACH 8.                                                                   |  |  |  |  |

| 42         | CLK287         | 0    | CLOCK 80287 is a 33% duty cycle clock output with frequency of OSC287 divided by 3, used as the 80287 fundamental clock frequency.                                                                                                          |  |  |  |  |

| 41         | CNTLOFF        | 0    | CONTROL OFF is used to enable the low byte data bus latch during byte accesses. This signal is active high.                                                                                                                                 |  |  |  |  |

T-52-33-05

## POACH 7 Pin Description (Continued)

| Pin<br>No. | Symbol   | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|------------|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

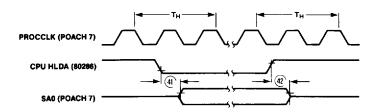

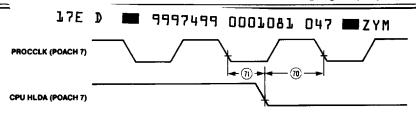

| 65         | CPU HLDA | 1    | CPU HOLD ACKNOWLEDGE is an active high inpution the processor. An active condition indicates that the CPU has relinquished the bus to another bus master in the system.                                                                                                                                                                                                                                             |  |  |  |  |  |  |

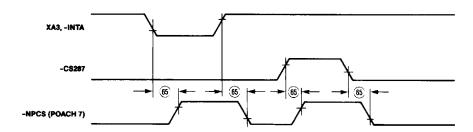

| 60         | -CS287   | I    | CHIP SELECT 287 is used to derive the -NPCS sign<br>Tie directly to the -CS287 pin of POACH 8.                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| 36         | DIR245   | 0    | DIRECTION-245 controls the high-to-low byte and low-to-high byte conversion during data transfers to and from 8-bit peripherals.                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| 39         | -DTR     | 0    | DATA TRANSMIT/RECEIVE establishes the data direction to and from the local data bus. When high, thi output signals a CPU write bus cycle to the memor DATA bus or a DMA read bus cycle from the local DATA bus. A low indicates a CPU read bus cycle from the memory DATA bus or the DMA write bus cycle to the local DATA bus. This signal is conditioned by LRAM. This signal is high when no bus cycle is active |  |  |  |  |  |  |

| 27         | -ERAS    | 0    | EARLY ROW ADDRESS STROBE is the RAS signal for DRAM. This is an active low output signal conditioned by -LRAM.                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| 10         | -ERROR   | 1    | ERROR is an active low input from the numeric processor indicating that an unmasked error condition exists. Tie directly to the -ERROR pin of the 80287.                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 45         | F16      | I    | F16 is an active high input indicating a word memor access. It is used to inhibit command delays for memory accesses.                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| 37         | GATE245  | 0    | GATE245 is an active low output. When active it enables the bus transceiver that performs the high-to-low byte conversion with the DIR245 signal. Conversion does not take place if A0 = 0 which indicates a word transfer.                                                                                                                                                                                         |  |  |  |  |  |  |

| 80         | -HSPEED  | 1    | -HSPEED is an active low input. When -HSPEED is low, PROCCLK has the same frequency as the X3 input clock. When -HSPEED is high, PROCCLK is the frequency of the X5 input clock.                                                                                                                                                                                                                                    |  |  |  |  |  |  |

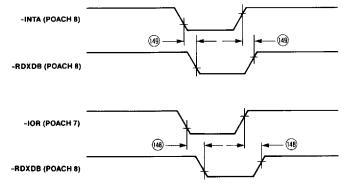

| 56         | -INTA    | 0    | INTERRUPT ACKNOWLEDGE instructs an interrupting device that its interrupt request is being acknowledged. This output signal is active lowINTA itri-stated when CPU HLDA is high and CNTLOFF illow. Tie directly to the -INTA pin of POACH 8.                                                                                                                                                                        |  |  |  |  |  |  |

## 17E D = 9997499 0001057 828 = ZYM

# POACH 7/POACH 8 APPIAN TECHNOLOGY INC

## POACH 7 Pin Description (Continued)

| Pin<br>No.                   | Symbol                                                | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|------------------------------|-------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 22                           | INTR                                                  | 0    | INTERRUPT REQUEST is connected directly to the CPU's interrupt pin. INTR is active high, and is generated when a valid interrupt request has been asserted.                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| 58                           | -INTR1CS                                              | 1    | INTERRUPT CONTROLLER 1 (MASTER) CHIP SELECT is an active low input that is used to select the interrupt controller as an I/O device. This allows communication between the master interrupt controller and the CPU via the 'X' Data Bus. Tie directly to the -INTR1CS pin of POACH 8.                                                                                                            |  |  |  |  |  |  |

| 57                           | -INTR2CS                                              | 1    | INTERRUPT CONTROLLER 2 (SLAVE) CHIP SELECT is an active low input that is used to select the interrupt controller as an I/O device. This allows communication between the slave interrupt controller and the CPU via the 'X' data bus. Tie directly to the -INTR2CS pin of POACH 8.                                                                                                              |  |  |  |  |  |  |

| 35                           | -IOCS16                                               | ı    | I/O 16-BIT CHIP SELECT signals the system that the current data transfer is a 16-bit, one wait-state, I/O cycle. It is derived from an address decode and is an active low signal.                                                                                                                                                                                                               |  |  |  |  |  |  |

| 53                           | -IOR                                                  | 0    | I/O READ instructs a selected I/O device to drive its data onto the data bus. The -IOR signal is active low. It is tri-stated when CPU HLDA is high and CNTLOFF is low.                                                                                                                                                                                                                          |  |  |  |  |  |  |

| 52                           | -IOW                                                  | 0    | I/O WRITE instructs a selected I/O device to read the data on the data bus. The -IOW signal is active low. It is tri-stated when CPU HLDA is high and CNTLOFF is low.                                                                                                                                                                                                                            |  |  |  |  |  |  |

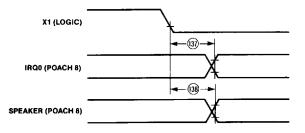

| 59                           | IRQ0                                                  | l    | INTERRUPT REQUEST 0 (system timer) receives interrupt requests from channel 0 of the timer/counter. Tie directly to the IRQ0 pin of POACH 8.                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

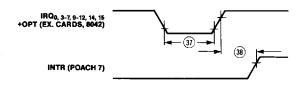

| 3–7<br>1–2<br>83–84<br>81–82 | IRQ7-IRQ3<br>IRQ10-IRQ9<br>IRQ12-IRQ11<br>IRQ15-IRQ14 | <br> | INTERRUPT REQUESTS 3-7, 9-12, and 14-15 are used to signal the CPU that an I/O device needs attention. The interrupt requests are prioritized with IRQ9-IRQ12; IRQ14-IRQ15 having the highest priority (IRQ9 highest) and IRQ3-IRQ7 having the lowest priority (IRQ7 lowest). IRQn signals are active high. The requesting signal is held high until the CPU acknowledges the interrupt request. |  |  |  |  |  |  |

| 40                           | -LOE                                                  | 0    | LEAST SIGNIFICANT DATA ENABLE is an active low output. When active, it enables the transceiver/receiver connected to the least significant byte of the local data bus. This signal is conditioned by -LRAM.                                                                                                                                                                                      |  |  |  |  |  |  |

## POACH 7 Pin Description (Continued)

| Pin<br>No. | Symbol         | Туре | Description                                                                                                                                                                                                               |  |  |  |  |  |

|------------|----------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 31         | -LMEM          | ı    | This active low input signal indicates a memory transaction with the local DATA bus.                                                                                                                                      |  |  |  |  |  |

| 66         | -MEMR          | I/O  | MEMORY READ COMMAND instructs a memory device to drive data onto the data bus. This signal active low. –MEMR is active on all memory read cycle. It is tri-stated when CPU HLDA is high and CNTLOF output is low.         |  |  |  |  |  |

| 44         | -MEMW          | I/O  | MEMORY WRITE COMMAND instructs a memory device to read the data on the data bus. This signal is active low. –MEMW is active on all memory write cycles. It is tri-stated when CPU HLDA is high and CNTLOFF output is low. |  |  |  |  |  |

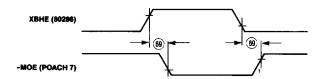

| 38         | -MOE           | 0    | MOST SIGNIFICANT DATA ENABLE is an active lo output. When active, it enables the transceiver connected to the most significant byte of the local data but This signal is conditioned by -LRAM.                            |  |  |  |  |  |

| 20         | M/IO           | ı    | MEMORY-INPUT OUTPUT is the M/IO signal from the CPU. When high, it indicates a memory access. When low, it indicates an I/O access. It is used to generate the memory and I/O signals for the system.                     |  |  |  |  |  |

| 16         | NA20           | ı    | NA20 is the CPU address 20. POACH 7 conditions thi signal with A20GATE to produce A20. This pin is tie directly to the CPU A20 output.                                                                                    |  |  |  |  |  |

| 9          | -NPCS          | 0    | NUMERICAL PROCESSOR CHIP SELECT is an active low output used to select the 80287 numerical processor. It is tied directly to the NPS1 pin of the 80287.                                                                   |  |  |  |  |  |

| 49         | +OPT           | 1    | KEYBOARD OUTPUT BUFFER FULL is an active high signal from the keyboard controller P24 pin. The signal is an interrupt request (IRQ1) signaling a full keyboard buffer.                                                    |  |  |  |  |  |

| 47         | 0WS            | 1    | ZERO WAIT STATE option. When pulled active (low), the current processor cycle can be terminated.                                                                                                                          |  |  |  |  |  |

| 43         | OSC287         | I    | OSCILLATOR 80287 is the clock input for the co-<br>processor clock generator.                                                                                                                                             |  |  |  |  |  |

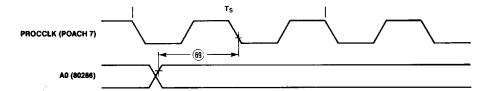

| 28         | PROCCLK        | 0    | PROCESSOR CLOCK provides the clock signal for the CPU. Tie directly to the CLK pins of the 80286.                                                                                                                         |  |  |  |  |  |

| 78         | POWER-<br>GOOD | 1    | POWERGOOD is an active high input that indicate that system power is sufficient to maintain the integrit of the system. A low-to-high transition will initiate system reset.                                              |  |  |  |  |  |

## 17E D 9997499 0001059 6TO 2YM

## POACH 7/POACH 8

# APPIAN TECHNOLOGY INC

## POACH 7 Pin Description (Continued)

| Pin<br>No.     | Symbol               | Туре | Description                                                                                                                                                                                                                                                                                                    |  |  |  |

|----------------|----------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

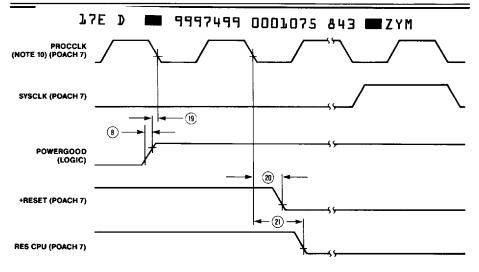

| 51             | RC                   | 1    | RESET CPU from the keyboard controller P21 pin.                                                                                                                                                                                                                                                                |  |  |  |

| 21             | -READY               | 0    | READY is an active low output that signals when the current bus cycle is to be completed. S0, S1, +POWE GOOD, and 0WS control the -READY output.                                                                                                                                                               |  |  |  |

| 64             | REFRDY               | ı    | REFRESH/IO-CHANNEL-READY is generated b<br>POACH 8. It is used to <u>preset</u> the READY Interfact<br>Asynchronous READY (ARDY).                                                                                                                                                                              |  |  |  |

| 8              | +RES 287             | 0    | RESET 80287 is the reset signal for the 80287 numerical processor.                                                                                                                                                                                                                                             |  |  |  |

| 23             | RES CPU              | 0    | RESET CPU is the reset signal for the CPU. Active high RESCPU is generated when either +POWERGOOD or RC become active, or when the CPU generates a HAL status by forcing M/IO high, S0, S1 and A1 low. If this signal is initiated by RC, or by M/IO, S0, S1 and A1, will remain active for 16 PROCCLK cycles. |  |  |  |

| 55             | +RESET               | 0    | RESET (SYSTEM) is an active high output derived from the POWER GOOD input. +RESET is used to force the system into an initial state. When +RESET is active, -READY will also be active (low).                                                                                                                  |  |  |  |

| 18, 19         | S0, S1               | I    | STATUS inputs from the CPU. The status signals are used by the bus controller to determine the state of the CPU.                                                                                                                                                                                               |  |  |  |

| 13             | SA0                  | I/O  | ADDRESS 0 of the CPU bus. SA0 outputs A0 from the CPU during local CPU cycles. The expansion bus can also force this pin when another master on the expansion bus has control. During an interrupt acknowledge this signal will be forced low. This signal becomes an input during non-CPU bus cycles.         |  |  |  |

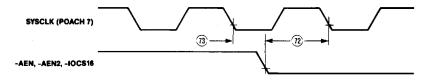

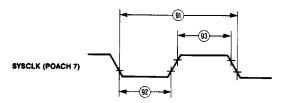

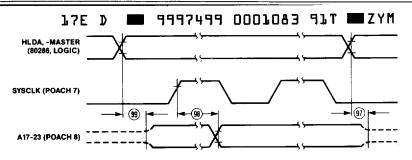

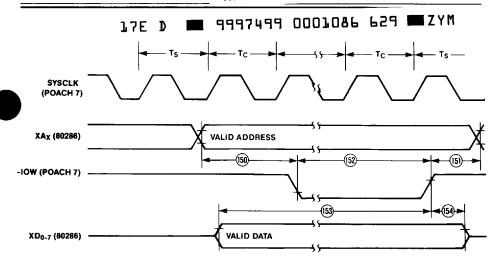

| 54             | SYSCLK               | 0    | SYSTEM CLOCK is the result of PROCCLK divided by two, thus synchronized to the processor's T-states. It may be used to clock peripheral devices that must be synchronized to the CPU.                                                                                                                          |  |  |  |

| 46             | TEST                 | 1    | TEST is an input which enables test modes. It should be connected to VSS through $10 \mathrm{K}\Omega$ resistor.                                                                                                                                                                                               |  |  |  |

| 24<br>75       | Vcc1<br>Vcc2         |      | POWER: +5-Volt supply.                                                                                                                                                                                                                                                                                         |  |  |  |

| 25<br>76<br>48 | Vss1<br>Vss2<br>Vss3 |      | GROUND.                                                                                                                                                                                                                                                                                                        |  |  |  |

T-52-33-05

## POACH 7 Pin Description (Continued)

| Pin<br>No. | Symbol          | Туре | Description                                                                                                                                                                                                         |  |  |  |  |

|------------|-----------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 26         | Х3              | I    | X3 is the clock input used to generate PROCCLK and SYSCLK. It is selected when the -HSPEED input is low.                                                                                                            |  |  |  |  |

| 12         | X5              | 1    | X5 is the clock input used to generate PROCCLK and SYSCLK. It is selected when the -HSPEED input is high.                                                                                                           |  |  |  |  |

| 30         | XA3             | I    | ADDRESS 3 is used for generating the chip select and reset signals for the 80287.                                                                                                                                   |  |  |  |  |

| 34         | XBHE            | 1/0  | BUS HIGH ENABLE is an active low signal used by POACH 7 to generate the -MOE signal.                                                                                                                                |  |  |  |  |

| 67–74      | XD7-XD0         | 1/0  | Data Bus 0-7 for the peripheral bus. The direction of the bus is determined by the RDXDB signal from POACH (It is used by the 8259A to decipher command words the CPU issues.                                       |  |  |  |  |

| POACI      | H 8 Pin Descrip | tion |                                                                                                                                                                                                                     |  |  |  |  |

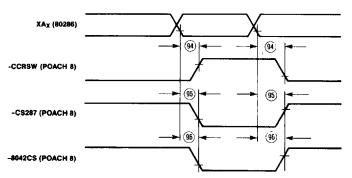

| 63         | -8042CS         | 0    | 8042 CHIP SELECT is an active low, chip select signal for the keyboard controller.                                                                                                                                  |  |  |  |  |

| 70-76      | A23-A17         | 0    | A23-A17 are the address bits 17-23 of the CPU address bus. They are outputs directly from the memo mapper pins MO1-MO7 and supply page information during DMA transfers.                                            |  |  |  |  |

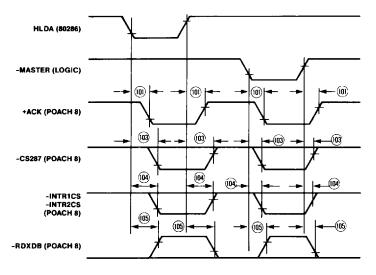

| 36         | +ACK            | 0    | ACKNOWLEDGE is an active low output. When acti it enables the bus transceiver between the system a peripheral (XBUS) bus. +ACK is used in conjuncti with -RDXDB, which controls the direction of the b transceiver. |  |  |  |  |

| 23<br>24   | -AEN1<br>-AEN2  | 0    | ADDRESS ENABLE FROM DMAs 1 & 2, respectively The signal is the result of the DMA's AEN signa NAND'd with -MASTER. Tie directly to the -AEN1 and -AEN2 pins of POACH 7.                                              |  |  |  |  |

| 25         | CCRSW           | 0    | CLOCK CALENDAR RAM Select signal for the real-<br>time clock. A high enables READ/WRITE operations<br>to the real-time clock. Tie directly to the CCRSW pir<br>of POACH 7.                                          |  |  |  |  |

| 64         | CPU HRQ         | 0    | CPU HOLD REQUEST is an active high output incating a DMA request to the CPU. It is also actiduring refresh cycles. CPU HRQ is normally connect to the 80286 HOLD pin.                                               |  |  |  |  |

| 26         | -CS287          | 0    | CHIP SELECT 287 is used by POACH 7 to derive the -NPCS signal. Tie directly to the -CS287 pin of POACH 7.                                                                                                           |  |  |  |  |

# 17E D ■ 9997499 0001061 259 ■ZYM POACH 7/POACH 8

## APPIAN TECHNOLOGY INC

## POACH 8 Pin Description (Continued)

| Pin<br>No.     | Symbol               | Туре | Description                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|----------------|----------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 61–58<br>57–55 | -DACK0-3<br>-DACK5-7 | 0    | DMA ACKNOWLEDGE 0-3 and 5-7 are used to ac<br>knowledge DMA requests (DRQ0-3 & 5-7). The output<br>signal is an active low.                                                                                                                                                                                   |  |  |  |  |

| 37             | -DMAAEN              | 0    | DMA ADDRESS ENABLE is an active low signal and is active when an I/O device is making a DMA access to system memory or during refresh.                                                                                                                                                                        |  |  |  |  |

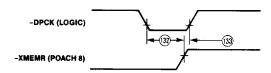

| 39             | -DPCK                | ı    | DATA PARITY CHECK is used to generate NMI. This input is active low.                                                                                                                                                                                                                                          |  |  |  |  |

| 46–49<br>50–52 | DRQ0-3<br>DRQ5-7     | 1    | DMA REQUEST 0-3 & 5-7 are synchronous channe requests used by peripheral devices and I/O processors to gain DMA service. The requests are prioritized with DRQ0 having the highest and DRQ7 having the lowes priorities. A DRQ line must be held active (high) until the corresponding DACK line goes active. |  |  |  |  |

| 21             | HLDA                 | I    | HOLD ACKNOWLEDGE is an active high input that is equivalent to CPU HLDA. An active condition indicates that the CPU has relinquished the bus to another bus master in the system.                                                                                                                             |  |  |  |  |

| 30             | -INTA                | l    | INTERRUPT ACKNOWLEDGE instructs an interrupting device that its interrupt is being acknowledged, and the device may place its interrupt vector onto the data bus. This input signal is active low. –INTA is used by POACH 8 in the generation of –RDXDB. From POACH 7 pin 56.                                 |  |  |  |  |

| 28             | -INTR1CS             | 0    | INTERRUPT CONTROLLER 1 (MASTER) CHIP SELECT is an active low output that is used by POACH 7 to select the interrupt controller as an I/O device. This allows communication between the master interrupt controller and the CPU via the 'X' data bus. Tie directly to the –INTR1CS pin of POACH 7.             |  |  |  |  |

| 29             | -INTR2CS             | 0    | INTERRUPT CONTROLLER 2 (SLAVE) CHIP SELECT is an active low output that is used by POACH 7 to select the interrupt controller as an I/O device. This allows communication between the slave interrupt controller and the CPU via the 'X' data bus. Tie directly to the -INTR2CS pin of POACH 7.               |  |  |  |  |

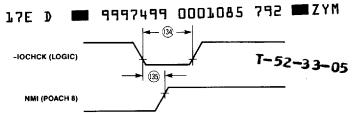

| 43             | -IOCHCK              | ı    | I/O CHANNEL CHECK is an active low input. It is used to indicate an uncorrectable system error. Usually provides the system with parity error information about memory or devices on the I/O channel.                                                                                                         |  |  |  |  |

## POACH 7/POACH 8

## APPIAN TECHNOLOGY INC

## POACH 8 Pin Description (Continued)

| Pin<br>No. | Symbol               | Туре | Description                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|------------|----------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 42         | IOCHRDY              | I    | I/O CHANNEL READY is generated by an I/O device. When low it indicates a 'not ready' condition and forces the insertion of wait states in I/O or memory accesses by the I/O device. When active (high), it will allow the completion of a memory or an I/O access by the I/O device.                                                                                                   |  |  |  |  |

| 33         | -IOR                 | 1/0  | I/O READ signal instructs a selected I/O device to drive its data onto the data bus. The -IOR signal is active low. It is used for data transfers between the CPU and by DMA transfers.                                                                                                                                                                                                |  |  |  |  |

| 34         | -IOW                 | I/O  | I/O WRITE signal instructs a selected I/O device to read the data on the data bus. The -IOW signal is active low. It is used for data transfers between the CPU and by DMA transfers.                                                                                                                                                                                                  |  |  |  |  |

| 27         | IRQ0                 | 0    | INTERRUPT REQUEST 0 (system timer) from channe 0 of the timer/counter. Tie directly to the IRQ0 pin o POACH 7.                                                                                                                                                                                                                                                                         |  |  |  |  |

| 40         | -MASTER              | I    | -MASTER is an active low input used in conjunction with a DRQ line to gain control of the system. A DMA controller or processor on the I/O channel may issue DRQ to a DMA channel and receive a -DACK. The I/O processor may then activate -MASTER, which allows to control the system address, data, and control lines.                                                               |  |  |  |  |

| 65         | NMI                  | 0    | NON-MASKABLE INTERRUPT is an active high output that is connected to the CPU NMI pin.                                                                                                                                                                                                                                                                                                  |  |  |  |  |

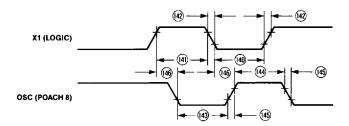

| 67         | OSC                  | 0    | OSCILLATOR output is the clock frequency of the crystal connected across X1–X2. It is the OSC output from the clock generator.                                                                                                                                                                                                                                                         |  |  |  |  |

| 20<br>35   | Reserved<br>Reserved |      | Do not connect.                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| 38         | -RDXDB               | 0    | READ X-DATA BUS controls the direction of the bidirectional buffer between the least significant byte of the 'S' data bus and the 'X' data busRDXDB is used in conjunction with +ACK to control XBUS activity. When +ACK is active and -RDXDB is low, data is to be read from the peripheral bus. When +ACK is active and -RDXDB is high, data is to be written to the peripheral bus. |  |  |  |  |

## 17E D 🖿 9997499 0001063 021 🗪 ZYM POACH 7/POACH 8

## APPIAN TECHNOLOGY INC

## POACH 8 Pin Description (Continued)

| Pin<br>No.         | Symbol                      | Туре            | Description                                                                                                                                                                                                               |  |  |  |

|--------------------|-----------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 22                 | REFRDY                      | 0               | REFRESH/IO-CHANNEL-READY is generated by +REFRESH OR'd with IOCHRDY. It is used by POACH 7 to preset the clock generator & ready interface asynchronous ready (ARDY).                                                     |  |  |  |

| 41                 | -REFRESH                    | 1/0             | REFRESH is an active low output used to initiate a refresh cycle for the dynamic RAMs.                                                                                                                                    |  |  |  |

| 31                 | +RESET                      | 1               | RESET (SYSTEM) is an active high input from POACH 7. +RESET is used to force POACH 8, as well as the system, into an initial state. From POACH 7 pin 55.                                                                  |  |  |  |

| 66                 | SPEAKER                     | 0               | SPEAKER DATA is an output of the programmable interval timer tone signal used to drive the speaker.                                                                                                                       |  |  |  |

| 32                 | SYSCLK                      | ı               | SYSTEM CLOCK input from POACH 7. It is used to synchronize POACH 8 to the system. From POACH 7 SYSCLK pin.                                                                                                                |  |  |  |

| 62                 | T/C                         | 0               | TERMINAL COUNT provides a pulse when the terminal count for any DMA channel is reached.                                                                                                                                   |  |  |  |

| 11<br>53           | Vcc1<br>Vcc2                |                 | POWER: +5-volt supply.                                                                                                                                                                                                    |  |  |  |

| 10<br>54           | Vss1<br>Vss2                |                 | GROUND.                                                                                                                                                                                                                   |  |  |  |

| 68<br>69           | X1<br>X2                    | 0               | CRYSTAL connections for the internal oscillator used to generate clocking for I/O devices. A parallel resonant fundamental frequency mode crystal is required. An alternative CMOS clock may be connected to X1 (pin 68). |  |  |  |

| 1–9<br>84<br>77–83 | XA8-XA0<br>XA9<br>XA16-XA10 | I/O<br>I/O<br>O | XBUS ADDRESSES 0-16 are the peripheral addresses for the local I/O bus.                                                                                                                                                   |  |  |  |

| 12-19              | XD0-XD7                     | 1/0             | Data Bus 0-7 for the peripheral bus. The direction of the bus is determined by the -RDXDB signal from POACH 8.                                                                                                            |  |  |  |

| 44                 | -XMEMR                      | I/O             | MEMORY READ signal indicating a DMA read operation from peripheral devices or memory.                                                                                                                                     |  |  |  |

| 45                 | -XMEMW                      | 0               | MEMORY WRITE signal indicating a DMA write operation to peripheral devices or memory.                                                                                                                                     |  |  |  |

## POACH 7/POACH 8

## APPIAN TECHNOLOGY INC

T-52-33-05

#### **ABSOLUTE MAXIMUM RATINGS\***

### POACH/ATF DC CHARACTERISTICS

$(V_{CC} = 5V \pm 5\%, T_A = 0^{\circ}C \text{ to } 70^{\circ}C)$

|                  |                               |                                       | Value |     |     |       |       |  |  |  |

|------------------|-------------------------------|---------------------------------------|-------|-----|-----|-------|-------|--|--|--|

| Symbol           | Parameter                     | Condition                             | Min   | Тур | Max | Units | Notes |  |  |  |

| INPUTS           | PUTS                          |                                       |       |     |     |       |       |  |  |  |

| V <sub>IL1</sub> | Input Low Voltage             |                                       |       |     | 0.5 | ٧     | 1     |  |  |  |

| V <sub>IH1</sub> | Input High Voltage            |                                       | 2.0   |     |     | ٧     | 1     |  |  |  |

| V <sub>IL2</sub> | Special Input Low Voltage     |                                       |       |     | 0.5 | ٧     | 2     |  |  |  |

| V <sub>IH2</sub> | Special Input High Voltage    |                                       | 4.5   |     |     | ٧     | 2     |  |  |  |

| I <sub>IL1</sub> | Input Low Current             | V <sub>IN</sub> = 0V                  | -100  |     |     | μΑ    | 3     |  |  |  |

| I <sub>IL2</sub> | Special Input Low Current     | V <sub>IN</sub> = 0V                  | -10   |     |     | μΑ    | 4     |  |  |  |

| I <sub>IH</sub>  | Input High Current            | V <sub>IN</sub> = V <sub>CC</sub>     |       |     | 10  | μΑ    |       |  |  |  |

| OUTPU            | TS                            | •                                     |       |     |     |       |       |  |  |  |

| I <sub>OL1</sub> | Output Low Current            | V <sub>OL</sub> = 0.45V               | 4     | 20  |     | mA    | 5     |  |  |  |

| I <sub>OL2</sub> | Output Low Current            | V <sub>OL</sub> = 0.45V               | 24    | 35  |     | mA    | 6     |  |  |  |

| I <sub>OL3</sub> | Open Drain Output Low Current | V <sub>OL</sub> = 0.45V               | 24    | 36  |     | mA    | 7     |  |  |  |

| I <sub>OH</sub>  | Output High Current           | V <sub>OH</sub> = 2.4V                |       | -20 | -4  | mA    | 8     |  |  |  |

| loz              | Off State Current             | V <sub>O</sub> = 0 to V <sub>CC</sub> | -10   |     | 10  | μΑ    | 9     |  |  |  |

<sup>\*</sup>Notice: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## 9997499 0001065 9T4 XYM POACH 7/POACH 8

## APPIAN TECHNOLOGY INC

## POACH/ATF DC CHARACTERISTICS (Continued)

$(V_{CC} = 5V \pm 5\%, T_A = 0^{\circ}C \text{ to } 70^{\circ}C)$

T-52-33-05

|                    |                                  |                                                              | Value |          |          |          |       |

|--------------------|----------------------------------|--------------------------------------------------------------|-------|----------|----------|----------|-------|

| Symbol             | Parameter                        | Condition                                                    | Min   | Тур      | Max      | Units    | Notes |

| INPUTS             |                                  |                                                              |       | <u> </u> |          |          | 1     |

| I <sub>CC7</sub>   | POACH 7 Operating Supply Current | f <sub>SYSCLK</sub> = 12.5MHz<br>f <sub>SYSCLK</sub> = 16MHz |       | 28<br>32 | 55<br>60 | mA<br>mA | 10    |

| I <sub>STAT7</sub> | POACH 7 Static Supply Current    |                                                              |       | 60       |          | μΑ       | 11    |

| I <sub>BATT</sub>  | POACH 7 Battery Supply Current   | V <sub>BATT</sub> = 5V<br>V <sub>BATT</sub> = 2.8V           |       | 10       | 25<br>20 | μA<br>μA | 12    |

| V <sub>BATT</sub>  | POACH 7 Battery Supply Voltage   |                                                              | 2.8   |          |          | ٧        | 12    |

| I <sub>CC8</sub>   | POACH 8 Operating Supply Current | f <sub>SYSCLK</sub> =12.5MHz<br>f <sub>SYSCLK</sub> =16MHz   |       | 26<br>30 | 45<br>50 | mA<br>mA | 13    |

#### Notes:

1. Includes all inputs, and I/O pin inputs except for POACH 7 pins POWERGOOD, X3, X5, CCRRST, CCROSC and POACH 8 pins X1, IOCHRDY and -REFRESH.

2. Special input pins include the crystal input pins and inputs needed for battery backup. On POACH 7 these signals are POWERGOOD, X3, X5, CCRRST and CCROSC. On POACH 8 they are signals X1, IOCHRDY and -REFRESH. Note that CCROSC is the only signal that should switch in the battery back up mode. For backup operation with V<sub>BATT</sub> < 4.75V CCROSC input levels V<sub>IL</sub>/V<sub>IH</sub> should be 10% and 90% of V<sub>BATT</sub>, respectively.

3. All input pins include a high impedance pullup with the static protection network except for the special inputs

POWERGOOD, X3, CCROSC, CCRRST and X1. I/O pins do not have this pullup.

4. Includes pin POWERGOOD, X3, CCROSC and CCRRST of POACH 7; and X1 of POACH 8.

5. Includes all outputs, and I/O pin outputs except for POACH 7 pins PROCCLK, SYSCLK, -IOR, -IOW, -MEMR, -MEMW, INTA, ALE, SAO, and POACH 8 pins -IOR, -IOW, OSC and -REFRESH.

6. Includes outputs PROCCLK, SYSCLK, -IOR, -IOW, -MEMR, -MEMW, INTA, ALE, SA0 of POACH 7 and -IOR, -IOW and OSC of POACH 8.

For the -REFRESH output of POACH 8.

8. Includes all outputs and I/O pin outputs except for -REFRESH of POACH 8.

9. For all 3-state and I/O pin outputs.

10. Includes I<sub>BATT</sub> current with V<sub>BATT</sub> = V<sub>CC</sub>, and f<sub>CCROSC</sub> = 32.768 KHz.

11. Inputs not switching at V<sub>IN</sub> = V<sub>CC</sub>, except f<sub>CCROSC</sub> = 32.768 KHz. Includes I<sub>BATT</sub> current with V<sub>BATT</sub> = V<sub>CC</sub>.

12. Tested with CCROSC input toggling at 32.768 KHz and CCRRST = V<sub>BATT</sub>, all other inputs and V<sub>CC</sub> supply pins

13. Tested with input X1 switching at 14.3181 MHz.

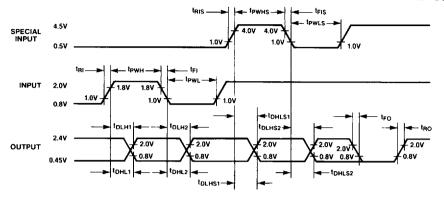

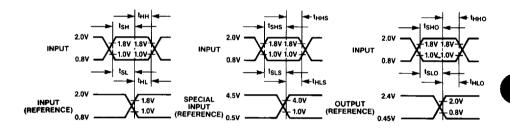

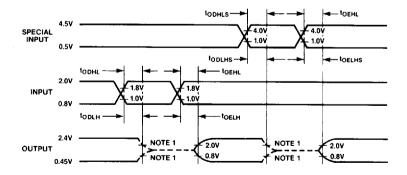

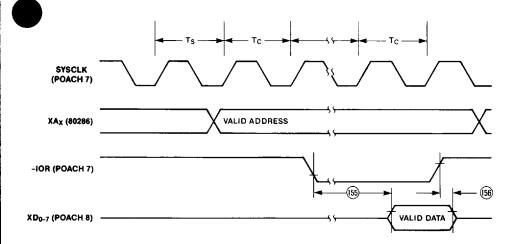

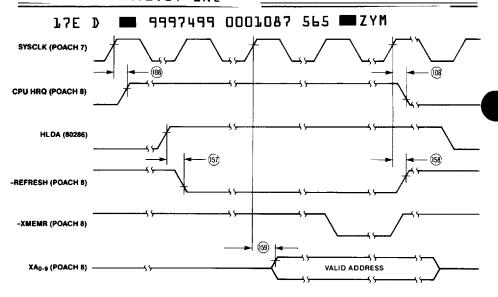

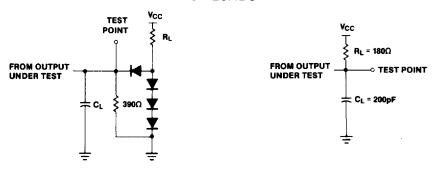

## **POACH 7 AC CHARACTERISTICS**

$(V_{DD} = 5V \pm 5\%, T_A = 0^{\circ} C \text{ to } 70^{\circ} C)$

| Symbol                  |                                                                                     | 1        | 2.5 MH   | iz             |          | 16 MH:  | Z              |                |        |

|-------------------------|-------------------------------------------------------------------------------------|----------|----------|----------------|----------|---------|----------------|----------------|--------|

| -Figure                 | Parameter                                                                           | Min      | Тур      | Max            | Min      | Тур     | Max            | Units          | Notes  |

| 53-15<br>54-15          | 0WS Setup Time to PROCCLKI<br>0WS Hold Time from PROCCLKI                           | 25<br>0  | 22<br>0  |                | 15<br>0  |         |                | ns<br>ns       |        |

| 69-22                   | A0 Setup Time to ALE<br>A0 Hold Time from ALE                                       | 25<br>0  | 11<br>0  |                | 15<br>0  |         |                | ns<br>ns       |        |

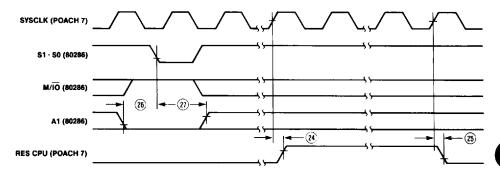

| 26-6<br>27-6            | A1 Setup Time to S1, S0<br>A1 Hold Time from S1, S0                                 | 22<br>0  | 10<br>0  |                | 15<br>0  |         |                | ns<br>ns       |        |

| 43-13<br>44-13<br>45-13 | A20 Delay from NA20<br>A20 Delay from A20GATE<br>A20 Disable Delay<br>from CPUHLDA1 |          | 14<br>24 | 22<br>32<br>30 |          |         | 20<br>31<br>30 | ns<br>ns<br>ns | 4      |

| 46-13                   | A20 Enable Delay<br>from CPUHLDA                                                    |          |          | 30             |          |         | 30             | ns             |        |

| 72-24                   | -AEN1, -AEN2 Setup Time to SYSCLKI                                                  |          | 15       |                |          | 15      |                | ns             |        |

| 73-24                   | -AEN1, -AEN2 Hold Time<br>from SYSCLK!                                              |          | 0        |                |          | 0       |                | ns             |        |

| 17-15                   | ALE Active Delay from PROCCLKI                                                      |          | 16       | 23             |          |         | 20             | ns             |        |

| 18-15                   | ALE Inactive Delay from PROCCLKI                                                    |          | 15       | 25             |          |         | 22             | ns             |        |

| 68-21                   | -BUSY286 Delay                                                                      |          | 20       | 35             |          |         | 31             | ns             |        |

|                         | CCROSC High Time<br>CCROSC Low Time<br>CCROSC Input Rise/Fall Time                  | 15<br>15 |          | 20             | 15<br>15 |         | 20             | μs<br>μs<br>ns | 5<br>5 |

| 39-10,11<br>40-10,11    | CCRR/W Setup Time to IOR/IOWI CCRR/W Hold Time from IOR/IOW1                        |          | 0<br>15  |                |          | 0<br>15 |                | ns<br>ns       |        |

|                         | CCRRST Pulse Width                                                                  | 83       |          |                | 62       |         |                | ns             |        |

| 12-3                    | CLK287 Delay from OSC2871                                                           |          |          | 35             |          |         | 35             | ns             |        |

| 67-20                   | CNTLOFF Delay<br>from PROCCLKI                                                      |          | 17       | 25             |          |         | 20             | ns             |        |

| 70-23                   | CPUHLDA Setup Time to PROCCLKI                                                      |          | 18       |                |          | 15      |                | ns             |        |

| 71-23                   | CPUHLDA Hold Time<br>from PROCCLK                                                   |          | 0        |                |          | 0       |                | ns             |        |

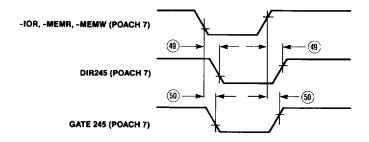

| 47-14                   | DIR245 Delay<br>from -IOR, -IOW                                                     |          | 6        | 15             |          |         | 15             | ns             |        |

| 49-14                   | DIR245 Delay<br>from -MEMR, -MEMW<br>DIR245 delay                                   |          | 6        | 15             |          |         | 15             | ns             |        |

|                         | from -AEN1, -AEN2                                                                   |          |          | 35             |          |         | 35             | ns             |        |

## POACH 7 AC CHARACTERISTICS (Continued)

T-52-33-05

$(V_{DD} = 5V \pm 5\%, T_A = 0^{\circ}C \text{ to } 70^{\circ}C)$

|                                                                                               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.5 MH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | lz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 16 MH2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2         |           |           |

|-----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------|-----------|