# Mobile AMD-K6®-III-P Processor

**Data Sheet**

Publication # 22655 Rev: C Amendment/O Issue Date: September 1999

#### © 1999 Advanced Micro Devices, Inc. All rights reserved.

The contents of this document are provided in connection with Advanced Micro Devices, Inc. ("AMD") products. AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this publication. Except as set forth in AMD's Standard Terms and Conditions of Sale, AMD assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right.

AMD's products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of AMD's product could create a situation where personal injury, death, or severe property or environmental damage may occur. AMD reserves the right to discontinue or make changes to its products at any time without notice.

#### Trademarks

AMD, the AMD logo, K6, 3DNow!, and combinations thereof, TriLevel Cache, and Super7 are trademarks, and AMD-K6 and RISC86 are registered trademarks of Advanced Micro Devices, Inc.

MMX is a trademark of Intel Corporation.

Microsoft, Windows, and Windows NT are registered trademarks of Microsoft Corporation.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

# Contents

| Revis | ion Hi                                                                                                | story                                                                                                                                                                                                                                                                                                                                                                                                | xi                                                                                  |

|-------|-------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| About | t This I                                                                                              | Data Sheet                                                                                                                                                                                                                                                                                                                                                                                           | iii                                                                                 |

| 1     | Mobil                                                                                                 | e AMD-K6 <sup>®</sup> -III-P Processor                                                                                                                                                                                                                                                                                                                                                               | 1                                                                                   |

|       | 1.1                                                                                                   | Super7 <sup>™</sup> Platform Initiative<br>Super7 Platform Enhancements:                                                                                                                                                                                                                                                                                                                             | 3                                                                                   |

| 2     | Intern                                                                                                | nal Architecture                                                                                                                                                                                                                                                                                                                                                                                     | 5                                                                                   |

|       | <ul> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>2.4</li> <li>2.5</li> <li>2.6</li> <li>2.7</li> </ul> | IntroductionMobile AMD-K6®-III-P Processor MicroarchitectureOverviewEnhanced RISC86® MicroarchitectureCache, Instruction Prefetch, and Predecode BitsCachePrefetching.Predecode BitsInstruction Fetch and DecodeInstruction FetchInstruction DecodeCentralized SchedulerExecution UnitsRegister X and Y PipelinesBranch-Prediction LogicBranch Target CacheReturn Address StackBranch Execution Unit | . 5<br>. 6<br>. 9<br>10<br>10<br>11<br>11<br>12<br>14<br>15<br>16<br>17<br>18<br>18 |

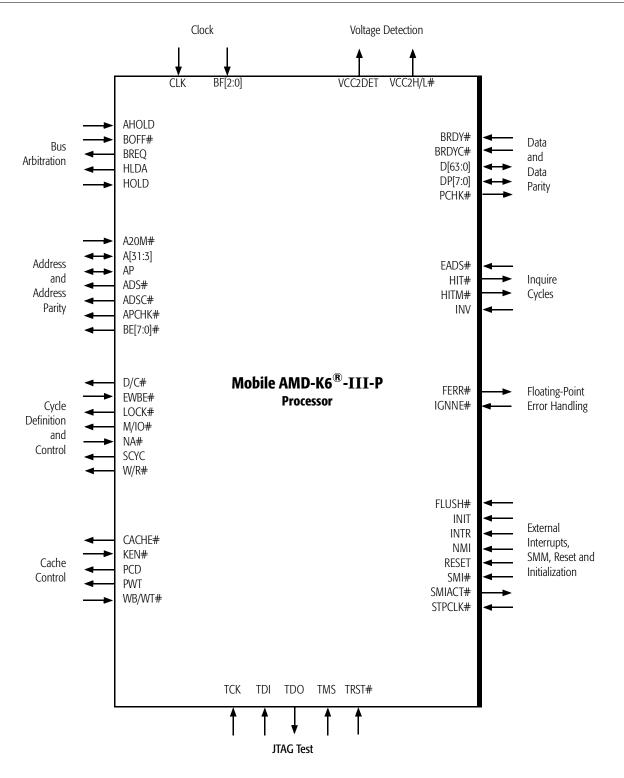

| 3     | Logic                                                                                                 | Symbol Diagram 2                                                                                                                                                                                                                                                                                                                                                                                     | 21                                                                                  |

| 4     | Signa                                                                                                 | l Descriptions                                                                                                                                                                                                                                                                                                                                                                                       | 23                                                                                  |

| 5     | Mobil                                                                                                 | e AMD-K6-III-P Processor Operation                                                                                                                                                                                                                                                                                                                                                                   | 35                                                                                  |

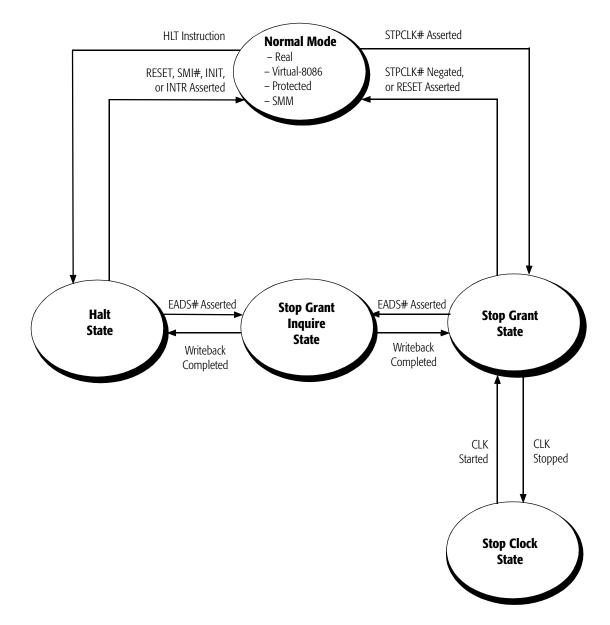

|       | 5.1<br>5.2                                                                                            | Process Technology<br>Clock Control<br>Halt State<br>Stop Grant State<br>Stop Grant Inquire State<br>Stop Clock State                                                                                                                                                                                                                                                                                | 35<br>36<br>37<br>38                                                                |

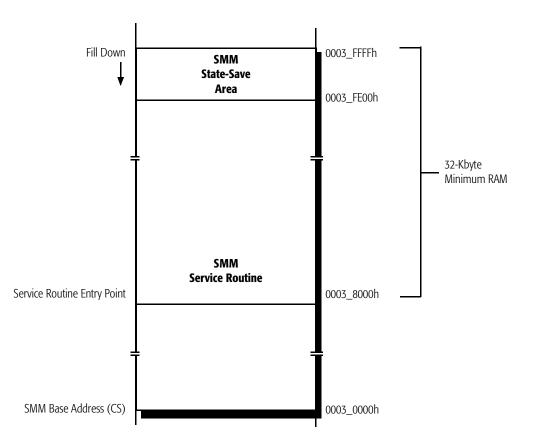

|   | 5.3                                                                         | System Management Mode (SMM)Overview.SMM Operating Mode and Default Register ValuesSMM State-Save AreaSMM Revision IdentifierSMM Base AddressHalt Restart SlotI/O Trap Dword.I/O Trap Restart SlotExceptions, Interrupts, and Debug in SMM         | . 40<br>. 40<br>. 42<br>. 45<br>. 45<br>. 46<br>. 46<br>. 47 |

|---|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| 6 | Signa                                                                       | Il Switching Characteristics                                                                                                                                                                                                                       | 51                                                           |

|   | 6.1<br>6.2                                                                  | CLK Switching Characteristics<br>Clock Switching Characteristics for 100-MHz Bus<br>Operation                                                                                                                                                      |                                                              |

|   | <ul> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>6.6</li> <li>6.7</li> </ul> | Clock Switching Characteristics for 66-MHz BusOperationValid Delay, Float, Setup, and Hold TimingsOutput Delay Timings for 100-MHz Bus OperationInput Setup and Hold Timings for 100-MHz BusOperationOutput Delay Timings for 66-MHz Bus Operation | . 53<br>. 54<br>. 56                                         |

|   | 6.8<br>6.9                                                                  | Input Setup and Hold Timings for 66-MHz BusOperationRESET and Test Signal Timing                                                                                                                                                                   |                                                              |

| 7 | Elect                                                                       | rical Data                                                                                                                                                                                                                                         | 69                                                           |

|   | 7.1<br>7.2<br>7.3<br>7.4<br>7.5                                             | Operating Ranges                                                                                                                                                                                                                                   | . 70<br>. 71<br>. 73<br>. 74<br>. 74<br>. 75                 |

| 8 | Ther                                                                        | mal Design                                                                                                                                                                                                                                         | 77                                                           |

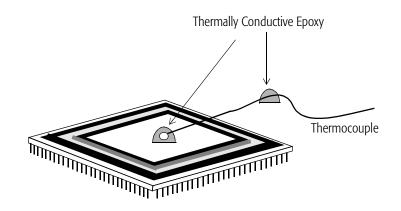

|   | 8.1                                                                         | Package Thermal SpecificationsHeat Dissipation PathMeasuring Case Temperature                                                                                                                                                                      | . 79                                                         |

| 9 | Packa                                                                       | age Specifications                                                                                                                                                                                                                                 | 81                                                           |

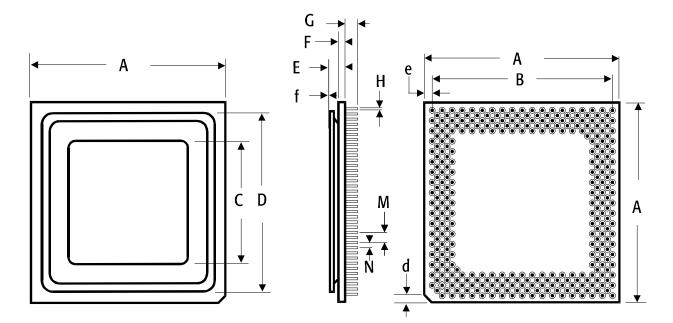

|   | 9.1                                                                         | 321-Pin Staggered CPGA Package Specification                                                                                                                                                                                                       | . 81                                                         |

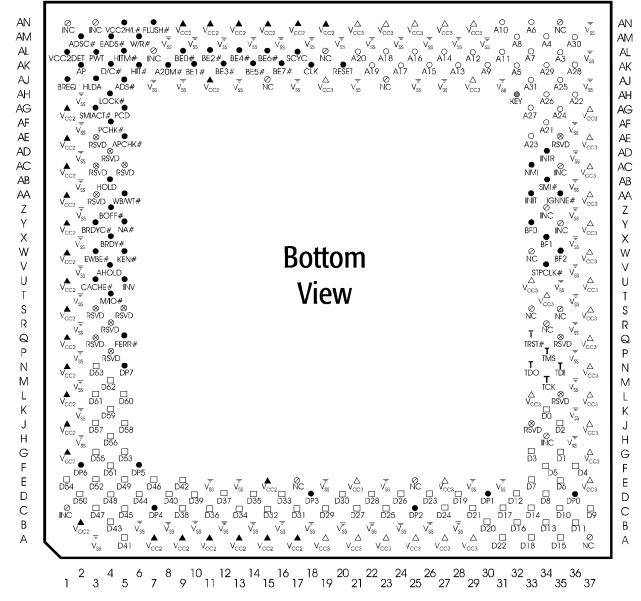

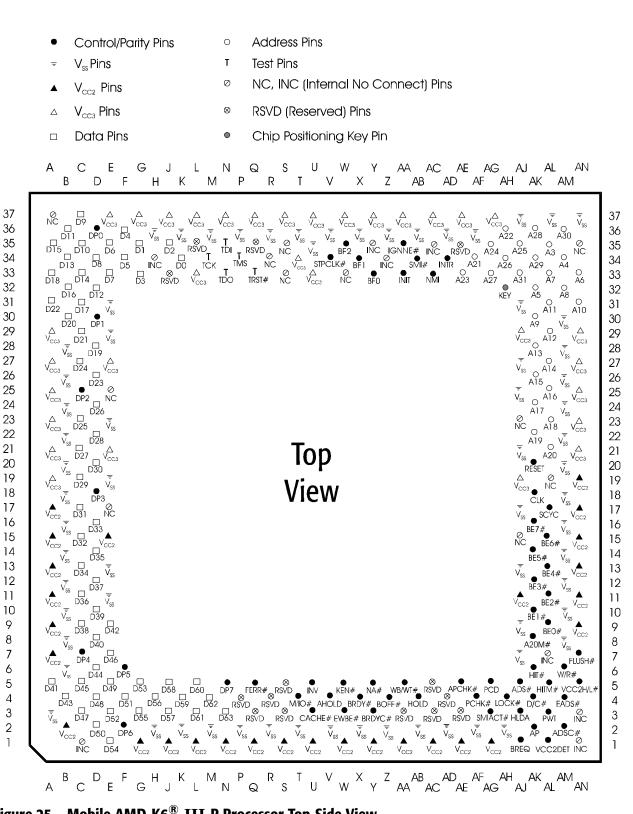

| 10   | Pin Description Diagrams                       |

|------|------------------------------------------------|

|      | 10.1 Pin Designations by Functional Grouping85 |

| 11   | Ordering Information                           |

| Inde | ex                                             |

# **List of Figures**

| Figure 1.  | Mobile AMD-K6 <sup>®</sup> -III-P Processor Block Diagram |

|------------|-----------------------------------------------------------|

| Figure 2.  | Cache Sector Organization10                               |

| Figure 3.  | The Instruction Buffer 11                                 |

| Figure 4.  | Mobile AMD-K6-III-P Processor Decode Logic12              |

| Figure 5.  | Mobile AMD-K6-III-P Processor Scheduler15                 |

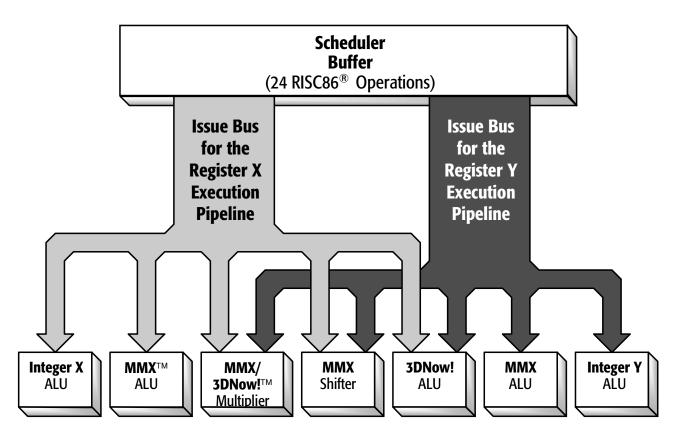

| Figure 6.  | Register X and Y Functional Units17                       |

| Figure 7.  | Clock Control State Transitions                           |

| Figure 8.  | SMM Memory                                                |

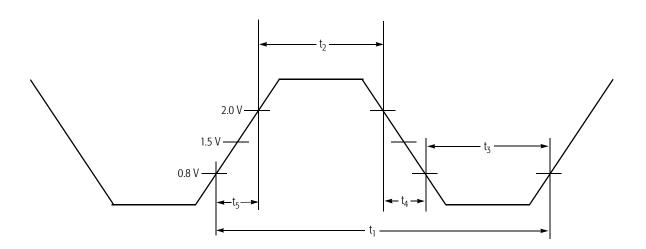

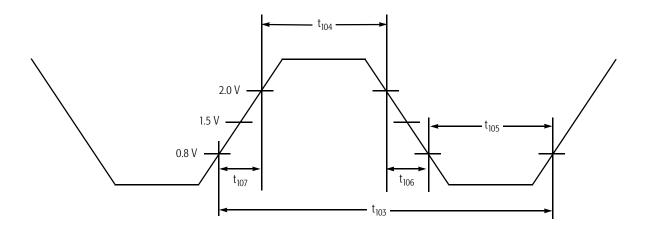

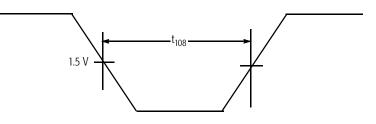

| Figure 9.  | CLK Waveform                                              |

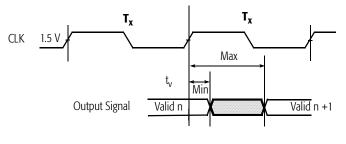

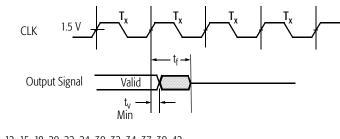

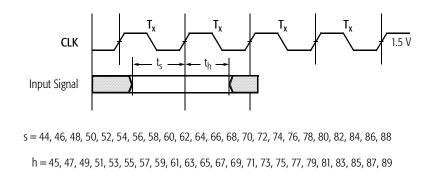

| Figure 10. | Diagrams Key                                              |

| Figure 11. | Output Valid Delay Timing65                               |

| Figure 12. | Maximum Float Delay Timing66                              |

| Figure 13. | Input Setup and Hold Timing66                             |

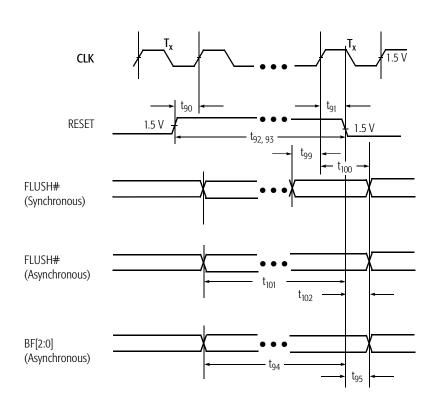

| Figure 14. | Reset and Configuration Timing67                          |

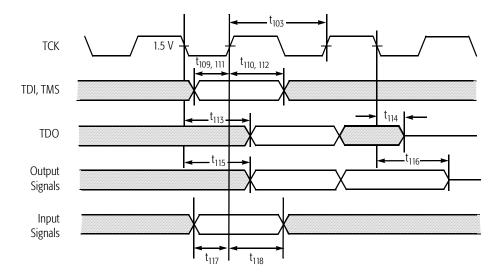

| Figure 15. | TCK Waveform                                              |

| Figure 16. | TRST# Timing68                                            |

| Figure 17. | Test Signal Timing Diagram68                              |

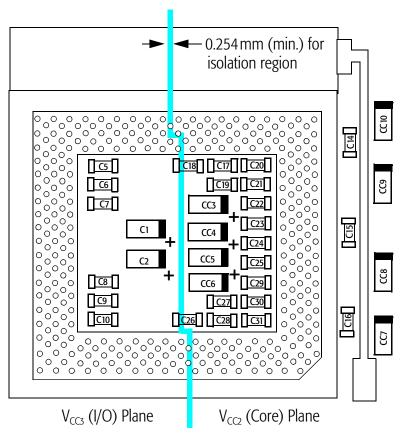

| Figure 18. | Suggested Component Placement                             |

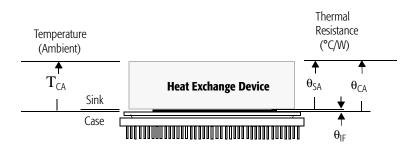

| Figure 19. | Thermal Model                                             |

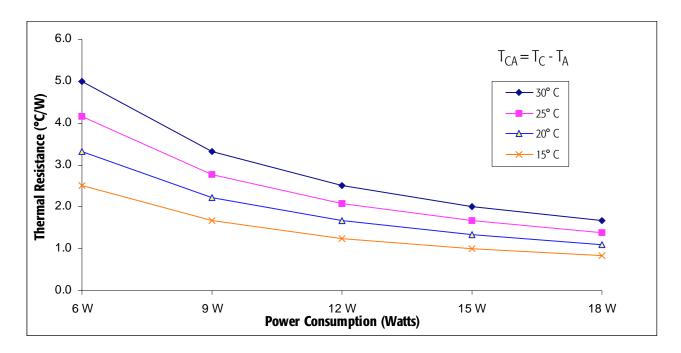

| Figure 20. | Power Consumption versus Thermal Resistance               |

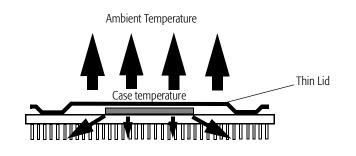

| Figure 21. | Processor's Heat Dissipation Path                         |

| Figure 22. | Measuring Case Temperature80                              |

| Figure 23. | 321-Pin Staggered CPGA Package Specification81            |

| Figure 24. | Mobile AMD-K6-III-P Processor Bottom-Side View83          |

| Figure 25. | Mobile AMD-K6-III-P Processor Top-Side View               |

# **List of Tables**

| Table 1.               | Execution Latency and Throughput of Execution Units16      |

|------------------------|------------------------------------------------------------|

| Table 2.               | Input Pin Types                                            |

| Table 3.               | Output Pin Float Conditions                                |

| Table 4.               | Input/Output Pin Float Conditions33                        |

| Table 5.               | Test Pins                                                  |

| Table 6.               | Bus Cycle Definition                                       |

| Table 7.               | Special Cycles                                             |

| Table 8.               | Initial State of Registers in SMM                          |

| Table 9.               | SMM State-Save Area Map42                                  |

| Table 10.              | SMM Revision Identifier45                                  |

| Table 11.              | I/O Trap Dword Configuration47                             |

| Table 12.              | I/O Trap Restart Slot                                      |

| Table 13.              | CLK Switching Characteristics for 100-MHz Bus Operation 52 |

| Table 14.              | CLK Switching Characteristics for 66-MHz Bus Operation 52  |

| Table 15.              | Output Delay Timings for 100-MHz Bus Operation54           |

| Table 16.              | Input Setup and Hold Timings for 100-MHz Bus Operation 56  |

| Table 17.              | Output Delay Timings for 66-MHz Bus Operation58            |

| Table 18.              | Input Setup and Hold Timings for 66-MHz Bus Operation 60   |

| Table 19.              | <b>RESET and Configuration Signals for 100-MHz Bus</b>     |

|                        | Operation                                                  |

| Table 20.              | RESET and Configuration Signals for 66-MHz Bus             |

| Table 21.              | Operation                                                  |

| Table 21.<br>Table 22. | Test Signal Timing at 25 MHz                               |

| Table 22.<br>Table 23. | Operating Ranges                                           |

| Table 23.<br>Table 24. | Absolute Ratings                                           |

| Table 24.<br>Table 25. | DC Characteristics                                         |

| Table 25.<br>Table 26. | Power Dissipation                                          |

| Table 20.<br>Table 27. | Package Thermal Specifications                             |

|                        |                                                            |

| Table 28.              | 321-Pin Staggered CPGA Package Specification               |

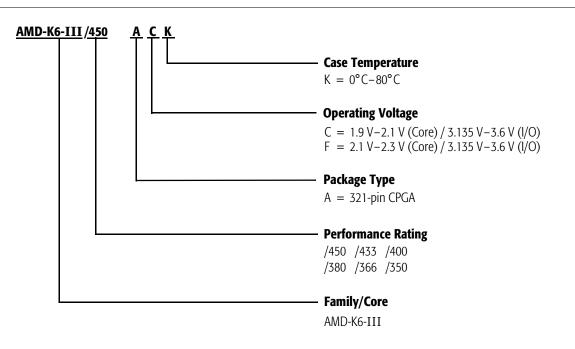

| Table 29.              | Valid Ordering Part Number Combinations87                  |

# **Revision History**

| Date        | Rev | Description                                                                                                                                                                       |  |  |  |  |  |

|-------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| May 1999    | Α   | Initial published release.                                                                                                                                                        |  |  |  |  |  |

| July 1999 B |     | Added two V <sub>CC2</sub> decoupling capacitors to Figure 18, "Suggested Component Placement," on page 75.                                                                       |  |  |  |  |  |

| Sept 1999   | С   | Added specifications and OPNs for 400 MHz, 433 MHz, and 450 MHz frequencies in Chapter 7, "Electrical Data", Chapter 8, "Thermal Design", and Chapter 11, "Ordering Information". |  |  |  |  |  |

22655C/0-September 1999

Mobile AMD-K6<sup>®</sup>-III-P Processor Data Sheet

# **About This Data Sheet**

The Mobile AMD-K6<sup>®</sup>-III-P Processor Data Sheet is a supplement to the AMD-K6<sup>®</sup>-III Processor Data Sheet, order# 21918. When combined, the two data sheets provide the complete specification of the Mobile AMD-K6-III-P processor.

1

# Mobile AMD-K6<sup>®</sup>-III-P Processor

- Advanced 6-Issue RISC86<sup>®</sup> Superscalar Microarchitecture

- Ten parallel specialized execution units

- Multiple sophisticated x86-to-RISC86 instruction decoders

- Advanced two-level branch prediction

- Speculative execution

- Out-of-order execution

- Register renaming and data forwarding

- Issues up to six RISC86 instructions per clock

- TriLevel Cache<sup>™</sup> Design

- Large On-Chip Split 64-Kbyte Level-One (L1) Cache

- 32-Kbyte instruction cache with additional predecode cache

- 32-Kbyte writeback dual-ported data cache

- On-die 256-Kbyte full processor speed, backside Level-Two (L2) Cache

- Support for external Level-Three (L3) Cache on 100-MHz frontside bus

- MESI protocol support

- High-Performance IEEE 754-Compatible and 854-Compatible Floating-Point Unit

- Superscalar MMX<sup>TM</sup> unit supports industry-standard MMX instructions

- 3DNow!<sup>TM</sup> Technology for high-performance multimedia and 3D graphics capabilities

- Compatible with Super7<sup>TM</sup> 100-MHz frontside bus or Socket 7 66-MHz notebook design

- Socket 7-Compatible Ceramic Pin Grid Array (CPGA) Package

- Industry-Standard System Management Mode (SMM)

- IEEE 1149.1 Boundary Scan

- x86 Binary Software Compatibility

- Low Voltage 0.25-Micron Process Technology

- 21.3 Million Transistors

The Mobile AMD-K6<sup>®</sup>-III-P processor is AMD's third generation mobile AMD-K6 processor delivering the highest performance yet for x86 notebook PC systems. The Mobile AMD-K6-III-P processor is based on the advanced Mobile AMD-K6-2 core and adds AMD's unique TriLevel Cache<sup>™</sup> design for enhanced system performance. The TriLevel Cache design provides a large 64-Kbyte L1 cache, a 256-Kbyte L2 cache operating at full processor speed on a backside bus, and up to 1 Mbyte of available L3 cache memory on the external 100-MHz frontside bus. This combination of the largest

and fastest cache memory subsystem gives the Mobile AMD-K6-III-P processor its performance edge over competing x86 mobile CPU solutions.

The Mobile AMD-K6-III-P processor also incorporates a superscalar MMX unit, support for a 100-MHz frontside bus, and AMD's innovative 3DNow! technology for high-performance multimedia and 3D graphics operation.

The Mobile AMD-K6-III-P processor includes several key features for the mobile market. The processor is implemented using an AMD-developed, state-of-the-art low power 0.25-micron process technology. This process technology features a split-plane design that allows the processor core to operate at a lower voltage while the I/O portion operates at the industry-standard 3.3V level. The 0.25-micron process technology with the split-plane voltage design enables the Mobile AMD-K6-III-P processor to deliver excellent portable PC performance solutions while utilizing a lower processor core voltage, which results in lower power consumption and longer battery life. In addition, the Mobile AMD-K6-III-P processor includes the complete industry-standard System Management Mode (SMM), which is critical to system resource and power management. The Mobile AMD-K6-III-P processor also features the industry-standard Stop-Clock (STPCLK#) control circuitry and the Halt instruction, both required for implementing the ACPI power management specification. The Mobile AMD-K6-III-P processor is offered in an industry-standard Socket 7-compatible, 321-pin Ceramic Pin Grid Array (CPGA) package.

The Mobile AMD-K6-III-P processor's RISC86 microarchitecture is a decoupled decode/execution superscalar design that implements state-of-the-art design techniques to achieve leading-edge performance. Advanced design techniques implemented in the Mobile AMD-K6-III-P processor include multiple x86 instruction decode, single-clock internal RISC operations, ten execution units that support superscalar operation, out-of-order execution, data forwarding, speculative execution, and register renaming. In addition, the processor supports the industry's most advanced branch prediction logic by implementing an 8192-entry branch history table, the industry's only branch target cache, and a return address stack, which combine to deliver better than a 95% prediction rate. These design techniques enable the Mobile AMD-K6-III-P processor to issue, execute, and retire multiple x86 instructions per clock, resulting in excellent scaleable performance.

AMD's 3DNow! technology is an instruction set extension to x86 that includes 21 new instructions to improve 3D graphics operations and other single precision floating-point compute intensive operations. AMD has already shipped millions of AMD-K6 family processors with 3DNow! technology for desktop PCs, revolutionizing the 3D experience with up to four times the peak floating-point performance of previous generation solutions. AMD is now bringing this advanced capability to notebook computing, working in conjunction with advanced mobile 3D graphic controllers to reach new levels of realism in mobile computing. With support from Microsoft<sup>®</sup> and the x86 software developer community, a new generation of visually compelling applications is coming to market that support the 3DNow! technology.

22655C/0-September 1999

The Mobile AMD-K6-III-P processor remains pin compatible with existing Socket 7 notebook solutions, however for maximum system performance, the processor works optimally in newer Super7 designs that incorporate advanced features such as support for the 100-MHz frontside bus and AGP graphics.

The Mobile AMD-K6-III-P processor has undergone extensive testing and is compatible with Windows<sup>®</sup> 98, Windows NT<sup>®</sup> and other leading operating systems. The Mobile AMD-K6-III-P processor is also compatible with more than 60,000 software applications, including the latest 3DNow! technology and MMX technology software. As the world's second-largest supplier of processors for the Windows environment, AMD has shipped more than 50 million Microsoft Windows compatible processors in the last five years.

The Mobile AMD-K6-III-P processor is the next generation in a long line of Microsoft Windows compatible processors from AMD. With its combination of state-of-the-art features, leading-edge performance, high-performance multimedia engine, x86 compatibility, and low-cost infrastructure, the Mobile AMD-K6-III-P processor is the superior choice for notebook computers.

## 1.1 Super7<sup>™</sup> Platform Initiative

AMD and its industry partners are investing in the future of Socket 7 with the new Super7 platform initiative. The goal of the initiative is to maintain the competitive vitality of the Socket 7 infrastructure through a series of planned enhancements, including the development of an industry-standard 100-MHz processor bus protocol. In addition to the 100-MHz processor bus protocol, the Super7 initiative includes the introduction of chipsets that support the AGP specification, and support for a backside L2 cache and frontside L3 cache.

#### Super7<sup>™</sup> Platform Enhancements:

- 100-MHz processor bus—The Mobile AMD-K6-III-P processor supports a 100-MHz, 800 Mbyte/second frontside bus to provide a high-speed interface to Super7 platform-based chipsets. The 100-MHz interface to the frontside L3 cache and main system memory speeds up access to the frontside cache and main memory by 50 percent over the 66-MHz Socket 7 interface—resulting in a significant 10% increase in overall system performance.

- Accelerated graphics port support—AGP improves the performance of mid-range PCs that have small amounts of video memory on the graphics card. The industry-standard AGP specification enables a 133-MHz graphics interface and will scale to even higher levels of performance.

- Support for backside L2 and frontside L3 cache—The Super7 platform has the 'headroom' to support higher-performance AMD-K6 processors, with clock speeds scaling to 450 MHz and beyond.

# 2 Internal Architecture

## 2.1 Introduction

The Mobile AMD-K6-III-P processor implements advanced design techniques known as the RISC86 microarchitecture. The RISC86 microarchitecture is a decoupled decode/execution design approach that yields superior sixth-generation performance for x86-based software. This chapter describes the techniques used and the functional elements of the RISC86 microarchitecture.

## 2.2 Mobile AMD-K6<sup>®</sup>-III-P Processor Microarchitecture Overview

When discussing processor design, it is important to understand the terms architecture, microarchitecture, and design implementation. The term architecture refers to the instruction set and features of a processor that are visible to software programs running on the processor. The architecture determines what software the processor can run. The architecture of the Mobile AMD-K6-III-P processor is the industry-standard x86 instruction set.

The term *microarchitecture* refers to the design techniques used in the processor to reach the target cost, performance, and functionality goals. The Mobile AMD-K6 family of processors are based on a sophisticated RISC core known as the Enhanced RISC86 microarchitecture. The Enhanced RISC86 microarchitecture is an advanced, second-order decoupled decode/execution design approach that enables industry-leading performance for x86-based software.

The term *design implementation* refers to the actual logic and circuit designs from which the processor is created according to the microarchitecture specifications.

#### Enhanced RISC86<sup>®</sup> Microarchitecture

The Enhanced RISC86 microarchitecture defines the characteristics of the AMD-K6 family. The innovative RISC86 microarchitecture approach implements the x86 instruction set by internally translating x86 instructions into RISC86 operations. These RISC86 operations were specially designed to include direct support for the x86 instruction set while observing the RISC performance principles of fixed length encoding, regularized instruction fields, and a large register set. The Enhanced RISC86 microarchitecture used in the Mobile AMD-K6-III-P processor enables higher processor core performance and promotes straightforward extensions, such as those added in the current Mobile AMD-K6-III-P processor and those planned for the future. Instead of directly executing complex x86 instructions, which have lengths of 1 to 15 bytes, the Mobile AMD-K6-III-P processor executes the simpler and easier fixed-length RISC86 operations, while maintaining the instruction coding efficiencies found in x86 programs.

The Mobile AMD-K6-III-P processor contains parallel decoders, a centralized RISC86 operation scheduler, and ten execution units that support superscalar operation—multiple decode, execution, and retirement—of x86 instructions. These elements are packed into an aggressive and highly efficient six-stage pipeline.

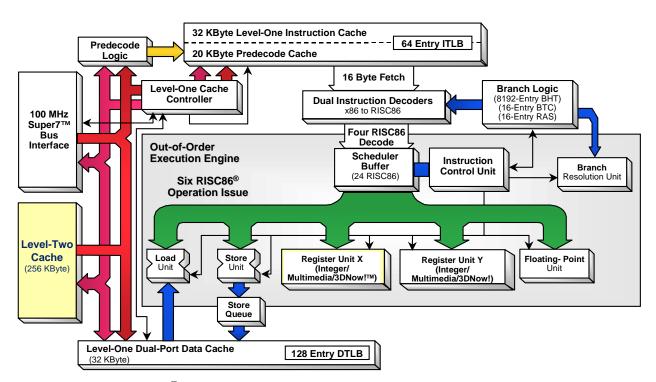

**Mobile AMD-K6**<sup>®</sup>-III-P Processor Block Diagram. As shown in Figure 1 on page 7, the high-performance, out-of-order execution engine of the Mobile AMD-K6-III-P processor is mated to a split, level-one, 64-Kbyte, writeback cache with 32 Kbytes of instruction cache and 32 Kbytes of data cache. Backing up the level-one cache is a large, unified, level-two, 256-Kbyte, writeback cache. The level-one instruction cache feeds the decoders and, in turn, the decoders feed the scheduler. The ICU issues and retires RISC86 operations contained in the scheduler. The system bus interface is an industry-standard 64-bit Super7 and Socket 7 demultiplexed bus.

The Mobile AMD-K6-III-P processor combines the latest in processor microarchitecture to provide the highest x86 performance for today's personal computers. The Mobile AMD-K6-III-P processor offers true sixth-generation performance and x86 binary software compatibility.

Figure 1. Mobile AMD-K6<sup>®</sup>-III-P Processor Block Diagram

**Decoders.** Decoding of the x86 instructions begins when the on-chip level-one instruction cache is filled. Predecode logic determines the length of an x86 instruction on a byte-by-byte basis. This predecode information is stored, along with the x86 instructions, in the level-one instruction cache, to be used later by the decoders. The decoders translate on-the-fly, with no additional latency, up to two x86 instructions per clock into RISC86 operations.

Note: In this chapter, "clock" refers to a processor clock.

The Mobile AMD-K6-III-P processor categorizes x86 instructions into three types of decodes—short, long, and vector. The decoders process either two short, one long, or one vector decode at a time. The three types of decodes have the following characteristics:

- Short decodes—x86 instructions less than or equal to seven bytes in length

- Long decodes—x86 instructions less than or equal to 11 bytes in length

- Vector decodes—complex x86 instructions

Short and long decodes are processed completely within the decoders. Vector decodes are started by the decoders and then completed by fetched sequences from an on-chip ROM. After decoding, the RISC86 operations are delivered to the scheduler for dispatching to the executions units.

**Scheduler/Instruction Control Unit.** The centralized scheduler or buffer is managed by the Instruction Control Unit (ICU). The ICU buffers and manages up to 24 RISC86 operations at a time. This equals from 6 to 12 x86 instructions. This buffer size (24) is perfectly matched to the processor's six-stage RISC86 pipeline and four RISC86-operations decode rate. The scheduler accepts as many as four RISC86 operations at a time from the decoders and retires up to four RISC86 operations per clock cycle. The ICU is capable of simultaneously issuing up to six RISC86 operations at a time to the execution units. This consists of the following types of operations:

- Memory load operation

- Memory store operation

- Complex integer, MMX or 3DNow! register operation

- Simple integer, MMX or 3DNow! register operation

- Floating-point register operation

- Branch condition evaluation

**Registers.** When managing the 24 RISC86 operations, the ICU uses 69 physical registers contained within the RISC86 microarchitecture. 48 of the physical registers are located in a general register file and are grouped as 24 committed or architectural registers plus 24 rename registers. The 24 architectural registers consist of 16 scratch registers and 8 registers that correspond to the x86 general-purpose registers— EAX, EBX, ECX, EDX, EBP, ESP, ESI, and EDI. There is an analogous set of registers specifically for MMX and 3DNow! operations. There are 9 MMX/3DNow! committed or architectural registers plus 12 MMX/3DNow! rename registers. The 9 architectural registers consist of one scratch register and 8 registers that correspond to the MMX registers (mm0–mm7). For more detailed information, see the *3DNow*!<sup>TM</sup> Technology Manual, order# 21928.

**Branch Logic.** The Mobile AMD-K6-III-P processor is designed with highly sophisticated dynamic branch logic consisting of the following:

- Branch history/Prediction table

- Branch target cache

- Return address stack

The Mobile AMD-K6-III-P processor implements a two-level branch prediction scheme based on an 8192-entry branch history table. The branch history table stores prediction information that is used for predicting conditional branches. Because the branch history table does not store predicted target addresses, special address ALUs calculate target addresses on-the-fly during instruction decode. The branch target cache augments predicted branch performance by avoiding a one clock cache-fetch penalty. This specialized target cache does this by supplying the first 16 bytes of target instructions to the decoders when branches are predicted. The return address stack is a unique device specifically designed for optimizing CALL and RETURN pairs. In summary, the Mobile AMD-K6-III-P processor uses dynamic branch logic to minimize delays due to the branch instructions that are common in x86 software.

**3DNow!™ Technology.** AMD has taken a lead role in improving the multimedia and 3D capabilities of the x86 processor family with the introduction of 3DNow! technology, which uses a packed, single-precision, floating-point data format and Single Instruction Multiple Data (SIMD) operations based on the MMX technology model.

#### 2.3

The writeback level-one cache on the Mobile AMD-K6-III-P processor is organized as a separate 32-Kbyte instruction cache and a 32-Kbyte data cache with two-way set associativity. The level-two cache is 256 Kbytes, and is organized as a unified, fourway set-associative cache. The cache line size is 32 bytes, and lines are fetched from external memory using an efficient pipelined burst transaction. As the level-one instruction cache is filled from the level-two cache or from external memory, each instruction byte is analyzed for instruction boundaries using predecoding logic. Predecoding annotates information (5 bits per byte) to each instruction byte that later enables the decoders to efficiently decode multiple instructions simultaneously.

**Cache, Instruction Prefetch, and Predecode Bits**

Mobile AMD-K6<sup>®</sup>-III-P Processor Data Sheet

| Cache          | The processor cache design takes advantage of a sectored<br>organization (see Figure 2). Each sector consists of 64 bytes<br>configured as two 32-byte cache lines. The two cache lines of a<br>sector share a common tag but have separate pairs of MESI<br>(Modified, Exclusive, Shared, Invalid) bits that track the state<br>of each cache line.                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | Two forms of cache misses and associated cache fills can take<br>place—a tag-miss cache fill and a tag-hit cache fill. In the case<br>of a tag-miss cache fill, the level-one cache miss is due to a tag<br>mismatch, in which case the required cache line is filled either<br>from the level-two cache or from external memory, and the<br>level-one cache line within the sector that was not required is<br>marked as invalid. In the case of a tag-hit cache fill, the address<br>matches the tag, but the requested cache line is marked as<br>invalid. The required level-one cache line is filled from the<br>level-two cache or from external memory, and the level-one<br>cache line within the sector that is not required remains in the<br>same cache state. |

| Prefetching    | The Mobile AMD-K6-III-P processor conditionally performs cache prefetching which results in the filling of the required cache line first, and a prefetch of the second cache line making up the other half of the sector. From the perspective of the external bus, the two cache-line fills typically appear as two 32-byte burst read cycles occurring back-to-back or, if allowed, as pipelined cycles. The 3DNow! technology includes an instruction called PREFETCH that allows a cache line to be prefetched into the level-one data cache and the level-two cache. For more detailed information, see the <i>3DNow</i> ! <sup>TM</sup> <i>Technology Manual</i> , order# 21928.                                                                                    |

| Predecode Bits | Decoding x86 instructions is particularly difficult because the instructions are variable-length and can be from 1 to 15 bytes long. Predecode logic supplies the five predecode bits that are associated with each instruction byte. The predecode bits indicate the number of bytes to the start of the next x86 instruction. The predecode bits are stored in an extended instruction cache alongside each x86 instruction byte as shown in Figure 2. The predecode bits are passed with the instruction bytes to the decoders where they assist with parallel x86 instruction decoding.                                                                                                                                                                               |

| Tag     | Cache Line 0 | Byte 31 | Predecode Bits | Byte 30 | Predecode Bits | <br> | Byte 0 | Predecode Bits | MESI Bits |

|---------|--------------|---------|----------------|---------|----------------|------|--------|----------------|-----------|

| Address | Cache Line 1 | Byte 31 | Predecode Bits | Byte 30 | Predecode Bits | <br> | Byte 0 | Predecode Bits | MESI Bits |

## Figure 2. Cache Sector Organization

### 2.4 Instruction Fetch and Decode

#### **Instruction Fetch**

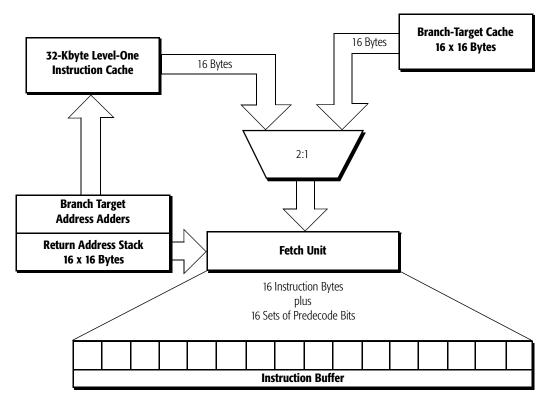

The processor can fetch up to 16 bytes per clock out of the levelone instruction cache or branch target cache. The fetched information is placed into a 16-byte instruction buffer that feeds directly into the decoders (see Figure 3). Fetching can occur along a single execution stream with up to seven outstanding branches taken.

The instruction fetch logic is capable of retrieving any 16 contiguous bytes of information within a 32-byte boundary. There is no additional penalty when the 16 bytes of instructions lie across a cache line boundary. The instruction bytes are loaded into the instruction buffer as they are consumed by the decoders. Although instructions can be consumed with byte granularity, the instruction buffer is managed on a memory-aligned word (two bytes) organization. Therefore, instructions are loaded and replaced with word granularity. When a control transfer occurs—such as a JMP instruction—the entire instruction buffer is flushed and reloaded with a new set of 16 instruction bytes.

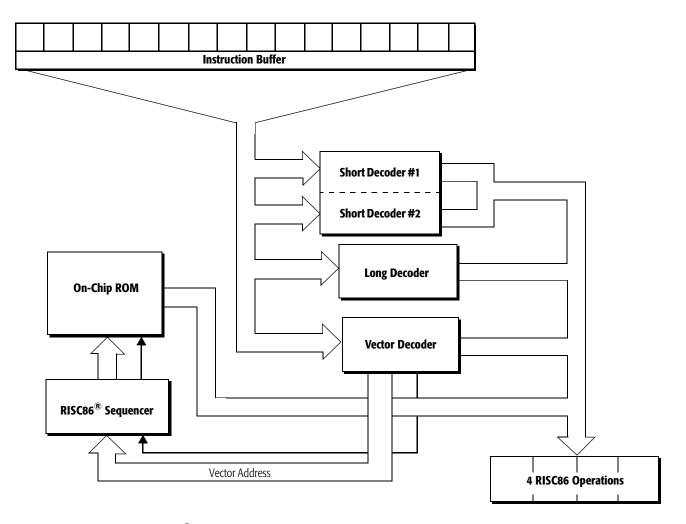

**Instruction Decode** The Mobile AMD-K6-III-P processor decode logic is designed to decode multiple x86 instructions per clock (see Figure 4). The decode logic accepts x86 instruction bytes and their predecode bits from the instruction buffer, locates the actual instruction boundaries, and generates RISC86 operations from these x86 instructions.

RISC86 operations are fixed-length internal instructions. Most RISC86 operations execute in a single clock. RISC86 operations are combined to perform every function of the x86 instruction set. Some x86 instructions are decoded into as few as zero RISC86 operations—for instance a NOP—or one RISC86 operation—a register-to-register add. More complex x86 instructions are decoded into several RISC86 operations.

Figure 4. Mobile AMD-K6<sup>®</sup>-III-P Processor Decode Logic

The Mobile AMD-K6-III-P processor uses a combination of decoders to convert x86 instructions into RISC86 operations. The hardware consists of three sets of decoders—two parallel short decoders, one long decoder, and one vector decoder. The two parallel short decoders translate the most commonly-used x86 instructions (moves, shifts, branches, ALU, FPU) and the extensions to the x86 instruction set (including MMX and 3DNow! instructions) into zero, one, or two RISC86 operations each. The short decoders only operate on x86 instructions that are up to seven bytes long. In addition, they are designed to decode up to two x86 instructions that are greater than seven bytes but not more than 11 bytes long, and semi-commonly-used x86 instructions that are up to seven bytes long are handled by the long decoder.

The long decoder only performs one decode per clock and generates up to four RISC86 operations. All other translations (complex instructions, serializing conditions, interrupts and exceptions, etc.) are handled by a combination of the vector decoder and RISC86 operation sequences fetched from an on-chip ROM. For complex operations, the vector decoder logic provides the first set of RISC86 operations and a vector (initial ROM address) to a sequence of further RISC86 operations. The same types of RISC86 operations are fetched from the ROM as those that are generated by the hardware decoders.

*Note:* Although all three sets of decoders are simultaneously fed a copy of the instruction buffer contents, only one of the three types of decoders is used during any one decode clock.

The decoders or the on-chip RISC86 ROM always generate a group of four RISC86 operations. For decodes that cannot fill the entire group with four RISC86 operations, RISC86 NOP operations are placed in the empty locations of the grouping. For example, a long-decoded x86 instruction that converts to only three RISC86 operations is padded with a single RISC86 NOP operation and then passed to the scheduler. Up to six groups or 24 RISC86 operations can be placed in the scheduler at a time.

All of the common, and a few of the uncommon, floating-point instructions (also known as ESC instructions) are hardware decoded as short decodes. This decode generates a RISC86 floating-point operation and, optionally, an associated

floating-point load or store operation. Floating-point or ESC instruction decode is only allowed in the first short decoder, but non-ESC instructions can be decoded simultaneously by the second short decoder along with an ESC instruction decode in the first short decoder.

All of the MMX and 3DNow! instructions, with the exception of the EMMS, FEMMS, and PREFETCH instructions, are hardware decoded as short decodes. The MMX instruction decode generates a RISC86 MMX operation and, optionally, an associated MMX load or store operation. A 3DNow! instruction decode generates a RISC86 3DNow! operation and, optionally, an associated load or store operation. MMX and 3DNow! instructions can be decoded in either or both of the short decoders.

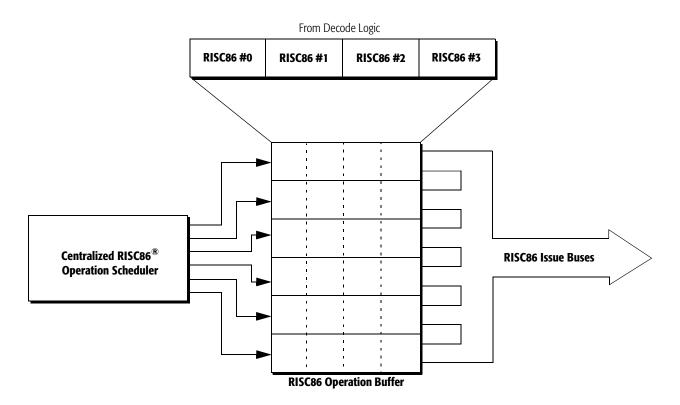

## 2.5 Centralized Scheduler

The scheduler is the heart of the Mobile AMD-K6-III-P processor (see Figure 5 on page 15). It contains the logic necessary to manage out-of-order execution, data forwarding, register renaming, simultaneous issue and retirement of multiple RISC86 operations, and speculative execution. The scheduler's buffer can hold up to 24 RISC86 operations. This equates to a maximum of 12 x86 instructions. The scheduler can issue RISC86 operations from any of the 24 locations in the buffer. When possible, the scheduler can simultaneously issue a RISC86 operation to any available execution unit (store, load, branch, register X integer/multimedia, register Y integer/multimedia, or floating-point). In total, the scheduler can issue up to six and retire up to four RISC86 operations per clock.

The main advantage of the scheduler and its operation buffer is the ability to examine an x86 instruction window equal to 12 x86 instructions at one time. This advantage is due to the fact that the scheduler operates on the RISC86 operations in parallel and allows the Mobile AMD-K6-III-P processor to perform dynamic on-the-fly instruction code scheduling for optimized execution. Although the scheduler can issue RISC86 operations for out-of-order execution, it always retires x86 instructions in order.

Figure 5. Mobile AMD-K6<sup>®</sup>-III-P Processor Scheduler

## **2.6 Execution Units**

The Mobile AMD-K6-III-P processor contains ten parallel execution units—store, load, integer X ALU, integer Y ALU, MMX ALU (X), MMX ALU (Y), MMX/3DNow! multiplier, 3DNow! ALU, floating-point, and branch condition. Each unit is independent and capable of handling the RISC86 operations. Table 1 on page 16 details the execution units, functions performed within these units, operation latency, and operation throughput.

The store and load execution units are two-stage pipelined designs. The store unit performs data writes and register calculation for LEA/PUSH. Data memory and register writes from stores are available after one clock. Store operations are held in a store queue prior to execution. From there, they execute in order. The load unit performs data memory reads. Data is available from the load unit after two clocks.

The Integer X execution unit can operate on all ALU operations, multiplies, divides (signed and unsigned), shifts, and rotates.

The Integer Y execution unit can operate on the basic word and doubleword ALU operations—ADD, AND, CMP, OR, SUB, XOR, zero-extend and sign-extend operands.

| Functional Unit   | Function                               | Latency | Throughput |

|-------------------|----------------------------------------|---------|------------|

| Store             | LEA/PUSH, Address (Pipelined)          | 1       | 1          |

| Store             | Memory Store (Pipelined)               | 1       | 1          |

| Load              | Memory Loads (Pipelined)               | 2       | 1          |

|                   | Integer ALU                            | 1       | 1          |

| Integer X         | Integer Multiply                       | 2–3     | 2–3        |

|                   | Integer Shift                          | 1       | 1          |

| Multimedia        | MMX ALU                                | 1       | 1          |

| (processes        | MMX Shifts, Packs, Unpack              | 1       | 1          |

| MMX instructions) | MMX Multiply                           | 2       | 1          |

| Integer Y         | Basic ALU (16-bit and 32-bit operands) | 1       | 1          |

| Branch            | Resolves Branch Conditions             | 1       | 1          |

| FPU               | FADD, FSUB, FMUL                       | 2       | 2          |

|                   | 3DNow! ALU                             | 2       | 1          |

| 3DNow!            | 3DNow! Multiply                        | 2       | 1          |

|                   | 3DNow! Convert                         | 2       | 1          |

Table 1.

Execution Latency and Throughput of Execution Units

#### Register X and Y Pipelines

The functional units that execute MMX and 3DNow! instructions share pipeline control with the Integer X and Integer Y units.

The register X and Y functional units are attached to the issue bus for the register X execution pipeline or the issue bus for the register Y execution pipeline or both. Each register pipeline has dedicated resources that consist of an integer execution unit and an MMX ALU execution unit, therefore allowing superscalar operation on integer and MMX instructions. In addition, both the X and Y issue buses are connected to the 3DNow! ALU, the MMX/3DNow! multiplier and MMX shifter, which allows the appropriate RISC86 operation to be issued through either bus. Figure 6 on page 17 shows the details of the X and Y register pipelines.

Figure 6. Register X and Y Functional Units

The branch condition unit is separate from the branch prediction logic in that it resolves conditional branches such as JCC and LOOP after the branch condition has been evaluated.

## 2.7 Branch-Prediction Logic

Sophisticated branch logic that can minimize or hide the impact of changes in program flow is designed into the Mobile AMD-K6-III-P processor. Branches in x86 code fit into two categories—unconditional branches, which always change program flow (that is, the branches are always taken) and conditional branches, which may or may not divert program flow (that is, the branches are taken or not-taken). When a conditional branch is not taken, the processor simply continues decoding and executing the next instructions in memory.

Typical applications have up to 10% of unconditional branches and another 10% to 20% conditional branches. The Mobile AMD-K6-III-P processor branch logic has been designed to

handle this type of program behavior and its negative effects on instruction execution, such as stalls due to delayed instruction fetching and the draining of the processor pipeline. The branch logic contains an 8192-entry branch history table, a 16-entry by 16-byte branch target cache, a 16-entry return address stack, and a branch execution unit.

**Branch History Table** The Mobile AMD-K6-III-P processor handles unconditional branches without any penalty by redirecting instruction fetching to the target address of the unconditional branch. However, conditional branches require the use of the dynamic branch-prediction mechanism built into the Mobile AMD-K6-III-P processor. A two-level adaptive history algorithm is implemented in an 8192-entry branch history table. This table stores executed branch information, predicts individual branches, and predicts the behavior of groups of branches. To accommodate the large branch history table, the Mobile AMD-K6-III-P processor does not store predicted target addresses. Instead, the branch target addresses are calculated on-the-fly using ALUs during the decode stage. The adders calculate all possible target addresses before the instructions are fully decoded and the processor chooses which addresses are valid.

- **Branch Target Cache** To avoid a one clock cache-fetch penalty when a branch is predicted taken, a built-in branch target cache supplies the first 16 bytes of instructions directly to the instruction buffer (assuming the target address hits this cache). (See Figure 3 on page 11.) The branch target cache is organized as 16 entries of 16 bytes. In total, the branch prediction logic achieves branch prediction rates greater than 95%.

- **Return Address Stack** The return address stack is a special device designed to optimize CALL and RET pairs. Software is typically compiled with subroutines that are frequently called from various places in a program. This is usually done to save space. Entry into the subroutine occurs with the execution of a CALL instruction. At that time, the processor pushes the address of the next instruction in memory following the CALL instruction onto the stack (allocated space in memory). When the processor encounters a RET instruction (within or at the end of the subroutine), the branch logic pops the address from the stack and begins fetching from that location. To avoid the latency of

22655C/0-September 1999

main memory accesses during CALL and RET operations, the return address stack caches the pushed addresses.

**Branch Execution** Unit The branch execution unit enables efficient speculative execution. This unit gives the processor the ability to execute instructions beyond conditional branches before knowing whether the branch prediction was correct. The Mobile AMD-K6-III-P processor does not permanently update the x86 registers or memory locations until all speculatively executed conditional branch instructions are resolved. When a prediction is incorrect, the processor backs out to the point of the mispredicted branch instruction and restores all registers. The Mobile AMD-K6-III-P processor can support up to seven outstanding branches.

22655C/0-September 1999

DЛ

# 3 Logic Symbol Diagram

# 4 Signal Descriptions

| Signal<br>Name | Pin Location                                              | Pin Attribute         | Name and Summary                                                                                                                                                                                                                                                                                                                                                  |

|----------------|-----------------------------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A20M#          | AK-08                                                     | Input                 | Address Bit 20 Mask                                                                                                                                                                                                                                                                                                                                               |

|                |                                                           |                       | A20M# is used to simulate the behavior of the 8086 when it is<br>running in Real mode. The assertion of A20M# causes the<br>processor to force bit 20 of the physical address to 0 prior to<br>accessing the cache or driving out a memory bus cycle. The<br>clearing of address bit 20 maps addresses that wrap above 1 Mbyte<br>to addresses below 1 Mbyte.     |

| A[31:3]        | See "Pin                                                  | A31-A5: Bidirectional | Address Bus                                                                                                                                                                                                                                                                                                                                                       |

|                | Designations<br>by Functional<br>Grouping" on<br>page 85. | A4-A3: Output         | A[31:3] contains the physical address for the current bus cycle. The processor drives addresses on A[31:3] during memory and I/O cycles, and cycle definition information during special bus cycles. The processor samples addresses on A[31:5] during inquire cycles.                                                                                            |

| ADS#           | AJ-05                                                     | Output                | Address Strobe                                                                                                                                                                                                                                                                                                                                                    |

|                |                                                           |                       | The assertion of ADS# indicates the beginning of a new bus cycle.<br>The address bus and all cycle definition signals corresponding to<br>this bus cycle are driven valid off the same clock edge as ADS#.                                                                                                                                                        |

| ADSC#          | AM-02                                                     | Output                | Address Strobe Copy                                                                                                                                                                                                                                                                                                                                               |

|                |                                                           |                       | ADSC# has the identical function and timing as ADS#. In the event ADS# becomes too heavily loaded due to a large fanout in a system, ADSC# can be used to split the load across two outputs, which improves timing.                                                                                                                                               |

| AHOLD          | V-04                                                      | Input                 | Address Hold                                                                                                                                                                                                                                                                                                                                                      |

|                |                                                           |                       | AHOLD can be asserted by the system to initiate one or more inquire cycles. To allow the system to drive the address bus during an inquire cycle, the processor floats A[31:3] and AP off the clock edge on which AHOLD is sampled asserted. The data bus and all other control and status signals remain under the control of the processor and are not floated. |

| AP             | AK-02                                                     | Bidirectional         | Address Parity                                                                                                                                                                                                                                                                                                                                                    |

|                |                                                           |                       | AP contains the even parity bit for cache line addresses driven and sampled on A[31:5]. The term <i>even parity</i> means that the total number of 1 bits on AP and A[31:5] is even. (A4 and A3 are not used for the generation or checking of address parity because these bits are not required to address a cache line.)                                       |

| Signal<br>Name | Pin Location                                              | Pin Attribute    | Name and Summary                                                                                                                                                                 |                         |  |  |

|----------------|-----------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--|--|

| APCHK#         | AE-05                                                     | Output           | Address Parity Check                                                                                                                                                             |                         |  |  |

|                |                                                           |                  | If the processor detects an address parity error of cycle, APCHK# is asserted for one clock.                                                                                     | during an inquire       |  |  |

| BE[7:0]#       | See "Pin                                                  | Output           | Byte Enables                                                                                                                                                                     |                         |  |  |

|                | Designations<br>by Functional<br>Grouping" on<br>page 85. |                  | BE[7:0]# are used by the processor to indicate the<br>during a write cycle and the requested data byt<br>cycle. The eight byte enables correspond to the<br>data bus as follows: | es during a read        |  |  |

|                |                                                           |                  | ■ BE7#: D[63:56] ■ BE3#: D[3                                                                                                                                                     | 31:24]                  |  |  |

|                |                                                           |                  | ■ BE6#: D[55:48] ■ BE2#: D[2                                                                                                                                                     | 23:16]                  |  |  |

|                |                                                           |                  | ■ BE5#: D[47:40] ■ BE1#: D[1                                                                                                                                                     | 15:8]                   |  |  |

|                |                                                           |                  | ■ BE4#: D[39:32] ■ BE0#: D[7                                                                                                                                                     | 7:0]                    |  |  |

|                |                                                           |                  | The byte enables are also used to distinguish between special bus cycles as defined in Table 7 on page 34.                                                                       |                         |  |  |

| BF[2:0]        | See "Pin Inputs,                                          |                  | Bus Frequency                                                                                                                                                                    |                         |  |  |

|                | Designations<br>by Functional<br>Grouping" on<br>page 85. | Internal Pullups | BF[2:0] determine the internal operating froe<br>processor. The frequency of the CLK input sig<br>internally by a ratio determined by the state of<br>shown below:               | nal is multiplied       |  |  |

|                |                                                           |                  |                                                                                                                                                                                  | r-Clock to<br>ock Ratio |  |  |

|                |                                                           |                  |                                                                                                                                                                                  | 5x                      |  |  |

|                |                                                           |                  | 101b 3.                                                                                                                                                                          | 0x                      |  |  |

|                |                                                           |                  | 111b 3.                                                                                                                                                                          | 5x                      |  |  |

|                |                                                           |                  | 010b 4.                                                                                                                                                                          | 0x                      |  |  |

|                |                                                           |                  | 000b 4.                                                                                                                                                                          | 5x                      |  |  |

|                |                                                           |                  | 001b 5.                                                                                                                                                                          | Ox                      |  |  |

|                |                                                           |                  | 011b 5.                                                                                                                                                                          | 5x                      |  |  |

|                |                                                           |                  | 110b 6.                                                                                                                                                                          | Ox                      |  |  |

|                |                                                           |                  | BF[2:0] have weak internal pullups and default to unconnected.                                                                                                                   | the 3.5 ratio if left   |  |  |

22655C/0-September 1999

| Signal<br>Name | Pin Location                                              | Pin Attribute   | Name and Summary                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------|-----------------------------------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BOFF#          | Z-04                                                      | Input           | Backoff                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                |                                                           |                 | If BOFF# is sampled asserted, the processor unconditionally aborts<br>any cycles in progress and transitions to a bus hold state by floating<br>the following signals: A[31:3], ADS#, ADSC#, AP, BE[7:0]#,<br>CACHE#, D[63:0], D/C#, DP[7:0], LOCK#, M/IO#, PCD, PWT, SCYC,<br>and W/R#. These signals remain floated until BOFF# is sampled<br>negated. This allows an alternate bus master or the system to<br>control the bus. |

| BRDY#          | X-04                                                      | Input,          | Burst Ready                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                |                                                           | Internal Pullup | BRDY# is asserted to the processor by system logic to indicate<br>either that the data bus is being driven with valid data during a<br>read cycle or that the data bus has been latched during a write<br>cycle. BRDY# is also used to indicate the completion of special bus<br>cycles.                                                                                                                                          |

| BRDYC#         | Y-03                                                      | Input,          | Burst Ready Copy                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                |                                                           | Internal Pullup | BRDYC# has the identical function as BRDY#. In the event BRDY# becomes too heavily loaded due to a large fanout in a system, BRDYC# can be used to reduce this loading, which improves timing.                                                                                                                                                                                                                                    |

| BREQ           | AJ-01                                                     | Output          | Bus Request                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                |                                                           |                 | BREQ is asserted by the processor to request the bus in order to complete an internally pending bus cycle. The system logic can use BREQ to arbitrate among the bus participants.                                                                                                                                                                                                                                                 |

| CACHE#         | U-03                                                      | Output          | Cacheable Access                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                |                                                           |                 | For reads, CACHE# is asserted to indicate the cacheability of the current bus cycle. For write cycles, CACHE# is asserted to indicate the current bus cycle is a modified cache-line writeback.                                                                                                                                                                                                                                   |

| CLK            | AK-18                                                     | Input           | Clock                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                |                                                           |                 | The CLK signal is the bus clock for the processor and is the reference for all signal timings under normal operation.                                                                                                                                                                                                                                                                                                             |

| D/C#           | AK-04                                                     | Output          | Data/Code                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                |                                                           |                 | The processor drives D/C# during a memory bus cycle to indicate whether it is addressing data or executable code. D/C# is also used to define other bus cycles, including interrupt acknowledge and special cycles.                                                                                                                                                                                                               |

| D[63:0]        | See "Pin                                                  | Bidirectional   | Data Bus                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                | Designations<br>by Functional<br>Grouping" on<br>page 85. |                 | D[63:0] represent the processor's 64-bit data bus. Each of the eight bytes of data that comprise this bus is qualified by a corresponding byte enable.                                                                                                                                                                                                                                                                            |